# HEWLETT-PACKARD

# HP Vectra QS Hardware Technical Reference Manual

(HP Vectra QS/16S, QS/16 and QS/20)

HP Part No. D1410-90002 Printed in France: JUNE 89

#### **Notice**

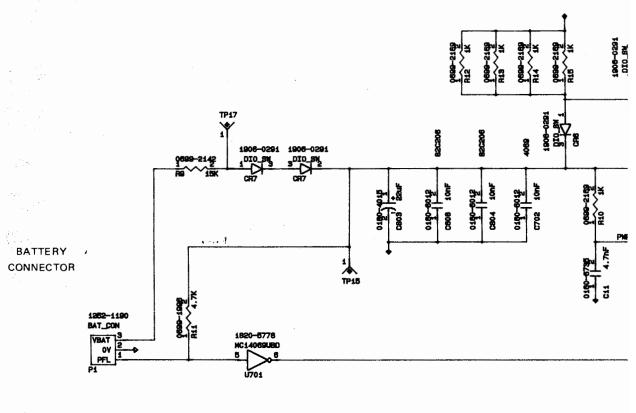

The information contained in this document is subject to change without notice.

Hewlett-Packard makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated into another language without the prior written consent of Hewlett-Packard Company.

IBM is a registered trademark of International Business Machines Corporation. Vectra is a registered trademark of Hewlett-Packard Company.

Lotus 1-2-3 is a registered trademark of Lotus Development Corporation.

MS-DOS is a U.S. registered trademark of Microsoft Corporation.

Centronics is a U.S. registered trademark of Centronics Data Computer Corporation.

© 1989 Hewlett-Packard Company

Hewlett-Packard Grenoble Personal Computer Division, 5, Avenue Raymond Chanas, 38320 Eybens, France.

# **Printing History**

Edition: 3 Printed in France: June 89

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

#### **FCC Statement**

Federal Communications Commission Radio Frequency Interference Statement (USA only).

This equipment has been certified to comply with the limits for a Class B computing device, pursuant to Subpart J of Part 15 of FCC Rules. Only peripherals (computer input/output devices, terminals, printers, etc.) certified to comply with the Class B limits may be attached to this computer. Operation with non-certified peripherals is likely to result in interference to radio and television reception.

Because the HP Vectra QS PC generates and uses radio frequency energy, it may cause interference with radio and television reception in a residential installation.

Hewlett-Packard provides instructions for using this computer in manuals covering setup, connection of peripheral devices, operation, service, and technical reference.

Installing and using the computer in strict accordance with Hewlett-Packard's instructions will minimize the chances that the HP Vectra QS PC will cause radio or television interference. However, Hewlett-Packard does not guarantee that the computer will not interfere with radio or television reception.

If you think the computer is causing interference, turn it off to see if radio or television reception improves. If the reception improves, the computer is causing the problem.

To correct interference, take one or more of the following steps:

- Relocate the radio or television antenna

- Move the computer away from the radio or television

- Plug the computer into a different electrical outlet, so that the computer and the radio or television are on separate electrical circuits

- Make sure that all of your peripheral devices are certified Class B by the FCC

- Make sure that you use only shielded cables to connect peripheral devices to your computer

- Consult your computer dealer, Hewlett-Packard, or an experienced radio/television technician for other suggestions.

# **Electrical Safety**

Warning

For user safety, the power cords supplied with this product have grounded plugs. The power cord should be used with properly grounded (3-hole) wall outlets to avoid electrical shock. (You can also use multiple-outlet strips that have their own circuit breakers.)

# INTRODUCTION

#### Audience

This manual is intended to help original equipment manufacturers, independent hardware vendors, and independent software vendors in their design efforts.

#### Scope of Manual

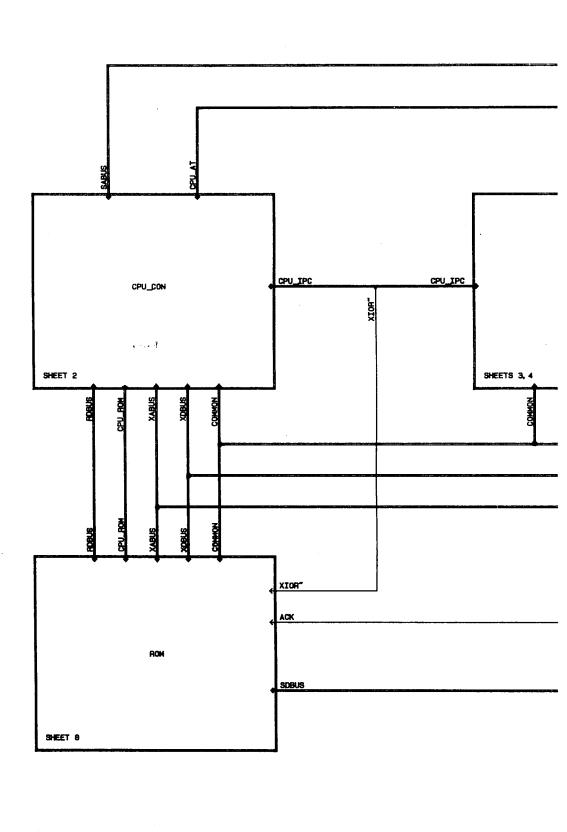

Chapter 1 gives a system overview of the Hewlett-Packard Vectra QS Personal Computer.

Chapter 2 discusses the QS/16 and QS/20 Processor/Memory PCA components.

Chapter 3 discusses the QS/16S Processor/Memory PCA components.

Chapter 4 discusses the System Interface PCA components.

Chapter 5 discusses the Power Supply.

Schematics and a Glossary of terms are also included.

# Contents

|   | Crant and Organization                                                   |

|---|--------------------------------------------------------------------------|

|   | System Overview .1 INTRODUCTION                                          |

| 1 |                                                                          |

|   | 1.1.1 Users                                                              |

|   | 1.1.2 Features                                                           |

|   | 1.1.3 Compatibility                                                      |

|   | 1.1.4 QS/16 Versus QS/20 Versus QS/16S                                   |

| 1 | 2 SYSTEM CONFIGURATIONS                                                  |

|   | 1.2.1 Basic Configuration                                                |

|   | 1.2.2 Configuration Options                                              |

| 1 |                                                                          |

|   | 1.3.1 Hardware                                                           |

|   | 1.3.2 Memory Subsystem                                                   |

|   | 1.3.3 Software                                                           |

| 1 | .4 SPECIFICATIONS AND DIMENSIONS                                         |

|   | 1.4.1 System Specifications                                              |

|   | 1.4.2 Environmental Specifications                                       |

|   | 1.4.3 HP Vectra QS PC Dimensions                                         |

|   | 1.4.4 I/O Accessory Card Dimensions                                      |

| 1 | 1.5 REFERENCES                                                           |

| • | 2.2 SYSTEM CLOCKS                                                        |

|   | QS/16 & QS/20 Processor/Memory Printed Circuit Assembly 2.1 INTRODUCTION |

|   |                                                                          |

| 2 | 2.3 MICROPROCESSOR                                                       |

|   | 2.3.1 I/O Address Map                                                    |

|   | 2.4 COPROCESSOR                                                          |

| 2 | 2.5 MEMORY                                                               |

|   | 2.5.1 Main Memory (RAM)                                                  |

|   | Main Memory Architecture                                                 |

|   | Memory Map                                                               |

|   | Main Memory Operation                                                    |

|   | 2.5.2 Read-Only Memory                                                   |

| : | 2.6 PAGE MEMORY CONTROLLER                                               |

|   | 2.7 BUS CONTROLLER                                                       |

|   | 2.8 CONTROL BUFFER                                                       |

|   | 2.9 ADDRESS BUFFERS                                                      |

|   | 2.10 DATA BUFFERS                                                        |

|   | 2.10 DAIA DUTTEMS                                                        |

|   | 2.11 LOCAL BUS (LBUS)                                                    |

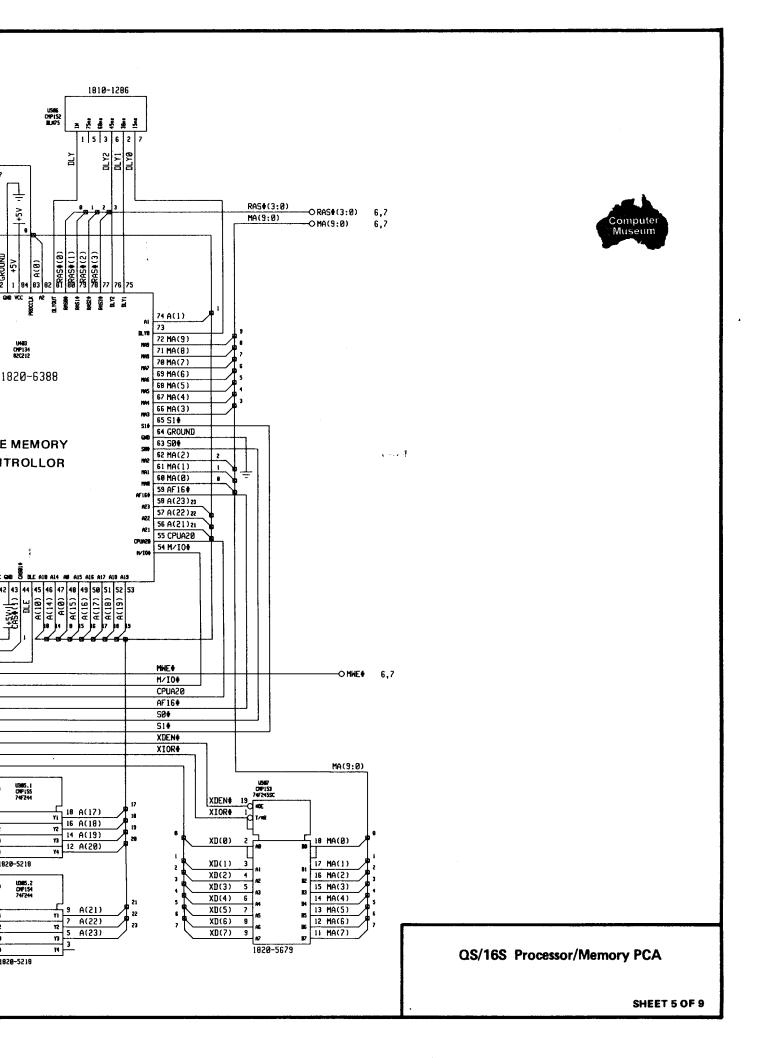

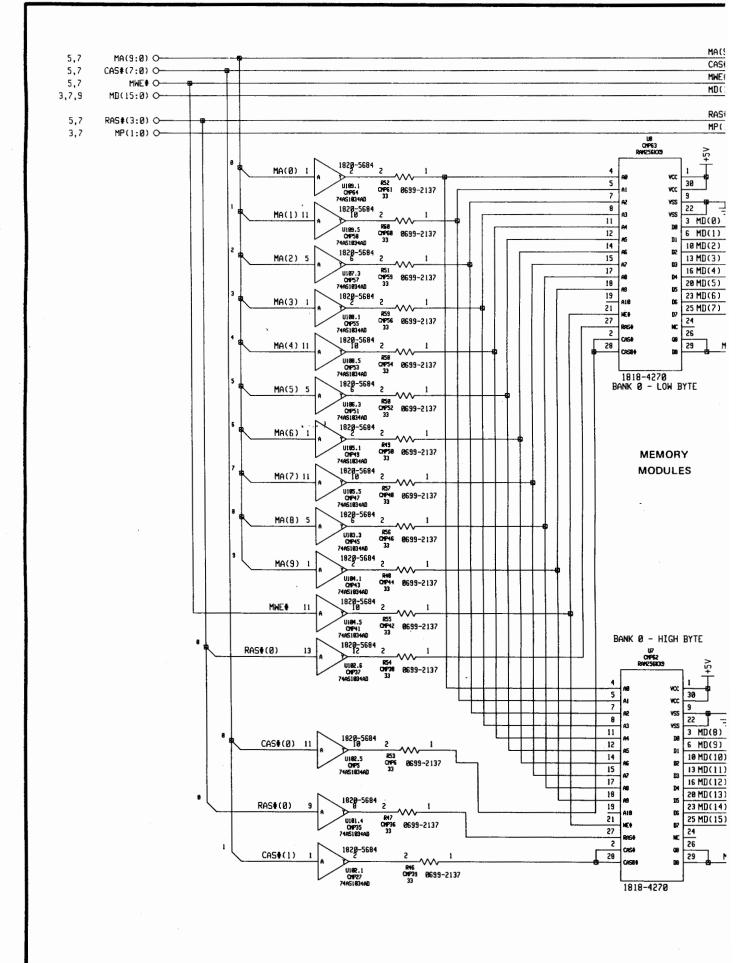

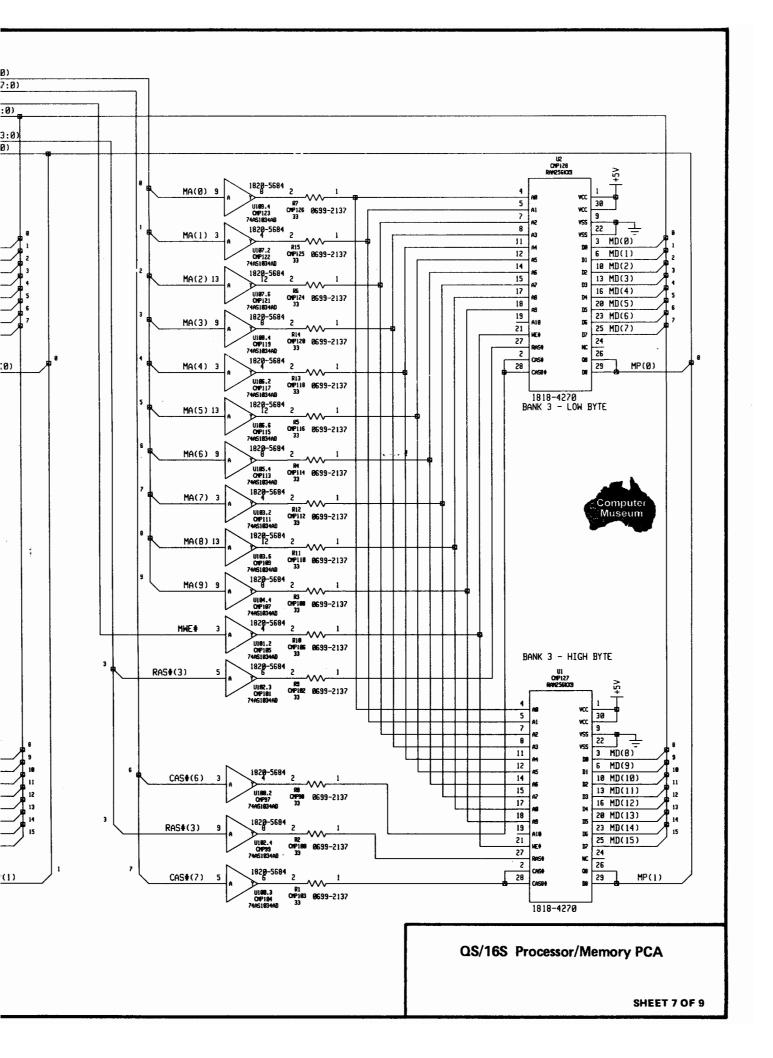

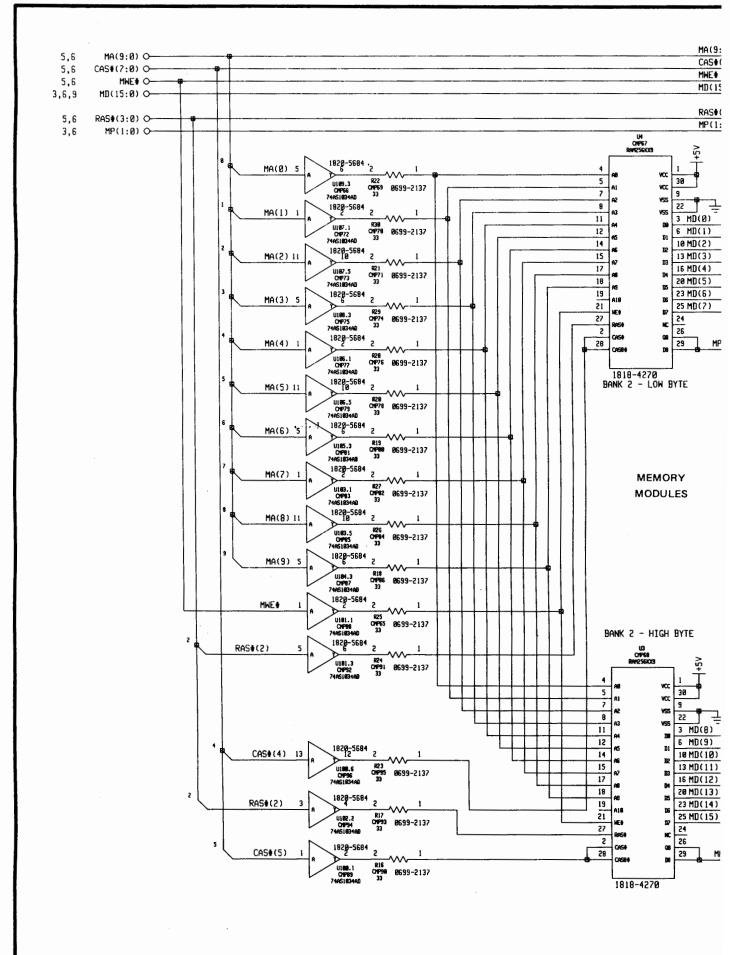

| . QS/16S Processor/Memory Printed Circuit Assembly                |  |

|-------------------------------------------------------------------|--|

| 3.1 INTRODUCTION                                                  |  |

| 3.2 SYSTEM CLOCKS                                                 |  |

| 3.3 MICROPROCESSOR                                                |  |

| 3.3.1 I/O Address Map                                             |  |

| 3.4 COPROCESSOR                                                   |  |

| 3.5 MEMORY                                                        |  |

| 3.5.1 Main Memory (RAM)                                           |  |

| Main Memory Architecture                                          |  |

| Memory Map                                                        |  |

| Main Memory Operation                                             |  |

| 3.5.2 Read-Only Memory                                            |  |

| 3.6 PAGE MEMORY CONTROLLER                                        |  |

| 3.7 BUS CONTROLLER                                                |  |

| 3.9 ADDRESS/DATA BUFFERS                                          |  |

| 3.10 LOCAL BUS (LBUS)                                             |  |

| 3.12 MEMORY BUS                                                   |  |

| 3.13 READ-ONLY MEMORY BUS                                         |  |

| 3.14 BACKPLANE I/O BUS (SBUS)                                     |  |

| 3.15 PERIPHERAL BUS                                               |  |

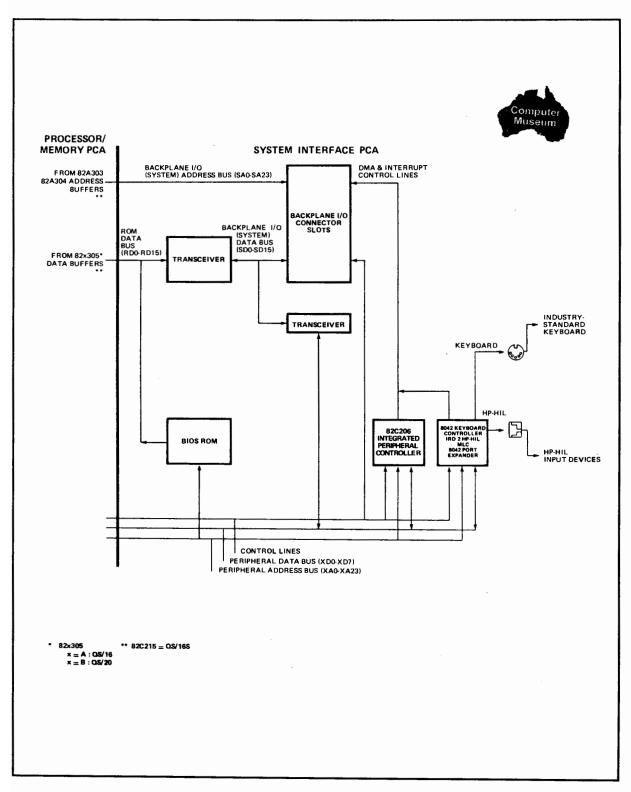

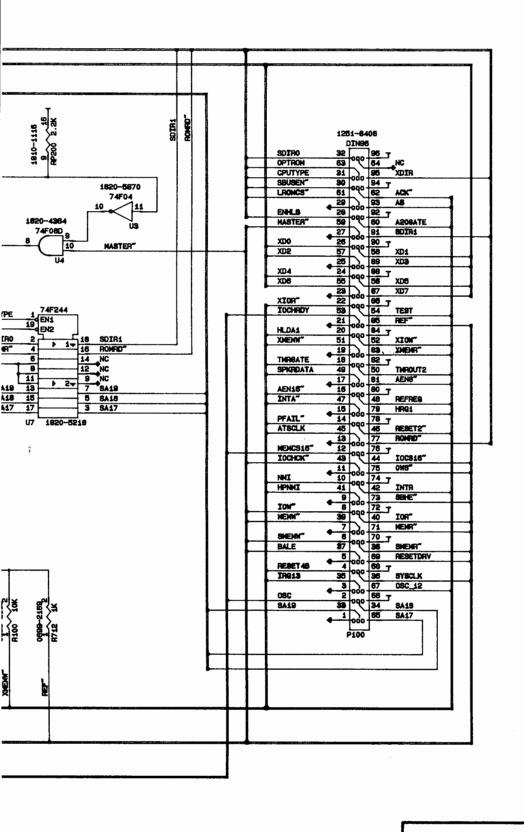

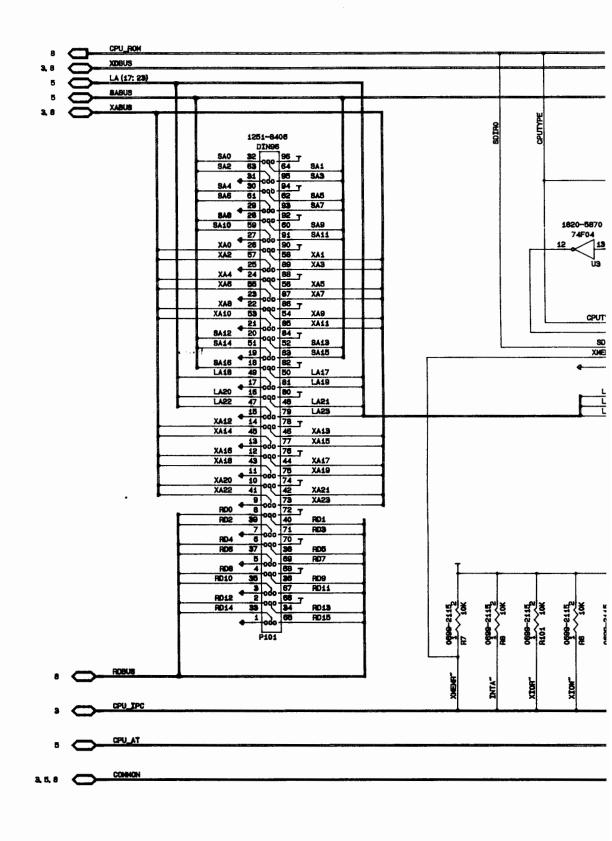

| System Interface Printed Circuit Assembly                         |  |

| 4.1 INTRODUCTION                                                  |  |

| 4.1.1 PC Type Selection                                           |  |

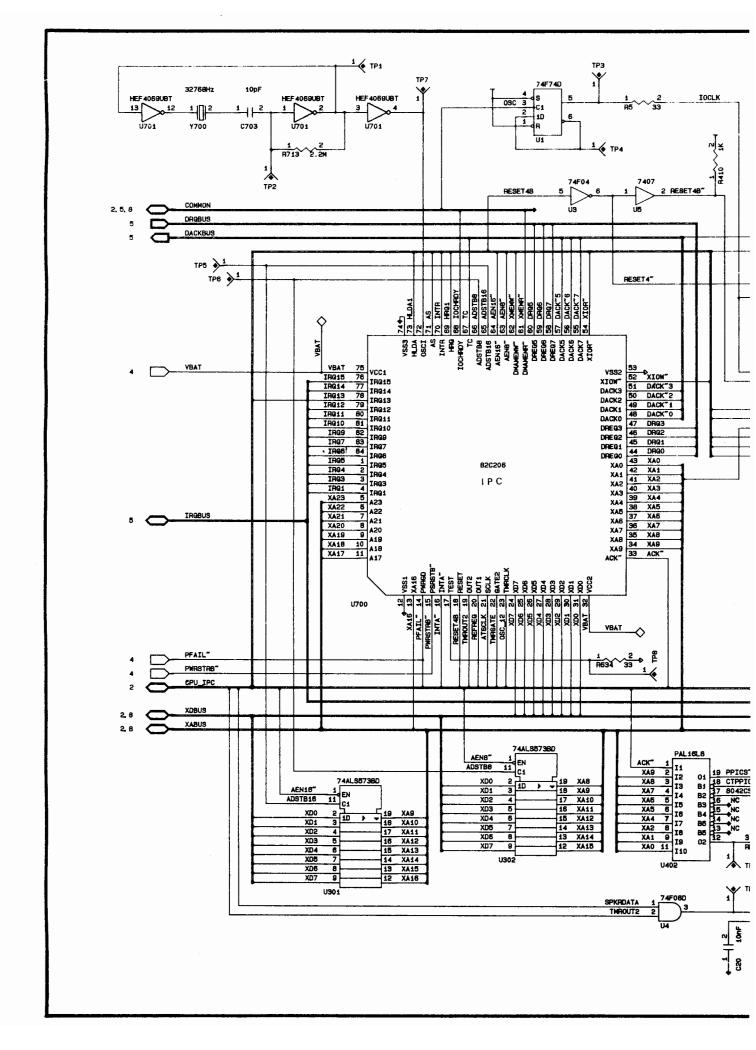

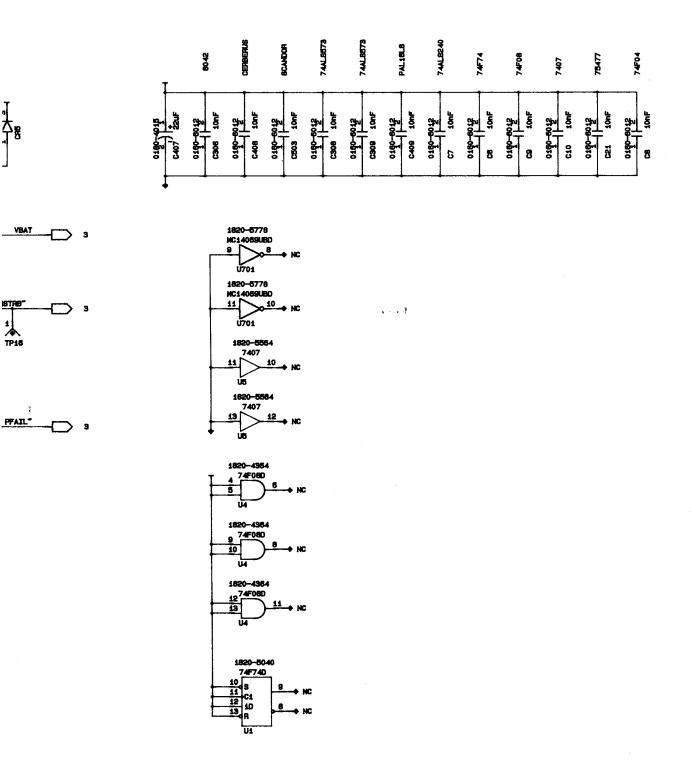

| 4.2 INTEGRATED PERIPHERAL CONTROLLER                              |  |

| 4.2.1 DMA Controller                                              |  |

| 4.2.2 Interrupt Controller                                        |  |

| 4.2.3 Real-Time Clock(RTC)/CMOS RAM                               |  |

| 4.2.4 Counter/Timers                                              |  |

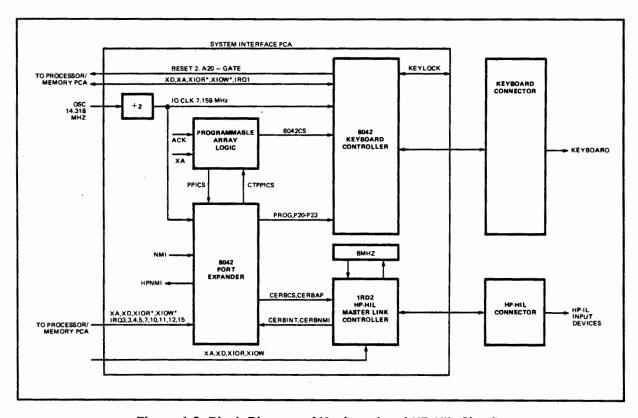

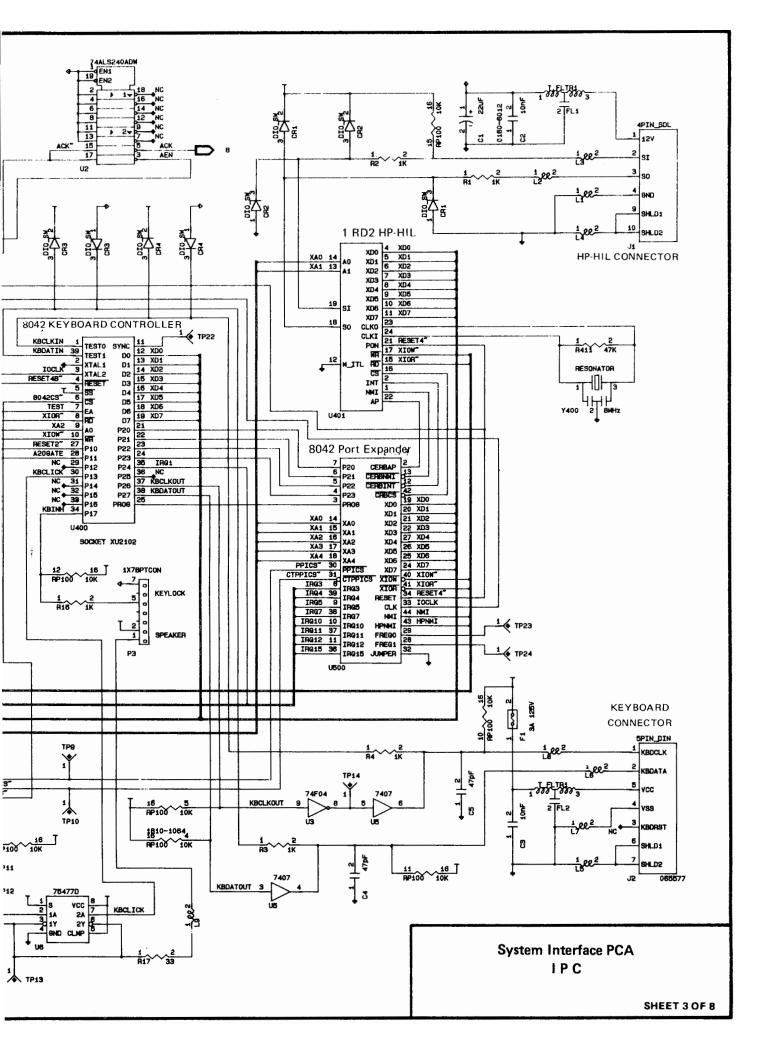

| 4.3 KEYBOARD AND HP-HIL CIRCUITS                                  |  |

| 4.3.1 Keyboard                                                    |  |

| 4.3.2 Keyboard Controller                                         |  |

| 4.3.3 8042 Keyboard Controller Port Expander                      |  |

| 4.3.4 HP-HIL                                                      |  |

| 4.4 READ-ONLY MEMORY                                              |  |

| 4.4.1 BIOS ROM                                                    |  |

| 4.4.2 Option ROM                                                  |  |

| 4.5 BACKPLANE I/O CONNECTOR SLOTS                                 |  |

| 4.5.1 Pinout Diagrams and Signal Assignments for Backplane I/O Co |  |

| Slots                                                             |  |

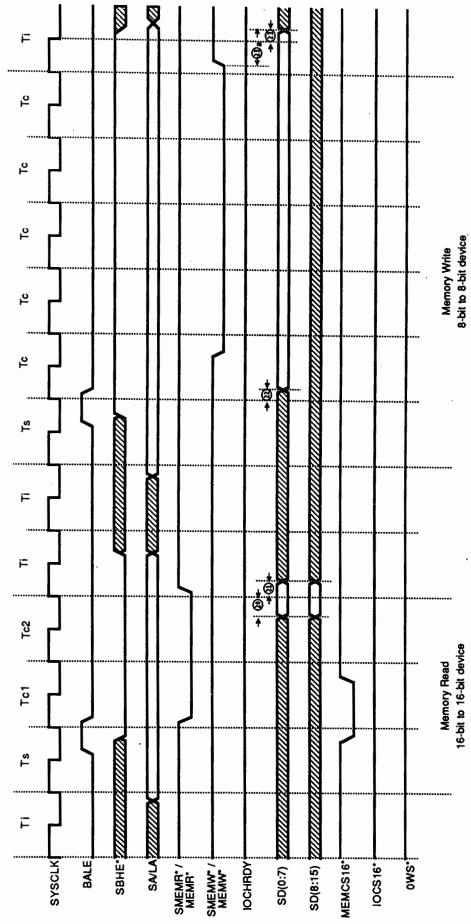

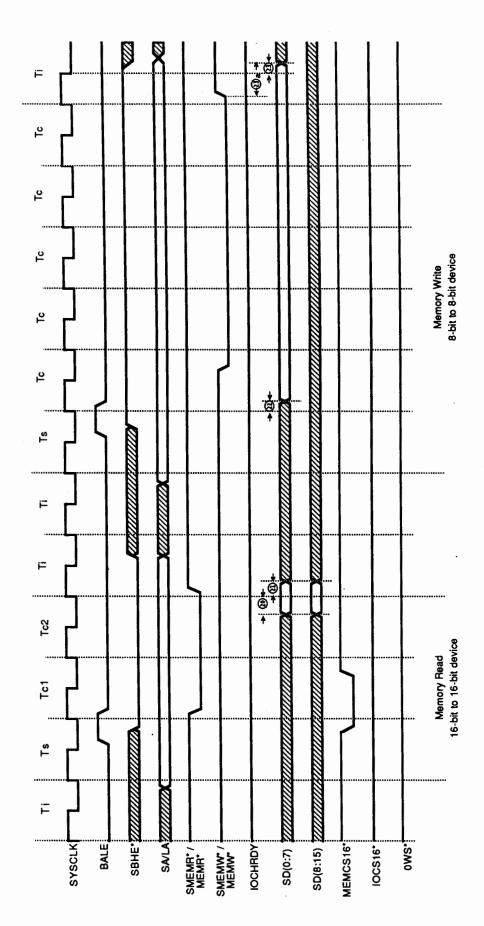

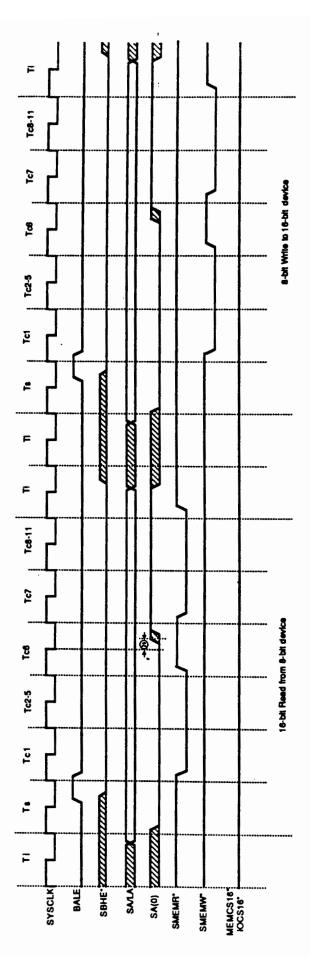

| 4.5.2 Backplane I/O Timing Diagrams                               |  |

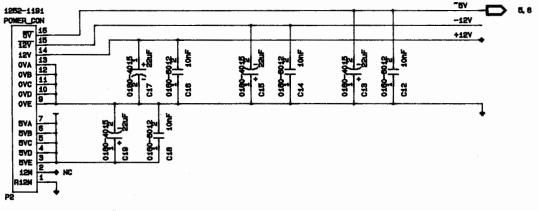

| <b>5</b> . | Power Supply                                |     |

|------------|---------------------------------------------|-----|

|            | 5.1 INTRODUCTION                            | 5-1 |

|            |                                             | 5-2 |

|            | 5.3 POWER SUPPLY OUTPUT                     | 5-2 |

|            | 5.3.1 Power to Backplane I/O                | 5-5 |

|            | 5.4 POWER SUPPLY PROTECTION                 | 5-6 |

|            | 5.4.1 Line Dropout Protection               | 5-6 |

|            |                                             | 5-6 |

|            |                                             | 5-6 |

|            | 5.4.4 Overcurrent Protection                | 5-6 |

|            | 5.4.5 Overvoltage Protection                | 5-7 |

|            |                                             | 5-7 |

|            | 5.4.7 Fan                                   | 5-7 |

|            | 5.5 POWER SUPPLY OPERATING STATUS INDICATOR | 5-8 |

|            | 5.6 BATTERY POWER                           | -10 |

| A.         | I/O Address Map                             |     |

| В.         | Drawings                                    |     |

|            | Glossary                                    |     |

|            | Index                                       |     |

# **Figures**

| 1-1.         | Basic Configuration of HP Vectra QS Personal Computer System Processing Unit |

|--------------|------------------------------------------------------------------------------|

| 1.9          | HP Vectra QS/16 & QS/20 System Architecture                                  |

|              | HP Vectra QS/16S System Architecture                                         |

|              | Industry-Standard I/O Card Dimensions                                        |

|              | QS/16 & QS/20 Processor/Memory PCA Component Layout                          |

|              | QS/16 & QS/20 Processor/Memory PCA Block Diagram                             |

|              | QS/16 & QS/20 Processor/Memory PCA Timing                                    |

|              | HP Vectra QS PC Memory Map                                                   |

|              |                                                                              |

| 2-3.         | QS/16 & QS/20 Physical Organization of DRAM (Board/Memory Modules            |

| 26           | View)                                                                        |

|              | QS/16 & QS/20 Processor/Memory PCA Switches                                  |

|              | QS/16S Processor/Memory PCA Component Layout                                 |

| ე-1.         | OS/16S Processor/Memory PCA Pleak Diagram                                    |

|              | QS/16S Processor/Memory PCA Block Diagram                                    |

|              | QS/16S Processor/Memory PCA Timing                                           |

|              | Coprocessor Interface                                                        |

| <b>3</b> -5. | HP Vectra QS PC Memory Map                                                   |

| 3-6.         | Memory Refresh                                                               |

|              | QS/16S Physical Organization of DRAM (Board/Memory Modules View) .           |

|              | Logical Organization of DRAM                                                 |

| 3-9.         | Address Control                                                              |

| 3-10.        | Data Control                                                                 |

| 3-11.        | QS/16S Processor/Memory PCA Switches                                         |

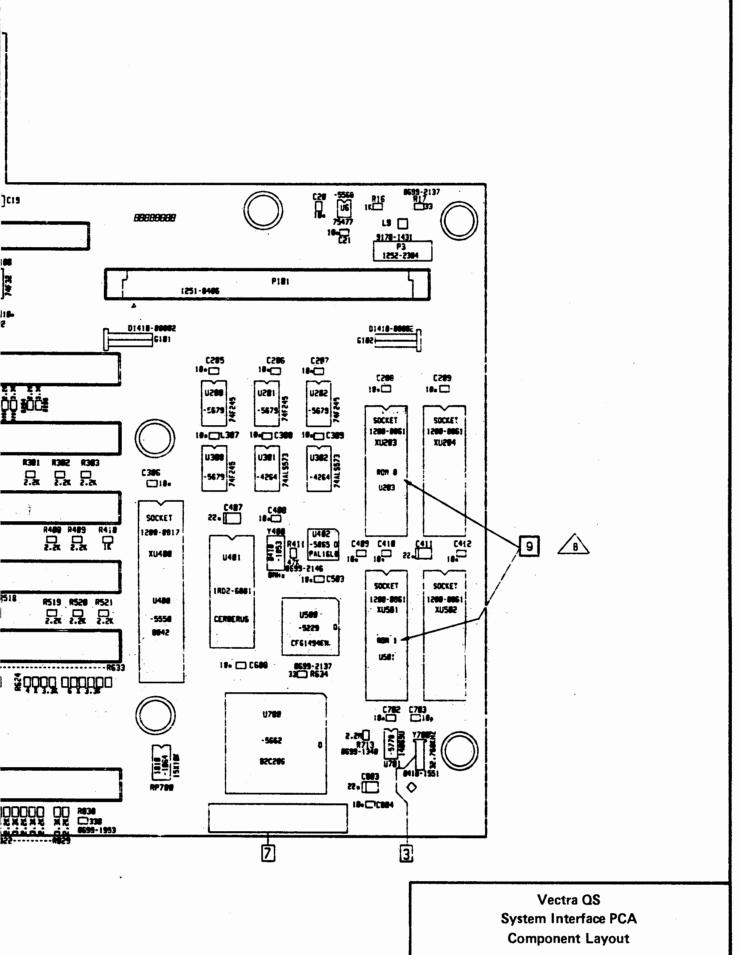

| 4-1.         | System Interface PCA Component Layout                                        |

|              | System Interface PCA Block Diagram                                           |

|              | Block Diagram of Keyboard and HP-HIL Circuits                                |

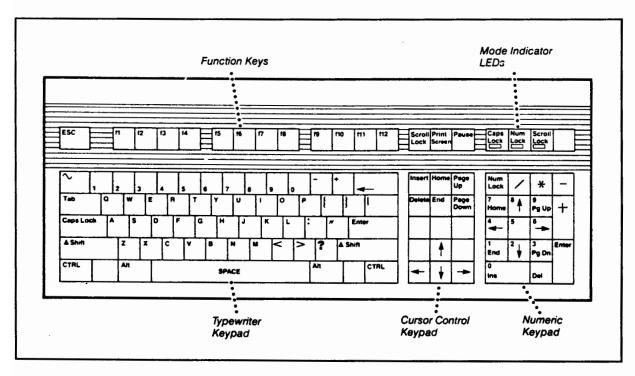

|              | HP Vectra QS PC Keyboard (USASCII)                                           |

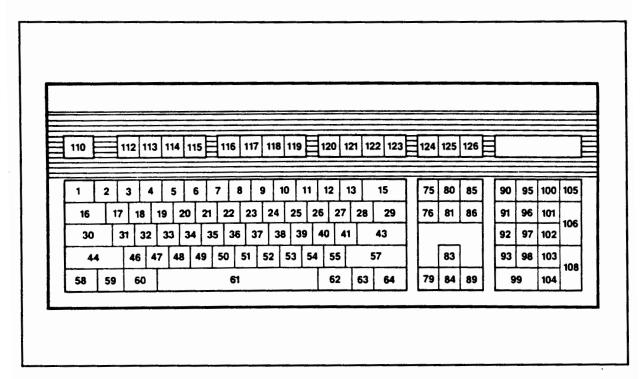

| 4-5.         | Keyboard Reference Numbers (USASCII)                                         |

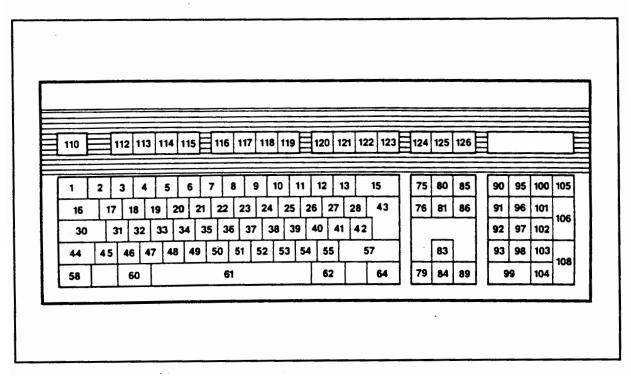

| 4-6.         | Keyboard Reference Numbers (National Keyboard)                               |

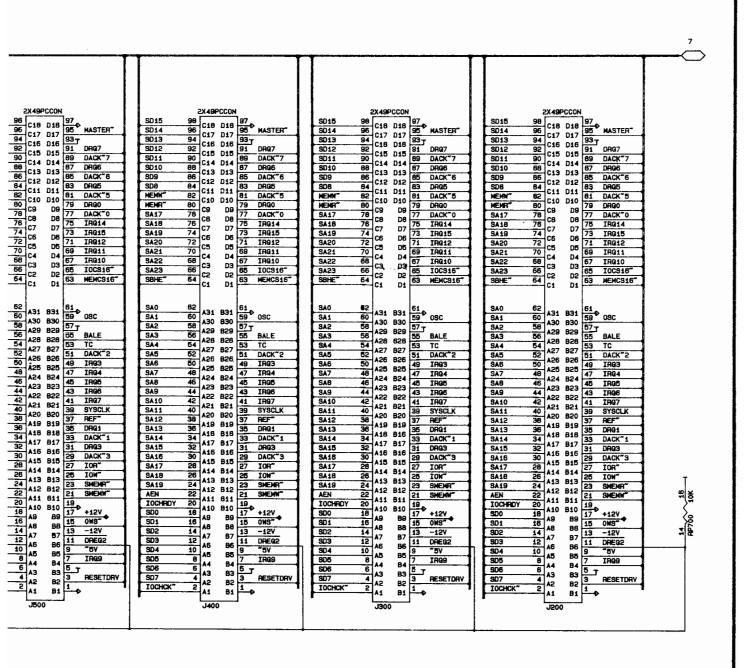

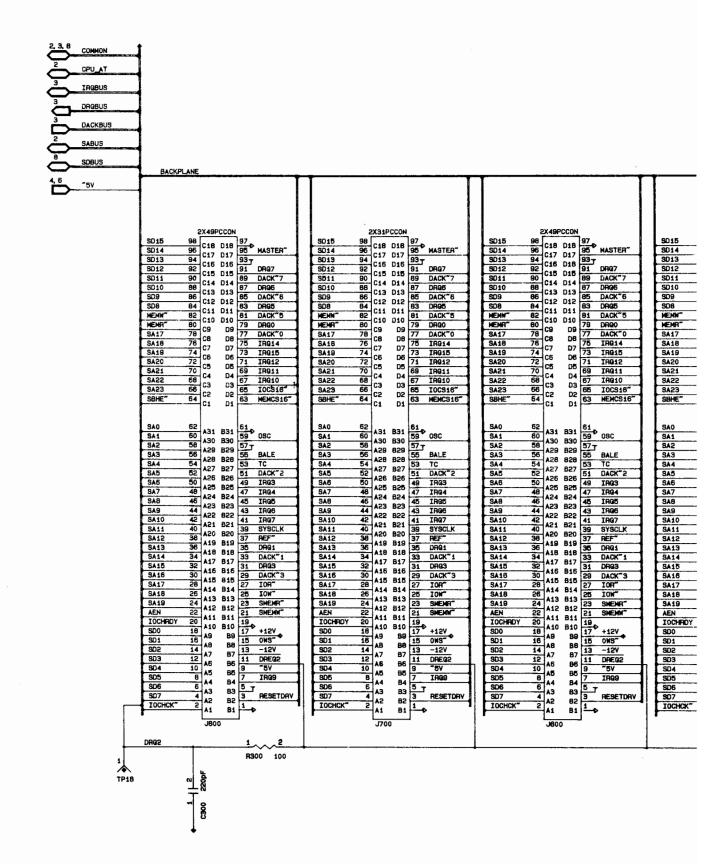

| 4-7.         | Pinout Diagrams for Backplane I/O Connector Slots                            |

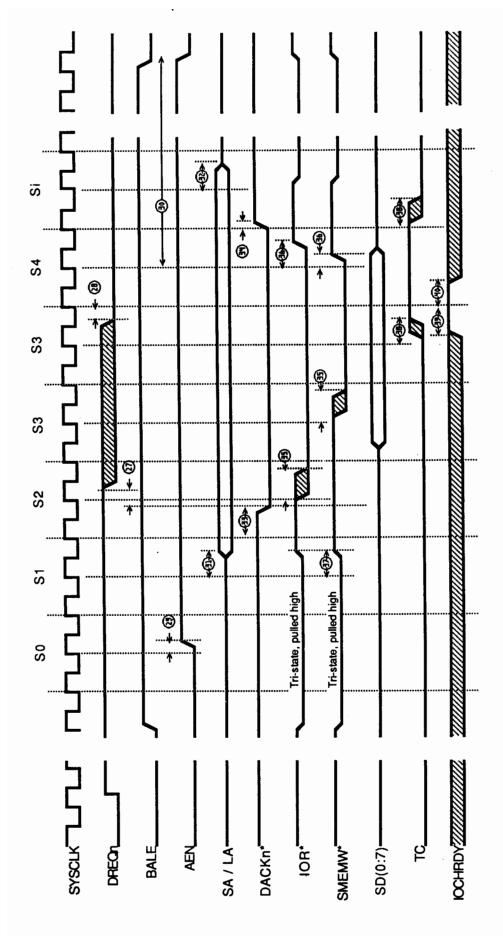

|              | Backplane I/O Timing diagram: Common timing                                  |

|              | Backplane I/O Timing diagram: Memory cycle                                   |

| 4-10.        | Backplane I/O Timing diagram: I/O cycle                                      |

|              | Backplane I/O Timing diagram: 16 bit to 8 bit cycles                         |

| 4-12.        | Backplane I/O Timing diagram: Single byte/word DMA transfer from I/O to      |

|              | memory                                                                       |

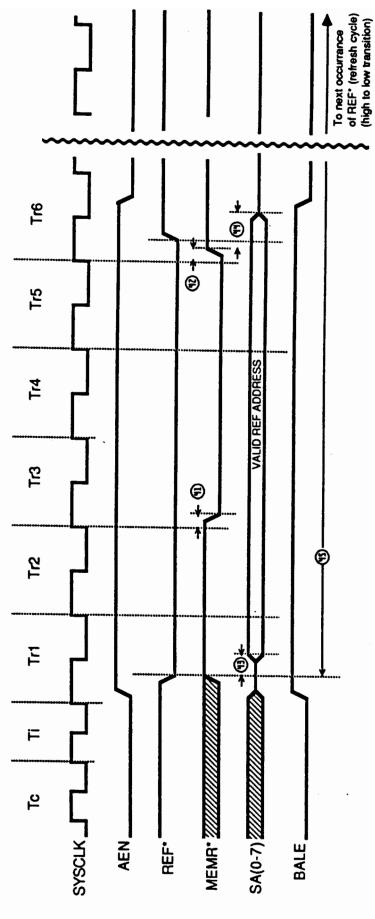

| 4-13.        | Backplane I/O Timing diagram: Refresh                                        |

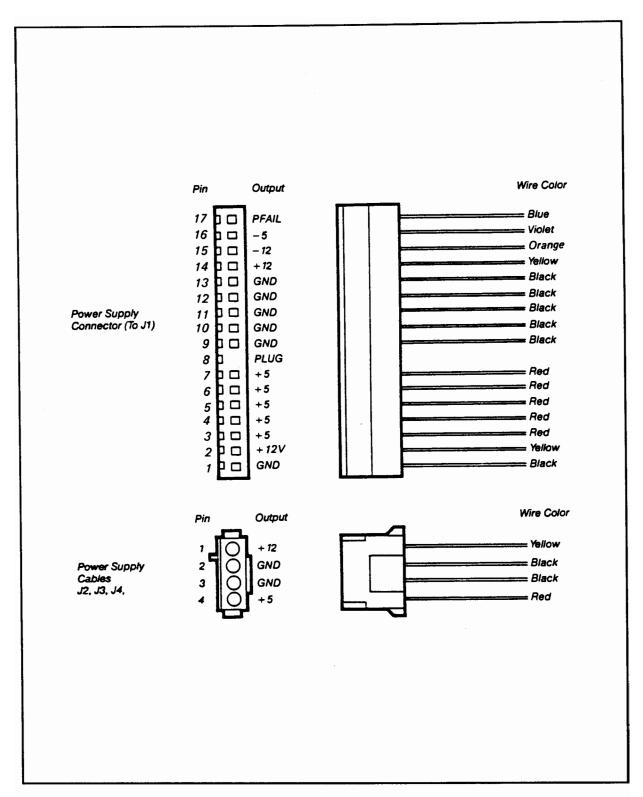

|              | Power Supply Connector Pinouts                                               |

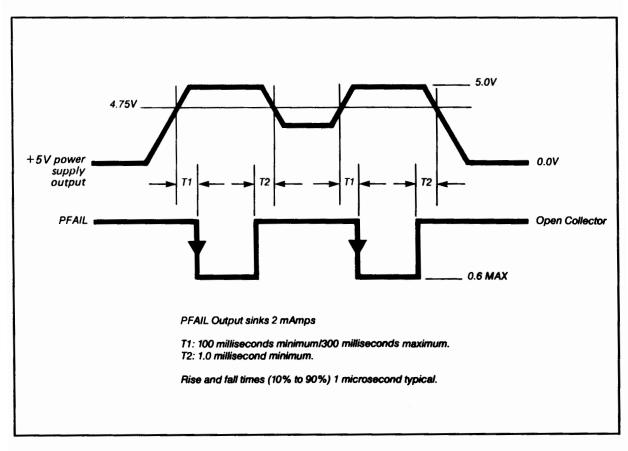

| 5-2          | PFAIL Timing Diagram                                                         |

|              | QS/16 & QS/20 PFAIL Block Diagram                                            |

|              | QS/16S PFAIL Block Diagram                                                   |

|              |                                                                              |

# **Tables**

| 1-1.  | Differences Between the QS/16, QS/20 and QS/16S                         |

|-------|-------------------------------------------------------------------------|

|       | QS/16 & QS/20 Main Memory Expansion                                     |

| 2-2.  | QS/16 & QS/20 Processor/Memory PCA Default Switch Settings              |

|       | QS/16S Supported Main Memory Expansion                                  |

| 3-2.  | QS/16S Processor/Memory PCA Default Switch Settings                     |

|       | I/O Addresses for IPC Components                                        |

|       | Interrupt Map                                                           |

|       | Real-Time Clock/CMOS RAM Memory Map                                     |

|       | Keyboard Hex Scan Codes                                                 |

|       | Keyboard Scan Codes                                                     |

|       | Keyboard Scan Codes                                                     |

|       | Keyboard Scan Codes                                                     |

|       | Keyboard Scan Codes                                                     |

|       | Commands Sent Between the System and the Keyboard                       |

| 4-10. | Keyboard Scan Codes Data Transmission Format                            |

| 4-11. | 8042 Keyboard Controller Port Expander Pin Assignments                  |

| 4-12. | HP-HIL Controller Pin Assignments                                       |

| 4-13. | HP-HIL Connector Pin Assignments                                        |

|       | Backplane I/O Connector Slot Signal Assignments                         |

|       | Backplane I/O Connector Slot Signal Descriptions                        |

|       | Notes for Timing Diagrams                                               |

| 5-1.  | Power Supply Voltages                                                   |

|       | Pin Assignments for Power Supply Connector J1 (To System Interface PCA) |

|       | Pin Assignments for Power Supply Connectors J2 to J4 (Cables To Disc    |

|       | Drives)                                                                 |

| 5-4.  | Power Supply Output at Start-up and After Start-up                      |

|       | Power to Backplane I/O Connector Slots                                  |

|       | . Voltage Levels Which Cause Power Supply Overvoltage                   |

|       | I/O Address Man for CPII Components                                     |

|  | . <del>(**</del> * |  |  |

|--|--------------------|--|--|

|  |                    |  |  |

|  |                    |  |  |

|  |                    |  |  |

|  |                    |  |  |

|  |                    |  |  |

|  |                    |  |  |

|  |                    |  |  |

|  |                    |  |  |

# System Overview

#### 1.1 INTRODUCTION

This manual provides information on the Hewlett-Packard Vectra QS/16, QS/20 and QS/16S Personal Computers. The manual refers to these computers using the generic name "HP Vectra QS". Where specific differences occur between the computers, these differences are explained in the text.

This chapter gives an overview of the Hewlett-Packard Vectra QS Personal Computer. It includes system configurations, architecture, and specifications, along with references used in writing this manual.

#### 1.1.1 **Users**

The HP Vectra QS is a high-performance, industry-standard, desk-top personal computer. The Vectra QS/16 and QS/20 are based on the Intel 80386 microprocessor running at 16 MHz and 20 MHz respectively. The Vectra QS/16S is based on the Intel 80386SX microprocessor running at 16 MHz.

The HP Vectra QS PC is geared towards users with demanding, computation-intensive tasks requiring great power and fast response time. Typical uses include the following:

Computer-Aided Design/Engineering/Manufacturing Database Management Desktop Publishing Local-Area Network Servers

#### 1.1.2 Features

The HP Vectra QS PC has the following features:

80386 microprocessor (QS/16 and QS/20)

80386SX microprocessor (QS/16S)

Socket for numeric coprocessor

System RAM, QS/16 and QS/20: 1 Mbyte of 32-bit RAM, expandable up to 16 Mbytes.

QS/16S: 1 Mbyte of 16-bit RAM, expandable up to 8 Mbytes.

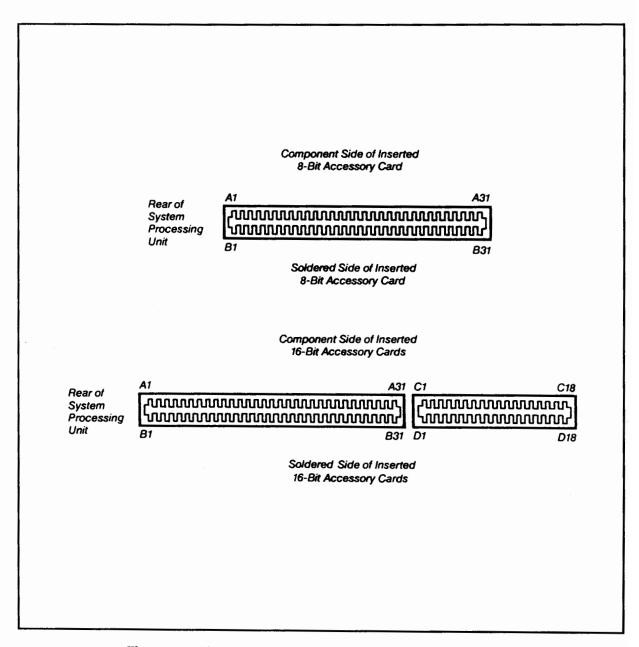

Backplane I/O connector slots for up to 7 industry-standard accessory cards

Disc caching

9-pin serial port and 25-pin parallel port

Flexible disc controller and drive

Hard disc controller and drive

Support for up to 3 mass storage devices

Industry-standard keyboard

Support for up to 7 HP-Human Interface Link input devices

#### 1.1.3 Compatibility

The HP Vectra QS PC is designed to be 100% compatible with the industry-standard IBM PC/AT II personal computer and with the HP Vectra family of personal computers.

It offers downward compatibility, running industry-standard operating systems (including MS-DOS 3.2, MS-DOS 3.3, Microsoft OS/2, and Windows 2.0) and industry-standard application software developed for systems based on 8088, 8086, or 80286 microprocessors. It also offers upward compatibility in that it is designed to run Windows/386 and operating systems and applications based on the 80386 microprocessor.

#### 1.1.4 QS/16 Versus QS/20 Versus QS/16S

Table 1-1 lists the differences between the QS/16, QS/20 and QS/16S.

Component QS/16 QS/20 **QS/16S** 80386 @ 16 MHz 80386 @ 20 MHz 80386SX at 16 MHz Processor 40 MHz Processor clock 32 MHz 32 MHz 82C301 @ 20 MHz Bus controller 82C301 @ 16 MHz 82C211 @ 16 MHz Control buffer 82C306 82C306 Page memory controller 82C302 @ 16 MHz 82C302 @ 20 MHz 82C212 @ 16 MHz Address buffer 82C303 & 82C304 82C303 & 82C304 82C215 Data buffer 82A305 82B305 100 ns, max 16 MB Memory modules 80 ns, max 16 MB 100 ns, max 8 MB

Table 1-1. Differences Between the QS/16, QS/20 and QS/16S

In addition, the Processor/Memory PCA "Switch 1" default settings (see Chapter 2 and 3) and BIOS are different.

#### 80386 Versus 80386SX

Both the 80386SX and the 80386 are 32-bit microprocessors, however:

- The 80386SX has a 16-bit external data bus, compared to 32 bits on the 80386. This means bus access is slower for 32-bit instructions.

- The 80386SX has a 24-bit external address bus, compared to 32 bits on the 80386. This means the 80386SX has a physical memory address space of 16 Mbytes compared with 4 gigabytes on the 80386.

In addition, the QS/16S coprocessor is selected using address line A23. On the QS/16 and QS/20, the coprocessor is selected using address line A31.

## 1.2 SYSTEM CONFIGURATIONS

#### 1.2.1 Basic Configuration

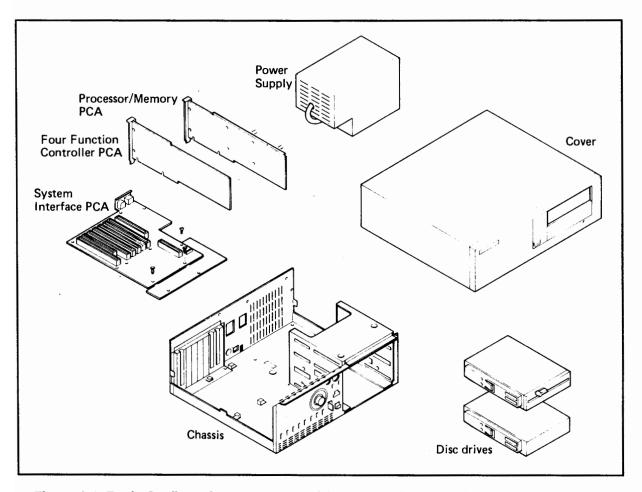

Figure 1-1 shows the basic configuration of the HP Vectra QS PC System Processing Unit (SPU):

- a power supply

- the System Interface PCA (printed circuit assembly) with seven backplane I/O (PCA) slots

- two other main PCAs (the Processor/Memory PCA and the Four-Function Controller PCA), that plug into the System Interface PCA

- one hard and one flexible disc drive.

Figure 1-1. Basic Configuration of HP Vectra QS Personal Computer System Processing Unit

#### 1.2.2 Configuration Options

The HP Vectra QS PC comes in several models. Refer to the product data sheet for complete details.

# 1.3 SYSTEM ARCHITECTURE OVERVIEW

This section gives an overview of the HP Vectra QS PC system architecture.

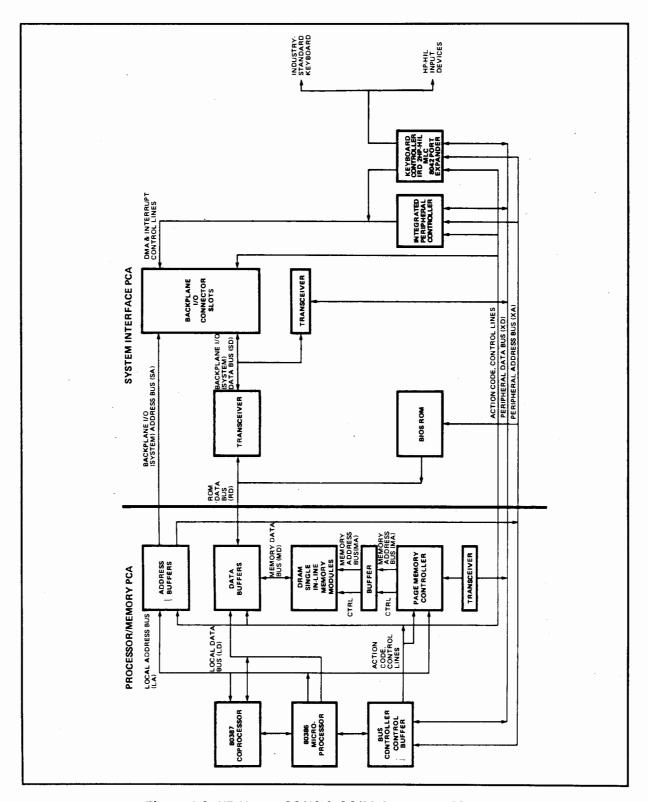

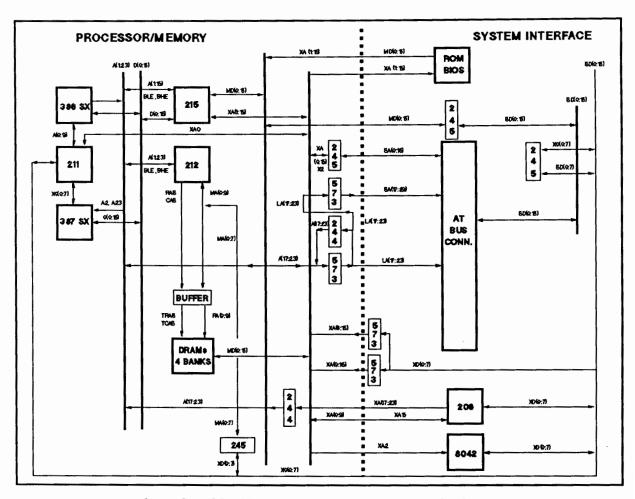

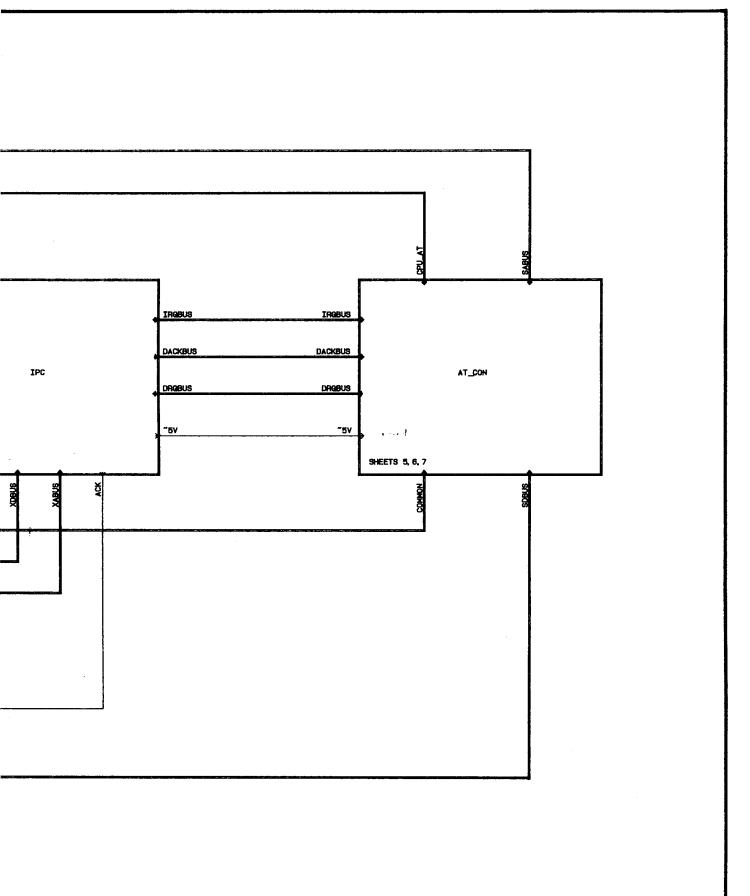

Figure 1-2. HP Vectra QS/16 & QS/20 System Architecture

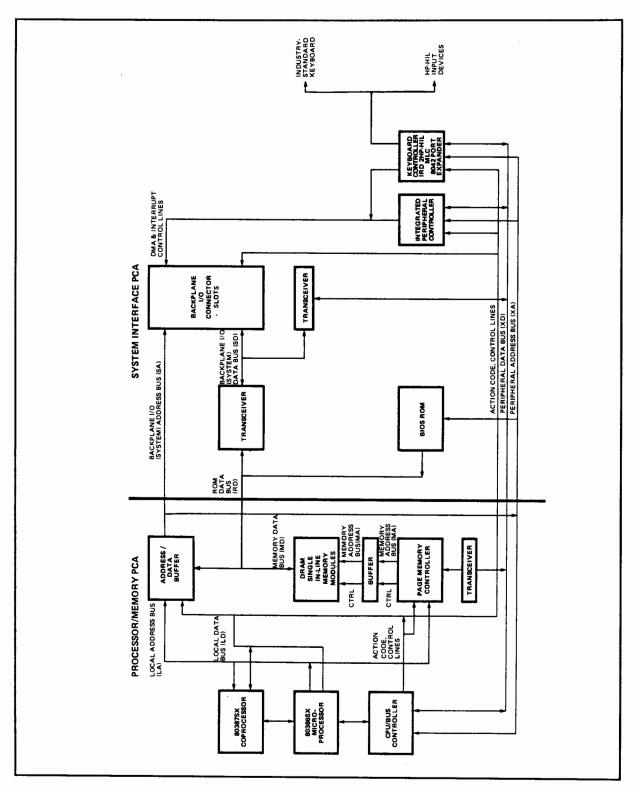

Figure 1-3. HP Vectra QS/16S System Architecture

#### 1.3.1 Hardware

Power Supply. The power supply provides 134 watts of continuous power (176 watts peak).

Backplane I/O. The backplane I/O consists of one 8-bit and six 16-bit I/O connector slots for industry-standard accessory cards operating at 8 MHz (or at 10 MHz on the QS/20).

Real-Time Clock/CMOS RAM. The real-time clock/calendar includes 114 bytes of CMOS RAM. A 6-Volt lithium battery provides power to the real-time clock/CMOS RAM during power-down and power failures.

System Microprocessor. The HP Vectra QS/16 and QS/20 PCs are based on the 32-bit 80386 microprocessor. The QS/16 uses a clock rate of 16-MHz, and the QS/20 uses 20-MHz. The HP Vectra QS/16S is based on the 32-bit, 16 MHz 80386SX microprocessor.

The keyboard can be used to switch the clock rate to 8 MHz.

Coprocessor. The HP Vectra QS supplies a socket for a numeric coprocessor: 80387 on the QS/16 and QS/20, 80387SX on the QS/16S.

The QS/16S coprocessor operates synchronously with the processor clock.

On the QS/16 and QS/20, the coprocessor operates either synchronously with the processor clock or asynchronously, switch selectable (via setting 6 on the Processor/Memory PCA's Switch 1).

Monitor. Both monochrome and color monitors are available, along with accessory cards for the monitors.

Security Lock. The HP Vectra QS PC has an optional security lock that can be fitted to the front of the SPU. It prevents inputs from the keyboard and other devices and also secures the SPU unit cover.

Keyboard. The HP Vectra PC Keyboard is a detachable, 101-key (USASCII) or 102-key (national), industry-standard keyboard. It has separate numeric and cursor control keypads and an industry-standard DIN cable connector.

Hewlett-Packard Human Interface Link Devices. The HP Vectra QS PC has an HP-HIL port which allows up to seven HP-HIL devices (such as a mouse, graphics tablet, and barcode reader) to be operated simultaneously.

Four-Function Controller PCA. The Four-Function Controller PCA supports the HP Vectra QS PC's hard disc, flexible disc, and tape backup drives, as well as a parallel port and a serial port. Depending on the PC model, the controller is either the industry-standard ST-506 controller or the Enhanced Small Device Interface (ESDI) controller.

Hard Disc Drives. The following hard disc drives are supported:

The D1297A 40 Mbyte hard disc drive. This drive has an average access time of 28 milliseconds and a maximum data transfer rate of 5 Mbits/second.

The D1445A 100 Mbyte hard disc drive.

The D1446A 150 Mbyte hard disc drive.

The HP Vectra QS PC can support up to two half-height hard disc drives. (See the data sheet for more information on the available hard disc drive models.)

Flexible Disc Drives. All HP Vectra QS PC models come with either a 5.25-inch, 1.2-Mbyte half-height flexible disc drive unit or a 3.5-inch, 1.44-Mbyte flexible disc drive. All models can support up to two flexible disc drive units.

Tape Backup Drives. For hard disc drive backup, the HP Vectra QS PC supports both an internal 40 Mbyte tape backup drive unit with an average data transfer rate of 1.7 Mbyte/minute, and an external 67 Mbyte tape backup drive unit with an average data transfer rate of 2.0 MB/minute.

#### 1.3.2 Memory Subsystem

RAM. The HP Vectra QS PC comes standard with 1 Mbyte of DRAM, expandable to 8 MB (QS/16S) or 16 Mbyte (QS/16 and QS/20). The DRAM subsystem uses a combination paged/interleaved architecture which allows for zero-wait state memory access.

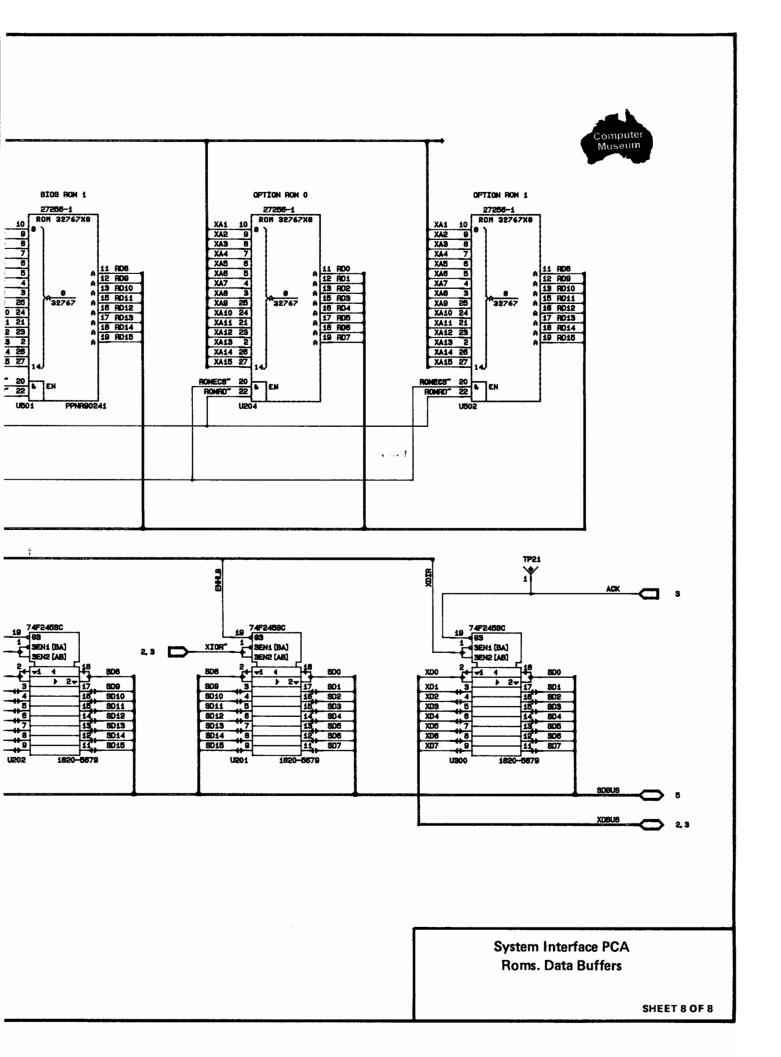

ROM. All models come with 64 Kbyte of system (BIOS) ROM, with two sockets available for 32-Kbyte option ROM chips (on the System Interface PCA).

#### 1.3.3 Software

The HP Vectra QS PC comes standard with the following:

HP Terminal Program software (for terminal emulation) Volume Expansion Utility HP Expanded Memory Manager /386

## 1.4 SPECIFICATIONS AND DIMENSIONS

### 1.4.1 System Specifications

#### Regulatory Compliance

1. Radio Frequency Interference:

FCC Class B FTZ 1046/84 Level B Radio Protection Mark pending SABS approval VCCI approval

2. Safety approvals:

UL listed CSA, TUV certified (FEI pending) IEC 380/435 compliance

3. Datacomm:

Belgium, Germany Nordic Network, and United Kingdom—pending Australian Telecomm Category A license.

4. Ergonomics:

Complies with German Standard ZH1/68

#### **Power Supply Specifications**

1. AC Input

Auto-ranging world-wide power supply, configured to operate with line voltages of:

88 to 132 Vac at 47 to 63 Hz 175 to 269 Vac at 47 to 63 Hz

2. Heat Output

710 BTUs/hour maximum

3. Output Power

176 watts peak (134 watts continuous)

4. Power Available to Accessory Cards

+5 Volts @ 7.5 Amps -5 Volts @ 0.3 Amps +12 Volts @ 0.5 Amps -12 Volts @ 0.3 Amps

5. Power Consumption

Convenience outlet unused:

480 watts maximum peak with 110 volts power supply

Convenience outlet used:

630 watts maximum peak with 110 volts power supply

#### 1-8 System Overview

#### 1.4.2 Environmental Specifications

#### Temperature Limits:

Operating temperature:

+5 to +40 °C (+40 to +104 °F) at the humidity limits given below

Storage temperature:

-40 to +70 °C (-40 to +158 °F)

#### Humidity Limits (Noncondensing):

5% to 95% relative humidity

#### Maximum Altitude at 40°C (104°F):

Operating altitude: 4.6 kilometers (15,000 feet)

Non-operating altitude: 15.2 kilometers (50,000 feet)

#### 1.4.3 HP Vectra QS PC Dimensions

#### System Processing Unit Dimensions:

Height: 17 centimeters (6.7 inches)

Width: 42.5 centimeters (16.7 inches)

Depth: 39 centimeters (15.3 inches)

Weight: 15 kilograms (33 pounds)

#### **Keyboard Dimensions:**

Height: 3.4 centimeters (1.4 inches)

Width: 46.8 centimeters (18.4 inches)

Depth: 19.8 centimeters (7.8 inches)

Weight: 1.9 kilograms (4.2 pounds)

#### Cable Length:

DIN cable: 2 meters (6.6 feet)

HP-HIL cable: 2.4 meters (8.0 feet)

Mouse cable: 2.5 meters (8.25 feet)

Video cable: 1 meter (3.3 feet)

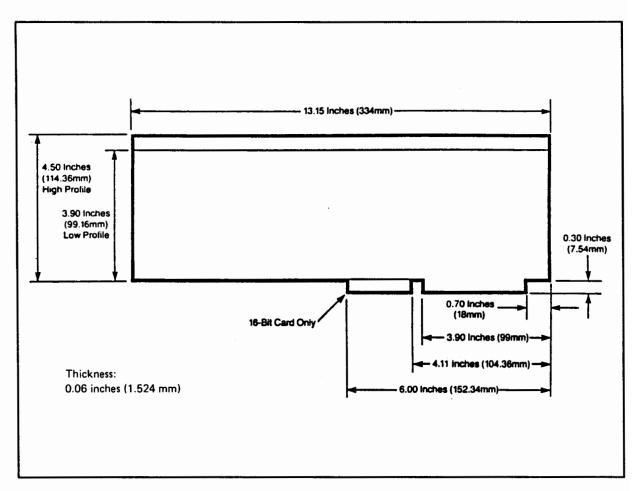

## 1.4.4 I/O Accessory Card Dimensions

Figure 1-4 shows the dimensions of industry-standard I/O accessory cards.

Figure 1-4. Industry-Standard I/O Card Dimensions

#### 1.5 REFERENCES

The following documents should be used for detailed information about components and functions discussed in this manual.

- Chips and Technologies series of 82A and 82C technical reference documents.

- HP Vectra MS-DOS 3.3 User's Reference Manual. HP product number 45951D.

- MS-DOS Macro Assembler Manual.

- MS-DOS 3.3 Programmer's Reference Manual.

- HP Vectra System BIOS Technical Reference Manual for the Vectra Series of Personal Computers. HP product number 45945-90012.

- HP-HIL Technical Reference Manual. HP product number 45918A.

- Intel 8086 Family User's Manual.

- Intel 80386 Hardware Reference Manual.

- Intel 80386SX Hardware Reference Manual.

- Intel 80386 Programmer's Reference Manual.

- Intel Microcontroller Handbook.

- Intel Microprocessor and Peripheral Handbook. Volume I -- Microprocessor.

- Intel Microsystem Components Handbook. Microprocessors and Peripherals. Volume II.

- Motorola Single Chip Microcomputer Data, Section C.

# QS/16 & QS/20 Processor/Memory **Printed Circuit Assembly**

## 2.1 INTRODUCTION

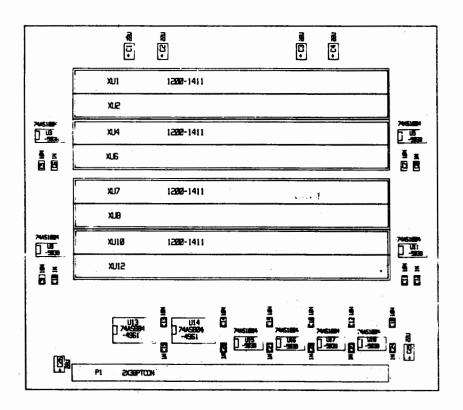

This chapter describes the QS/16 and QS/20 Processor/Memory PCA—a six-layer, surface-mount printed circuit assembly which provides the HP Vectra QS (QS/16 and QS/20) PC with all its RAM, the support circuitry for all buses, and support for the board's subsystems.

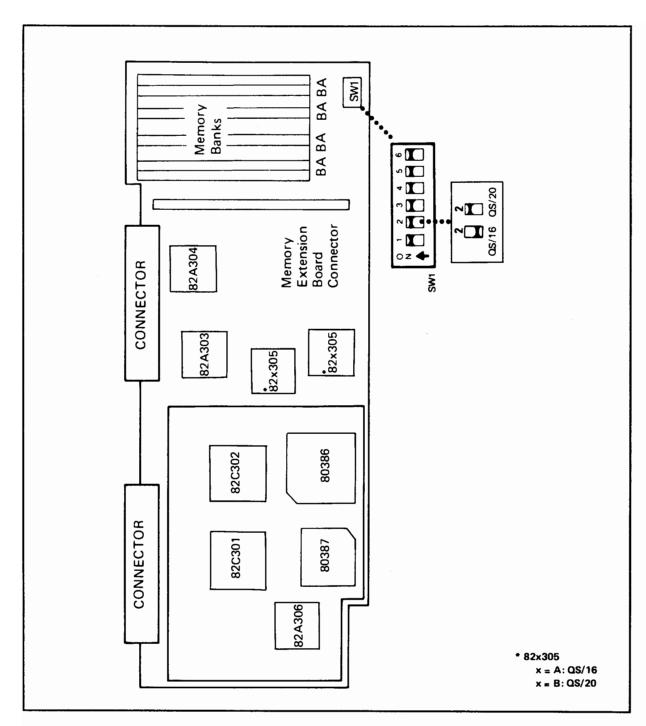

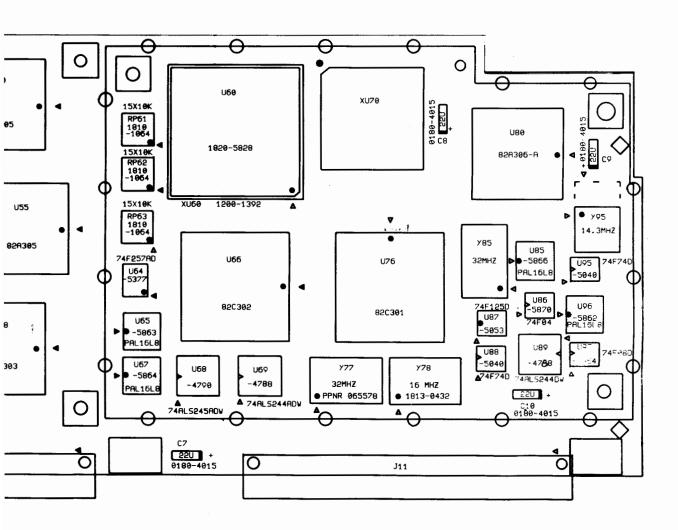

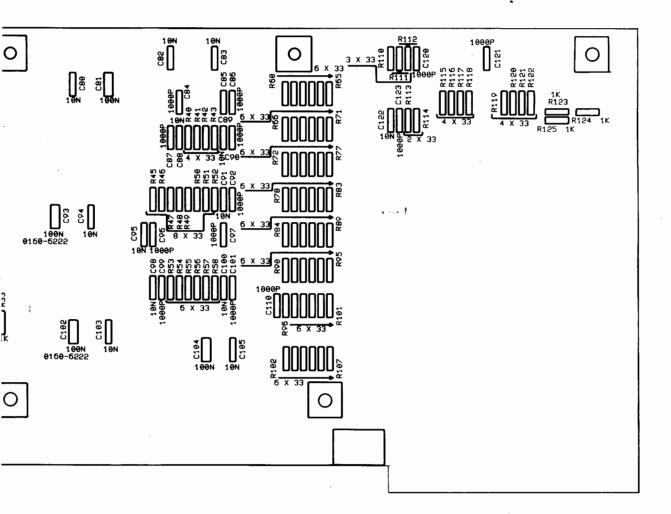

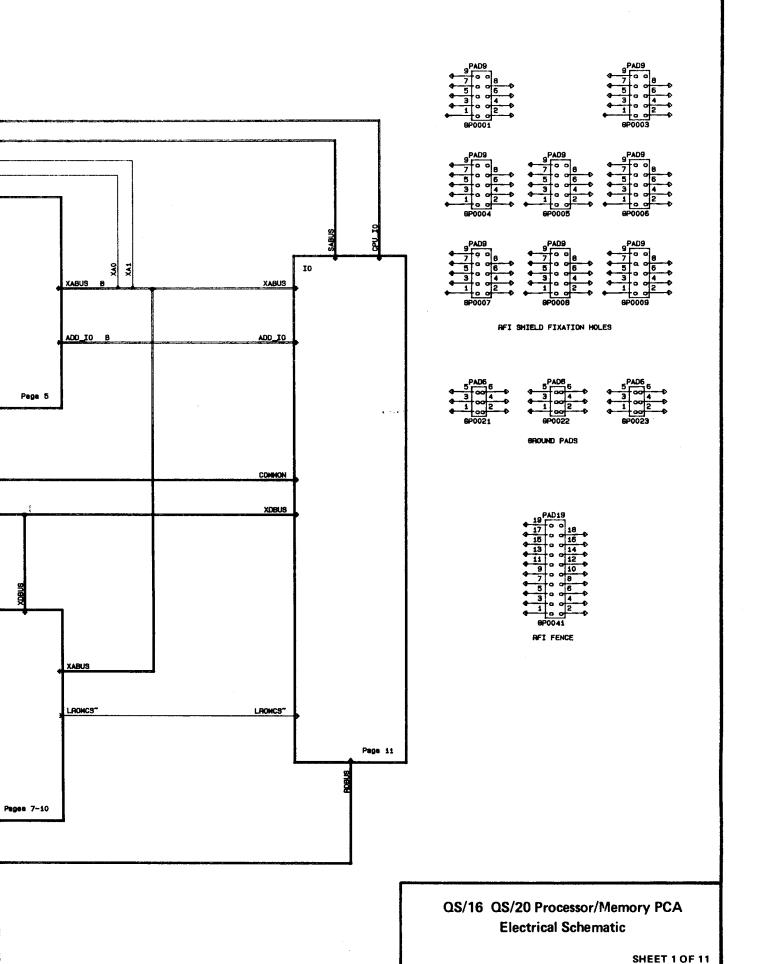

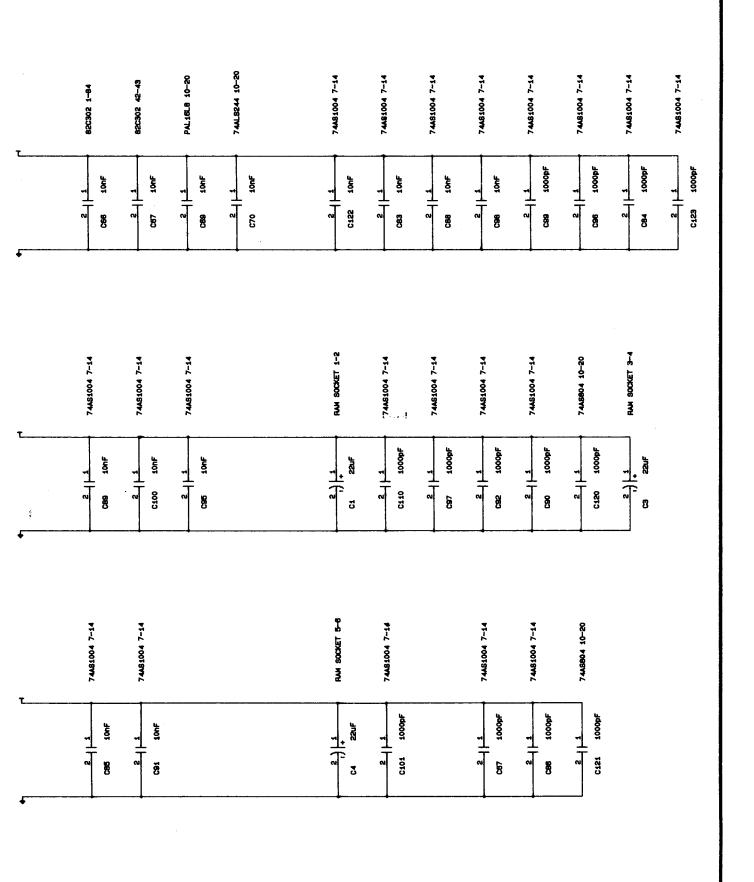

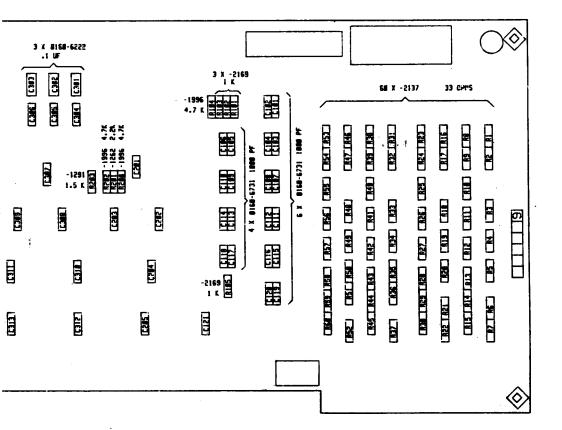

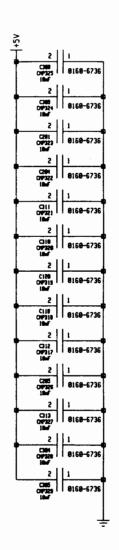

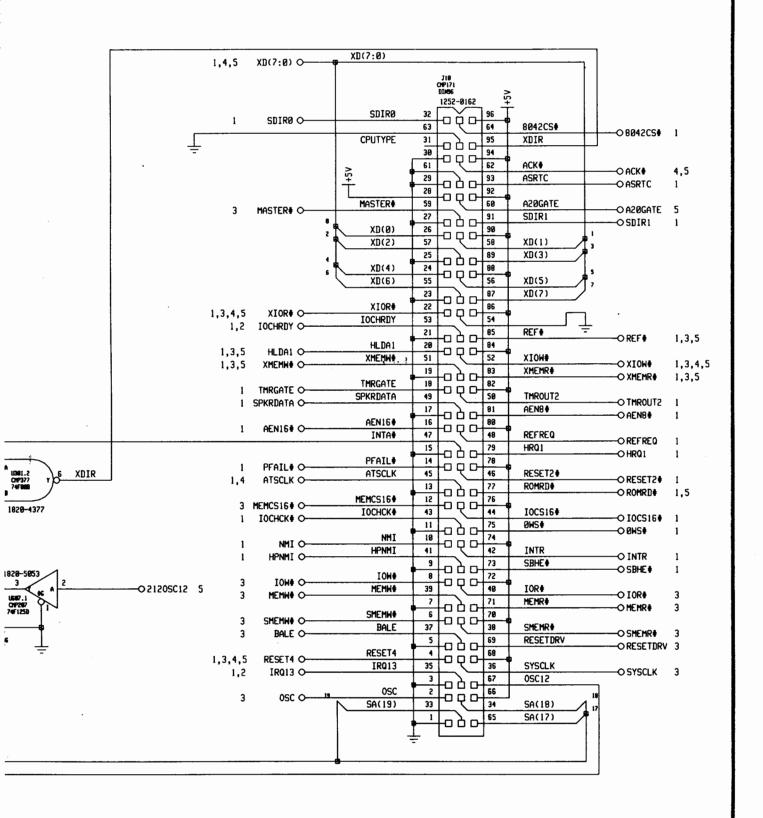

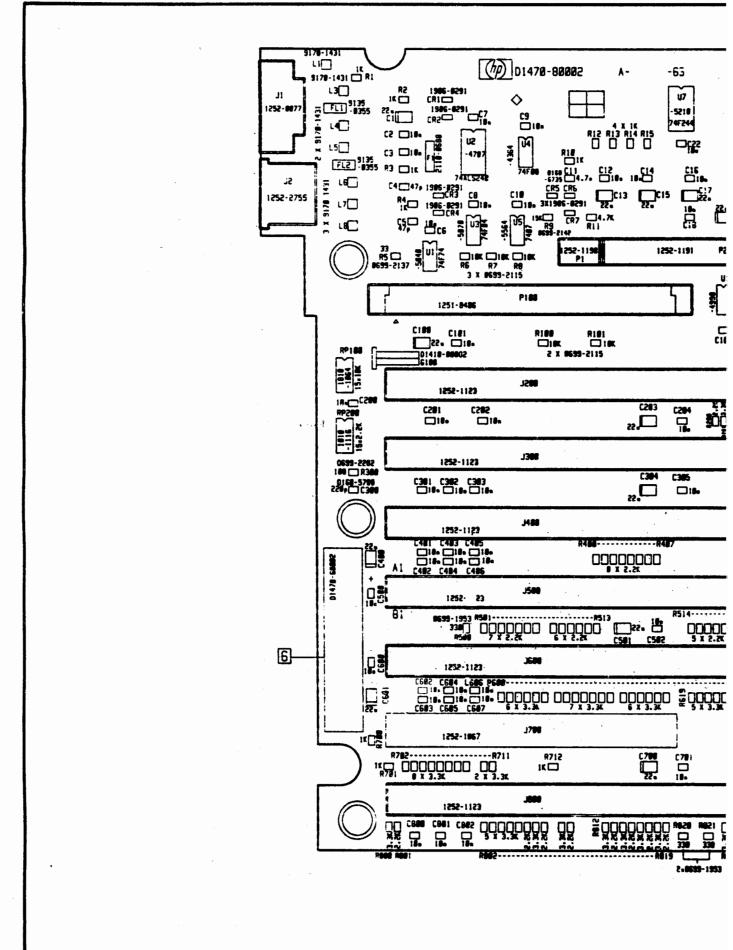

Below is a list of the major QS/16 & QS/20 Processor/Memory PCA components. Figure 2-1 shows their layout. Figure 2-2 is a block diagram of the QS/16 & QS/20 Processor/Memory PCA.

Major QS/16 & QS/20 Processor/Memory PCA Components:

| Component:                           | Quantity: | QS/16:          | QS/20:          |

|--------------------------------------|-----------|-----------------|-----------------|

| Microprocessor                       | 1         | 80386 @ 16 MHz  | 80386 @ 20 MHz  |

| Bus controller                       | 1         | 82C301 @ 16 MHz | 82C301 @ 20 MHz |

| Page memory controller               | 1         | 82C302 @ 16 MHz | 82C302 @ 20 MHz |

| High address buffer                  | 1         | 82A303          | 82A303          |

| Low address buffer                   | 1         | 82A304          | 82A304          |

| Data buffers                         | 2         | 82A305          | 82B305          |

| Control buffer                       | 1         | 82A306          | 82A306          |

| Backplane clock, OSC1                | 1         | 16 MHz          | 16 MHz          |

| Processor clock, OSC2                | 1         | 32 MHz          | 40 MHz          |

| Coprocessor clock, OSC3              | 1         | 32 MHz          | 32 MHz          |

| System clock, OSC4                   | 1         | 14.318  MHz     | 14.318  MHz     |

| Single in-line memory modules        | -         | 100 ns          | 80 ns           |

| Sockets for single in-line memory    | 8.        |                 |                 |

| module                               |           |                 |                 |

| Connector slot for memory extension  | 1         |                 |                 |

| PCA (the PCA has 8 sockets for       |           |                 |                 |

| single in-line memory modules)       |           |                 |                 |

| Dip switch bank for configuration    | 1         |                 |                 |

| 2-connector slot to System Interface | 1         |                 |                 |

| PCA                                  |           |                 |                 |

| Socket for 80387 coprocessor         | 1         |                 |                 |

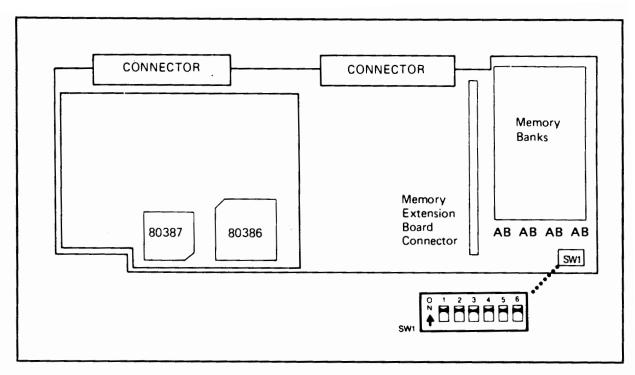

Figure 2-1. QS/16 & QS/20 Processor/Memory PCA Component Layout

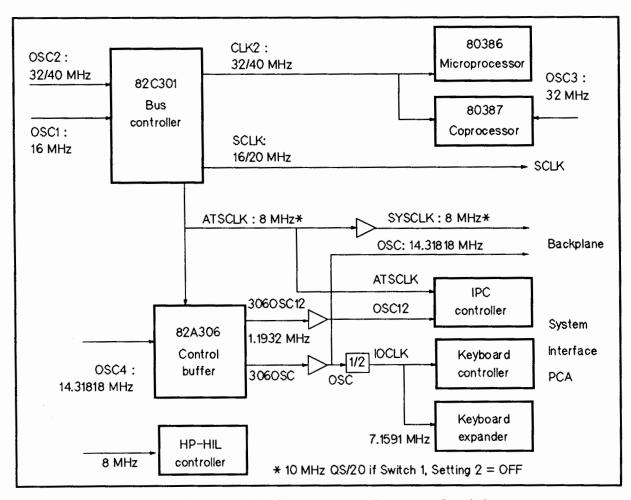

Figure 2-2. QS/16 & QS/20 Processor/Memory PCA Block Diagram

## 2.2 SYSTEM CLOCKS

The system's main oscillators, located on the QS/16 & QS/20 Processor/Memory PCA, generate the various system clock signals and are discussed under the components for which they provide clocking. (Other oscillators are part of a particular chip or family of chips and are described in the sections covering these chips.)

Oscillator 1 provides 16 MHz for the 82C301 bus controller's ATCLK1. (For further information, see the "Bus Controller" section in this chapter.)

Oscillator 2 provides 32 MHz (QS/16) or 40 MHz (QS/20) for the 82C301 bus controller's CLK2IN. (For further information, see the "Bus Controller" section in this chapter.)

Oscillator 3 is a 32-MHz oscillator which provides clocking for the 80387 coprocessor's asynchronous mode. (For further information, see the "Coprocessor" section in this chapter.)

Oscillator 4 provides 14.318 MHz to the 82A306 control buffer. (For further information, see the "Control Buffer" section in this chapter.)

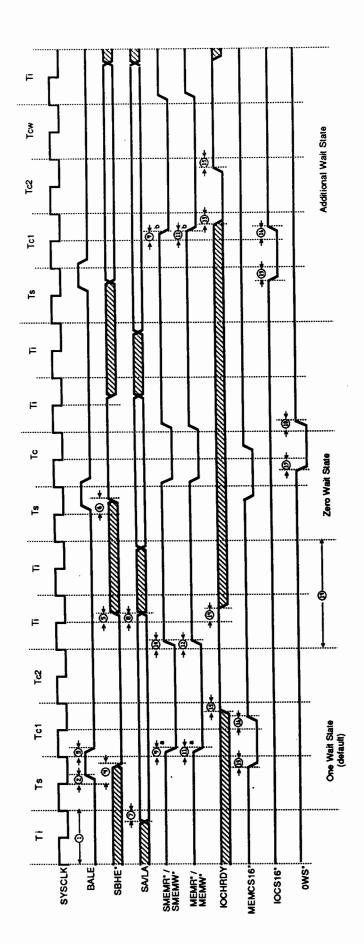

Figure 2-3. QS/16 & QS/20 Processor/Memory PCA Timing

#### 2.3 MICROPROCESSOR

The HP Vectra QS/16 and QS/20 uses the 80386 microprocessor as the central processing unit. It provides the following:

- 4-gigabyte physical memory capacity

- 32-bit registers

- comprehensive instruction set

- downward compatibility with the 8088, 8086 and 80286 microprocessors

- interrupt support capabilities

- processing modes: protected, real-address, and virtual 8086 mode

- separate 32-bit address and data paths

- support for 8-, 16-, and 32-bit data types

#### Microprocessor Clocking

The HP Vectra QS/16 uses a 16-MHz 80386, which is driven by a 32-MHz clock (OSC2). The HP Vectra QS/20 uses a 20-MHz 80386, which is driven by a 40-MHz clock (OSC2).

OSC2 provides the CLK2 clock signal (32 or 40 MHz) for the 82C301 bus controller. In turn, the bus controller provides the 386CLK2 signal (32 or 40 MHz) for the 80386 microprocessor. The 80386 internally divides the 386CLK2 signal to 16 MHz or 20 MHz. (For more information, see the "Bus Controller" section in this chapter.)

#### Microprocessor Compatibility

By dynamically sizing data, the 80386 microprocessor maintains hardware compatibility with the 8088, 8086 and the 80286 microprocessors. The 80386 microprocessor also maintains software compatibility, in that it runs industry-standard operating systems (including MS-DOS 3.2, MS-DOS 3.3, Microsoft OS/2, and Windows 2.0) and application software developed for systems based on 8088, 8086, or 80286 microprocessors.

#### Microprocessor Operating Modes

The 80386 microprocessor offers the following operating modes:

#### 1. Real-Address Operating Mode

The 80386 microprocessor's real-address operating mode is entered when the SPU is powered up or a system reset occurs. This operating mode addresses up to 1 Mbyte of system memory and allows 32-bit operands, but does not provide memory protection.

Windows 2.0, all versions of MS-DOS, as well as nearly all industry-standard application software, run in the real-address operating mode.

The real-address operating mode is compatible with operating systems written for the 8086 microprocessor. With a few differences (described in the HP Vectra System BIOS Technical Reference Manual for the HP Vectra Series of Personal Computers), the 80386's real-address object code is compatible with the real-address object code of the 8088, 8086, and 80286 microprocessors.

#### 2. Protected Operating Mode

The 80386 microprocessor's protected operating mode provides addressing beyond 1 Mbyte, with up to 4 gigabytes of physical memory available, and supports programs that use memory above 1 Mbyte (VDisk and Disc Cache, for instance).

When the 80386 microprocessor is in the protected operating mode, its object code is compatible with that of the 80286 in protected operating mode, but not with an 80286 in the real-address operating mode. In addition, if the 80386 is in the protected operating mode, its object code is compatible with that of the 8088 or 8086 microprocessor.

#### 3. Virtual-Address Operating Mode

The virtual-address operating mode allows multiple 8086 sessions of 1 Mbyte each and can provide access up to 64 terabytes of virtual memory addresses. This mode supports 8088 and 8086 applications that run as a subset of the 80386 microprocessor's protected operating mode.

In the virtual-address operating mode, the 80386 microprocessor's software and operating systems are compatible with those written for the 8088 and 8086 microprocessors.

For more information on the 80386 microprocessor, refer to the *Intel 80386 Hardware Reference Manual*.

#### 2.3.1 I/O Address Map

Appendix A gives the I/O address map for the central processing unit. The HP Vectra QS PC uses the first 1024 I/O hex addresses, 0000 through 03FF.

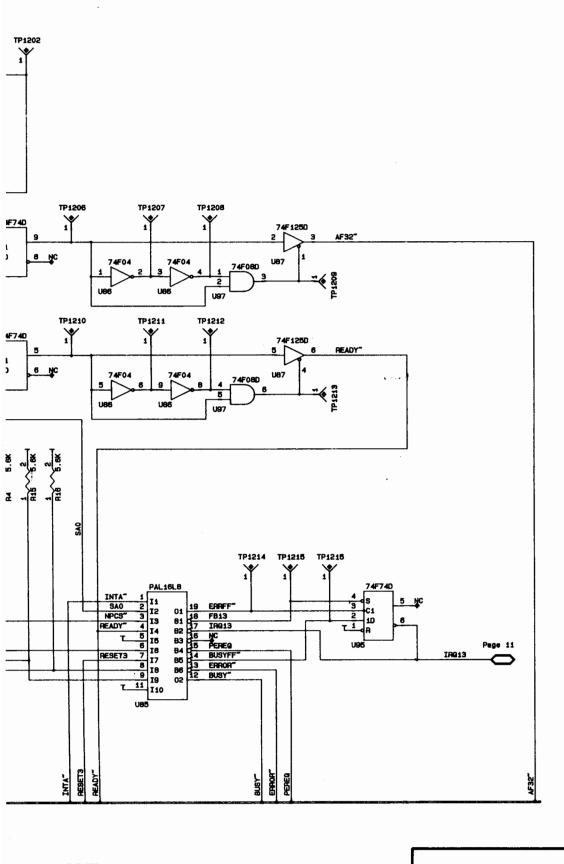

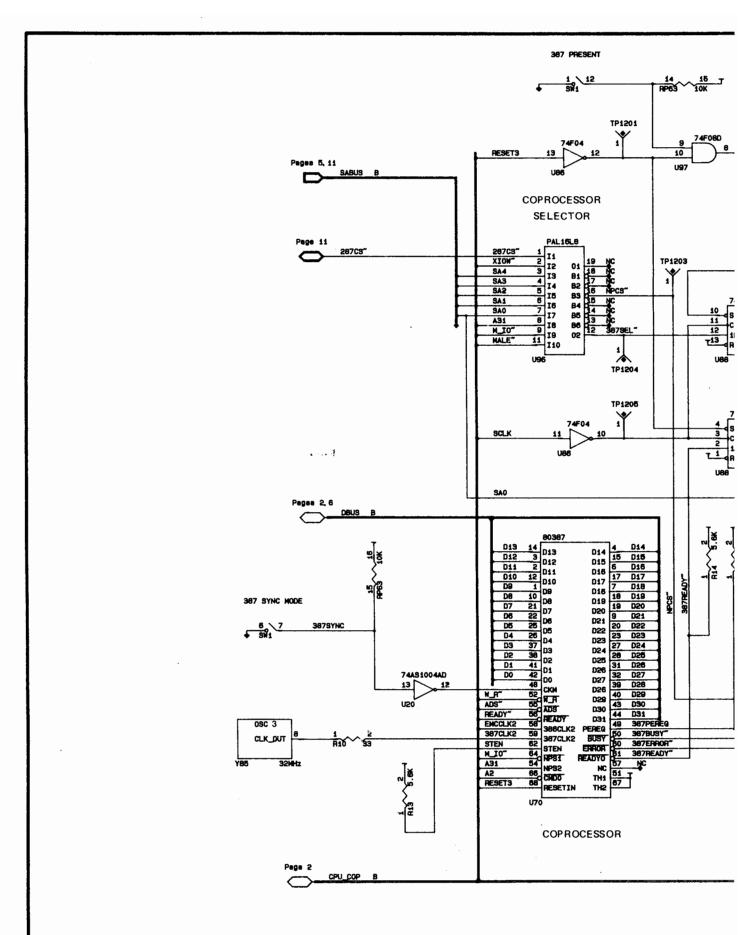

#### 2.4 COPROCESSOR

The HP Vectra QS PC does not come standard with the coprocessor, but it does provide supporting software and an extended math coprocessor socket in which the coprocessor can be installed.

The industry-standard coprocessor (80387) is a numeric processing unit which significantly improves performance of spreadsheets, CAD/CAE/CAM, engineering, and scientific applications. (Only applications with built-in support for the 80387 will realize these performance improvements.)

The coprocessor interfaces directly with the 80386; it extends the 80386 instruction set by providing hardware for BCD data and the high-precision integer functions and floating-point calculations otherwise performed by software.

If the 80387 coprocessor is installed, setting 1 of Switch 1 on the Processor/Memory PCA's should be set to the OFF position in order to connect it.

(Note that a Weitek floating point accelerator cannot be used.)

#### Coprocessor Clocking

The 80387 coprocessor can be operated in either the synchronous or the asynchronous mode. (It is recommended that synchronous mode only is used.)

If the Processor/Memory PCA's Switch 1, setting 6, is set to its default ON position, the 80387 operates in the synchronous mode, using the same clock as the 80386 microprocessor.

If Switch 1, setting 6, is set to the OFF position, the 80387 operates asynchronously, using a clock signal from the 32 MHz (OSC3) clock.

#### Coprocessor Hardware Interface and Compatibility

#### 1. Hardware Interface

If an 80387 coprocessor is installed, setting 1 of Switch 1 should be set to OFF to enable it.

Immediately after a system power-up or reset, the 80387 indicates its presence to the 80386 microprocessor by sending it an ERROR# control signal. (The # symbol at the end of the 80386 signal names is used by Intel to indicate that the active or asserted state occurs when the signal is at a low-voltage level.)

This causes the 80386 to set the Extension Type (ET) bit in its Control Register 0.

The 80387 coprocessor is directly connected to the 80386 microprocessor via the local address and data bus. Three control signals (BUSY#, PEREQ and ERROR#) synchronize the transfer of instructions and data between the 80386 and the 80387. When the 80386 selects the 80387, it asserts I/O address bit A31 so that the 80387 acts as an I/O device in a reserved I/O space.

#### 2. Compatibility

The HP Vectra QS PC numeric coprocessor interface supports the 80387 coprocessor. The 80387 coprocessor supports 8087 and 80287 coprocessor instruction sets.

#### Coprocessor Operating Modes

Since all memory accesses are handled by the 80386 microprocessor, the 80387 works the same whether the 80386 is executing in the real-address, the protected, or the virtual-address operating mode. (For further information on the 80387 coprocessor, refer to Intel reference manuals.)

For further information, refer to the Intel reference manuals.

#### 2.5 MEMORY

All "A", "B", "C" and "D" sockets \*\*

All "A" and "B" sockets

All 16 sockets \*\*

In all "A" and "B" sockets

in all "C" and "D" sockets \*\*

#### 2.5.1 Main Memory (RAM)

The HP Vectra QS PC main memory (also known as system memory, or system RAM, or RAM) consists of dynamic RAM chips mounted on single in-line memory modules.

The modules are available in 256-Kbyte or 1-Mbyte modules and fit into sockets. Eight sockets are available on the Processor/Memory PCA (arranged in banks "A" and "B"). An additional eight sockets are available on a plug-in Memory Extension card, arranged in banks "C" and "D". (See the figure in this chapter, "Processor/Memory PCA Component Layout" to locate the banks of sockets.)

#### Main Memory Configurations

This memory is expandable to 16 Mbyte by placing even increments of modules in the sockets, as shown in Table 2-1.

For Total DRAM of: Type of Modules Needed: Sockets Used: 4 256-Kbyte 1 Mbyte All "A" sockets 2 Mbytes 8 256-Kbyte All "A" and "B" sockets 4 Mbytes 4 1-Mbyte All "A" sockets

Table 2-1. QS/16 & QS/20 Main Memory Expansion

#### Notes:

4 Mbytes \*

8 Mbytes

10 Mbytes

16 Mbytes

16 265-Kbyte

8 1-Mbyte

8 256-Kbyte

16 1-Mbyte

and 8 1-MByte

<sup>(\*)</sup> For improved system performance, it is recommended that 16 256-Kbyte modules are used. (This allows the memory controller to use interleaving mode.)

<sup>(\*\*)</sup> These configurations require the plug-in Memory Extension card.

#### **Base RAM Configurations**

The Processor/Memory PCA's Switch 1, setting 3, can be used to configure the main memory base RAM as required by applications used.

In the ON position, the main memory's base RAM is set to 640 Kbytes; in the OFF position, base RAM is set to 512 Kbytes.

#### **Main Memory Architecture**

The HP Vectra QS has a paged/interleaved main memory architecture, using a 82C302 page/interleave memory controller that organizes main memory DRAM to decrease the number of accesses that incur a wait state penalty.

Paged DRAM is organized into paged rows and columns. One memory strobe (the RAS, or row address strobe) generates the row address (or the page address); a second memory strobe (the CAS, or column address strobe) generates the column address.

If access is required on the same page of DRAM, there may be zero wait states as the row address is already strobed (only CAS is generated). But if access is required on a different page of DRAM, there is at least one wait state.

Interleaved DRAM is organized into four banks, with each bank having four single in-line memory module sockets. When only the "A" bank of four sockets is filled, the system operates in the non-interleaved mode. Because interleaving is done between pairs of banks, for the system to operate in the paged/interleaved mode, either two or four (never three) banks of sockets must be filled. (For more information, see the "Page Memory Controller" section in this chapter.)

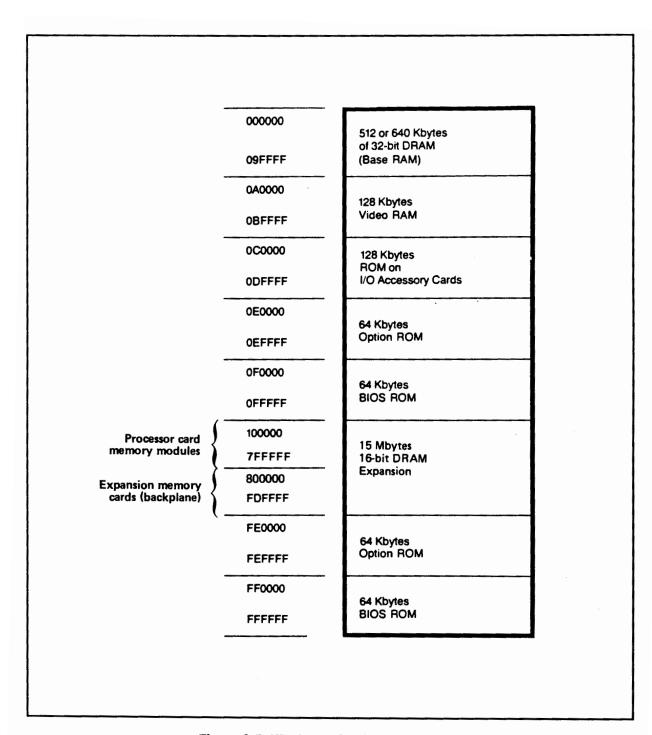

#### **Memory Map**

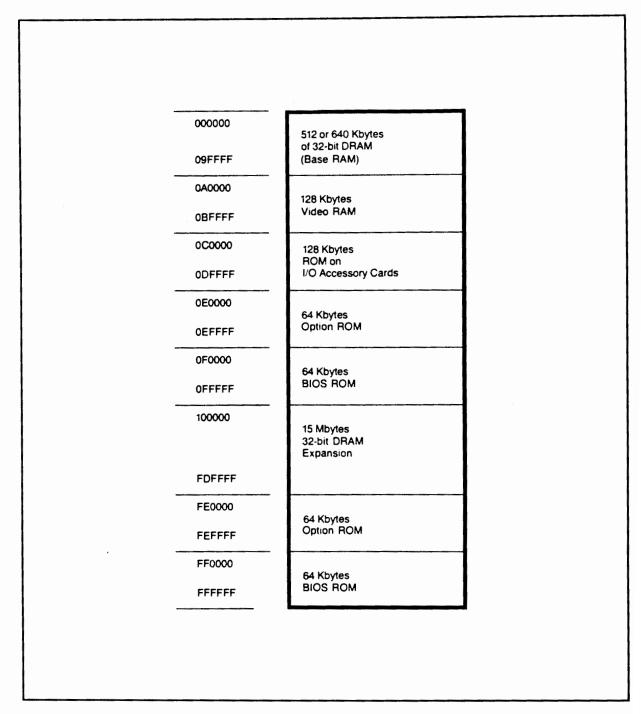

Figure 2-4 gives the HP Vectra QS PC memory map. As with industry-standard products, the first 1 Mbyte of main memory is reserved for standard memory.

The base RAM (either the first 512 Kbytes or 640 Kbytes of main memory, depending on how the RAM is configured, using Switch 1 setting 3) is used for MS-DOS applications.

From hex address 0A0000 to 0FFFFF, the system reserves main memory for video RAM, I/O adapters, option ROM, and BIOS ROM.

Main memory from hex address 100000 to FDFFFF is reserved for 32-bit dynamic expansion using the serial in-line memory modules.

Upon power-up, the 64 Kbytes of option ROM on the System Interface PCA at hex address 0E0000 to 0EFFFF are automatically mapped to hex address FE0000 to FEFFFF; similarly, the 64 Kbytes of BIOS ROM on the System Interface PCA at hex address 0F0000 to 0FFFFF are automatically mapped to hex address FF0000 to FFFFFF.

(If you have option ROMs, they are also mapped at hex address FFFE0000 to FFFEFFFF, and BIOS ROMs are also mapped at hex address FFFF0000 to FFFFFFFF. However, the upper eight bits of these addresses do not appear on the backplane I/O bus.)

Figure 2-4. HP Vectra QS PC Memory Map

#### **Main Memory Operation**

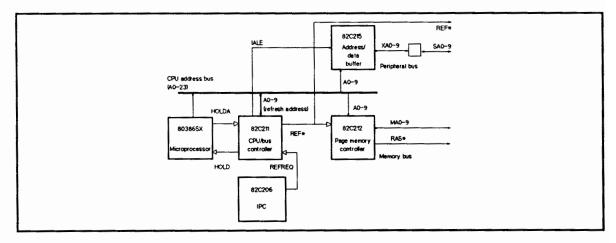

#### 1. Refresh

All DRAM is refreshed within 4 milliseconds (for 256-Kbyte DRAM) to 8 milliseconds (for 1 Mbyte DRAM). A refresh cycle for one bank of DRAM requires seven 386CLK2 cycles, with refreshes to additional banks staggered by one 386CLK2 cycle, so that four banks take ten 386CLK2 cycles to refresh.

A refresh cycle begins with the 82C206 IPC's (integrated peripheral controller on the System Interface PCA) OUT1 pin generating a refresh request (REFREQ) to the 82C301 bus controller every 15 microseconds.

To perform a refresh, the 82C301 bus controller generates a hold request (HOLD) to the 80386 microprocessor, which subsequently generates a hold acknowledge (HLDA) to the bus controller.

The bus controller then issues a refresh signal (REF\*) which goes to the 82C302 page memory controller, the 82A303 and 82A304 address buffers, and the backplane I/O.

- When the page memory controller receives the REF\* signal, it strobes the refresh row address into the banks of DRAM on the processor/memory card.

- When the address buffers receive the REF\* signal: The 82A303 high address buffer sets system address bus lines SA23 to SA12 low. A counter within the 82A304 low address buffer drives the system address bus lines SA11 to SA0, which represents the refresh row address for RAM on the backplane (for I/O accessory cards). Note that the AT standard uses SA0-7 for the refresh operation.

The REF\* signal goes to the backplane I/O and indicates to I/O accessory cards that a refresh operation is taking place.

In addition, an I/O accessory card can issue a REF\* signal to initiate a refresh request to the bus controller, the page memory controller, and the address buffers, independent of the IPC's periodic refresh requests (REFREQ).

#### 2. Access Time

The main memory for the HP Vectra QS uses DRAM with the following access and cycle time:

| PC:   | Access Time:    | Cycle Time:     |

|-------|-----------------|-----------------|

| QS/16 | 100 nanoseconds | 190 nanoseconds |

| QS/20 | 80 nanoseconds  | 165 nanoseconds |

(Hewlett-Packard assumes no responsibility for the access time of memory modules not supplied by an HP-approved vendor.)

(\*)Active low.

#### 3. Parity

DRAM uses eight data bits and one parity bit.

Parity is generated for each byte of DRAM during write operations, and checked during read operations.

If a parity error occurs, a parity check signal LPAR\* is generated by the 82C306 control buffer and sent to the 82C301 bus controller. (LPAR\* is also sent to the page memory controller for diagnostic purposes.)

If parity error detection is enabled, the bus controller generates a non-maskable interrupt (NMI), which is sent to the 80386 microprocessor via the 8042 port expander. (For details, refer to the "Interrupt Controller" section in the "System Interface PCA" chapter.) This operates as follows.

For memory write operations, the parity is controlled through an external parity generation circuit:

The data goes through the data buffers, which generate low and high parity bits (PL0-PL3 and PH0-PH3), representing the parity of the lower and upper nibbles (4 bits) of each byte written.

PL0-PL3 and PH0-PH3 are exclusive ORed together to form memory parity bits MP0-MP3, representing the parity for byte 0 to 3 for the data being written.

MP0-MP3 are then written into the proper parity bits in the DRAM banks (the MP0-MP3 inputs to the control control buffer are ignored during the write operation). These bits are used to check parity during read operations.

For memory read operations, the parity is checked by the control buffer:

The data from the DRAM is read into the data buffer, which produces parity bits PL0-PL3 and PH0-PH3. These parity bits go to the 82A306 control buffer.

MP0-MP3 (which represent the parity as determined when the data was written) are also read from DRAM and are sent to the control buffer. MP0-MP3 are compared with PL0-PL3 and PH0-PH3, the parity found when data is read back.

The control buffer then produces a parity output signal, LPAR\*, which is active if a parity error exists. LPAR\* is sent to the bus controller and page memory controller. (The failing address is latched within the page controller for diagnostic purposes.)

#### 4. Self-tests

Upon power-up, the main memory goes through a self-test, as discussed in the HP Vectra System BIOS Technical Reference Manual for the HP Vectra Series of Personal Computers.

#### 2.5.2 Read-Only Memory

The System Interface PCA provides two 32-Kbyte ROM chips (containing the BIOS firmware) and sockets for two 32-Kbyte option ROM chips. (See the "System Interface PCA" chapter for more information on ROM.)

(\*)Active low.

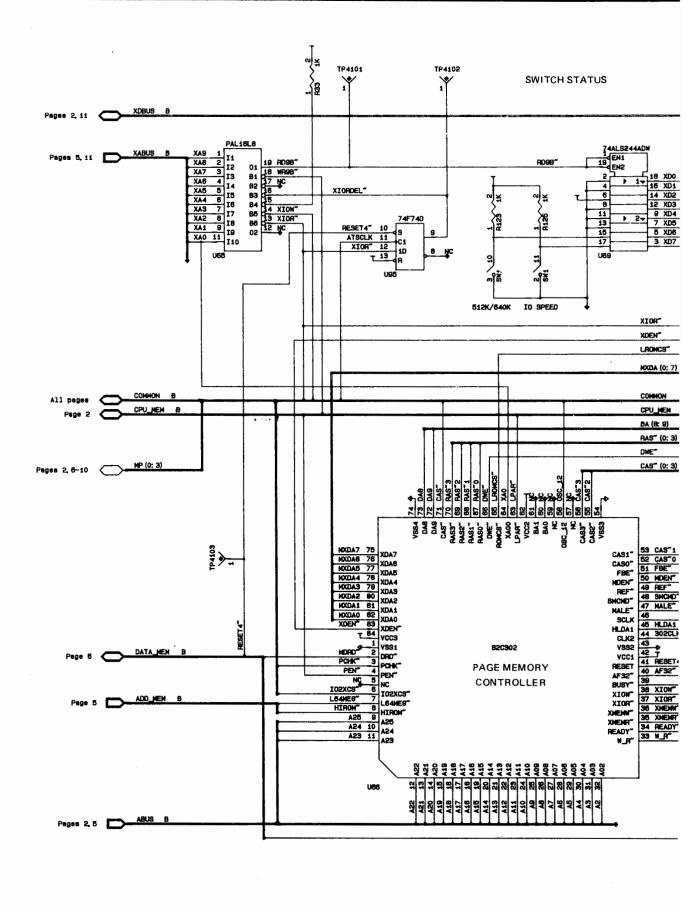

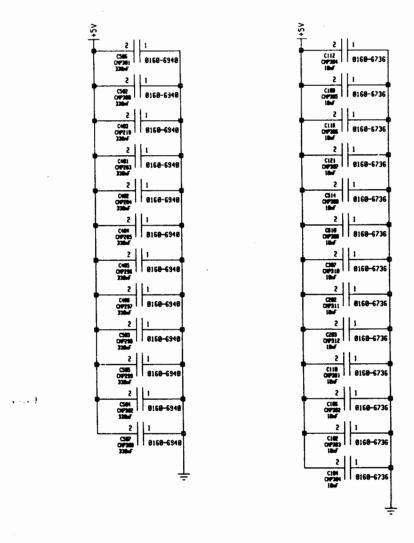

### 2.6 PAGE MEMORY CONTROLLER

The 82C302 page memory controller:

- Controls all main memory accesses from the 80386 microprocessor, direct memory access refresh requests, and

- Organizes the main memory DRAM into paged and interleaved DRAM to decrease the number of accesses incurring a wait state penalty.

Clocking for the page memory controller comes from the signal 302CLK2, which originated from the 82C301 bus controller.

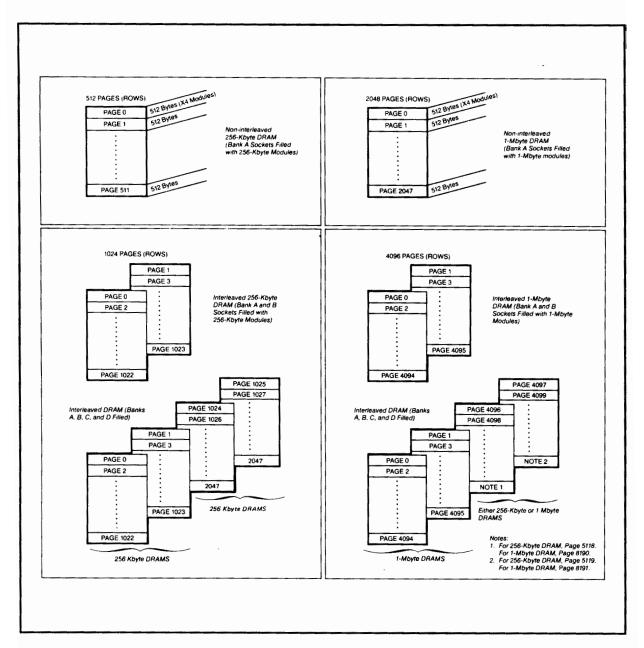

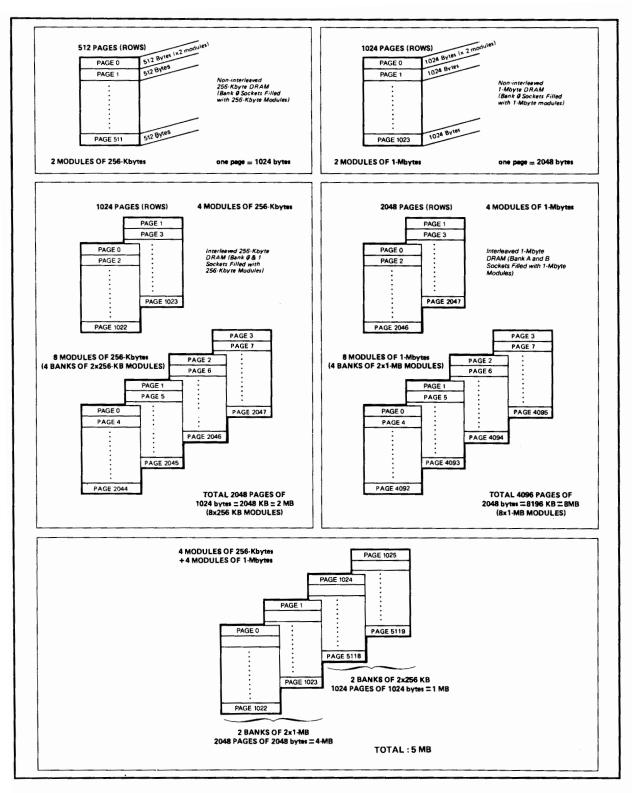

DRAM chips are physically organized onto single in-line memory modules, which can make up to four 4-byte wide banks: banks A, B, C, and D. If four 256-Kbyte modules are used, a bank has 1 Mbyte of DRAM; if four 1-Mbyte modules are used, a bank has 4 Mbytes of DRAM. (Refer to the "Main Memory" section and the "Main Memory Expansion" table in this chapter for more information on the physical organization of the DRAM.)

The page memory controller logically organizes DRAM as pages. For each 256-Kbyte module, there are 512 pages (rows), with each page having 512 bytes (1 byte for each 512 columns). Since a bank has 4 single in-line memory modules, a banked page has 2 Kbytes of dynamic RAM (i.e. 512 bytes x 4 modules = 2 Kbytes). This paged memory can be accessed as 8-bit bytes, 16-bit words, or 32-bit words.

To access memory, the page memory controller issues to each accessed module a row address and then a column address. The row address indicates the page, while the column address indicates which of the 512 bytes on that page (row) are to be accessed.

The row and column addresses are multiplexed over MA0-MA7 and DA8-DA9 from the page memory controller and are latched into a memory module by the appropriate row address strobe (RAS) and column address strobe (CAS) signals.

To achieve 8-bit, 16-bit, or 32-bit operations, the CAS signal is ANDed with the appropriate latch byte enable (LBE) signal from the 82A306 control buffer. If the next access is within the current page (row), a new row address does not need to be issued, just a new column address and CAS signal, resulting in fewer wait states.

If more than one bank of sockets are filled with DRAM modules, the page memory controller interleaves the pages between banks, with even pages on one bank, and odd pages on the next bank. Interleaving requires that two or four (but never three) banks of sockets be filled with DRAM modules. If more than one bank of sockets is to be filled, the two banks making up a pair of banks must each use the same type of modules, but two pairs can use different types of modules.

Interleaving pages on different banks can minimize the number of row addresses and RAS signals required, as the page memory controller has a separate page register for each bank. If bank "A" has an even page number as its current page, and bank "B" has the next (odd) page number as its current page, no new row addresses or RAS signals are needed as long as accesses are within these two pages.

Once the 80386 microprocessor generates a local address, the page memory controller decodes the type of access according to its various configuration registers. These registers determine if a ROM access, an access of the backplane I/O, or a DRAM access is required. If a DRAM access is required, the page memory controller accesses the DRAM according to configuration registers that state what type of DRAMs are used and how many wait states are desired.

In direct-memory accesses (DMA), only 8-bit and 16-bit operations are supported. The address on the local address bus comes from the System Interface PCA's 82C206 Integrated Peripheral Controller via the peripheral address bus and the address buffers. The page memory controller decodes the address as it would an access from the 80386 microprocessor.

A refresh access is initiated when the page memory controller receives a REF\* input from the 82C301 bus controller. The refresh row address is strobed into each bank with an offset of one 386CLK2 cycle between strobes. (For more information on the 82C302 page/interleave memory controller, consult the Chips and Technologies data sheet, CS8230: AT/386 CHIPSet.)

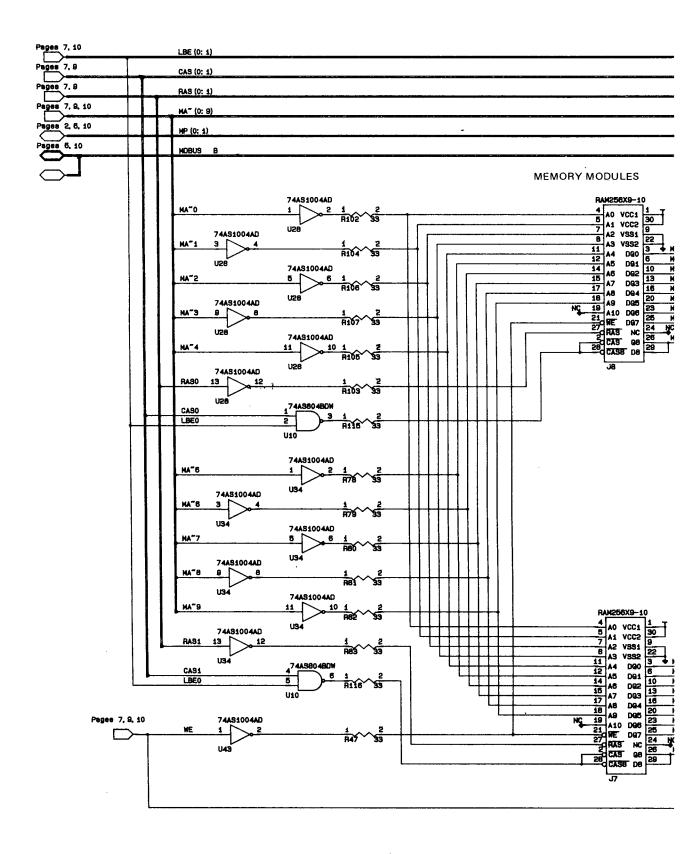

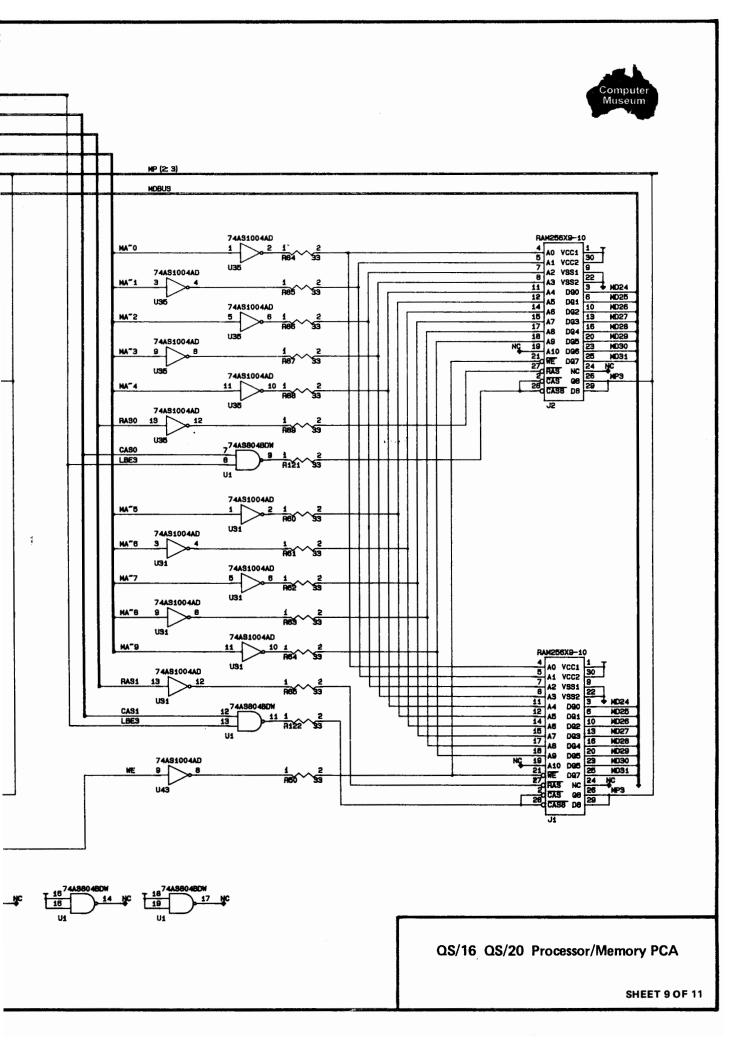

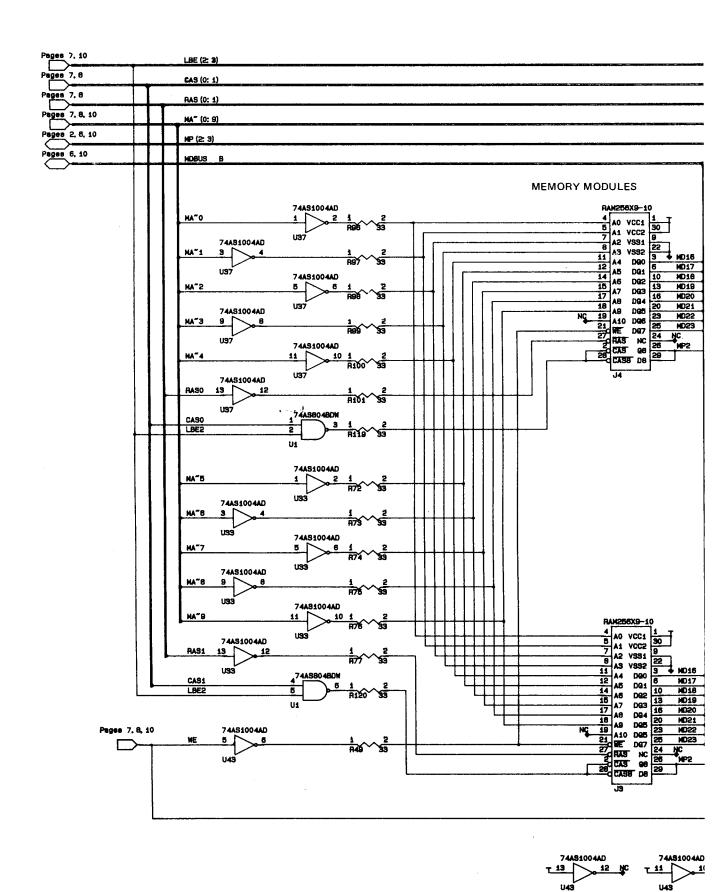

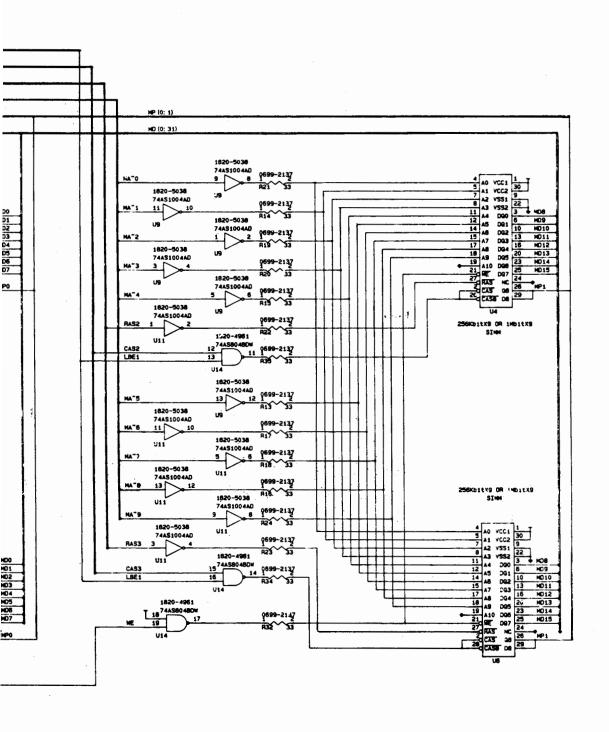

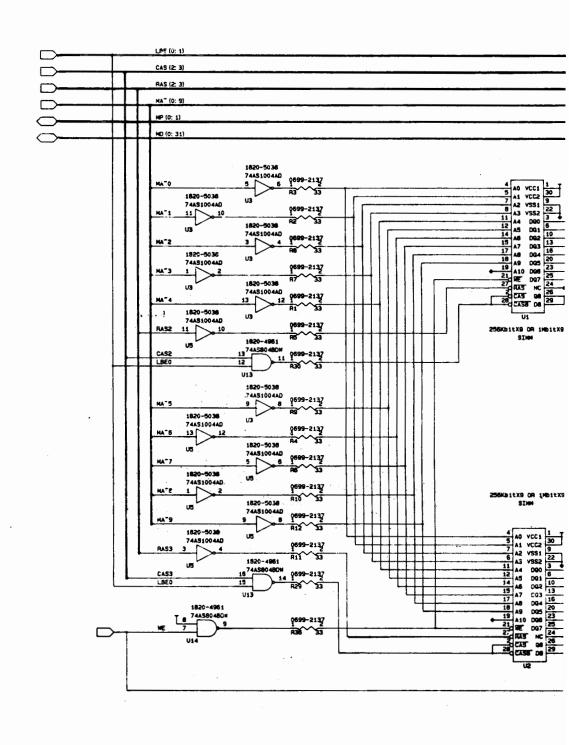

Figure 2-5. QS/16 & QS/20 Physical Organization of DRAM (Board/Memory Modules View)

<sup>\*</sup> Active low

Figure 2-6. Logical Organization of DRAM

# 2.7 BUS CONTROLLER

The 82C301 bus controller works in conjunction with the 82A306 control buffer to generate clocking for the 80386 microprocessor, the coprocessor, and the page memory controller. The bus controller also provides the generation and synchronization of control signals for all buses. In addition, it offers an industry-standard Port B status register, and optional speeds for timing-dependent software. (For more information, refer to Chips and Technologies Reference Manuals.)

# **Bus Controller Clocking**

The clock input to the bus controller is provided by ATCLK1 (OSC1, 16 MHz) and CLK2IN (OSC2: 32 MHz on QS/16, 40 MHz on QS/20).

The CLK2 output from the bus controller (to the microprocessor [386CLK2], coprocessor [EMCCLK2], and page memory controller [302CLK2]) is derived from OSC2, and is either 32 MHz (QS/16) or 40 MHz (QS/20). Simultaneously pressing CTRL (Alt) (C) causes CLK2 to be derived from OSC1, for a 16-MHz signal.

The bus controller's SCLK output signal, used in various timing circuits on the Processor/Memory PCA, is equal to one-half the CLK2 signal.

The bus controller's ATSCLK output signal is provided to the 82A306 control buffer and buffered to drive the clock signal SYSCLK, the signal for the industry-standard backplane I/O bus. In addition, ATSCLK is sent to the 82C306 Integrated Peripheral Controller.

Through software control, ATSCLK's frequency can be selected as:

- 1. Synchronous with CLK2 from OSC2 (that is, CLK2÷4; namely, 8 MHz on the QS/16 and 10 MHz on the QS/20) default QS/16.

- 2. Or, ATCLK1÷2 (from OSC1); that is, 8 MHz default QS/20.

For more information, refer to Chips and Technologies Reference Manuals.

#### **Bus Arbitration**

The bus controller synchronizes control of all bus activities. For direct memory accesses (DMA), the bus controller accesses memory as described in the "DMA Controller" section of Chapter 3. The bus controller has the following two state machines that control access to devices by the 80386 microprocessor:

- 1. The local bus state machine, controls accesses by the 80386 to devices on the local bus. It also supports 32-bit transfers between the 80386 and system memory (or memory-mapped I/O), but does no data size conversions.

- 2. The AT (industry-standard) bus state machine, controls the 80386 microprocessor accesses to devices on non-local buses. It provides sequencing and timing controls (including wait state generation) for status and command phases of the different bus cycles. In addition, it generates action control code signals that go to the data buffers for data size conversions.

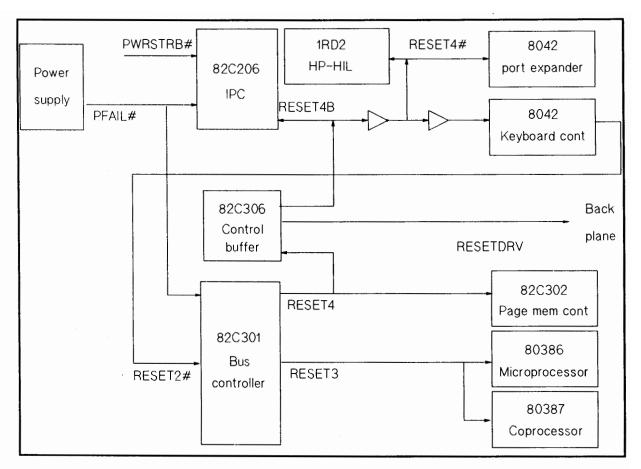

#### **Bus Controller Reset Control**

When the power supply's PFAIL signal goes high (detected at the bus controller's RESET1\* pin, see Chapter 5), it activates the bus controller's RESET3 and RESET4.

RESET3 Resets the 80386 microprocessor, the 80387 coprocessor and various

Processor/Memory PCA timing circuits.

RESET4 Provides the backplane I/O connector slots with a reset for input devices and

resets the following:

82C302 page memory controller

82C206 IPC (integrated peripheral controller)

8042 keyboard controller

8042 keyboard controller port expander

HP-HIL master controller (IRD2)

For more details on the PFAIL signal, refer to the chapter Power Supply.

Note that simultaneously pressing Ctrl Alt Del causes a soft reset - no reset lines are activated.

However, it is possible to reset the microprocessor by writing FEh to I/O address 64 (within the 8042 keyboard controller on the System Interface PCA). This activates RESET2\*, which in turn activates RESET 3. This is provided for compatibility with the AT 286 computers, as it is the only way to return from protected mode to real mode.

\* Active low

# 2.8 CONTROL BUFFER

The 82A306 control buffer receives a 14.318 MHz signal (OSC4), which is divided by 12 to generate a 1.19 MHz signal. This signal is sent to the 82C206 integrated peripheral controller's (on the System Interface PCA) timer 0, counter 1 and counter 2.

The control buffer also provides the byte-enable latch which, during memory cycles, holds valid the byte enables from the 80386 microprocessor.

The control buffer checks parity by generating read parity from the data buffer's partial parity bits. (Write parity is controlled through an external parity generation circuit.) Refer to "Main Memory (RAM)" in this chapter.

In addition, the control buffer provides drivers for control signals on the backplane I/O. Furthermore, the 82A306 control buffer generates some of the signals used by the 82C301 bus controller to control bus accesses.

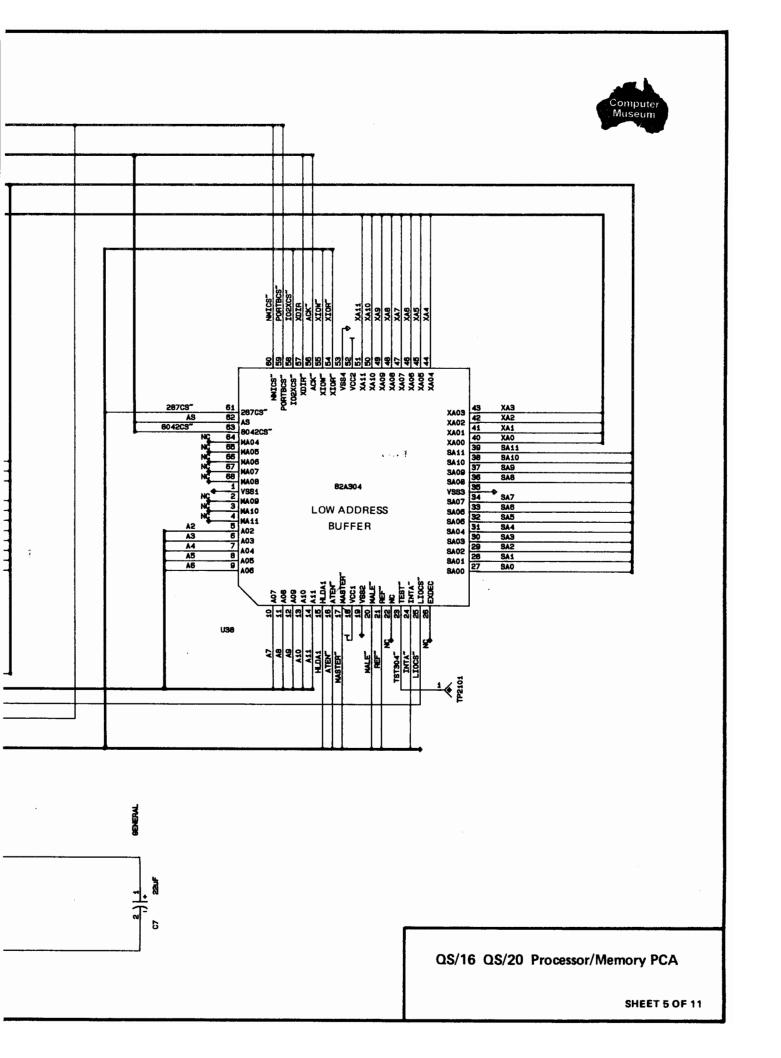

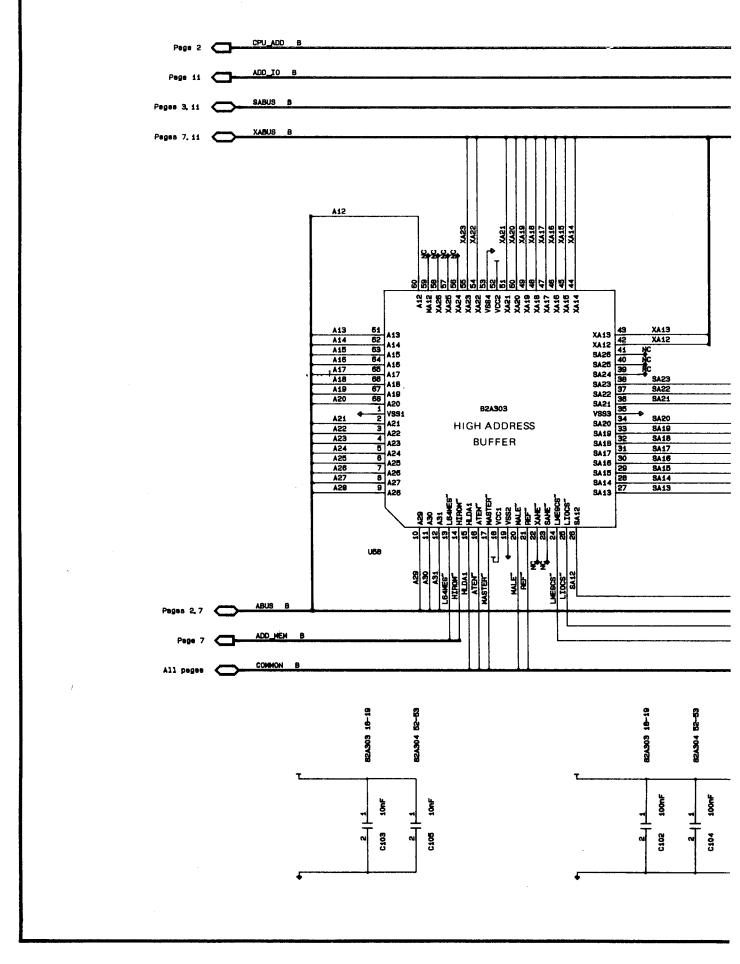

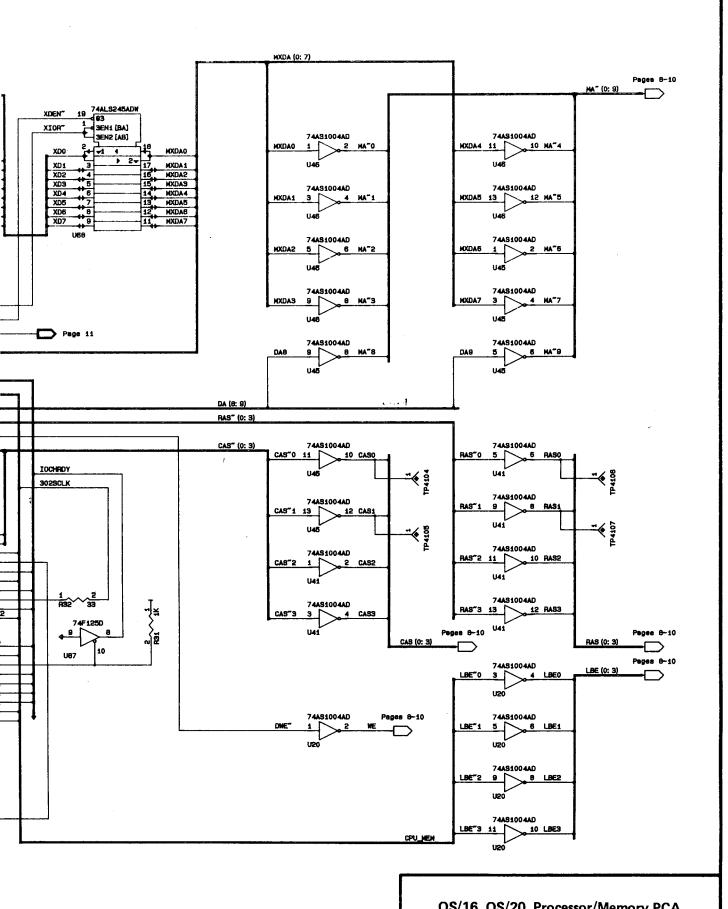

# 2.9 ADDRESS BUFFERS

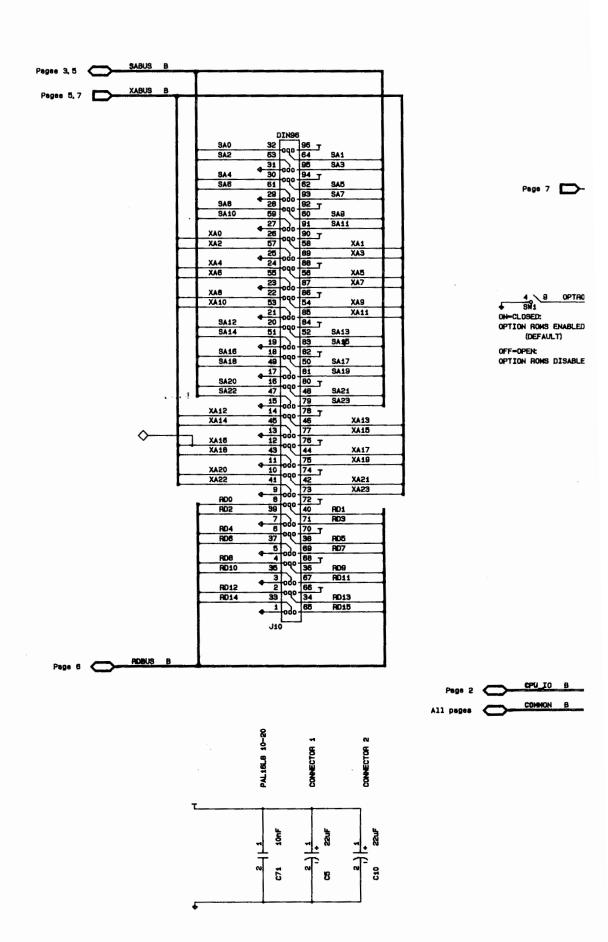

The address buffer for the HP Vectra QS PC comprises an 82A303 high address buffer and an 82A304 low address buffer. They support transfers on the following buses:

- A, the local address bus to the 80386 microprocessor and the coprocessor

- SA, the system address bus for the backplane I/O

- XA, the peripheral address bus for the keyboard controller 8042 keyboard controller port expander, HP-HIL Controller (IRD2), and 82C206 IPC (integrated peripheral controller).

The 82A303 high address buffer acts as a buffer for local address bits A31 through A12, system address bits SA23 through SA12, and peripheral address bits XA23 through XA12.

The 82A304 low address buffer acts as a buffer for address bits A11 through A2, SA11 through SAO, and XA11 through XAO. (XAO and XA1 are generated by the 82C301 bus controller for use by the AT bus.)

The 82A303 high address buffer provides address decoding signals required by other chips, such as the 82C302 memory controller. The 82A304 low address buffer provides address decoding signals required by peripheral devices. In addition, the 82A304 low address buffer provides refresh address generation for the system address bus (see the "Main Memory Operation" section in this chapter).

The high and low address buffers buffer the interface between the A bus, the SA bus, and the XA bus, according to various control line states. Both the high and low address buffers directly interface to the industry-standard bus (the 24-bit XA bus and SA bus) via bidirectional drivers.

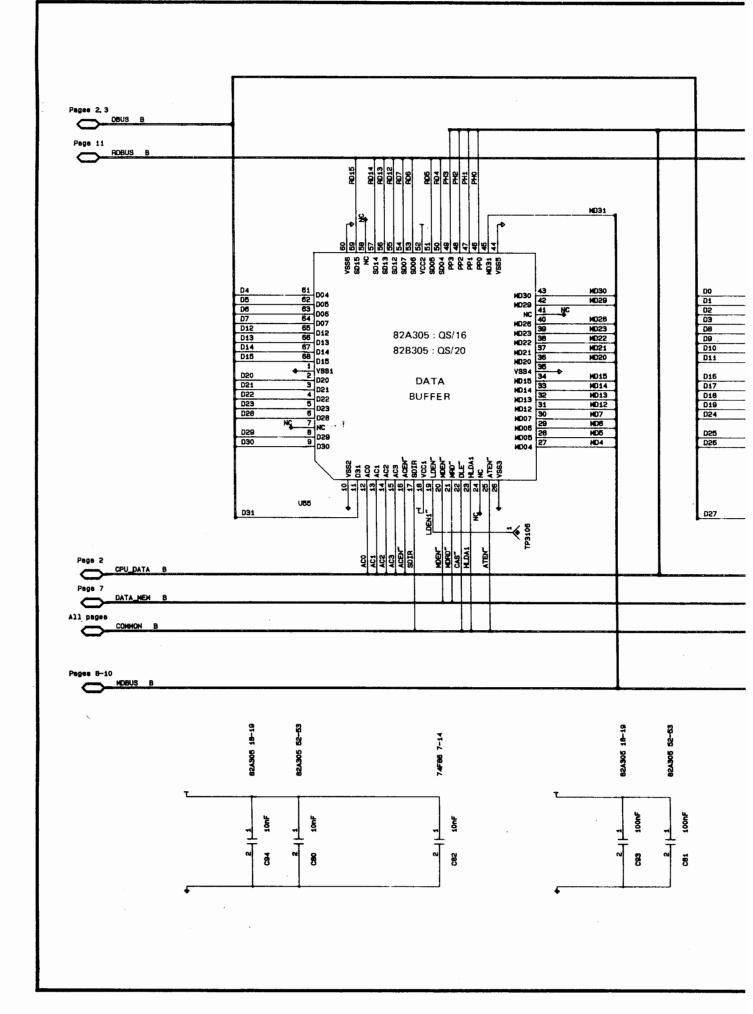

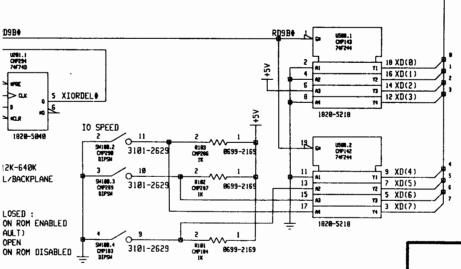

# 2.10 DATA BUFFERS

The data buffer for the HP Vectra QS PC consists of either two 82A305 data buffers (QS/16) or two 82B305 data buffers (QS/20). The data buffers support data transfers over the following buses:

- D, the local data bus to the 80386 microprocessor and the coprocessor

- MD, the system memory data bus to the dynamic RAM

- RD, the ROM data bus connected to the BIOS ROMs

- SD, the system data bus to the backplane I/O, connected to the RD by a transceiver

- XD, the peripheral data bus to the keyboard controller 8042 keyboard controller port expander, HP-HIL controller (IRD2) and the 82C206 IPC (on the System Interface PCA), connected to SD by a transceiver.

Via D and MD, the data buffers support data transfers between the 80386 microprocessor and the system RAM. Via D, RD and SD, the data buffers also support data transfers between the 80386 and the industry-standard backplane connector slots. During direct-memory accesses, the data buffers connect RD to both D and MD. In addition, the data buffers provide data bus connections that convert data words to a size compatible with backplane I/O operations.

#### Control of Data Bus Buffers

According to signals received from the bus controller and the page memory controller, the data buffers determine (1) which data buses are active (i.e. connected) and (2) the subsequent direction for data bus buffer drivers.

#### **Data Conversion**

The data buffer converts data to a size permitting the 80386 microprocessor to access the I/O bus. Data is converted via action code control signals from four bus controller lines to the data buffer; these codes control the connection of bus bits between (1)the system data bus for the backplane I/O and (2)either the local data bus or the memory data bus.

# 2.11 LOCAL BUS (LBUS)

The local bus consists of the local address bus (A), the local data bus (D), bus status pins, and bus control pins for the 80386 microprocessor (and the coprocessor, if installed). The local bus connects the 80386 microprocessor and the coprocessor to the rest of the system.

Separate from the local data bus, the local address bus generates 32-bit addresses. Its 30 address lines (A31 to A2) indicate a 4-byte location, from which the local address bus's four byte enable lines (BE3\* to BE0\*) select the bytes to be enabled. The 32 local data bus lines (D31 to D0) transfer either 8, 16, 24, or 32 bits of data. The local bus status lines (D/C\*, M/IO\*, W/R\* and LOCK\*) establish the type of bus cycle to be performed.

The 82C301 bus controller and the 82A306 control buffer use the local bus control pins to control the bus cycle on a cycle-by-cycle basis.

At the start of a local bus cycle, the 80386 microprocessor places on the local address bus (A) valid address signals which go to: (1)the address buffers and then to other buses and to (2)the 82C302 page memory controller, which interfaces with the DRAM, and (3)the coprocessor. Status signals corresponding to the bus cycle to take place are then sent to the 82C301 bus controller, the 82A306 control buffer, and the coprocessor. Data to/from the 80386 microprocessor are sent over the local data bus (D) to/from the data buffers.

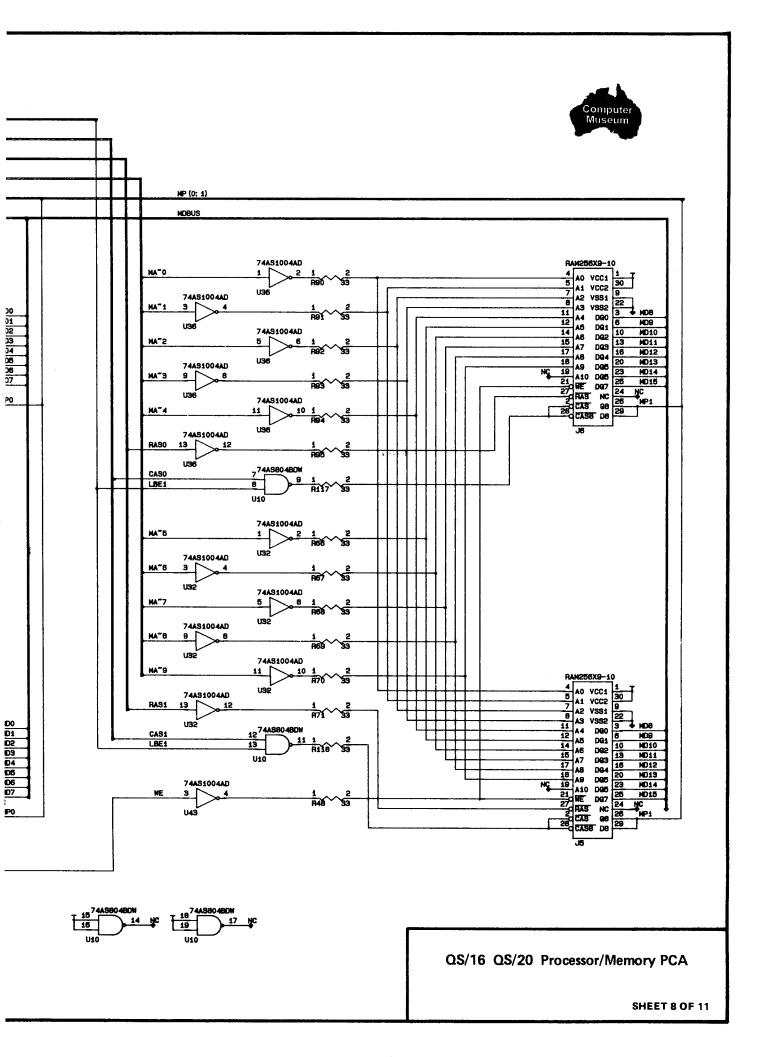

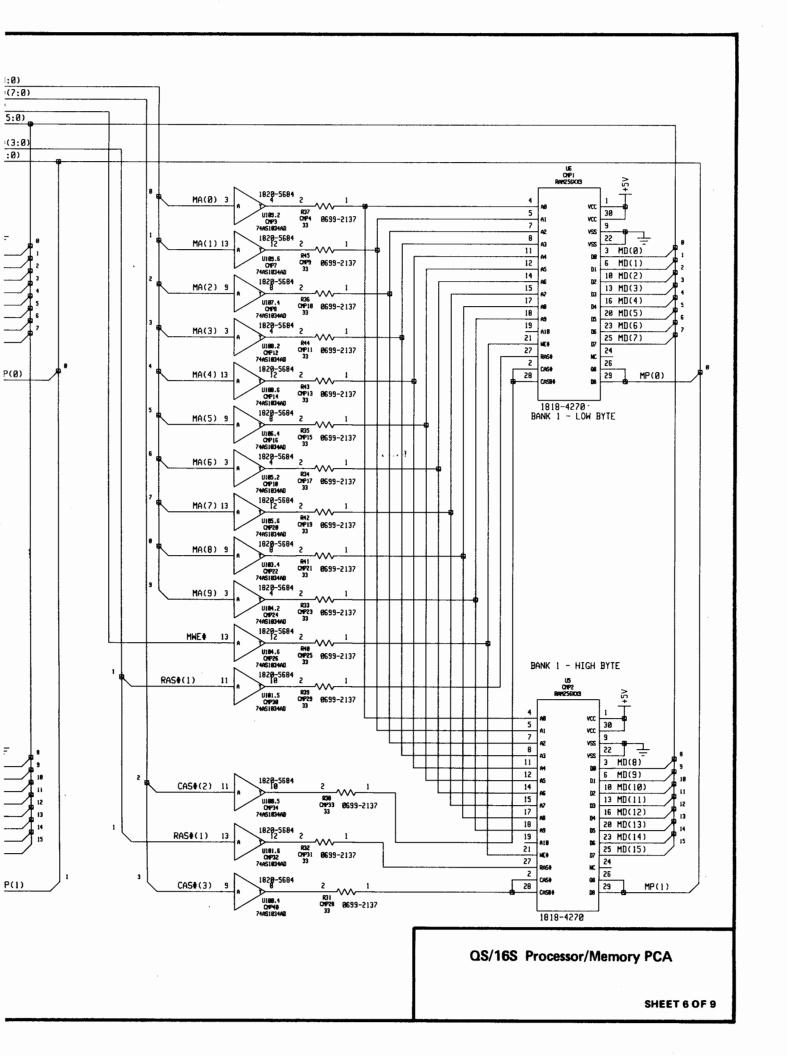

# 2.12 MEMORY BUS

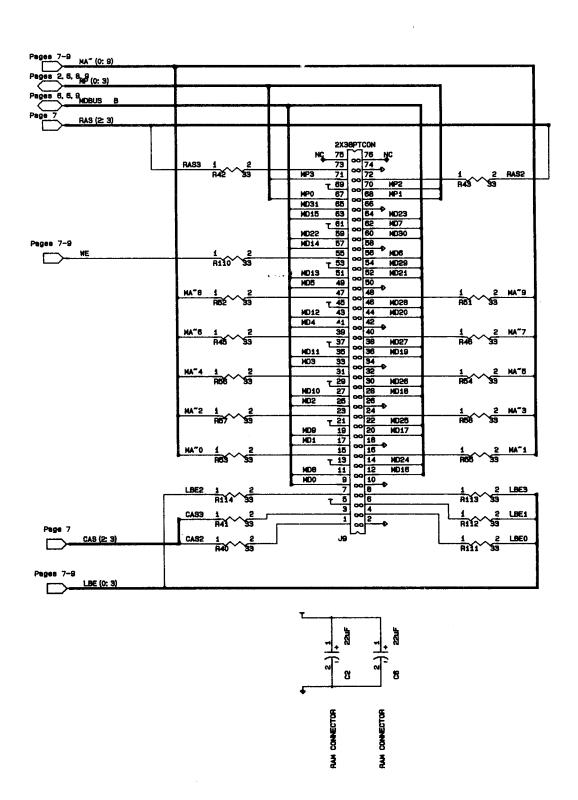

The memory data bus (MD) is 36 bits wide (32 data bits, with 4 parity bits). The system memory data bus interfaces to the local data bus or the ROM data bus, through the data buffer. The Memory Address Bus (MA) is an 10-bit bus (MA0-MA9) from the 82C302 page memory controller that accesses a particular DRAM location. (Row address strobes RAS˜0 to RAS˜3, column address strobes CAS˜0 to CAS˜3, and byte enable control signals LBE0 to LBE3 complete the memory address scheme.)

# 2.13 READ-ONLY MEMORY BUS

All data coming from the BIOS ROMs or option ROMs (on the System Interface PCA), or going to or from the peripheral data bus or the backplane I/O data bus, go over the 16-bit ROM data bus (RD).

Via the data buffer, the local data bus and the system memory data bus interface with the RD. Through a transceiver, RD interfaces with the backplane I/O data bus, which in turn, interfaces with the peripheral data bus through another transceiver.

# 2.14 BACKPLANE I/O BUS (SBUS)

The HP Vectra QS PC backplane I/O bus, an industry-standard 8-MHz bus (also known as the S-bus, or system bus) is separate from the system memory bus. It connects to the rest of the computer system, one 8-bit and six 16-bit backplane I/O connector slots. Further information is to be found in the chapter "System Interface Printed Circuit Assembly."

The system address bus (SA) is a 24-bit address bus (SA0-SA23), connected to the 82A303 and 82A304 address buffers on the Processor/Memory PCA, for connection to other address buses in the system. Backplane I/O connector slots can receive an address from any of the other address buses or generate an address to any of the other buses, depending on the operation involved. (For more information, see the section on "Address Buffers" in this chapter.)

The system data bus (SD) is a 16-bit data bus (D0-D15) over which data to/from the backplane I/O connector slots are sent. This data, in turn, are sent over the ROM data bus to the data buffers on the Processor/Memory PCA for connection to the rest of the system.

If a backplane I/O connector slot needs control of the system, it holds MASTER\* low. After the appropriate protocol has been completed, an address originating from an I/O accessory card is sent over SA to other address buses in the system.

If the 80386 microprocessor needs to access a backplane I/O connector slot, an address is sent over the local address bus, through the address buffers, and then to SA.

During direct-memory access (DMA) operations, an address originating from the integrated peripheral controller's DMA controller is sent over the peripheral bus to both the S-bus and the local bus.

### Backplane I/O Bus Clocking

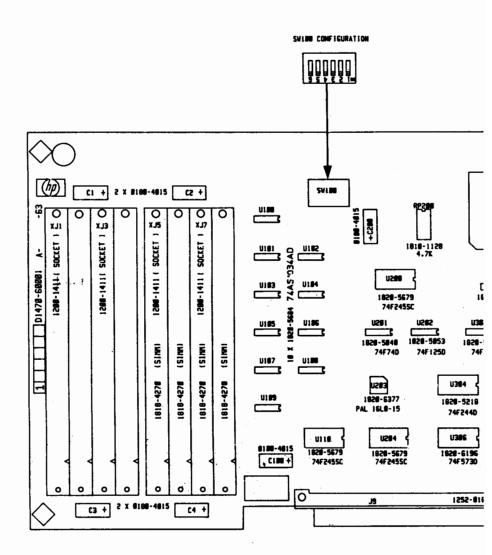

The clock used for the industry-standard I/O backplane depends on the position of Processor/Memory PCA's Switch 1, setting 2.

When setting 2 is in the OFF position (default QS/16), the HP Vectra QS uses a synchronous clock signal generated by the 82C301 bus controller's processor crystal oscillator, OSC2 (32 MHz on a QS/16, 40 MHz on a QS/20), ÷4. That is 8 MHz on a QS/16, and 10 MHz on a QS/20. On a QS/20, this option should only be used if all accessory cards can run at 10 MHz.

When setting 2 is in the ON position (default QS/20), the HP Vectra QS uses an asynchronous clock generated by the 82C301 bus controller's 16 MHz backplane crystal oscillator, OSC1, ÷2. That is, 8 MHz.

# 2.15 PERIPHERAL BUS

The peripheral bus (also known as the X-bus) connects to the 80386 microprocessor the following controllers:

- 82C301 bus controller on the Processor/Memory PCA

- 82C302 page memory controller on the Processor/Memory PCA

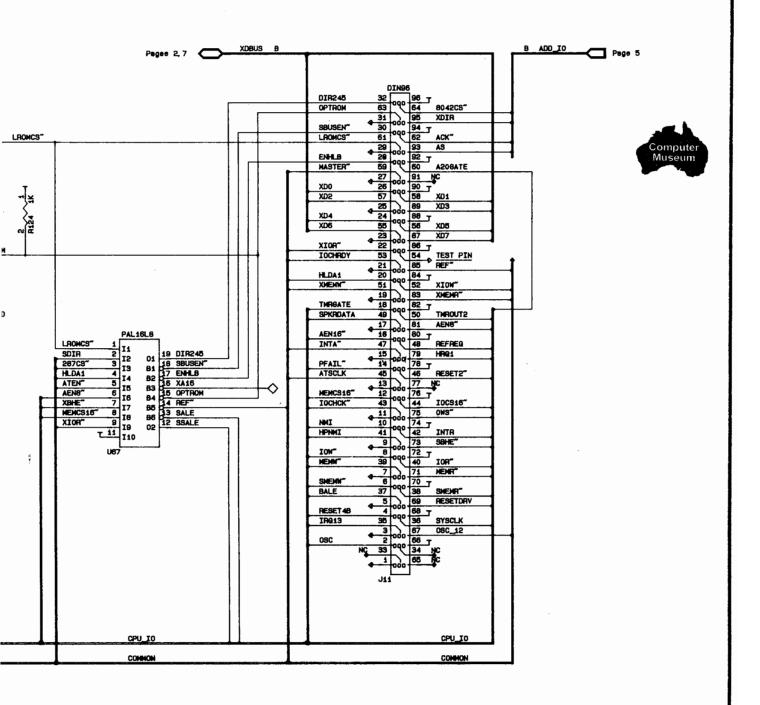

- 82C206 integrated peripheral controller (IPC) on the System Interface PCA

- HP-HIL controller (IRD2) on the System Interface PCA

- 8042 keyboard controller on the System Interface PCA

- 8042 port expander on the System Interface PCA.

The 24-bit peripheral address bus (XA) connects the controllers to the 82A303 and 82A304 address buffers (on the Processor/Memory PCA), for connection to the local address bus (A). Through the local address bus and peripheral address bus, the 80386 microprocessor can access the various controller's registers.

The 8-bit peripheral data bus (XD) accesses the backplane I/O system data bus via a transceiver and allows the 80386 to read data from or write data to the control registers. The backplane I/O (system) data bus, in turn, interfaces with the ROM data bus via another transceiver. Via the data buffer, the ROM data bus then connects to the local data bus or the memory data bus.

During DMA cycles, the 82C206 integrated peripheral controller generates a DMA address and sends it over the XA bus, which is connected to the local address bus and the backplane I/O system address bus via the address bus. The BIOS ROMs are addressed through the XA bus; however, data is read directly over the ROM data bus.

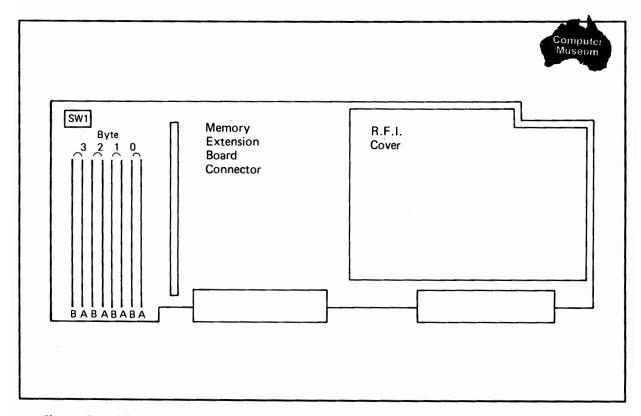

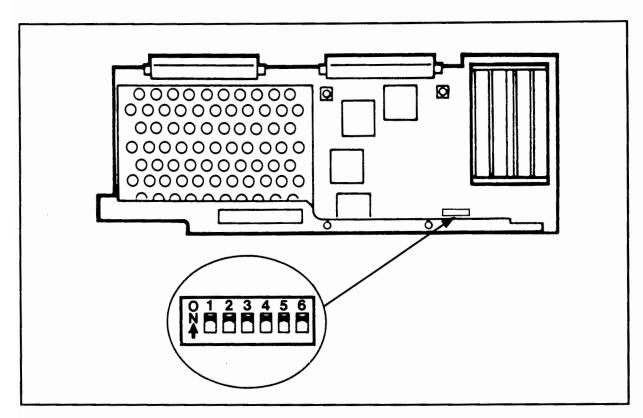

Figure 2-7. QS/16 & QS/20 Processor/Memory PCA Switches

Table 2-2. QS/16 & QS/20 Processor/Memory PCA Default Switch Settings

| Switch # | ON                                                                                                         | OFF                                                                                                                                    | QS/16 | QS/20 |

|----------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|

| 1        | 80387 disabled                                                                                             | 80387 enabled                                                                                                                          | ON    | ON    |

| 2        | Backplane I/O channel speed<br>8 MHz asynchronous. Derived<br>from the "backplane" oscillator<br>(OSC1)÷ 2 | Backplane I/O channel speed<br>8 MHz (QS/16) or 10 MHz<br>(QS/20*) synchronous. Derived<br>from the clock used by 80386<br>(OSC2) ÷ 4. | OFF   | ON    |

| 3        | Base RAM: 640 KB                                                                                           | Base RAM: 512 KB                                                                                                                       | ON    | ON    |

| 4        | Option ROM enabled                                                                                         | Option ROM disabled                                                                                                                    | ON    | ON    |

| 5        | HP Reserved                                                                                                | HP Reserved                                                                                                                            | ON    | ON    |

| 6        | 80387 clock uses same clock as<br>80386 (OSC2) - synchronous                                               | 80387 clock uses the "coprocessor" oscillator (OSC3) - asynchronous                                                                    | ON    | ON    |

<sup>\*</sup> On the QS/20, switch 2 should only be set to OFF if all accessory cards are designed to run at 10 MHz.

# QS/16S Processor/Memory **Printed Circuit Assembly**

### 3.1 INTRODUCTION

This chapter describes the QS/16S Processor/Memory PCA—a six-layer, surface-mount printed circuit assembly which provides the HP Vectra QS/16S PC with all its RAM, the support circuitry for all buses, and support for the board's subsystems.

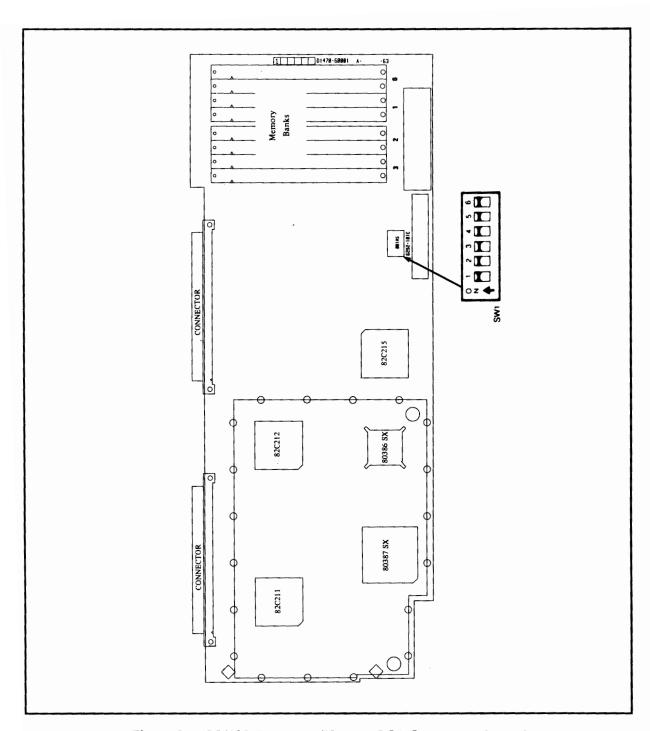

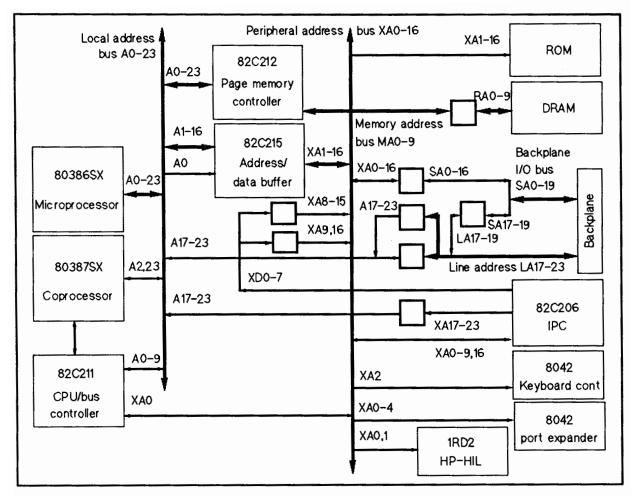

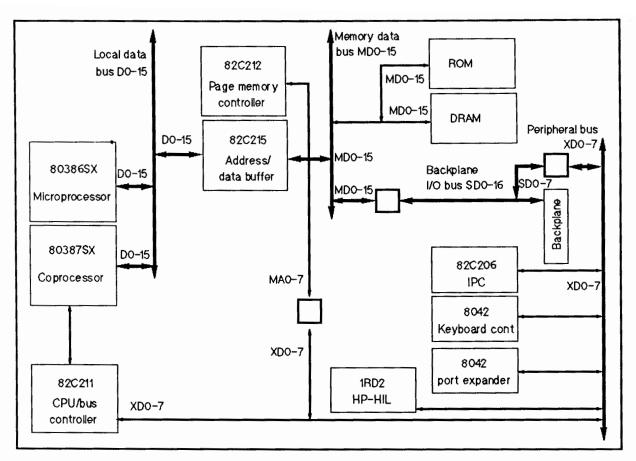

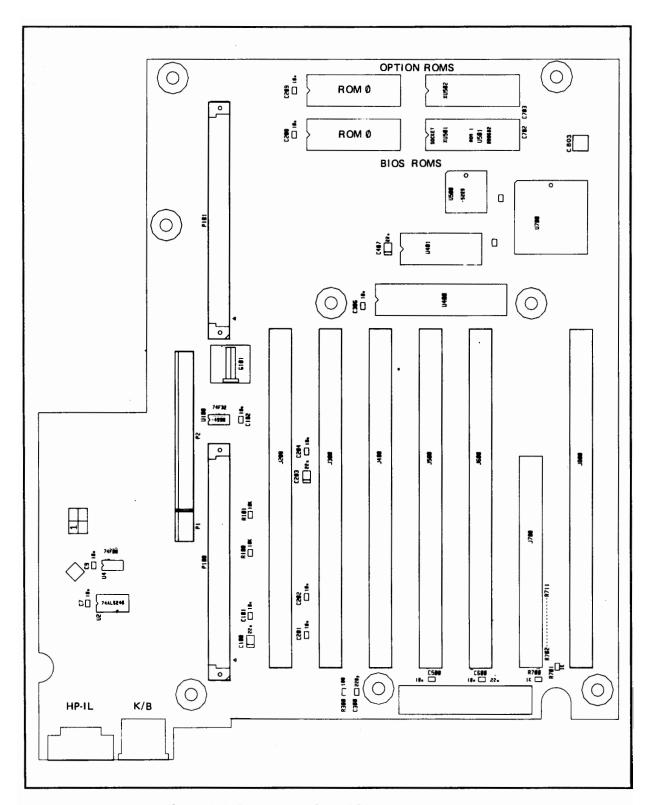

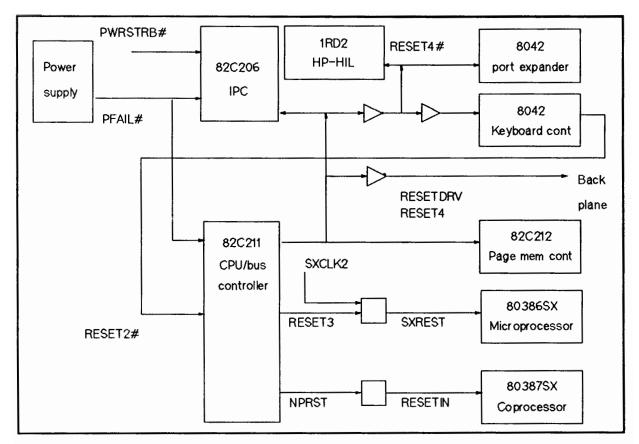

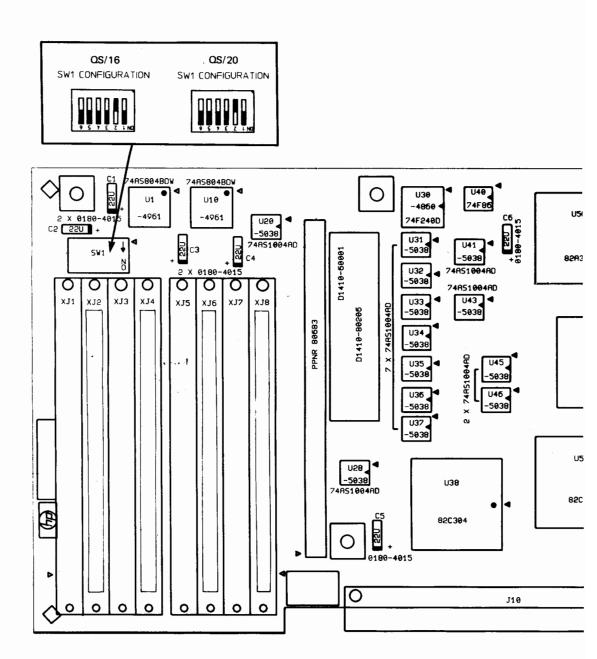

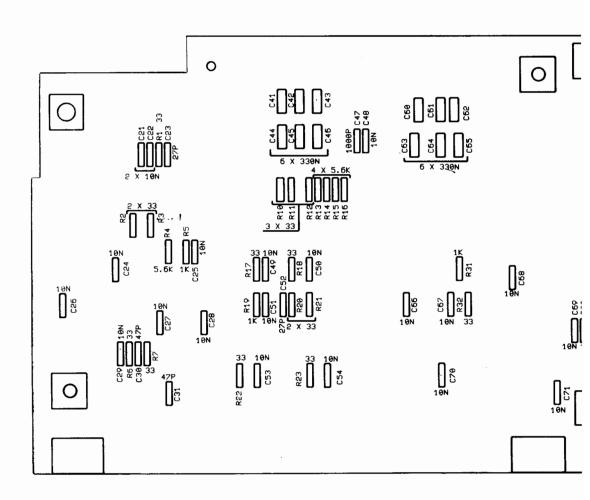

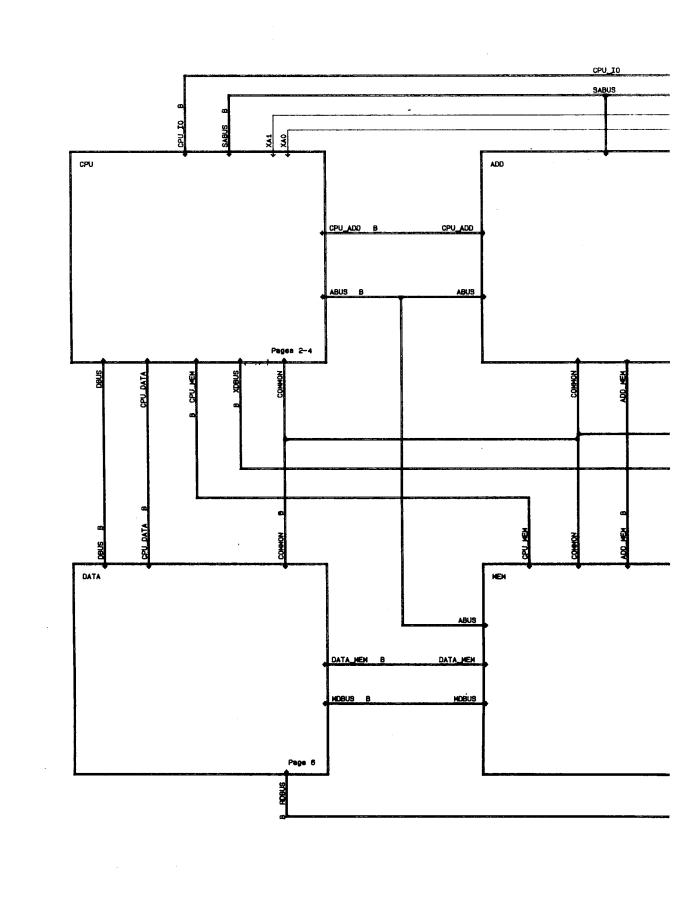

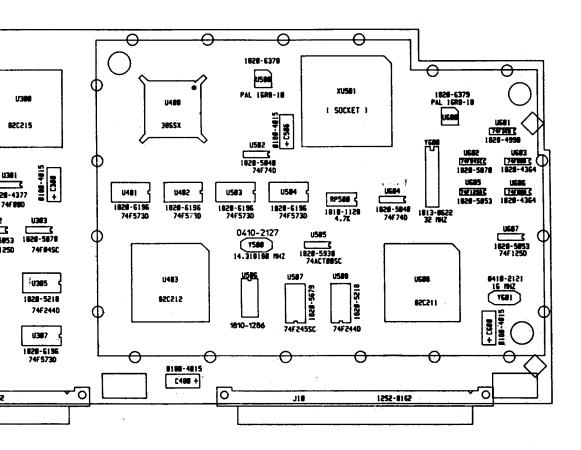

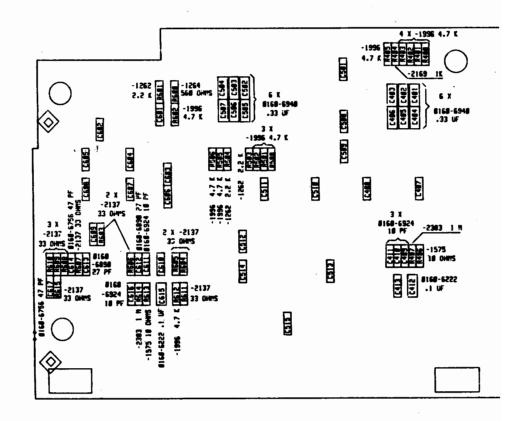

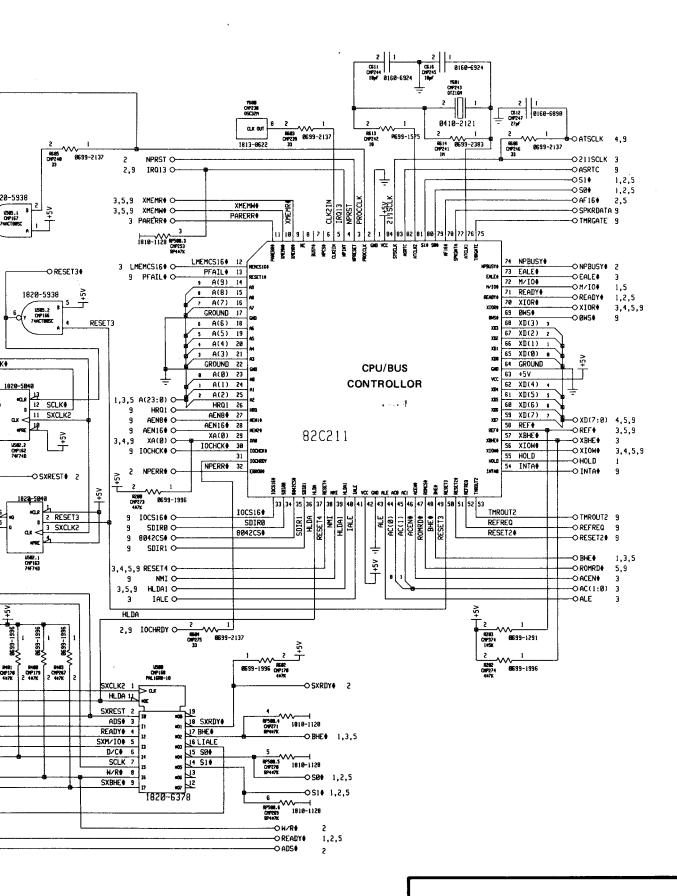

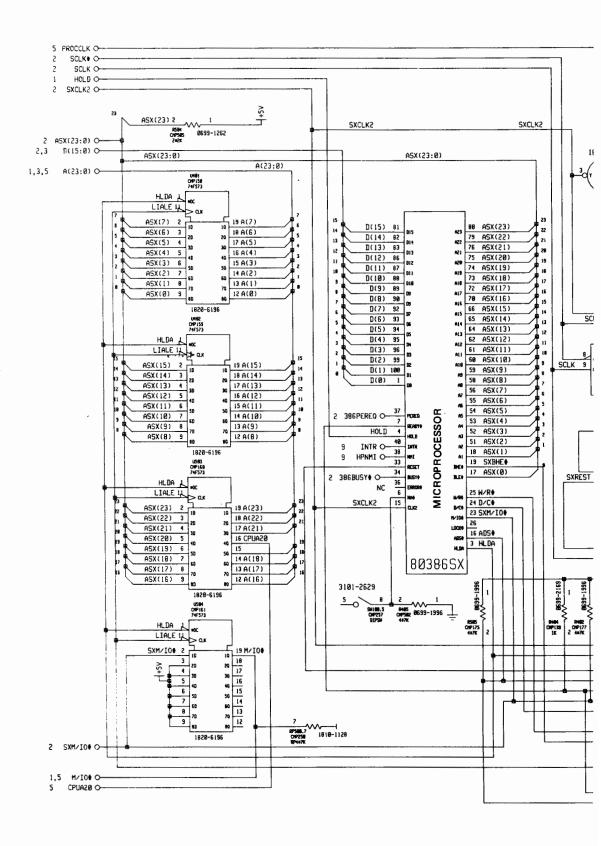

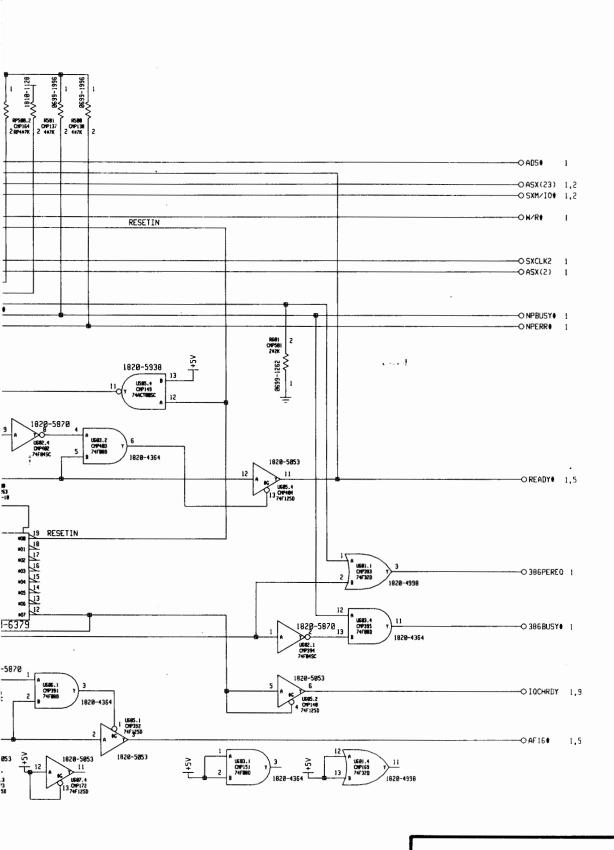

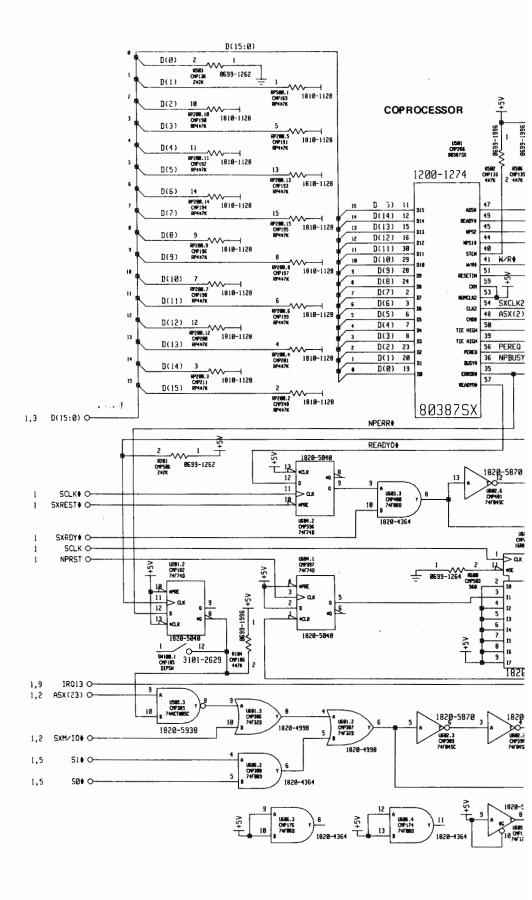

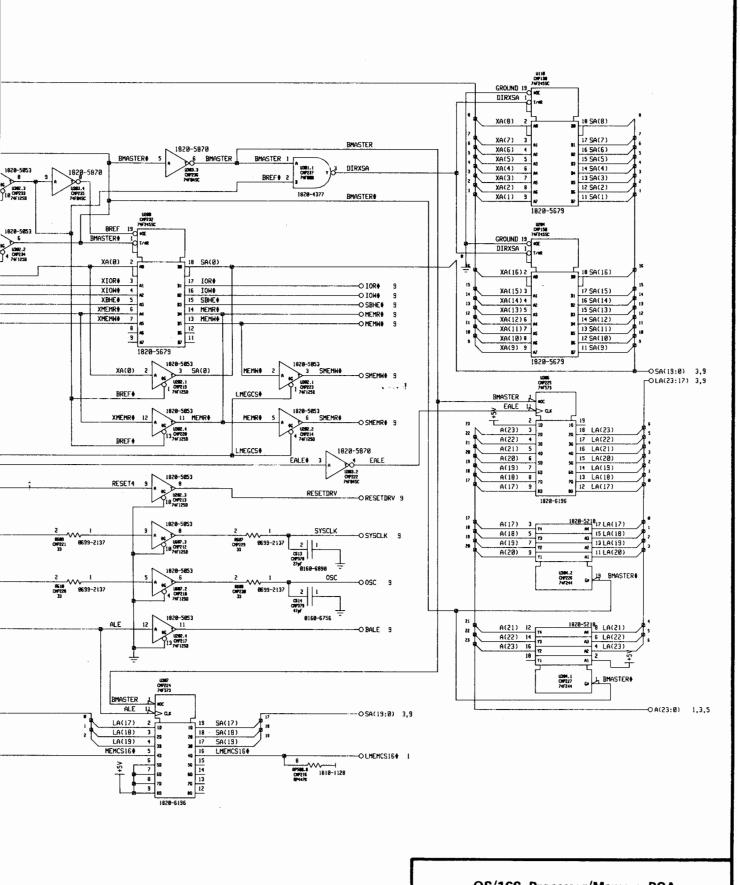

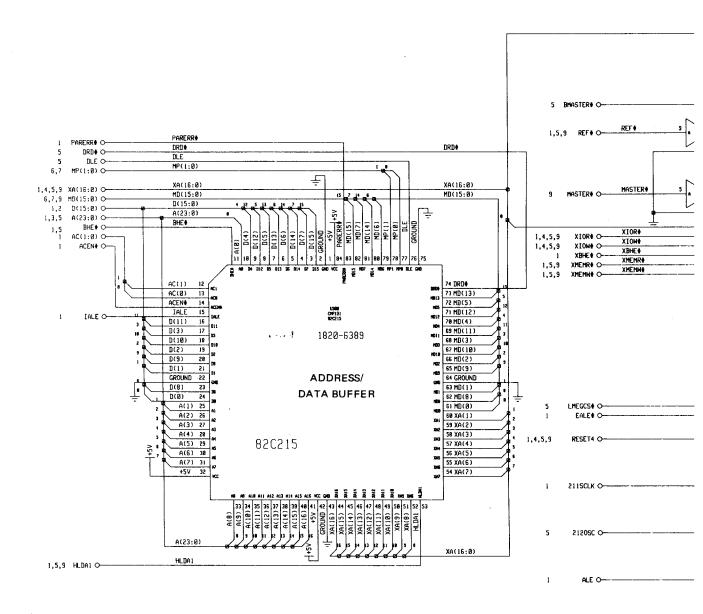

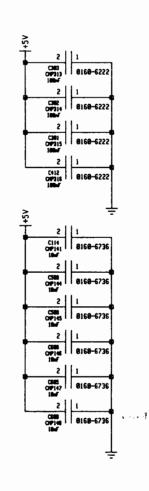

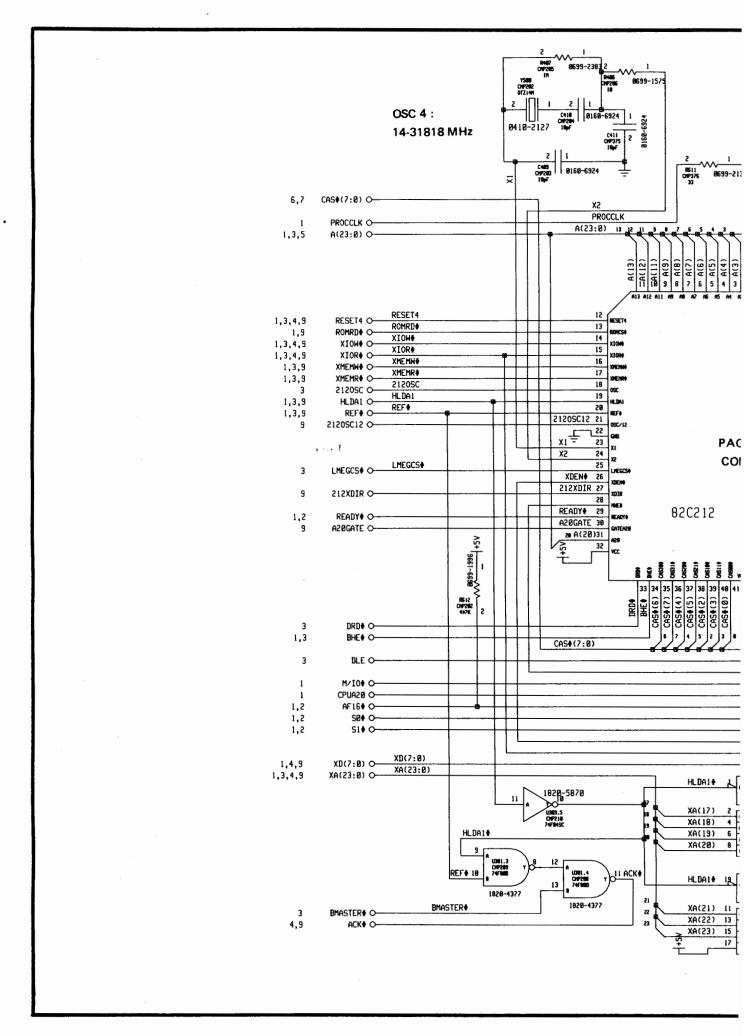

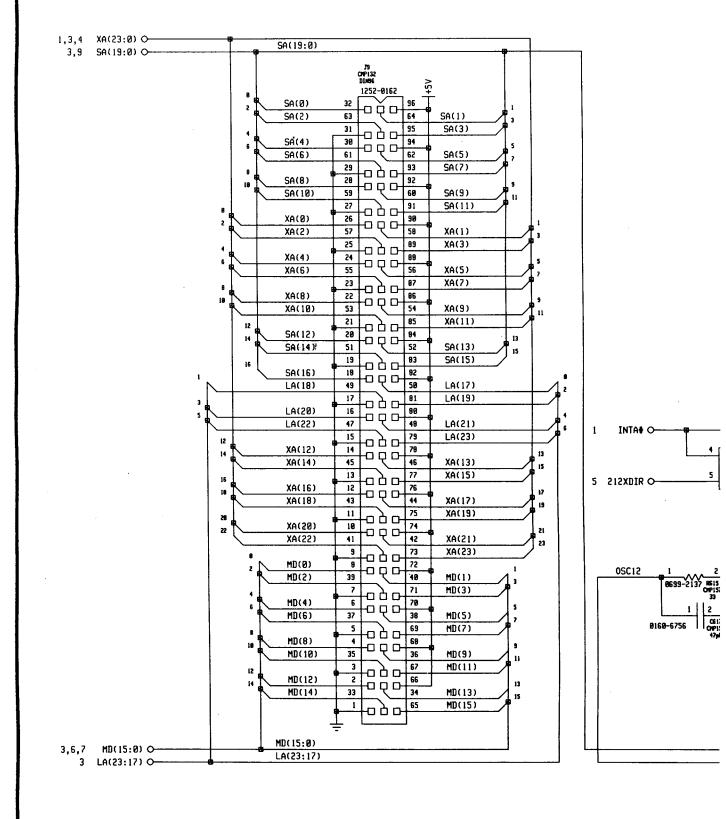

Below is a list of the major QS/16S Processor/Memory PCA components. Figure 3-1 shows their layout. Figure 3-2 is a block diagram of the QS/16S Processor/Memory PCA.

Major QS/16S Processor/Memory PCA Components:

| Component:                               | Quantity: | Туре:            |

|------------------------------------------|-----------|------------------|

| Microprocessor                           | 1         | 80386SX @ 16 MHz |

| CPU/bus controller                       | 1         | 82C211 @ 16 MHz  |

| Page memory controller                   | 1         | 82C212 @ 16 MHz  |

| Address and data buffer                  | 1         | 82C215           |

| Backplane clock, OSC1                    | 1         | 16 MHz           |

| Processor clock, OSC2                    | 1         | 32 MHz           |

| System clock, OSC4                       | 1         | 14.318 MHz       |

| Single in-line memory modules            | -         | 100 ns           |

| Sockets for single in-line memory module | 8         |                  |

| Dip switch bank for configuration        | 1         |                  |

| 2-connector slot to System Interface PCA | 1         |                  |

| Socket for 80387SX coprocessor           | 1         |                  |

Note: The following components used on the QS/16 & QS/20 Processor/Memory PCA are NOT available on the QS/16S Processor/Memory PCA:

- Coprocessor clock (OSC3) and

- Memory Extension PCA.

Figure 3-1. QS/16S Processor/Memory PCA Component Layout

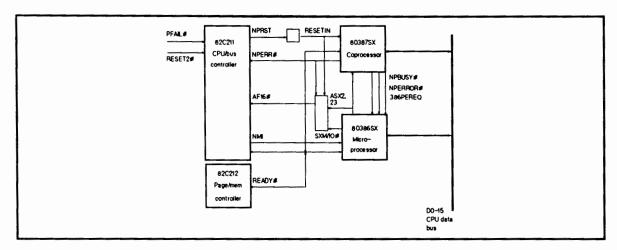

Figure 3-2. QS/16S Processor/Memory PCA Block Diagram

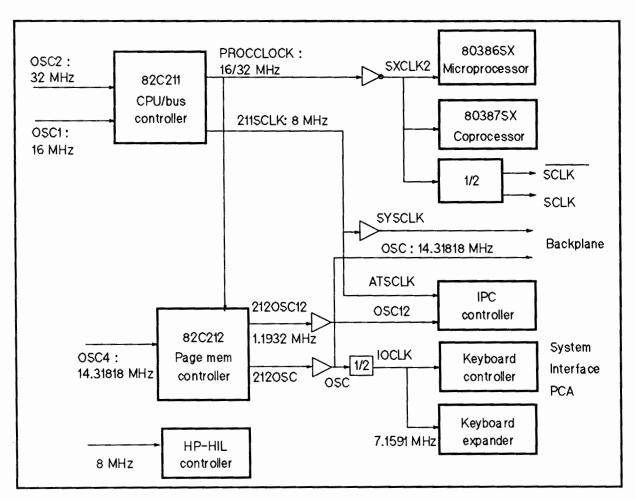

# 3.2 SYSTEM CLOCKS

The system's main oscillators, located on the QS/16S Processor/Memory PCA, generate the various system clock signals and are discussed under the components for which they provide clocking. (Other oscillators are part of a particular chip or family of chips and are described in the sections covering these chips.)

Oscillator 1 provides 16 MHz for the 82C211 CPU/bus controller.

Oscillator 2 provides 32 MHz for the 82C211 CPU/bus controller.

Oscillator 4 provides 14.318 MHz to the 82C212 page memory controller. This in turn provides the clocking for the integrated peripheral controller, keyboard and HP-HIL controllers on the System Interface PCA. (For further information, see the "Control Buffer" section in this chapter.)

Figure 3-3. QS/16S Processor/Memory PCA Timing

# 3.3 MICROPROCESSOR

The HP Vectra QS/16S uses the 80386SX microprocessor as the central processing unit. It provides the following:

- 16 MB physical memory capacity.

- 32-bit registers.

- comprehensive instruction set.

- downward compatibility with the 8088, 8086 and 80286 microprocessors, and upward compatible with the 80386 microprocessor.

- interrupt support capabilities.

- processing modes: protected, real-address, and virtual 8086 mode.

- separate 16-bit external data bus and 24-bit external address bus.

- support for 8-, 16-, and 32-bit data types.

### Microprocessor Clocking

The HP Vectra QS/16S uses a 16-MHz 80386SX microprocessor, which can also be run at 8 MHz.

The 82C211 CPU/bus controller receives two oscillator inputs, 16 MHz from OSC1 and 32 MHz from OSC2, see Figure 3-3.

The 82C211 CPU/bus controller uses the 32 MHz from OSC2 to generate the signal PROCCLK. However, pressing (CTRL) (Alt) (\(\sigma\) causes the CPU/bus controller to use the 16 MHz from OSC2÷2 to generate the signal PROCCLK. This is to allow the QS/16S to operate either at 16 MHz or 8 MHz (as PROCCLK is ÷2 within the microprocessor).

The signal PROCCLK is buffered to generate the SXCLK2 signal for the 80386SX microprocessor (and 80387SX coprocessor if fitted).

The 80386SX internally divides the SXCLK2 signal for its own uses.

SXCLK2 also generates the signals SCLK and SCLK# that are used on the Processor/Memory PCA. (For more information, see the "Bus Controller" section in this chapter.)

#### Microprocessor Compatibility

By dynamically sizing data, the 80386SX microprocessor maintains hardware compatibility with the 8088, 8086, 80286 and the 80386 microprocessors.

The 80386SX microprocessor also maintains software compatibility, in that it runs industry-standard operating systems (including MS-DOS, Microsoft OS/2, and Windows 2.0) and application software developed for systems based on 8088, 8086, 80286 or 80386 microprocessors.

#### Microprocessor Operating Modes

The 80386SX microprocessor offers the following operating modes:

#### 1. Real-Address Operating Mode

The 80386SX microprocessor's real-address operating mode is entered when the SPU is powered up or a system reset occurs. This operating mode addresses up to 1 MB of system memory and allows 32-bit operands, but does not provide memory protection.