# RTE Operating System Driver Writing Manual

### PRINTING HISTORY

The Printing History below identifies the Edition of this Manual and any Updates that are included. Periodically, Update packages are distributed which contain replacement pages to be merged into the manual, including an updated copy of this Printing History page. Also, the update may contain write-in instructions.

Each reprinting of this manual will incorporate all past Updates, however, no new information will be added. Thus, the reprinted copy will be identical in content to prior printings of the same edition with its user-inserted update information. New editions of this manual will contain new information, as well as all Updates.

To determine what manual edition and update is compatible with your current software revision code, refer to the appropriate Software Numbering Catalog, Software Product Catalog, or Diagnostic Configurator Manual.

| Fifth EditionF | 'eb | 1980 |                       |

|----------------|-----|------|-----------------------|

| Update 1       | Jul | 1981 | Manual enhancement    |

| Reprint        | Jul | 1981 | Update 1 incorporated |

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANT-ABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another program language without the prior written consent of Hewlett-Packard Company.

## HP Computer Museum www.hpmuseum.net

For research and education purposes only.

#### **DOCUMENTATION MAP**

(Refer to the Documentation Map in the appropriate operating system manual for a complete list of related manuals.)

## **CONTENTS**

| Section I                              | Page  | Returning DCPC Channels to RTE 3-17                   |

|----------------------------------------|-------|-------------------------------------------------------|

| INTRODUCTION                           |       | Handling the DCPC Interrupt                           |

| Purpose                                | 1-1   | Intermixed DCPC and Non-DCPC Operations 3-19          |

| Scope                                  | 1-1   | Driver Automatic "Up"3-19                             |

| Supporting Documentation               | 1-1   | Power Fail Processing3-19                             |

|                                        |       | Power Down Sequence                                   |

| Section II                             | Page  | Power Up Sequence 3-20                                |

| RTE INPUT/OUTPUT STRUCTURE             |       | Restart I/O Sequence 3-21                             |

| Introduction                           | 2-1   | Program Scheduling by Drivers 3-22                    |

| Software I/O Structure                 |       | Determination of Operating System                     |

| Input/Output Device Drivers            |       | Environment                                           |

| System I/O Processor                   |       | Subroutines for Special Mapping Functions             |

| Base Page Communications Area          |       | (DMS Systems Only)                                    |

| Equipment Table                        |       | Mapping in RTE-III and RTE-M/III                      |

| Logical Unit Numbers                   |       | Mapping in RTE-IV                                     |

| Device Reference Table                 |       | Sample Standard RTE Driver                            |

| Computer Interrupt Mechanism           |       | Dample Standard 1012 Briver                           |

| Interrupt Table                        |       |                                                       |

| Driver Mapping Table (RTE-IV only)     |       | Section IV Page                                       |

| General Operation of RTE I/O           |       | WRITING PRIVILEGED RTE DRIVERS                        |

| I/O Initiation                         |       | Introduction                                          |

| I/O Continuation                       |       | General Privileged Driver Structure and Operation 4-3 |

| I/O Completion                         |       | Initiation Section                                    |

| 20 Completion                          | 2-17  | Privileged Section 4-6                                |

| Section III                            | Page  | Completion Section 4-9                                |

| WRITING STANDARD RTE DRIVERS           | 1 age | Privileged Driver Design Considerations               |

| Introduction                           | 3-1   | Communication With User Programs                      |

| General Driver Structure and Operation |       | (DMS Systems Only)                                    |

| Driver Naming Requirements             |       | Discussion of Sample DMS Privileged Driver 4-10       |

| Initiation Section                     |       | Initiation Section                                    |

| Functions of the Initiation Section    |       |                                                       |

|                                        |       | Privileged Section                                    |

| Continuation/Completion Section        |       | Completion Section                                    |

| Device Clear on Program Abort          |       | Time-Out Values for Privileged Drivers 4-12           |

| I/O Controller Time-Out                |       | Subroutines for Special Mapping Functions             |

| Driver Processing of Time-Out          |       | (DMS Systems Only)                                    |

| System Processing of Time-Out          |       | Mapping in RTE-III and RTE-M/III 4-13                 |

| DCPC Processing                        |       | Mapping in RTE-IV 4-15                                |

| RTE Control of DCPC Assignment         |       | Sample DMS Privileged Driver 4-17                     |

| DCPC Assignment by RTE                 | 3-13  | Sample Non-DMS Privileged Driver 4-18                 |

|                                        |       |                                                       |

## **ILLUSTRATIONS**

| Title                                 | Page          | Title                                      | Page |

|---------------------------------------|---------------|--------------------------------------------|------|

| Equipment Table Entry Format          | 2-5           | I/O Driver Initiation Section              | 3-4  |

| Expansion of CONWD (EQT Entry Word 6) | 2-6           | I/O Driver Continuation/Completion Section | 3-7  |

| Device Reference Table Entry Format   | 2-9           | DCPC Channel Assignment Words              | 3-13 |

| Device Reference Table                | 2-9           | Determining DCPC Assignment                | 3-16 |

| Interrupt Table                       | 2-12          | Standard RTE Driver Example                | 3-30 |

| Driver Mapping Table                  | $\dots 2$ -14 | DMS Privileged RTE Driver Example          | 4-18 |

| Unbuffered I/O Read Request           | 2-16          | Non-DMS Privileged RTE Driver Example      | 4-25 |

## **TABLES**

| Title                                         | Page     | Title              | Page       |

|-----------------------------------------------|----------|--------------------|------------|

| Base Page Communications Area — I/O Operation | ns . 2-3 | \$OPSY Word Format | <br>. 3-24 |

V

## INTRODUCTION

SECTION

ı

#### 1-1. PURPOSE

The RTE Operating System Driver Writing Manual is a reference for those users who wish to develop their own device drivers. A device driver provides the software interface between a peripheral device and the RTE operating system. Many drivers for HP peripherals have already been written and are available from HP. Users who wish to interface peripherals that are not supported by HP will require specialized drivers. The information in this manual will aid the user in the development of such routines.

Note that it is not the purpose of the manual to describe the various HP-supplied drivers in any detail. Each of these is described in a separate manual specific to the driver.

#### 1-2. SCOPE

The manual first provides the reader with a general description of the input/output (I/O) characteristics of the RTE family of operating systems. The techniques and requirements for developing device drivers are then presented in subsequent sections.

Since all of the RTE operating systems have the same general I/O structure, the manual can be used to develop general purpose drivers for use in any of these RTE systems. There are some areas where differences between operating systems may affect driver structure and operation; these areas are clearly pointed out in the text with notations such as "RTE-IV only" or "RTE-III only." Phrases such as "RTE-III only" should be interpreted as referring to both RTE-III (disc-based system) and RTE-M/III (memory-based equivalent of RTE-III).

#### 1-3. SUPPORTING DOCUMENTATION

To use this manual effectively, the reader should be thoroughly familiar with HP Assembly Language and with the Programming and Operating Manual for the RTE system in which the driver is to be used. Refer to the Documentation Map at the front of this manual for information on these and other available manuals. For specific information on an HP supplied driver, refer to the appropriate driver manual.

## RTE INPUT/OUTPUT STRUCTURE

SECTION

#### 2-1. INTRODUCTION

In RTE, centralized control and logical referencing of input and output (I/O) operations effect simple device-independent programming. By means of several user-defined I/O tables, I/O drivers, and program EXEC calls, the programmer is relieved of most I/O problems. To understand the software I/O characteristics of RTE, the user should be familiar with two hardware related terms used in this manual:

I/O Controller A combination of I/O card, cable, and (for some devices) controller box used

to control one or more I/O devices on a computer I/O select code.

I/O Device A physical unit (or portion of a unit) identified in the RTE operating system

by means of an Equipment Table entry and a subchannel assignment.

Each I/O device is interfaced to the computer through an I/O controller. This controller is associated with one or more of the computer I/O select codes. Interrupts from controllers on specific select codes are directed to specific memory locations in the computer for system processing.

It is also important to note the difference between a synchronous device and a non-synchronous device. An interrupt from a synchronous device controller must be processed within a specified time period, or the data will be lost. Examples of synchronous devices are moving-head disc drives and nine-track magnetic tape drives. Non-synchronous devices have no such requirement, and interrupts from these device controllers can be serviced whenever the computer is able to do so. Examples of non-synchronous devices include paper tape punches and readers.

#### 2-2. SOFTWARE I/O STRUCTURE

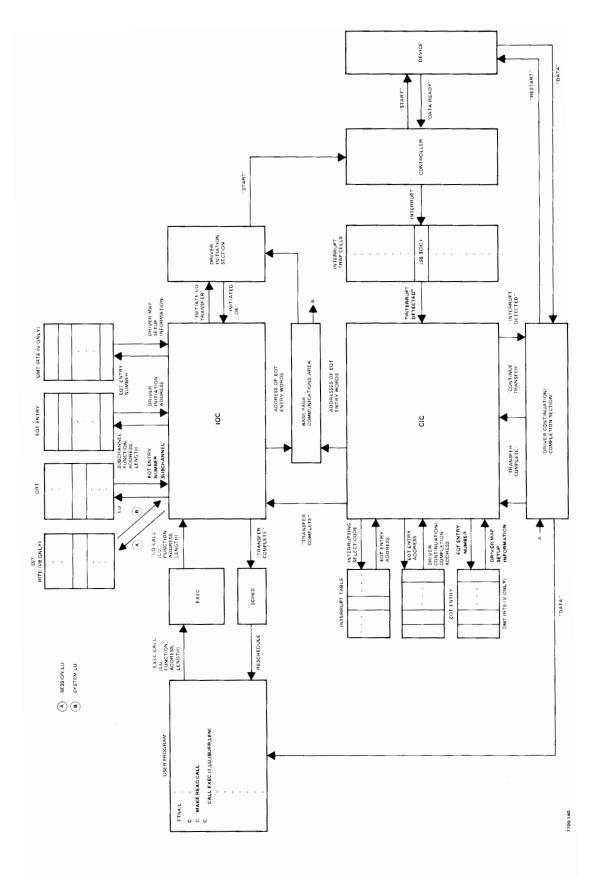

The RTE I/O structure is made up of two general types of software (the system I/O processor and the various device drivers) and a number of I/O tables and a communications area (the Equipment Table, the Device Reference Table, the Interrupt Table, the Driver Mapping Table (RTE-IV only), and the Base Page Communications Area). These tables and areas are used for communication between the system and the drivers, and for control of the many I/O operations that can be in progress simultaneously. Each component of the I/O structure is discussed individually in this subsection. A summary of the overall I/O process is given in the next subsection.

#### INPUT/OUTPUT DEVICE DRIVERS

Input/output device drivers provide the software interface between peripheral I/O devices and the operating system. Drivers are responsible for the initiation, continuation, and completion of all data transfers between an I/O device and the computer. Drivers communicate with the system directly via parameter passing, and indirectly through the various tables and communications areas (particularly the Equipment Table and the Base Page Communications Area) that are discussed later in this subsection.

There are two types of drivers; standard and privileged. Standard drivers are simpler and can be used for most asynchronous devices and some high speed and synchronous devices (if DCPC transfers are used); these drivers are discussed in Section III. Privileged drivers are more complex and are generally used for high speed and synchronous devices that require driver interaction on each data word transferred (i.e., DCPC transfers cannot be used); these drivers are discussed in Section IV.

#### SYSTEM I/O PROCESSOR

The system I/O processor (RTIOC) provides the software interface between user programs that perform I/O and the drivers that actually handle the I/O operations. RTIOC checks user I/O calls for validity, suspends programs while their I/O is in progress (if necessary), calls drivers to initiate the I/O data transfers, directs controller interrupts to the appropriate drivers, and restarts programs suspended for I/O. The mechanism for communication between RTIOC and user programs is the EXEC call and its associated parameters. Communication between RTIOC and drivers is handled directly via parameters and indirectly through the various I/O tables discussed in this section.

Two general areas within RTIOC are discussed in this manual; IOC and CIC. The Input/Output Control module (IOC) is entered when a user program makes an I/O request. IOC is responsible for initiating the I/O transfer by calling the appropriate driver. The Central Interrupt Control module (CIC) is entered when a device controller interrupt is detected. CIC is responsible for calling the correct driver to handle the interrupt.

#### BASE PAGE COMMUNICATIONS AREA

A block of storage in base page contains the system's communications area and is used by RTE to define request parameters, I/O tables, scheduling lists, operating parameters, memory bounds, etc. The RTE Assembler allows absolute references to addresses less than octal 2000 so that user programs can read information from the base page. Programs cannot alter the base page, however, because of the memory protect feature of RTE. Table 2-1 illustrates the portion of the Base Page Communications Area that pertains to I/O operations. The meaning and use of the various words illustrated in the table will become clear in subsequent sections of this manual. (For a complete description of the Base Page Communications Area, refer to the appropriate RTE System Programming and Operating Manual.)

Table 2-1. Base Page Communications Area — I/O Operations

| OCTAL<br>LOCATION                                                                      | CONTENTS                                                                               | DESCRIPTION                                                                               |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| •                                                                                      |                                                                                        |                                                                                           |

| 01650                                                                                  | EQTA                                                                                   | Address of Equipment Table (EQT)                                                          |

| 01651                                                                                  | EQT#                                                                                   | Number of EQT entries                                                                     |

| 01652                                                                                  | DRT                                                                                    | Address of Device Reference Word 1 Table                                                  |

| 01653                                                                                  | LUMAX                                                                                  | Number of logical units (in Device Reference Table)                                       |

| 01654                                                                                  | INTBA                                                                                  | Address of Interrupt Table                                                                |

| 01655                                                                                  | INTLG                                                                                  | Number of Interrupt Table entries                                                         |

| 01656                                                                                  | TAT                                                                                    | Address of Track Assignment Table (disc-based systems only)                               |

| 01657                                                                                  | KEYWD                                                                                  | Address of keyword block                                                                  |

| 01660<br>01661<br>01662<br>01663<br>01664<br>01665<br>01666<br>01667<br>01670<br>01671 | EQT1<br>EQT2<br>EQT3<br>EQT4<br>EQT5<br>EQT6<br>EQT7<br>EQT8<br>EQT9<br>EQT10<br>EQT11 | Addresses of first 11 words of current EQT entry (see location of 01771 for last 4 words) |

| 01673                                                                                  | CHAN                                                                                   | Current DCPC Select Code (6 or 7)                                                         |

|                                                                                        |                                                                                        |                                                                                           |

| 01717                                                                                  | XEQT                                                                                   | ID segment address of current program                                                     |

| :                                                                                      |                                                                                        |                                                                                           |

| 01737                                                                                  | DUMMY                                                                                  | I/O channel of privileged interrupt card (0 if none)                                      |

| :                                                                                      |                                                                                        |                                                                                           |

| 01770                                                                                  | MPTFL                                                                                  | Memory Protect On/Off (0/1) flag.                                                         |

| 01771<br>01772<br>01773<br>01774                                                       | EQT12<br>EQT13<br>EQT14<br>EQT15                                                       | Addresses of last 4 words of current EQT entry                                            |

#### **EQUIPMENT TABLE**

The Equipment Table (EQT) is used to maintain a list of all the I/O equipment in the system. This table consists of a number of EQT entries, with one EQT entry for each I/O controller defined in the system at generation time. The EQT entry contains all of the information required by the system and the associated driver to operate the equipment, including: the I/O select code in which the controller is interfaced to the computer, the driver type, and the various requirements and specifications of the controller or driver (e.g., DCPC, buffering, time-out, power fail, etc.). To distinguish between multiple I/O devices connected to a single controller, the system also inserts the subchannel number of the device being referenced into the EQT entry before calling the driver.

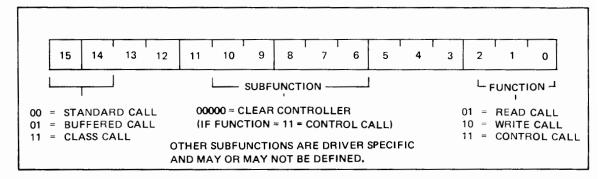

The format of each EQT entry is illustrated in Figure 2-1. Some information in the EQT entry is static; other parts are dynamic. Information marked <A> is fixed at generation time (or, for the I/O select code number in RTE-IV, at reconfiguration time) and never changes during on-line operation of the system. Words marked <B> are also fixed at generation time (or, for RTE-IV, at reconfiguration time) but can be changed on-line via operator commands. Information marked  $\ge$ C> is modified or set up for the driver prior to each I/O initialization; it informs the driver of the nature of the request. Words marked  $\ge$ D> are not used by the system and are therefore available to the driver for use as temporary storage for the duration of each I/O request.

EQT words 9 and 10 are available for use as temporary storage unless optional parameters were specified in the EXEC call. For the case of an EXEC call with the control word's Z bit clear, EQT words 9 and 10 contain the values of the optional parameters. If the Z bit was set, however, EQT word 9 contains the address of the optional buffer while word 10 contains the length of the buffer.

| ļ <u>-</u>                                                  |                                                                                                                                                                                                        |                                                                      | CONTENTS                      |                                      |               |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------|--------------------------------------|---------------|

|                                                             | 5 14 13 12 11                                                                                                                                                                                          | 10 9                                                                 | 8 7 6                         | 5 4 3                                | 2 1 1 1 0     |

| 1                                                           | I/O REQUEST LIST                                                                                                                                                                                       | POINTER <0                                                           | >                             |                                      |               |

| 2                                                           | R DRIVER "INITIATI                                                                                                                                                                                     | ON" SECTION                                                          | ADDRESS <a></a>               |                                      |               |

| 3                                                           | DRIVER "CONTINU                                                                                                                                                                                        | ATION/COMPL                                                          | ETION" SECTION                | ADDRESS <a< td=""><td>&gt;</td></a<> | >             |

| 4                                                           | (A> <b> <e> <e> <c<br>D B P S T</c<br></e></e></b>                                                                                                                                                     | SUBCHA                                                               | NNEL # <c></c>                | I/O SELECT CO                        | DDE # <a></a> |

| 5                                                           | AV <f> EQUIPMENT T</f>                                                                                                                                                                                 | PE CODE <a< td=""><th>&gt; STATUS</th><td><e></e></td><td></td></a<> | > STATUS                      | <e></e>                              |               |

| 6                                                           | CONWD (CURRENT I/O RE                                                                                                                                                                                  | QUEST WORD)                                                          | <b>&lt;</b> C>                |                                      |               |

| 7                                                           | REQUEST BUFFER ADDRI                                                                                                                                                                                   | SS <b>&lt;</b> C>                                                    |                               |                                      |               |

| 8                                                           | REQUEST BUFFER LENGT                                                                                                                                                                                   | H <b>&lt;</b> C>                                                     |                               |                                      |               |

| 9                                                           | TEMPORARY STORAGE <                                                                                                                                                                                    | D> OR OP                                                             | TIONAL PARAMET                | TER < C >                            |               |

| 10                                                          | TEMPORARY STORAGE <                                                                                                                                                                                    | D > OR OP                                                            | TIONAL PARAMET                | ER < C >                             |               |

| 11                                                          | TEMPORARY STORAGE F                                                                                                                                                                                    | OR DRIVER <                                                          | (D)                           | . <u>.</u>                           |               |

| 12                                                          | TEMPORARY STORAGE<br>FOR DRIVER <d></d>                                                                                                                                                                | OR EQTE                                                              | XTENSION SIZE,<br>Y ≺A>       |                                      |               |

| 13                                                          | TEMPORARY STORAGE OR EQT EXTENSION STARTING FOR DRIVER <d> ADDRESS, IF ANY <a></a></d>                                                                                                                 |                                                                      |                               |                                      |               |

| 14                                                          | 14 DEVICE TIME-OUT RESET VALUE <b></b>                                                                                                                                                                 |                                                                      |                               |                                      |               |

| 15                                                          | 15 DEVICE TIME-OUT CLOCK <c></c>                                                                                                                                                                       |                                                                      |                               |                                      |               |

| <a> = F</a>                                                 | WHERE THE LETTERS IN BRACKETS (<>) INDICATE THE NATURE OF EACH DATA ITEM, AS FOLLOWS: <a> = FIXED AT GENERATION TIME (OR, FOR I/O SELECT CODE # IN RTE-IV, AT RECONFIGURATION TIME); NEVER CHANGES</a> |                                                                      |                               |                                      |               |

| <b> = FIXED AT GENERATION TIME; CAN BE CHANGED ON-LINE.</b> |                                                                                                                                                                                                        |                                                                      |                               |                                      |               |

| <c> = SET UP OR MODIFIED AT EACH I/O INITIALIZATION.</c>    |                                                                                                                                                                                                        |                                                                      |                               |                                      |               |

| <d> = AVAILABLE FOR USE AS TEMPORARY STORAGE BY DRIVER.</d> |                                                                                                                                                                                                        |                                                                      |                               |                                      |               |

| 1                                                           | <e> = CAN BE SET BY DRIVER.</e>                                                                                                                                                                        |                                                                      |                               |                                      |               |

| 1                                                           | AINTAINED BY SYSTEM.                                                                                                                                                                                   |                                                                      |                               |                                      |               |

| AND WHERE:                                                  | D /2-                                                                                                                                                                                                  | TED VED 505 -                                                        | VOTEM ::05                    |                                      |               |

| I/O REQUE                                                   | ST LIST POINTER = POI<br>ENT                                                                                                                                                                           | RY. FIRST ENT                                                        |                               | RRENT REQUEST                        |               |

|                                                             | A = 1 IF                                                                                                                                                                                               | DCPC WAS ALI                                                         | LOCATED DYNAM NUATION (RTE-IV | ICALLY AT REQU                       | JEST          |

|                                                             |                                                                                                                                                                                                        | DCPC REQUIR                                                          |                               | D GIVE I /                           |               |

|                                                             |                                                                                                                                                                                                        |                                                                      | <br>OUTPUT BUFFERIN           | NG USED                              |               |

|                                                             | P = 1 iF                                                                                                                                                                                               | DRIVER IS TO                                                         | PROCESS POWER                 | FAIL                                 |               |

| ·                                                           | S = 1 IF                                                                                                                                                                                               | DRIVER IS TO                                                         | PROCESS TIME-O                | JT                                   |               |

|                                                             |                                                                                                                                                                                                        | DEVICE TIMES<br>H I/O REQUES                                         | O OUT (SYSTEM SE              | TS TO ZERO BEF                       | ORE           |

| SUBCHANN                                                    | EL# = LAS                                                                                                                                                                                              | T SUBCHANNE                                                          | L ADDRESSED                   |                                      |               |

Figure 2-1. Equipment Table Entry Format (Sheet 1 of 2)

I/O SELECT CODE # I/O SELECT CODE FOR THE I/O CONTROLLER (LOWER NUMBER IF A MULTI-BOARD INTERFACE) ΑV = I/O CONTROLLER AVAILABILITY INDICATOR: 0 = AVAILABLE FOR USE 1 DISABLED (DOWN) **BUSY (CURRENTLY IN OPERATION)** 2 WAITING FOR AN AVAILABLE DCPC CHANNEL EQUIPMENT TYPE CODE IN GENERAL, INDICATES TYPE OF DEVICE ON THIS CON-TROLLER. WHEN THIS OCTAL NUMBER IS LINKED WITH "DVY", IT IDENTIFIES THE DEVICE'S SOFTWARE DRIVER ROUTINE. SOME STANDARD EQUIPMENT TYPE CODES ARE: 00 TO 07 = PAPER TAPE DEVICES OR CONSOLES 00 TELEPRINTER (OR KEYBOARD CONTROL DEVICE) = PHOTOREADER 01 = PAPER TAPE PUNCH 02 = 264X SERIES TERMINALS 05 = MULTI-POINT DEVICES 07 = UNIT RECORD DEVICES 10 TO 17 = PLOTTER 10 11 CARD READER = LINE PRINTER 12 MARK SENSE CARD READER 15 20 TO 37 = MAGNETIC TAPE/MASS STORAGE DEVICES 23 = 9 TRACK MAGNETIC TAPE = 7900 MOVING HEAD DISC 31 = 7905/06/20 MOVING HEAD DISC 32 = FLEXIBLE DISC DRIVES 33 36 = WRITABLE CONTROL STORE = HPIB 37 **= INSTRUMENTS** 40 TO 77 **STATUS** ACTUAL PHYSICAL STATUS OR SIMULATED STATUS AT THE END OF EACH OPERATION. CONWD COMBINATION OF USER CONTROL WORD AND USER REQUEST CODE WORD IN THE I/O EXEC CALL (SEE BELOW).

Figure 2-1. Equipment Table Entry Format (Sheet 2 of 2)

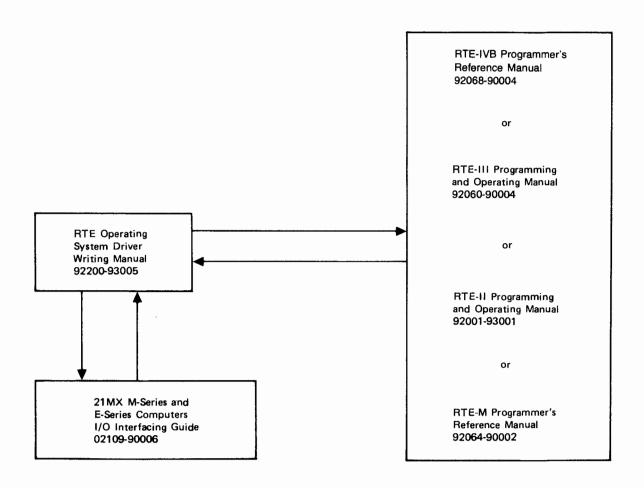

Figure 2-2. Expansion of CONWD Word (EQT Entry Word 6)

If the number of words marked <D> does not provide sufficient temporary storage for the driver, additional space can be allocated at generation time by specifying that an EQT entry extension is needed for a particular EQT entry. This space can only be used to extend the referenced EQT entry and therefore should only be allocated for drivers that need the additional space. When an EQT entry extension is specified, EQT entry words 12 and 13 are used to identify the location and length of the extension (since the extension does not immediately follow the EQT entry) and therefore should not be modified by the driver. Otherwise, these words are available as temporary storage.

For programming convenience, the addresses of each word in the current EQT entry (except for words in the extension, if an extension exists) are placed in the Base Page Communications Area by the system before calling the driver to initiate or continue an I/O operation. A driver should use these addresses instead of computing them from the EQT entry number and the start of the Equipment Table. In this way, the driver can remain independent of the actual organization of the Equipment Table in memory.

All Equipment Table entries are located sequentially in memory beginning with EQT entry number 1. The address of the first entry and the total number of entries in the table can be found in the Base Page Communications Area.

#### LOGICAL UNIT NUMBERS

Logical unit numbers (LU's) provide the RTE user with the capability of logically addressing the physical devices defined by the Equipment Table. LU numbers are maintained by the Device Reference Table (see below), and their definition can be changed on-line by the LU operator request. This scheme allows the programmer to reference changeable logical units instead of fixed physical units.

The function of Logical Units 0 through 6 are predefined in the RTE system as follows:

- 0 "bit bucket" (null device, no entry in Device Reference Table)

- 1 system console

- 2 reserved for system (system disc subchannel in disc-based systems)

- 3 reserved for system (auxiliary disc subchannel in disc-based systems)

- 4 standard output device

- 5 standard input device

- 6 standard list device

Logical Unit 8 is recommended for the magnetic tape device, if one is present in the system. Peripheral discs must be assigned logical units greater than 6. Additional logical units may be assigned for any functions desired.

#### DEVICE REFERENCE TABLE

The Device Reference Table (DRT) is part of the mechanism by which logical unit numbers for I/O are implemented. RTE users request I/O by specifying a logical unit number. The DRT is used to translate this logical unit number into a physical device, as specified by an EQT entry number and subchannel. The DRT is also used to queue requests for I/O on a device when it is

unavailable (down). (The DRT is not used to queue requests when the device is up. The request list for available (i.e., up) devices originates from word 1 of the EQT entry as illustrated in Figure 2-1.)

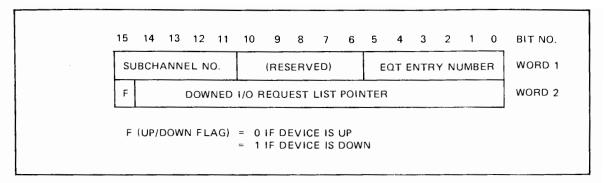

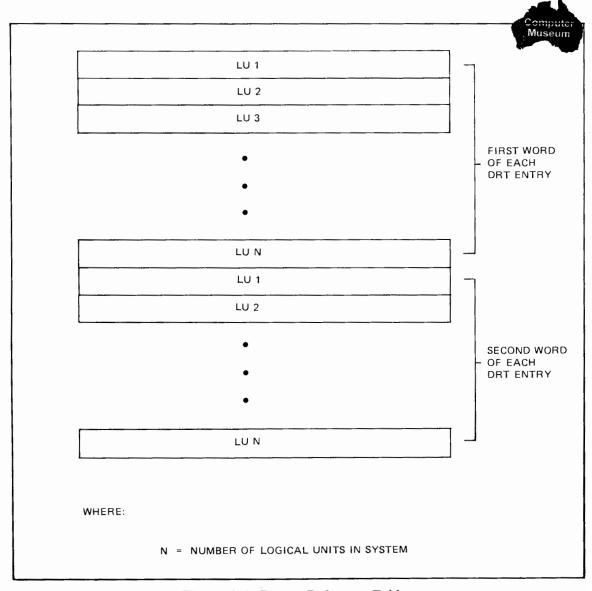

Each DRT entry is two words long. There is one entry for each logical unit number defined at generation time, beginning with logical unit 1. The format of each entry is illustrated in Figure 2-3. The first word of the entry contains several items, including: 1) the EQT entry number of the controller assigned to the logical unit, and 2) the subchannel number of the specific device on that controller to be referenced. The second word of each entry contains the status of the logical unit: up (available) or down (unavailable). If the device is down, word two also contains a pointer to the list of requests waiting to access the LU.

Figure 2-3. Device Reference Table Entry Format

Figure 2-4. Device Reference Table

The DRT table is actually split into two separate parts. The first part contains word 1 of each DRT entry, and the second part contains word 2 of each DRT entry. This format is illustrated in Figure 2-4. The starting address and length of part one of the table can be found in the Base Page Communications Area. Part two is located in memory immediately following part one and has the same length as part one.

#### COMPUTER INTERRUPT MECHANISM

When a device controller interrupts RTE, the computer transfers control to one of a group of memory locations on base page known as the interrupt trap cells. The I/O select code of the interrupting controller determines the location of the transfer. For example, interrupts from select code 12 cause a transfer to memory location 12. Interrupts from select code 13 cause a transfer to memory location 13, and so on. Select code numbers range from 4 to 77 (octal). Thus, the group of memory locations from 4 to 77 (octal) comprises the entire set of interrupt trap cells.

Transferring control to an interrupt trap cell causes the instruction located there to be executed. For all devices operating under the control of CIC, this instruction is a JSB LINK,I, where LINK is a base page link containing the address of the entry point to CIC. This instruction is initially set up by the RTE generator, and is reset into the trap cell each time the system is rebooted. The fact that the JSB instruction references an indirect address causes the computer to hold off any further interrupts for one instruction after the JSB. This gives CIC a chance to issue a CLF 0 instruction (which disables the interrupt system entirely) to prevent further interrupts from occurring while the current one is being processed.

Since CIC is entered at the same location for all device controller interrupts under its control, a method is needed by which the select code of the interrupting device controller can be determined. CIC obtains the interrupting select code number by accessing the contents of the computer's Central Interrupt Register via an LIA 4 instruction. CIC can then use this information to index into the Interrupt Table (see next subsection) to determine how to process the interrupt.

The interrupt trap cells are not limited to containing a JSB LINK,I instruction (where LINK contains the address of CIC). Other instructions can be placed in a trap cell by the generator or by a system routine. However, the trap cell should not contain any instruction other than a HALT instruction or a JSB indirect to an interrupt processing routine (such as CIC or a user-written routine) that saves the state of the machine on entry and restores it to its original state on exit. This includes saving and restoring the registers, state of the memory protect fence, etc.

Specifically, I/O instructions and NOP instructions must not be put into trap cells because they do not provide any way to restore the system to its original state. Microcode macro's (i.e., jumps to microcoded routines) may be used if a microcoded driver is used to process the interrupts.

Note that if a JSB instruction is placed in the interrupt trap cell, it must reference an indirect address. The indirect address keeps the interrupt system suppressed for one instruction after the JSB, as explained above. This allows the interrupt processing routine to issue a CLF 0 instruction to prevent further interrupts from occurring while the state of the machine is being saved. (Note that the generator automatically provides a base page link for all JSB instructions it places in the interrupt trap cells. A JSB indirect instruction is created whenever an "ENT," "PRG," or "EQT" entry is specified during generation.)

Systems without the power fail/automatic restart feature have a HALT 4 instruction inserted by the generator into the power fail interrupt trap cell (memory location 4). As a result, the computer will halt when a power fail interrupt occurs. An example of a JSB to a user-written interrupt processing routine is discussed later in the "Writing Privileged Drivers" section of this manual.

#### INTERRUPT TABLE

The Interrupt Table directs CIC's action when an interrupt occurs on any I/O select code that contains a JSB LINK,I instruction (where LINK contains the address of CIC). CIC can call a driver, schedule a specified program, or handle the interrupt itself.

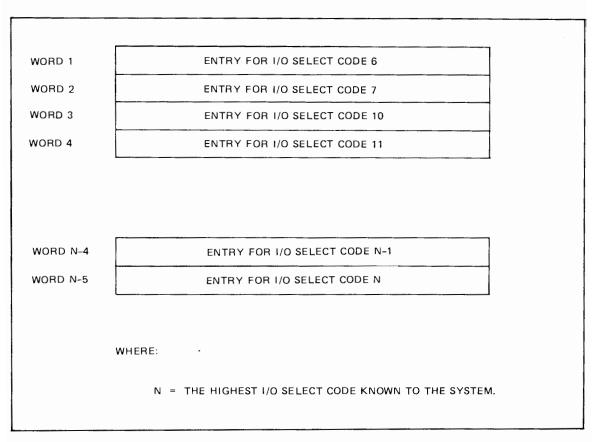

There is one Interrupt Table entry for each I/O select code from 6 up to the highest select code defined in the system at generation. (Systems with I/O reconfiguration ability at boot-up (e.g., RTE-IV) always include Interrupt Table entries for all select codes, even if some select codes were not defined in the initial generation.) Each Interrupt Table entry is one word long and can have three possible values: zero, positive, or negative.

1. If the entry is zero, the select code is undefined in the Interrupt Table. Any interrupts on this select code are illegal and cause the following message to be printed:

#### ILL INT xx

where xx is the octal I/O select code number. RTE then clears the interrupt flag on the select code and returns to the suspended process at the point of interruption. (Note that an Interrupt Table entry can also be zero if interrupts on the associated select code are handled by a special routine instead of by CIC and a driver. Refer to the "Writing Privileged Drivers" section later in this manual for more information on this subject.)

- 2. If the contents of the entry are positive, the entry contains the address of the EQT entry associated with the controller on the select code.

- 3. If the contents are negative, the entry contains the negative of the address of the ID segment of the program to be scheduled whenever an interrupt occurs on the select code. If such a program is not dormant when an interrupt occurs on the select code, the following message is output to the system console:

#### SC03 INT xxxxx

where xxxxx is the program name. RTE then clears the interrupt flag on the select code and control is returned to the suspended process at the point of interruption.

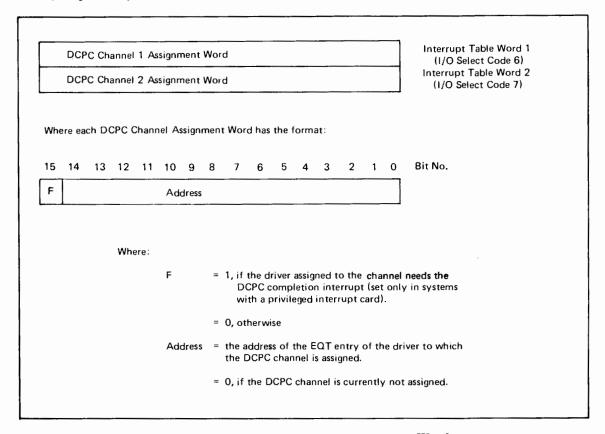

All Interrupt Table entries are located sequentially in memory beginning with the entries for I/O select codes 6 and 7 (DCPC). This format is illustrated in Figure 2-5. There are no entries for I/O select codes 4 and 5 because the system is able to process interrupts from these select codes (power fail interrupts, memory protect violations, etc.) without the need for an Interrupt Table entry. The address of the first word of the table and the number of entries in the table can be found in the Base Page Communications Area.

#### NOTE

The reader should not confuse the interrupt trap cell area of the computer, which is located on base page, with the Interrupt Table of RTE, which is located elsewhere. The interrupt trap cells are those memory locations (4 to 77 octal) to which control is transferred when an interrupt occurs. The Interrupt Table, on the other hand, is merely a convenient way for RTE to record what action CIC should take when an interrupt occurs on a select code under CIC's control.

Figure 2-5. Interrupt Table

#### DRIVER MAPPING TABLE (RTE-IV ONLY)

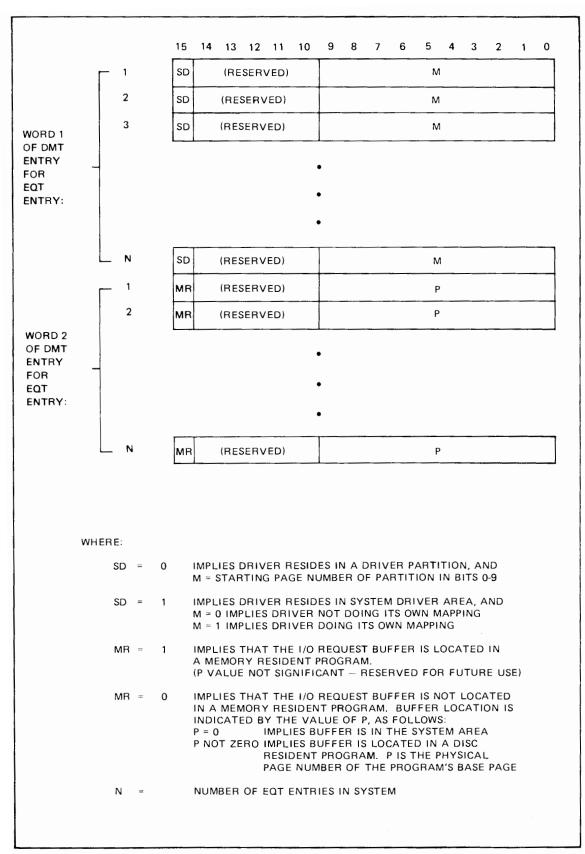

In the RTE-IV Operating System, drivers can be placed in one of two areas: in the System Driver Area (SDA) or in one of the driver partitions. Most standard drivers are placed in driver partitions. The SDA is primarily used for privileged drivers, drivers that do their own mapping, and very large drivers. (For more information on driver placement, refer to the appropriate operating system reference and/or generation manual.)

The Driver Mapping Table (DMT) is used to record where a driver resides in physical memory and other static and dynamic information about the driver and the location of the I/O request buffer.

There is one DMT entry associated with each EQT entry defined at generation time. Each entry is two words long, as illustrated in Figure 2-6. Word 1 is set up at generation time and its contents are never changed. It indicates whether the driver resides in the System Driver Area (SDA) or in a driver partition. If it is in the SDA, it also indicates whether or not the driver is doing its own memory mapping. (See the "Subroutines for Special Mapping Functions" subsection later in this manual.) If the driver is in a partition, word 1 also indicates the starting physical memory page number of the driver partition in which it is located.

Word 2 of the DMT entry is dynamic in nature and is set up at each I/O initialization of the associated EQT entry. This word indicates whether the I/O request buffer is located within a disc resident program, memory resident program, or system area. If a disc resident program is making the request and the I/O request buffer is located within the program (i.e., an unbuffered request), word 2 also indicates the physical memory page number of the disc resident program's base page. This information is used to save time on setting up the proper map when processing interrupts handled by the driver.

Figure 2-6. Driver Mapping Table

#### 2-3. GENERAL OPERATION OF RTE I/O

Input/Output transfers in RTE can be conveniently broken into three parts for discussion: initiation, continuation, and completion. A user program is involved only in the initiation and completion phases; the system I/O processor and the device drivers are involved in all three phases. The following is a simplified discussion of each phase. (As an aid to understanding this explanation, the general flow of events for an unbuffered I/O READ request is illustrated in Figure 2-7.)

Figure 2-7. Unbuffered I/O READ Request

#### I/O INITIATION

A user program makes an EXEC call to initiate I/O transfers. Parameters passed along with this call specify the logical unit, control information, buffer location, buffer length, and type of request (READ, WRITE, or CONTROL) to be made. The user request is channelled to the IOC (Input/Output Control) module of the system by the RTE request processor. The request is checked for legality and rejected if any errors are found. If there are no errors, the logical unit number supplied is used to index into the DRT (Device Reference Table) to determine which I/O controller (EQT entry number) and device (subchannel) are actually being referenced. The I/O request is then linked into the request list for the referenced controller.

If the device controller is available (i.e., no prior requests are pending), the parameters of the request are put into the associated EQT entry, the addresses of the EQT entry words are set into the Base Page Communications Area for convenience, the proper map (System or User) is enabled (performed in systems with Dynamic Mapping only), and the "initiation" section of the driver is called. This section initializes the device controller, starts the data transfer or control function, and returns to IOC.

IOC then returns to the system's dispatching module to begin execution of the highest priority scheduled program. If the operation was successfully initiated by the driver, the data transfer is now under way.

#### I/O CONTINUATION

When the device controller finishes transferring a data word, or block of words, it interrupts the computer. This causes a transfer to one of the interrupt locations in the computer's memory, and the instruction located there is executed. For most I/O devices, this instruction is a JSB LINK,I (where LINK contains the address of the entry point to CIC). Execution of this instruction causes control to be transferred to CIC, the Central Interrupt Control module of the system. CIC obtains the number of the interrupting select code from the computer's Central Interrupt Register and uses it to index into the Interrupt Table.

For those I/O processes operating under the control of CIC and a driver, the Interrupt Table tells CIC which EQT entry is associated with the interrupting select code. CIC looks at the EQT entry, determines which driver is responsible for handling the interrupt, enables the correct map (System or User) in systems with Dynamic Mapping, and calls the driver's "continuation/completion" section to process the interrupt. The driver either accepts the data from the device (read operation) or sends more data to the device (write operation) and restarts the device. Return is then made to CIC with a code indicating that more interrupts are expected. This process (interrupt, CIC, driver, CIC) is repeated once for each word or block of words transferred until the entire transfer is complete.

#### I/O COMPLETION

Eventually the driver will determine that the required amount of data has been transferred and that the I/O process is now complete. The driver then returns to CIC with a special code indicating that the I/O operation is complete and can be terminated; no more interrupts are expected.

CIC, in turn, transfers control back to IOC to terminate the I/O process. IOC causes the program that made the initial I/O request to be placed back into the scheduled list and checks to see if there are any other I/O requests pending for this controller. If at least one request is pending, the initiation section of the driver is again called to begin the next operation. IOC then returns control to the system's dispatching module to begin execution of the highest priority scheduled program.

## WRITING STANDARD RTE DRIVERS

SECTION

Ш

#### 3-1. INTRODUCTION

This section describes in detail the structure, operation, and design of standard RTE drivers. Standard drivers are fairly simple in structure and can generally be used to control most asynchronous devices. They can also be used to control synchronous and high-speed devices if these devices are driven under DCPC control. DCPC processing is also described in this section.

An alternate method for controlling synchronous and high-speed devices is to employ the more complex privileged driver. Section IV of this manual describes the differences in the design of privileged drivers versus standard drivers. Thus, if the user wishes to design a privileged driver, the material in this section should be read and understood before continuing with the privileged driver discussion in Section IV.

Note that the operation of RTE requires that synchronous and high-speed devices be driven either by a standard driver utilizing DCPC transfers, or by a privileged driver. This is necessary to ensure that interrupts from such devices are serviced within the required response time. The reader should keep this requirement in mind when deciding upon the type of driver to be written.

#### 3-2. GENERAL DRIVER STRUCTURE AND OPERATION

An I/O driver, operating under control of the Input/Output Control (IOC) and Central Interrupt Control (CIC) modules of RTE, is responsible for all data transfers between an I/O device controller and the computer. Each driver is written in two functional sections: an initiation section and a continuation/completion section. The initiation section is responsible for starting up the device and initiating the first data transfer. The continuation/completion section is responsible for processing each interrupt generated by the device under its control. This involves accepting data from the device (read operation), sending more data to the device (write operation), and then restarting the device to continue the transfer. Eventually, the continuation/completion section determines that a sufficient amount of data has been transferred and terminates the I/O operation.

A standard RTE driver operates with the interrupt system disabled (or effectively disabled, if the system contains a Privileged Interrupt card. Refer to the "Writing Privileged Drivers" section of this manual.) This means that once a driver is entered to process an interrupt, no other interrupts (except privileged interrupts) can be serviced until the driver completes its operation and returns to CIC. (CIC turns the interrupt system back on to allow other interrupts to occur.) Drivers should therefore be coded as efficiently as possible to minimize the amount of time that the interrupt system is disabled and the processing of other interrupts is delayed.

#### 3-3. DRIVER NAMING REQUIREMENTS

To facilitate the identification of driver programs and entry points, the following naming scheme has been devised. This scheme must be incorporated into the design of all RTE drivers so that the RTE system generator programs can identify the drivers and relocate them in the proper memory area of the operating system.

- a. Driver names must be five characters in length, beginning with the characters "**DV**" and ending with a two-digit octal number (known as the equipment type code of the device).

- b. The initiation and continuation/completion sections must have entry points whose names are four characters in length, beginning with the character "I" or "C" respectively, and ending with the same two-digit octal number used in the driver name.

Thus, if "nn" is the octal equipment type code, Ixnn and Cxnn are the entry point names of the initiation and continuation/completion sections respectively. **DVynn** is the driver name.

The user is allowed some flexibility in the choice of the "x" (in Ixnn and Cxnn) and "y" (in **DVynn**) characters referred to above. This flexibility allows several drivers with the same octal equipment type code to have unique names and entry points. The rules for the choice of "x" and "y" are:

```

If "y" is "R" then "x" = "."

If "y" is not "R" then "x" = "y"

```

Using the above rules, a driver named DVR66 has entry points I.66 and C.66. A driver named DVA66 has entry points IA66 and CA66.

The octal equipment type code (nn) can be any octal number between 00 and 77. A table of "standard" type codes is given in Figure 2-1. Care should be taken to choose the type code and/or "x" and "y" characters so that new driver names and entry points do not conflict with those of any standard HP drivers or other user written drivers present in the system.

#### 3-4. INITIATION SECTION

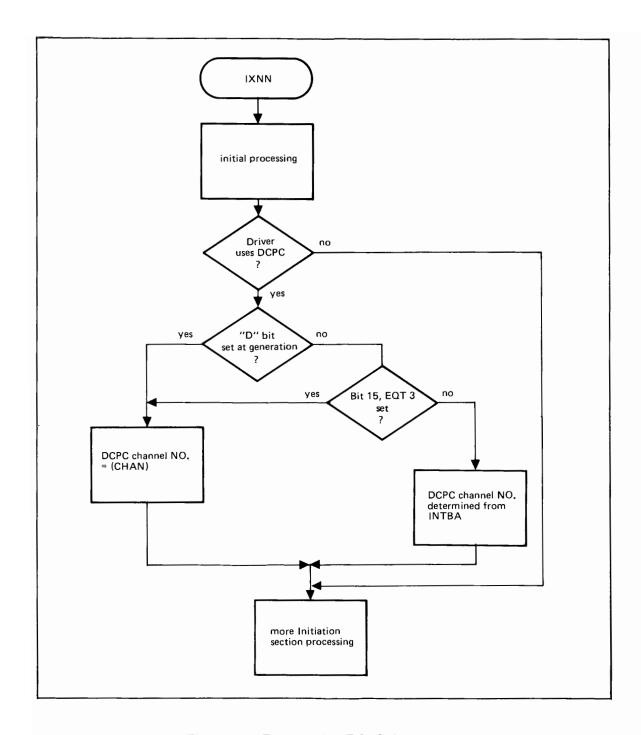

The IOC module of RTE calls the driver initiation section when an I/O transfer is initiated. (Note that the initiation section may also be entered when a DCPC channel is assigned by IOC in response to a dynamic DCPC request by the driver. Refer to the "DCPC Processing" subsection of this manual.) Prior to actually entering the driver initiation section, IOC sets up all the information needed by the driver to process the call in the associated EQT entry and in the Base Page Communications Area, as follows:

a. Locations EQT1 through EQT15 in the Base Page Communications Area are set to contain the addresses of each word of the EQT entry associated with the call. Base page word EQT1 is set to contain the address of EQT entry word 1, base page word EQT2 is set to contain the address of EQT entry word 2, and so on. If the driver uses DCPC (that is, if bit 15 of EQT entry word 4 is set), IOC also assigns a DCPC channel to the driver and stores the DCPC channel number in base page word CHAN.

- b. Words 6 through 10 of the EQT entry pointed to by the Base Page Communications Area are set to contain the request parameters from the user's EXEC call (request code, subfunction, buffer address, buffer length, and optional parameters, if present). Note that EQT entry word 6 (CONWD) contains the CONWD from the user's EXEC call, modified to contain the request code in bits 0 and 1 in place of the logical unit. The subchannel being referenced by the call is placed into bits 6 through 10 of EQT entry word 4.

- c. CIC also sets up and enables the correct map (System or User) needed by the driver to process the call. (This step is performed in systems with Dynamic Mapping only.)

After performing these tasks, IOC enters the driver directly via a jump subroutine to the initiation entry point Ixnn (JSB Ixnn). Upon entry, the A-register contains the I/O select code of the controller being referenced in the call. (This same information is present in bits 0 through 5 of EQT entry word 4.) Later, when the driver has completed (or rejected, if necessary) the initialization procedure, it must return to IOC via a jump indirect through the Ixnn entry point (JMP Ixnn,I).

Once entered, the driver is free to use EQT entry words 6 through 13 in any way, but words 1 through 4 and 14 must not be altered. If an EQT entry extension was specified at generation, the space in the extension is also available to the driver. In this case words 12 and 13 (which define the extension) must not be modified. The driver can also update the status field in word 5, if appropriate, but this must be done without altering the rest of word 5. Finally, EQT entry word 15 may be modified, if desired, to set a time-out value for the device. (Refer to the "I/O Controller Time-Out" subsection in this manual.)

#### FUNCTIONS OF THE INITIATION SECTION

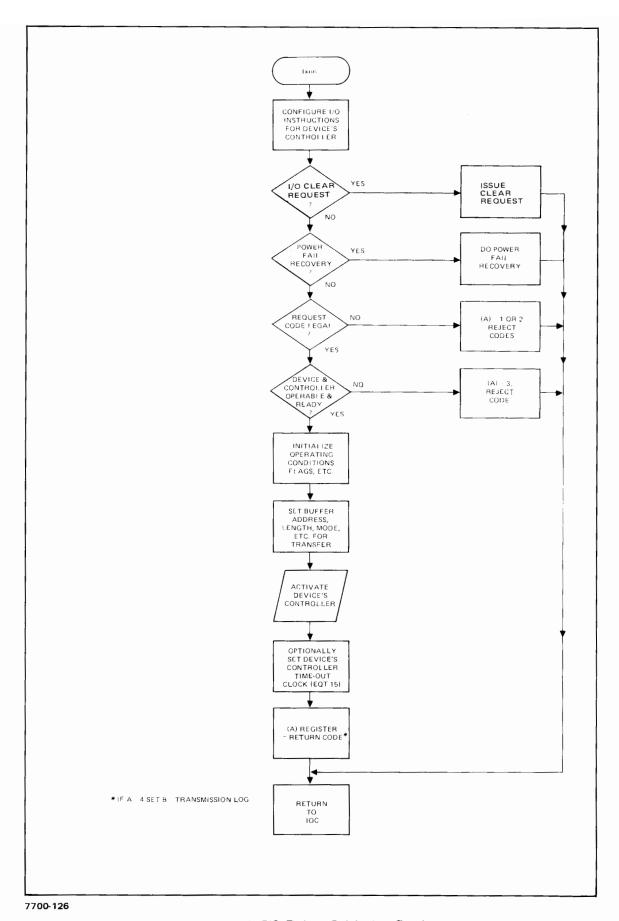

As part of the general I/O structure of RTE, the initiation section of a standard driver performs the functions illustrated in Figure 3-1. A more detailed description of the initiation section functions is given below.

- a. Checks for power fail/automatic restart entry by examining bit 15 of EQT entry word 5, which is set to 1 only on this type of entry. If bit 15 is set, the appropriate power fail/automatic restart processing should be done. This check need only be made by drivers that are designed to process power fail interrupts (as described in the "Power Fail Processing subsection of this manual).

- b. Rejects the request by following the procedure described in step "g" if:

- 1. A status check of the device or controller indicates that it is inoperable, or

- 2. The request code or other parameters are illegal.

Figure 3-1. I/O Driver Initiation Section

- c. Configures all I/O instructions in the driver to reference the specific I/O select code (and DCPC channel, if used) of the device controller.

- d. Initializes DCPC, if used. (Refer to the "DCPC Processing" subsection of this manual.)

- e. Initializes software flags and activates the device controller. All variable information pertinent to the transmission must be saved in the EQT entry associated with the controller because the driver may be called for another controller before the first operation is complete.

- f. Optionally sets the device controller time-out clock (EQT entry word 15) to modify the time-out value inserted there by the system. (Refer to the "I/O Controller Time-Out" subsection of this manual.)

- g. Returns to IOC (via **JMP I***xnn*,**I**) with the A-register set to indicate initiation or rejection (and the cause of the rejection) as follows:

If A = 0 the operation was initiated successfully.

If A = 1,2,3 The operation was rejected, where:

1 = read or write illegal for device

2 = control request illegal or undefined,

3 = equipment malfunction or not ready

If A = 4 the operation was immediately completed. This means that the driver was able to completely satisfy the request without the need of a subsequent interrupt and that the program making the I/O call can be rescheduled immediately. The B-register should be set to the positive number of words or characters (depending upon which the user specified) transferred. This value is known as the transmission log.

If A = 5 a DCPC channel is required but none was assigned by IOC. This can only occur when the "DCPC channel required" bit is not set in the EQT entry, and the driver decides that it needs a DCPC channel to process this specific call. (Refer to the "DCPC Processing" subsection of this manual.)

If A=6 a DCPC channel was assigned by IOC but the driver did not use it and wants to give it up. After IOC deallocates the channel, processing continues as for a successful initiation return (A=0). (RTE-IVB only.)

If A = 7 - 99

the program making the I/O request is aborted (unless the no-abort bit was set in the call), and an I/O error message is printed on the system console. (Note that this return can be used for unbuffered user I/O requests only. This therefore excludes the use of return codes 6 through 99 on any Class, buffered or system I/O request.) The error message has the following format:

IOxx yyyyy NNNNN ABORTED

where: xx = the return code from the driver (decimal 06 to decimal 99).

yyyyy = the address of the aborted I/O request in program NNNNN, and

NNNNN =the name of the program that made the I/O request.

This type of return can be used by drivers to generate their own I/O error messages at the system console. Note that certain codes are reserved for system use, as follows:

| Return Code | Reserved for                         |

|-------------|--------------------------------------|

| 7 - 59      | HP system modules and system drivers |

| 60 - 99     | user written drivers                 |

#### 3-5. CONTINUATION/COMPLETION SECTION

The CIC module of RTE calls the continuation/completion section of a driver whenever an interrupt is recognized on an I/O controller associated with the driver. Before calling the driver to process the interrupt, CIC issues a clear flag instruction (CLF) to the interrupting select code, sets the addresses of the associated EQT entry into the Base Page Communications Area, and sets the interrupt source code (I/O select code of interrupting controller) into the A-register. (The interrupting I/O select code address is also available in EQT entry word 4.)

CIC also sets up and enables the correct map (System or User) needed by the driver to process the call. (This step is performed in systems with Dynamic Mapping only.) The driver is then entered with the correct map enabled by executing a jump subroutine to the continuation/completion section of the driver at entry point Cxnn (JSB Cxnn). This call has the following format:

| Location | Action                                          |

|----------|-------------------------------------------------|

|          | (Set A-register equal to interrupt source code) |

| P        | JSB Cxnn                                        |

| P+1      | Completion return from Cxnn                     |

| P+2      | Continuation return from Cxnn                   |

| P+3      | Get/give up DCPC continuation return from       |

|          | Cxnn (RTE-IVB only)                             |

| 3.6      |                                                 |

The return points from **Cxnn** to CIC indicate whether:

- 1. the transfer has been completed.

- 2. the transfer is continuing (i.e., further interrupts are expected from the device controller).

- 3. the driver is requesting the allocation or deallocation of a DCPC channel.

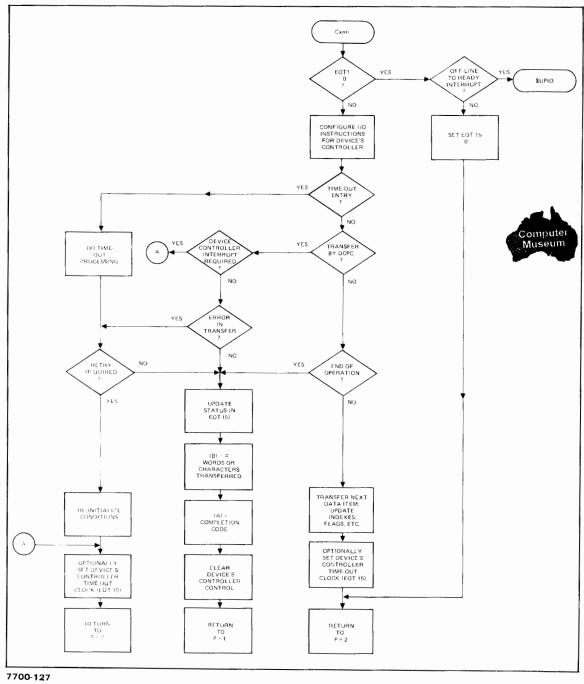

The continuation/completion section of the driver is flowcharted in Figure 3-2 and performs the following functions. Note that steps "a" through "e" are always executed whenever the driver is entered at Cxnn. Then, depending on whether the I/O operation is now complete or is still continuing, the driver executes either step "f" (completion return) or step "g" (continuation return) respectively.

Figure 3-2. I/O Driver Continuation/Completion Section

- a. Checks whether bits 14 0 of EQT entry word 1 (the controller I/O request list pointer) equal zero. If so, a spurious interrupt has occurred (i.e., no I/O operation was in progress on the controller). The driver can handle the spurious interrupt in one of two ways:

- 1. Ignore the interrupt by setting EQT entry word 15 (the time-out clock) to zero to prevent time-out and making a continuation return as described in step "g" below.

- 2. Ignore the interrupt and have RTE display a message by making a completion return as described in step "f" below. No special A-register return value is needed. Upon return from the driver, RTE looks at the I/O request list pointer and, if the pointer is zero, displays the following message on the system console (where the "sc" indicates the interrupting select code):

#### ILL INT sc

- b. If the interrupt is valid (i.e., bits 14 0 of word 1 are non-zero), the driver configures all I/O instructions in the continuation/completion section to reference the interrupting select code.

- c. Checks to see if a time-out has occurred on the device by checking bit 11 of EQT entry word 4. If this bit is set, the device has timed-out, and any required time-out processing should be done. Note that this check need only be made by drivers that are designed to process time-out interrupts (as described in the "I/O Controller Device Time-Out" subsection of this manual). Drivers not processing time-out are not entered on device time-out.

- d. If both the DCPC and the device controller interrupts are expected, but only the device controller interrupt is significant, the DCPC interrupt can be ignored by making a continuation return to CIC as described in step "g" below. (Refer to the "DCPC Processing" subsection of this manual for a method to suppress the DCPC interrupt entirely.)

- e. Performs the input or output of the next data item if the device is driven under program control. One of three possible actions is then taken:

- 1. If the transfer is not complete, the driver follows the procedure described in step "g" below to make a continuation return.

- 2. If the transfer is complete, the driver follows the procedure described in step "f" below to make a completion return.

- 3. If the driver detects a transmission error, it can reinitiate the transfer and attempt a retransmission. A counter for the number of retry attempts can be kept in the EQT entry. After initiating each retry, the driver makes a continuation return to CIC as described in step "g" below.

- f. (Completion Return.) At the end of a successful transfer or after completing the retry procedure, the driver performs the following steps before returning to CIC:

- 1. Sets the actual or simulated device controller status into bits 7 through 0 of EQT entry word 5 without altering the rest of word 5.

- 2. Sets the number of words or characters (depending on which the user requested) transmitted into the B-register. This value is known as the transmission log.

- 3. Clears the device controller (and DCPC if used).

Sets the A-register to indicate successful or unsuccessful completion and the reason, as follows:

If A = 0 the operation was successfully completed.

If A = 1,2,3,4 the operation was not completed, where:

1 = device or controller malfunction or not ready

2 = end-of-tape or end-of-information

3 = transmission parity error

4 = device time-out

- 5. Return to CIC at P+1 (JMP Cxnn, I).

- g. (Continuation return.) When the driver wishes to continue the transfer (i.e., additional interrupts are expected), the driver performs the following steps before returning to CIC at P+2:

- 1. Sets the device controller (and DCPC if used) for the next transfer or retry.

- 2. Optionally sets the device time-out clock (EQT entry word 15) to modify the value inserted there by the system. (Refer to the "I/O Controller Time-Out" subsection of this manual.)

- 3. Returns to CIC at P+2 or (for RTE-IVB) P+3 as follows:

ISZ Cxnn

JMP Cxnn,I

or

ISZ Cxnn

ISZ Cxnn

JMP Cxnn.I

For the P+3 return, the content of the A-register determines the action taken by the system. The A-register should be set as follows:

A = 5 request the allocation of a DCPC channel. After assigning a DCPC channel, the system will reenter the driver at Lxnn.

A=6 request the deallocation of a DCPC channel. After releasing the DCPC channel, the system continues processing as if this were a P+2 continuation return.

#### 3-6. DEVICE CLEAR ON PROGRAM ABORT

If an I/O suspended program is aborted while waiting for a controller, the system attempts to clear the controller by issuing a clear control request to the driver (i.e., request code 3, subfunction code 00, as indicated in EQT entry word 6). All drivers written for use in RTE must be prepared to handle this request even if no other control requests are supported for the controller.

If the controller can be cleared without interrupt (i.e., immediately), the driver should perform the clear operation and return to IOC with the A-register equal to 2 (control request illegal) or 4 (immediate completion). Either return is sufficient in this case; they are both treated equivalently by the system.

If an interrupt is required, the driver should return with the A-register equal to 0. In this case, the system forces a one second time-out for the controller. When the device controller interrupts, the driver should complete the clear operation and make a successful completion return

(A-register=0) to CIC at P+1. However, if the interrupt does not occur within the one second time-out, the system itself issues a clear control command (CLC) to the controller's select code(s). Note that in this case the driver is not entered to process the time-out even if it had previously set the "driver processes time-out" bit in EQT entry word 4. (Refer to the "I/O Controller Time-Out" subsection in this manual.)

# 3-7. I/O CONTROLLER TIME-OUT

Each I/O controller can have a time-out clock to prevent indefinite I/O suspension. Indefinite I/O suspension can occur when a program initiates I/O, and the device controller fails to return a flag indicating that the transfer is complete. This can occur as the result of either a hardware malfunction or improper program encoding. Without the controller time-out, the program making the I/O call would remain in I/O suspension indefinitely, awaiting the completion indication from the device controller.

EQT entry words 14 and 15 function as an I/O controller's time-out clock. EQT entry word 15 is the actual working clock. Prior to each call to the driver, word 15 is set to a value "m," where "m" is a negative number of ten millisecond time intervals. Thereafter, this counter is incremented by one at each ten millisecond tick of the system's real-time clock. If the controller does not interrupt within the required time interval (i.e., before the counter in EQT entry word 15 goes to 0), it is considered as having "timed-out."

The EQT entry word 15 clock for each controller can be individually set by either of the following two methods:

- a. The system always inserts the contents of EQT entry word 14 (a negative number) into EQT entry word 15 before the initiation or continuation/completion section of a driver is entered. Word 14 can be preset to "m" by entering a time-out value during the EQT entry phase of generation, or it can be set or modified on-line with the TO operator request.

- b. When the driver initiates I/O and expects to be entered due to a subsequent interrupt, the driver itself can set the value "m" into EQT entry word 15 just before it exits. The value "m" can either be coded permanently into the driver or can be passed to the driver as an I/O request parameter.

#### NOTE

The system always inserts the contents of EQT entry word 14 into EQT entry word 15 before entering a driver, with the following exceptions: 1) if an initiation call is being made and word 15 is already non-zero, it is not reset, and 2) if a continuation call is being made and word 14 is zero, word 15 is not reset. In any case, a time-out value inserted by the driver directly into word 15 overrides any value previously set by the system.

A time-out value of zero is equivalent to not using the time-out feature for a particular controller. If a time-out parameter is not entered, its value remains zero and time-out is disabled for the controller.

Time-out is enabled for a controller only while the controller is processing an I/O request. The working time-out clock (EQT entry word 15) is set as described above. If the controller does not time-out, the clock is then cleared by the system after one of these driver returns:

- 1. An Initiation return indicating a rejected initiation request (A-register not equal to zero).

- 2. A Completion return.

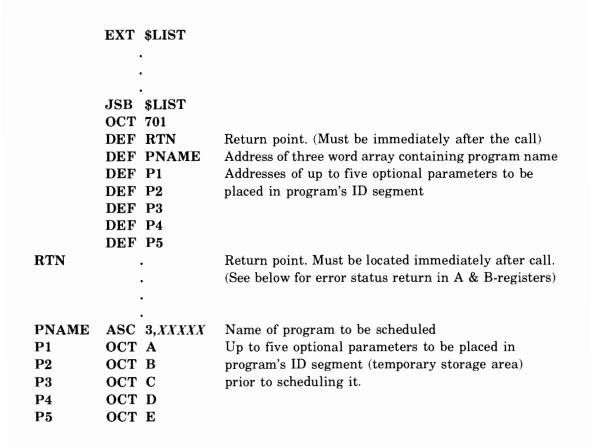

## DRIVER PROCESSING OF TIME-OUT