### PRINCIPLES OF OPERATION

DPC 1200 SERIES

CHAINTRAIN™ LINE PRINTERS

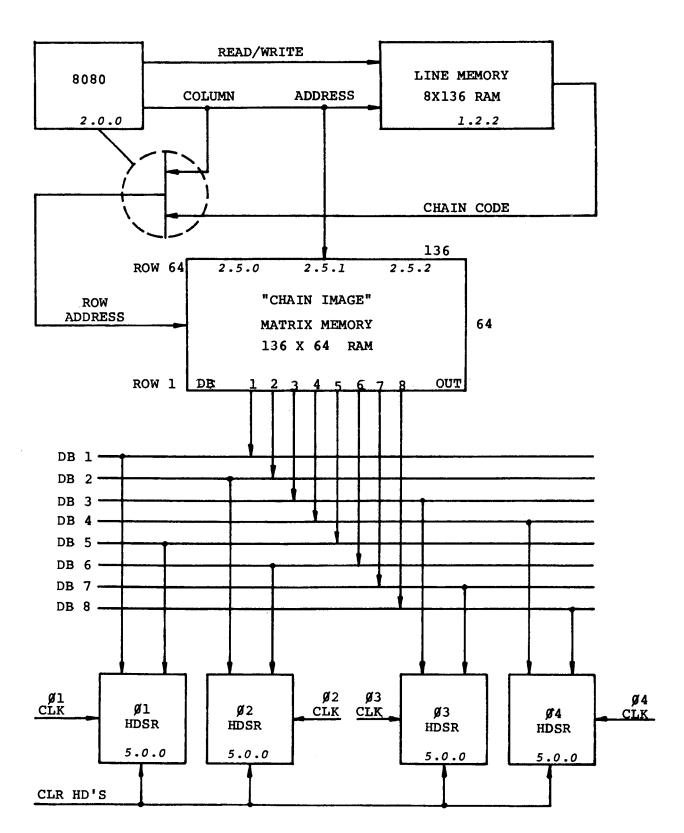

Models CT-1260, CT-1290, and CT-1210

MAY 1979

Data Printer Corp © 1979

DATA PRINTER CORP 99 Middlesex Street Malden, MA 02148

Tel: (617 321-2400 TWX: 710-348-0794

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

#### **PREFACE**

The operating principles of three of the four models in the DPC (Data Printer Corp) 1200 CHAINTRAIN™ Line Printer Series (Models CT-1260, CT-1290, and CT-1210) are described in this manual entitled <u>Principles of Operation</u> (DPC Form 1260/90/10-2). Its purpose is to prepare you to perform the maintenance procedures outlined in the companion <u>Maintenance Instructions</u> manual (DPC Form 1260/90/10-3).

The operating principles and maintenance procedures for the fourth model in the DPC 1200 Series (Model CT-1200) are described in a similar set of manuals, entitled <u>Principles of Operation</u> (DPC Form 1200-2) and <u>Maintenance Instructions</u> (DPC Form 1200-3).

Two additional manuals, each of which covers all four models in the DPC 1200 Series, are also included in your printer's documentation package: Operating Instructions (DPC Form 1200-1), and Illustrated Parts Breakdown and Circuit Diagrams (DPC Form 1200-4).

Additional copies of any of these manuals can be obtained from your local DPC representative or by writing directly to Data Printer Corp at the address below. The price of each manual is listed in the current issue of the <u>Customer Services Catalog</u>, a free copy of which can be obtained by writing or phoning the DPC Customer Services Department in Malden, Massachusetts.

The postage-paid "Readers' Comments" card at the end of this manual is provided for your convenience if you wish to suggest improvements to this manual. We welcome your comments.

DATA PRINTER CORP

99 Middlesex Street

Malden, MA 02148

Tel: (617) 321-2400

|  |  | · . |  |

|--|--|-----|--|

## TABLE OF CONTENTS

| Section                                                                                                            |                                                                                                                                                                                                                                                                                                                                                 | Page No.                                                                                          |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|                                                                                                                    | CHAPTER 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                         |                                                                                                   |

| 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.3<br>1.4                                                                         | OBJECTIVES  METHOD OF TREATMENT  Appendices  CD and IPB References  FIELD SERVICE PHILOSOPHY  MODEL IDENTIFICATION                                                                                                                                                                                                                              | 1-1<br>1-1<br>1-2<br>1-3<br>1-5<br>1-6                                                            |

|                                                                                                                    | CHAPTER 2. PRINT SYSTEM OPERATION                                                                                                                                                                                                                                                                                                               |                                                                                                   |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8<br>2.3<br>2.3.1<br>2.3.2<br>2.4 | INTRODUCTION.  PRINT MECHANISM.  Yoke Latch and Interlock Switches.  Print Hammers and Actuators.  DPC CHAINTRAIN™ Type Carrier.  Hammer-to-Character Alignment.  Character and Index  Strobe Transducers.  Impression Control.  Phasing Control.  Hammer Driver Cabling.  RIBBONFEED MECHANISM.  Ribbonfeeding and Reversing.  Ribbon Skewing. | 2-1<br>2-3<br>2-5<br>2-12<br>2-18<br>2-21<br>2-23<br>2-24<br>2-28<br>2-29<br>2-29<br>2-30<br>2-30 |

| 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12        | Paper Tractors  Vertical Form Tension Control  Tractor Positioning System  Paper Guide/Scale  Stepper Motor Tractor Drive System  Infinite Forms Position Control  Paper Low Switch  Paper Motion Sensor  Paper Receptical  Paper Puller  Static Eliminator  Vertical Format Units                                                              | 2-32<br>2-34<br>2-34<br>2-36<br>2-36<br>2-39<br>2-39<br>2-40<br>2-42<br>2-42<br>2-43              |

| 2.4.13                                                                                                             | Optional 6/8 LPI Switch                                                                                                                                                                                                                                                                                                                         | 2-44                                                                                              |

# TABLE OF CONTENTS

| Section          |                                                                                                                                                                                                                                                                                                                                                                          | Page No.                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|                  | CHAPTER 3. CONTROL SYSTEM OPERATION                                                                                                                                                                                                                                                                                                                                      |                                                                              |

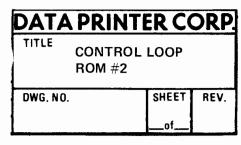

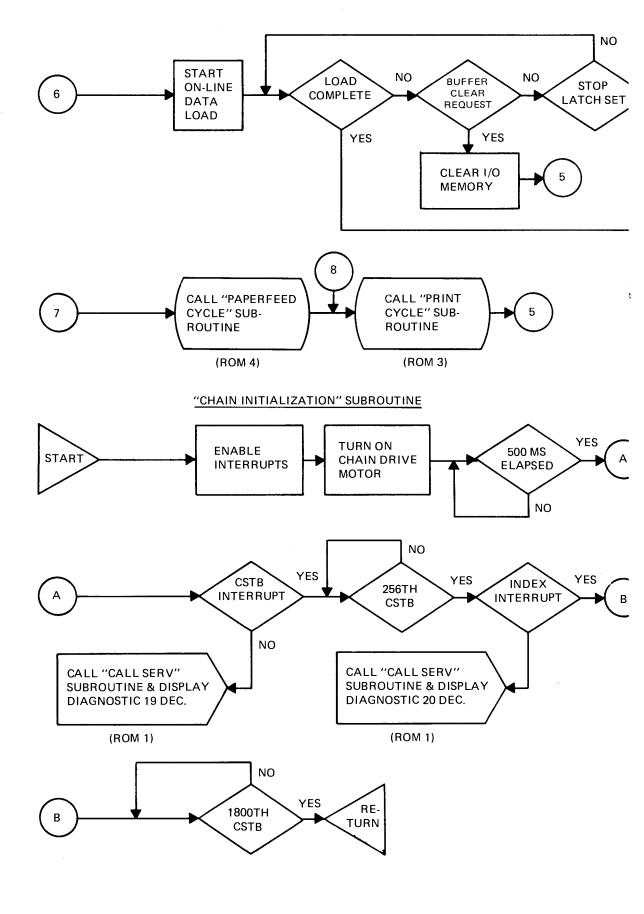

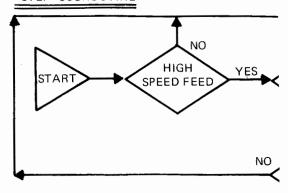

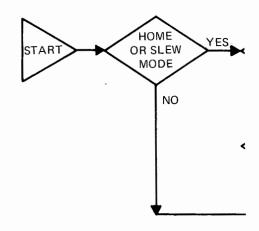

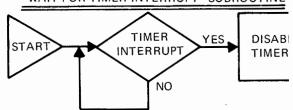

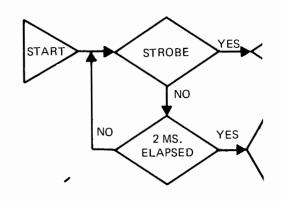

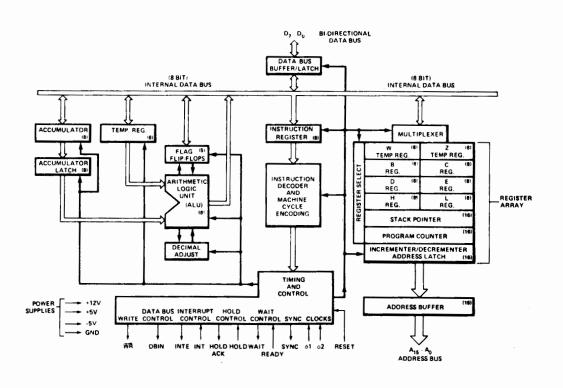

|                  | CONTROL SYSTEM ARCHITECTURE.  CONTROL SYSTEM OPERATING PROGRAM.  ROM #1 - INITIALIZATION.  ROM #2 - CONTROL LOOP.  ROM #3 - PRINT CYCLE.  ROM #4 - PAPERFEED.  ROM #5 - VF SAMPLE.  ROM #6 - PAPERFEED INTERRUPTS.  ROM #7 - VF TAPE READ CHECK.  INPUT/OUTPUT BOARD.  RANDOM ACCESS MEMORY (RAM).  INPUT PORTS.  PRIORITY INTERRUPT CONTROL UNIT (PICU).  OUTPUT PORTS. | 3-4<br>3-5<br>3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-10<br>3-11<br>3-11 |

|                  | APPENDICES                                                                                                                                                                                                                                                                                                                                                               |                                                                              |

| A<br>B<br>C<br>D | TYPICAL OPERATION PROGRAM FLOW CHART DIAGNOSTIC ERROR CODES INTEL DATA SHEETS ABBREVIATIONS                                                                                                                                                                                                                                                                              | B-1                                                                          |

## LIST OF ILLUSTRATIONS

| Figure                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page No.                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                     | CHAPTER 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                 |

| 1-1                                                                                                                                                                 | Nameplate Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-8                                                                                                                                                             |

|                                                                                                                                                                     | CHAPTER 2. PRINT SYSTEM OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                 |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12<br>2-13<br>2-14<br>2-15<br>2-16<br>2-17<br>2-18<br>2-19<br>2-20<br>2-21<br>2-22 | Print Mechanism with Yoke Open Yoke Latch and Interlock Switches Eight-Up Hammer Module Straight and Offset Hammer Actuators Actuator Tip Interlace Pattern Hammer in Resting Position Location of Flight Timing Screws DPC CHAINTRAINTM Lateral Type Carrier Typical 64-Character Array Motor/Flywheel Drive Assembly Slug Guide Rails and Ribbon/Slug Guides Vacuum Cleaning System Four-to-Three Alignment Ratio Two Consecutive Four Phase Alignment Sequence CSTB and INDEX Variable Reluctance Transducers Phasing Control Assembly Phasing Control Operation Paperfeed Path Paperfeed Tractors. Vertical Form Tension Control. Stepper Motor Tractor Drive System Paper Motion Sensor. | 2-2<br>2-4<br>2-6<br>2-7<br>2-9<br>2-11<br>2-13<br>2-14<br>2-14<br>2-16<br>2-17<br>2-19<br>2-20<br>2-22<br>2-25<br>2-26<br>2-31<br>2-33<br>2-35<br>2-37<br>2-41 |

|                                                                                                                                                                     | CHAPTER 3. CONTROL SYSTEM OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                 |

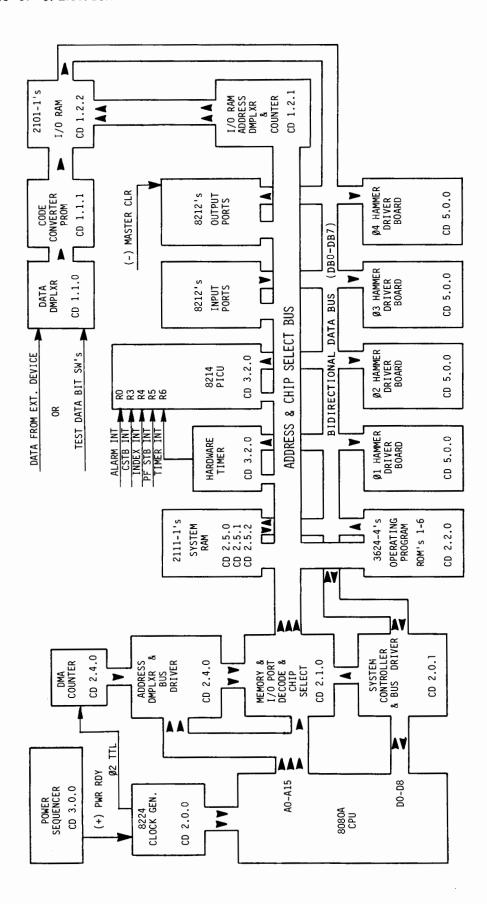

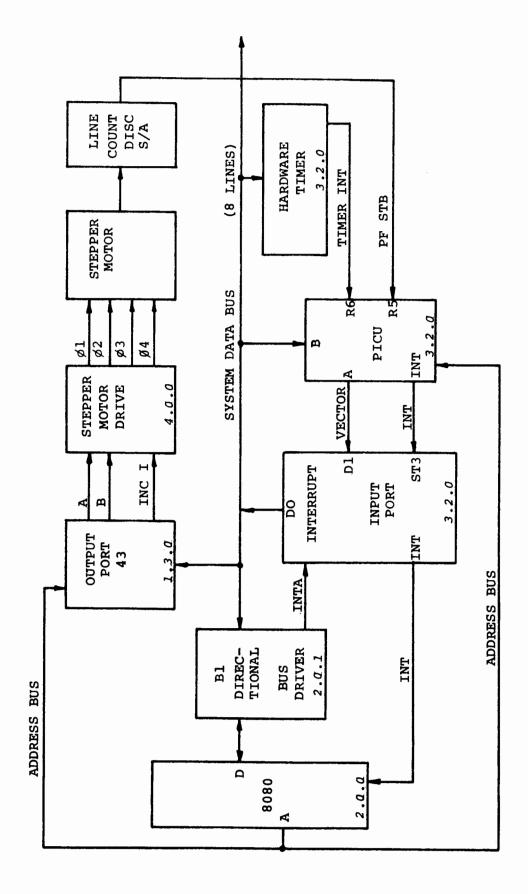

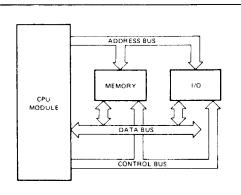

| 3-1<br>3-2<br>3-3                                                                                                                                                   | System Architecture (DDC Models CT-1260, CT-1290, CT-1210)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-2<br>3-15<br>3-16                                                                                                                                             |

### LIST OF TABLES

| <u>Table</u> |                                                                         | Page No.     |

|--------------|-------------------------------------------------------------------------|--------------|

|              | CHAPTER 1. INTRODUCTION                                                 |              |

| 1-1          | THROUGHPUT IN LINES PER SECOND (LPS)                                    | 1-8          |

|              | CHAPTER 2. PRINT SYSTEM OPERATION                                       |              |

| 2-1          | HAMMER ACTUATOR CABLING                                                 | 2-29         |

|              | CHAPTER 3. CONTROL SYSTEM OPERATION                                     |              |

| 3-1<br>3-2   | Input PortsOutput Ports                                                 | 3-12<br>3-13 |

|              | APPENDICES                                                              |              |

| B-1<br>B-2   | "CALL SERV" DIAGNOSTIC ERROR CODES" "V.F. ERROR" DIAGNOSTIC ERROR CODES | B-1<br>B-3   |

# CHAPTER 1 INTRODUCTION

#### 1.1 OBJECTIVES

This manual describes the principles of operation of three of the four models in the DPC 1200 CHAINTRAIN<sup>™</sup> Line Printer Series: CT-1260, CT-1290, and CT-1210. Its purpose is to prepare you to perform the maintenance and repair operations described in the companion Maintenance Instructions manual (DPC Form 1260/90/10-3). 1

Written from a Field Service point of view, the chapters that follow present material in a logical, step-by-step way in order to build the kind of understanding that makes it possible to service a printer with confidence and dispatch. Model- and option-related differences are pointed out where appropriate so that careful reading will enable you to understand the operation any CT-1260, CT-1290, or CT-1210 printer, however configured.

#### 1.2 METHOD OF TREATMENT

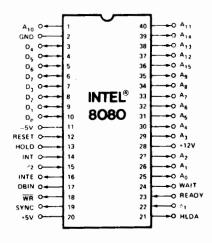

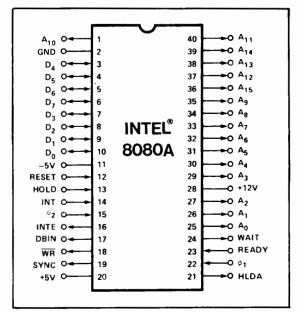

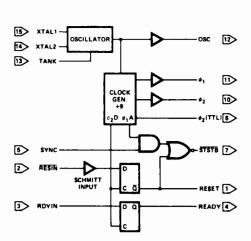

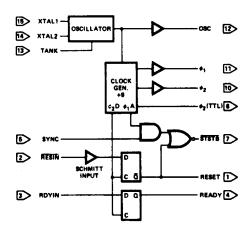

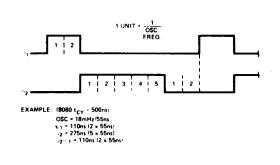

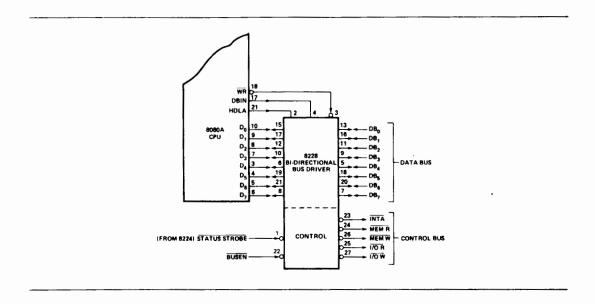

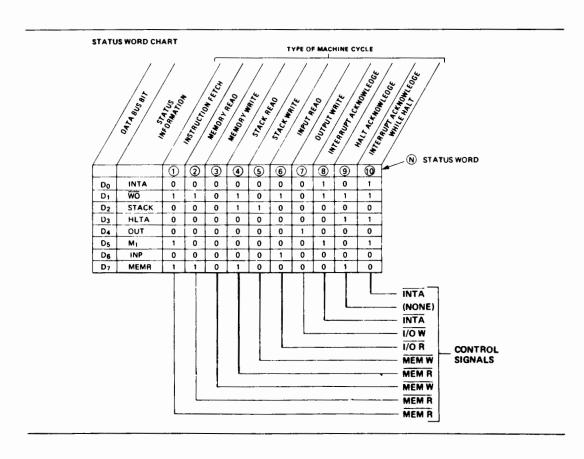

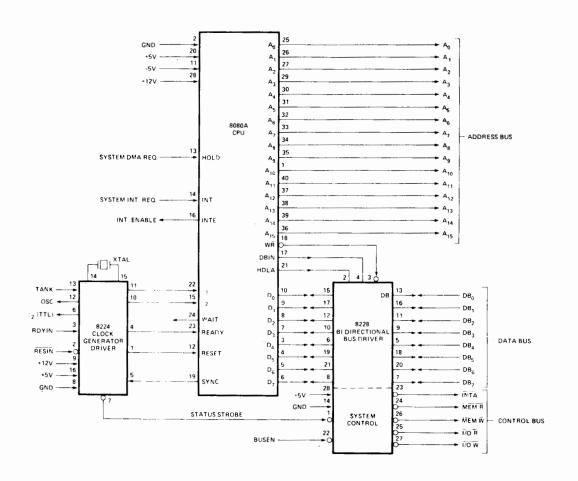

Although each of the three models dealt with in this manual can be configured in a variety of ways, all consist of two basic subsystems: (1) a electromechanical, back-impact  $\underline{Print}$   $\underline{System}$ , based on the DPC CHAINTRAIN<sup>™</sup> lateral type carrier; and (2) a programmable  $\underline{Control}$   $\underline{System}$ , based on an 8080A CPU.

For purposes of this discussion, the Print System shall be understood to include all mechanisms and related mechanical adjustments needed to print a line of data and feed ribbon and paper. The Control System shall be under-

<sup>&</sup>lt;sup>1</sup>The fourth model in this series, the CT-1200, differs sufficiently in operation from the other three to warrant treatment in a separate <u>Principles of Operation manual</u> (DPC Form 1200-2). Its companion <u>Maintenance Instructions manual is DPC Form 1200-3.</u>

stood to include all drive, control, and interface circuitry, power supplies and power-sequencing circuitry, and all indicators and switches needed to make the Print System perform its printing and paperfeeding tasks. Because the nature of the Control System is determined in large part by the nature of the Print System it must control, a detailed description of the Print System (Chapter 2) precedes a detailed description of the Control System (Chapter 3).

Some familiarity with the operation of back-impact printer mechanisms would be helpful, but this manual is not written in a way that makes such knowledge essential. If you are new to printer mechanisms, you will find the footnotes in Chapter 2 informative.

Because printers in the DPC 1200 Series are microprocessor-controlled, understanding this manual requires some familiarity with the operation of small microcomputer systems. The reference books mentioned at the beginning of Appendix C provide helpful background material if you are unfamiliar with the operation of these devices.

If you have not already done so, read through the <u>Operating Instructions</u> manual (DPC Form 1200-1) before proceeding: this manual was written on the assumption that you have at least an operator's familiarity with DPC 1200 Series printers. Read also the "INTRODUCTION" to the <u>Illustrated Parts Breakdown and Circuit Diagrams</u> manual (DPC Form 1200-4) so that you will be able to locate and understand drawings referred to in this manual.

#### 1.2.1 Appendices

Appendices containing useful reference material have been placed at the back of this manual for your convenience. They are as follows:

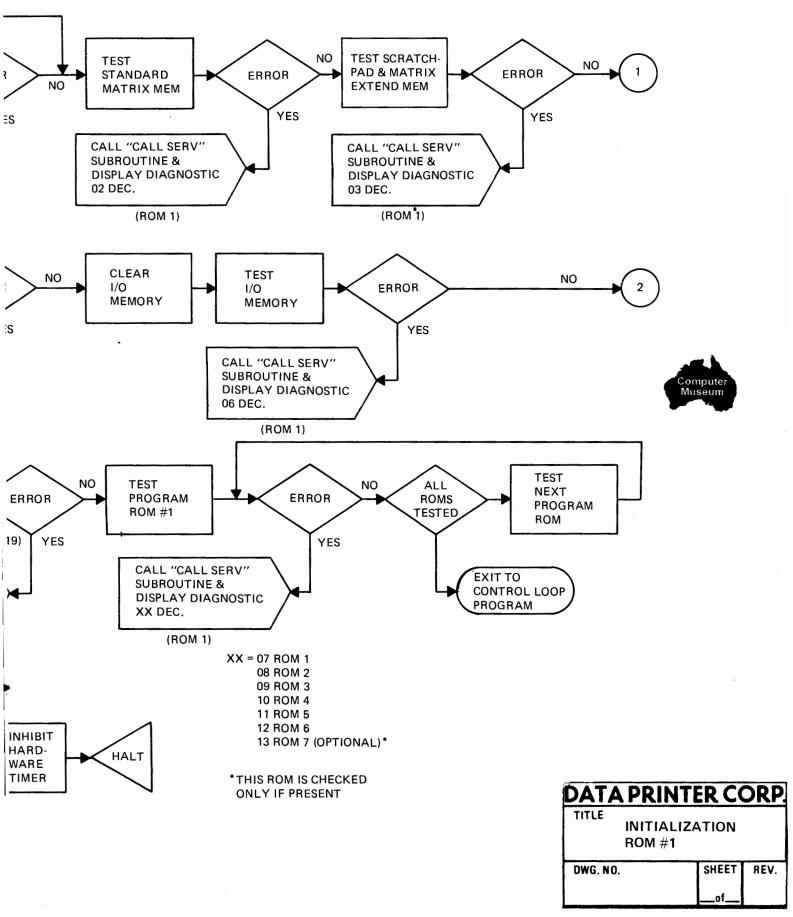

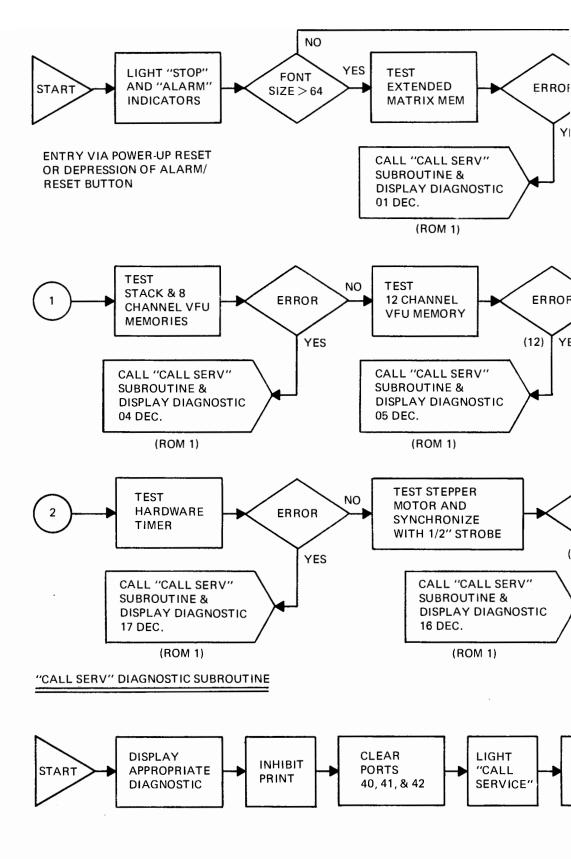

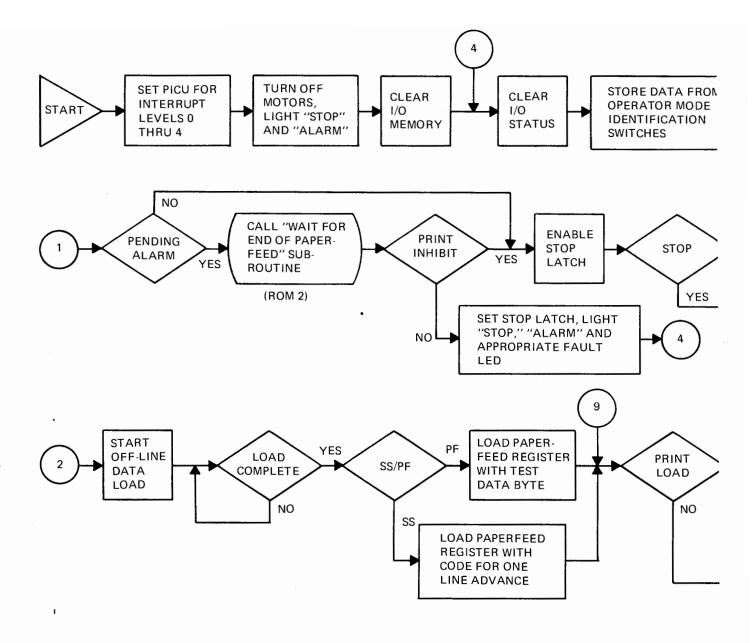

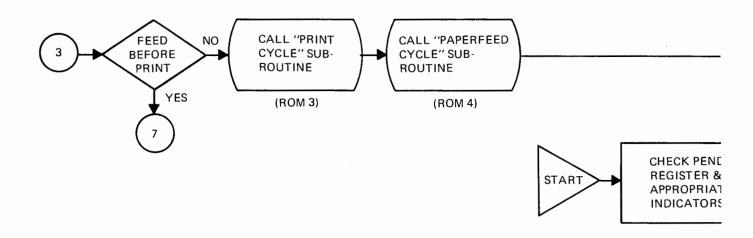

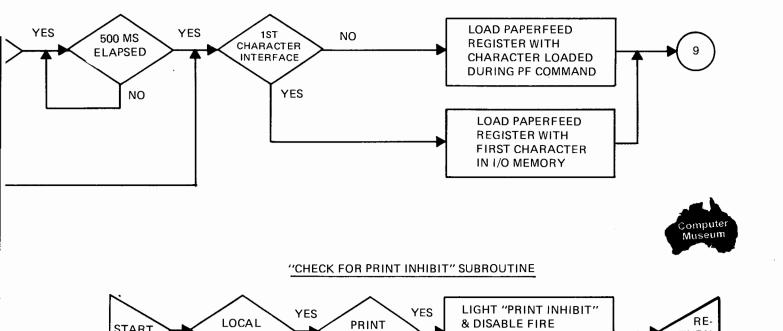

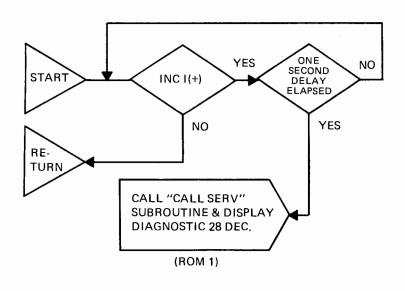

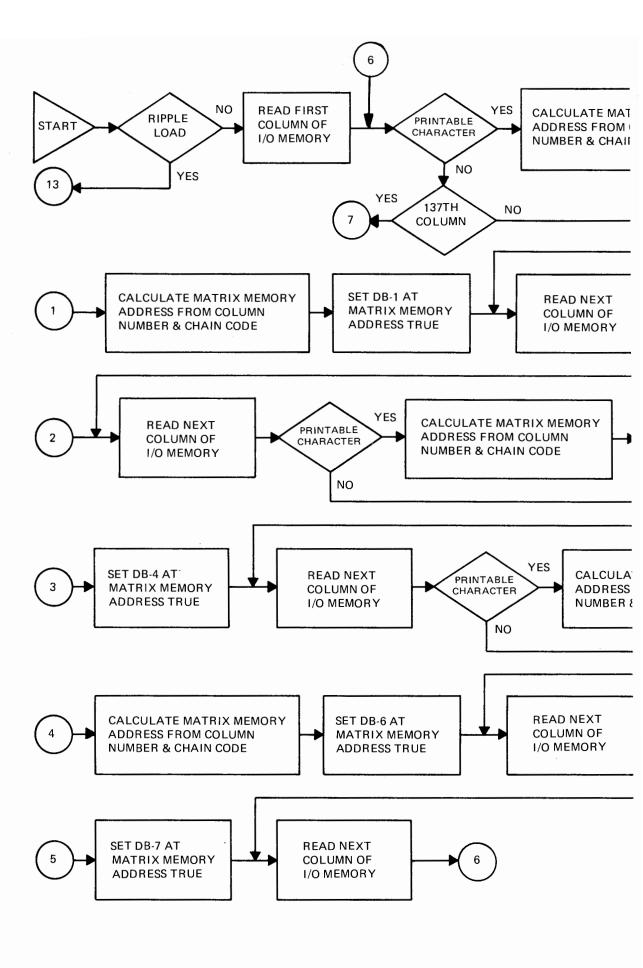

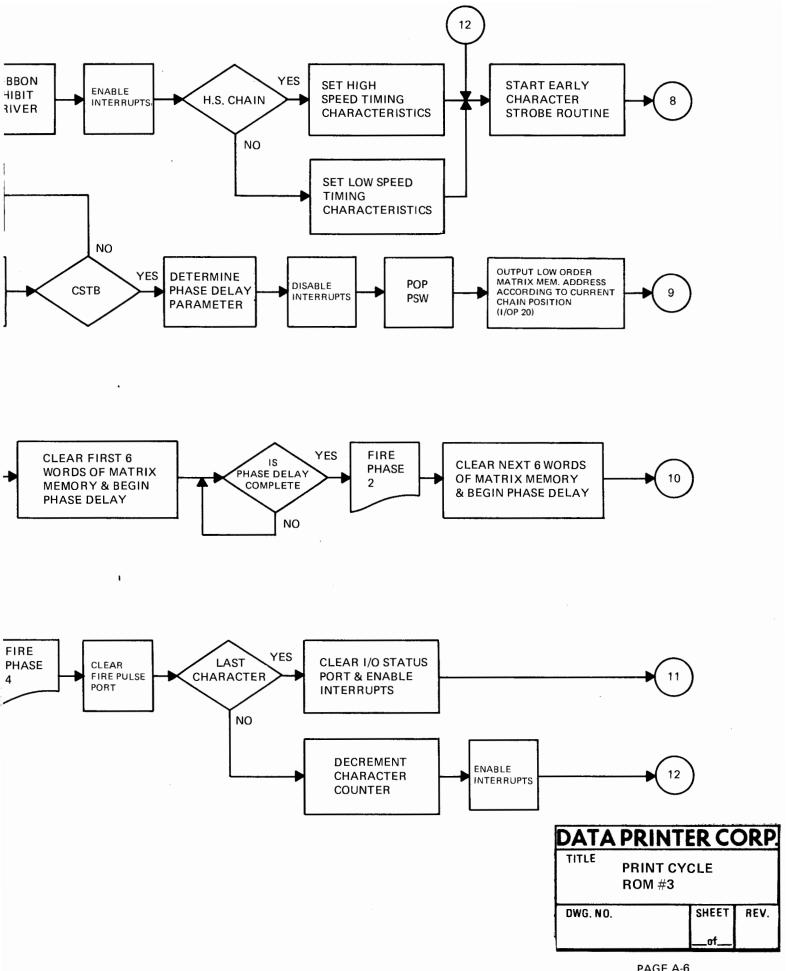

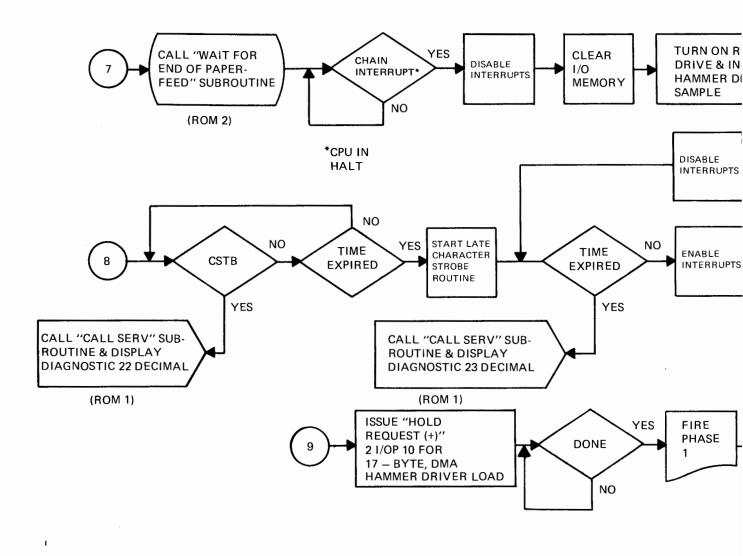

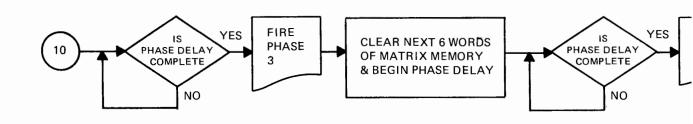

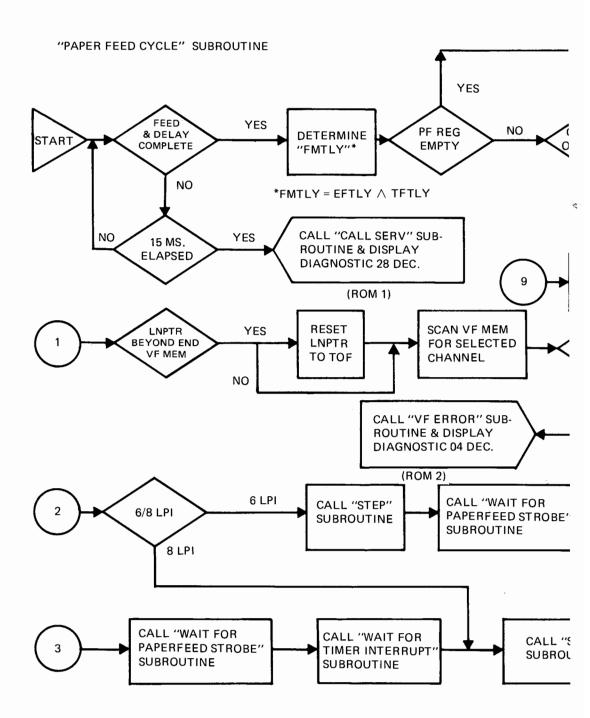

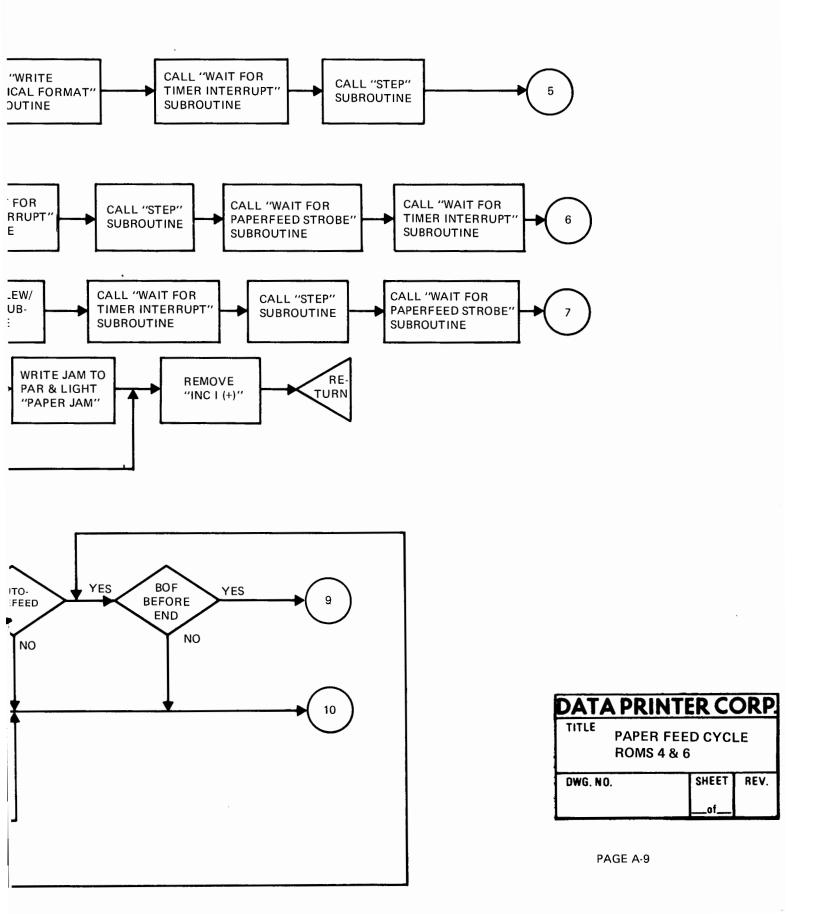

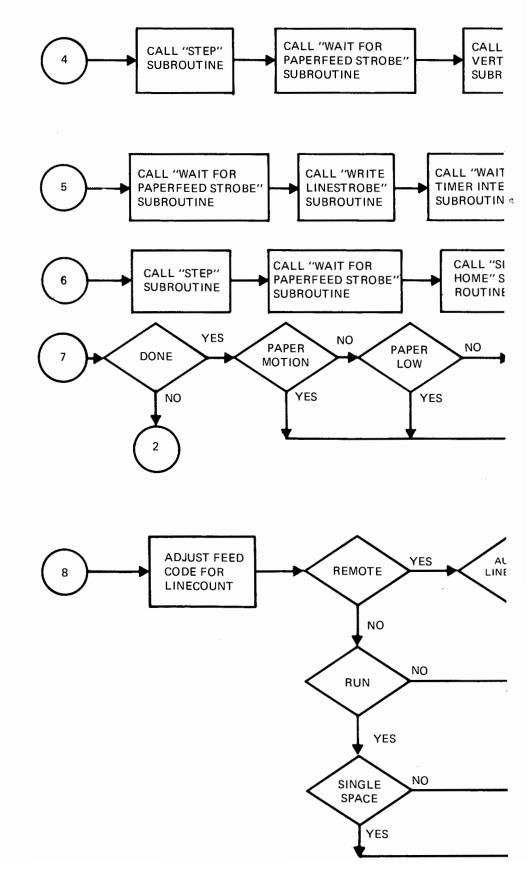

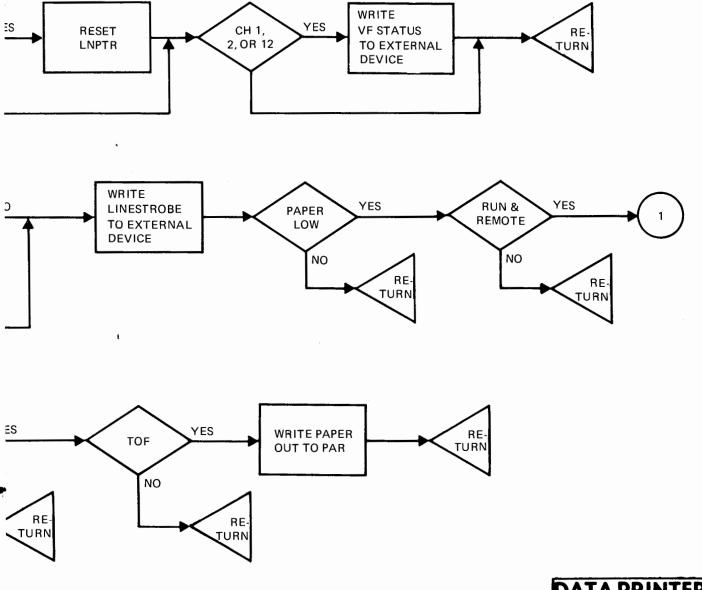

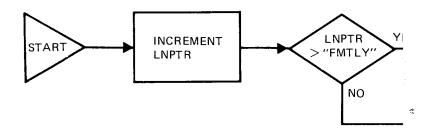

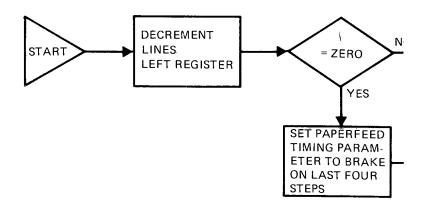

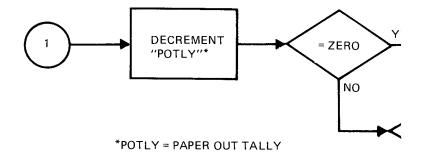

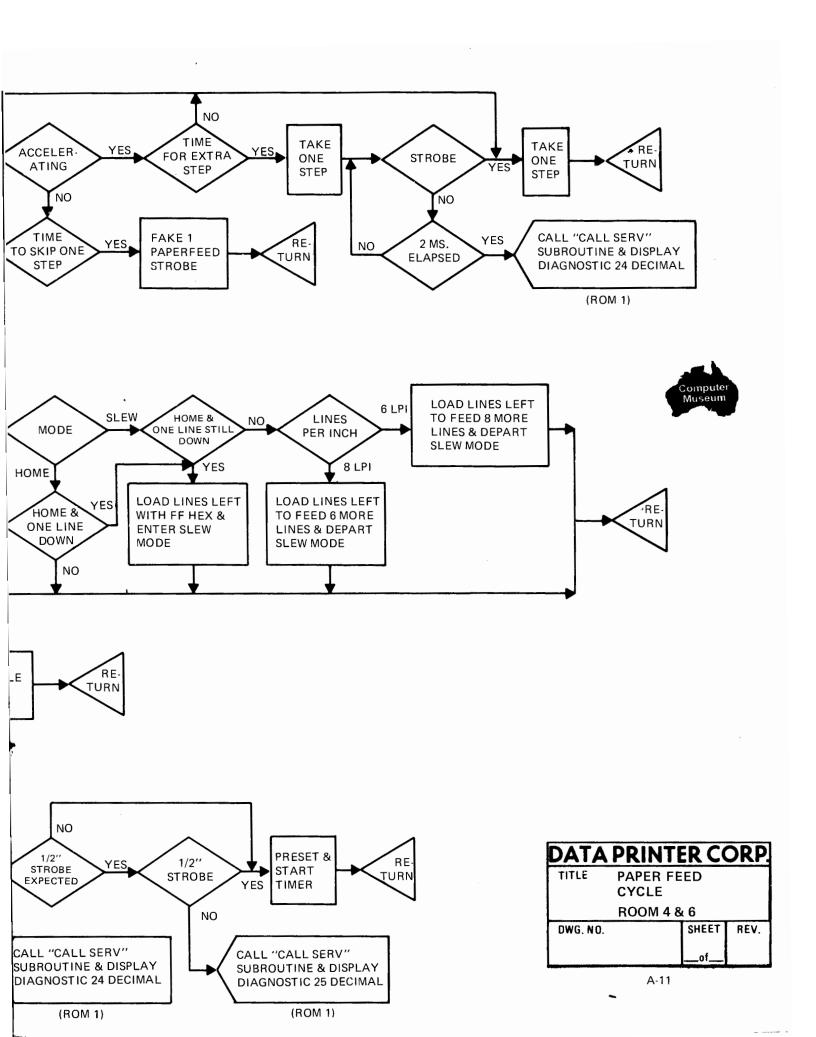

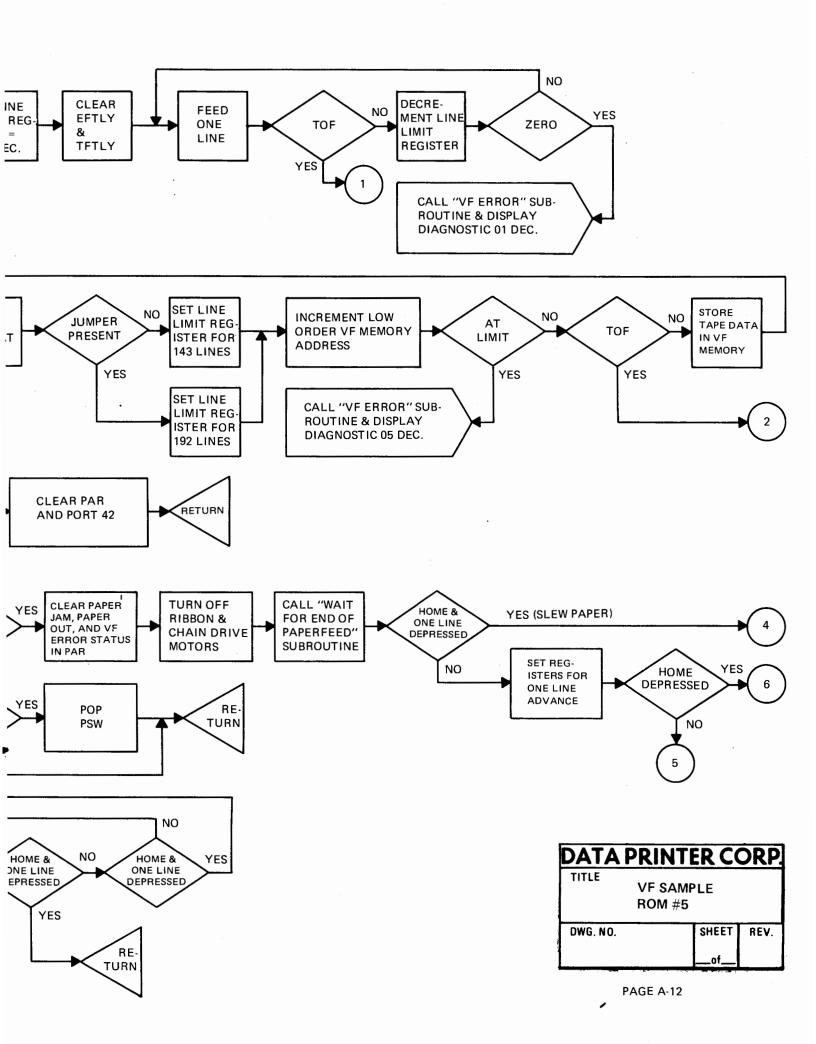

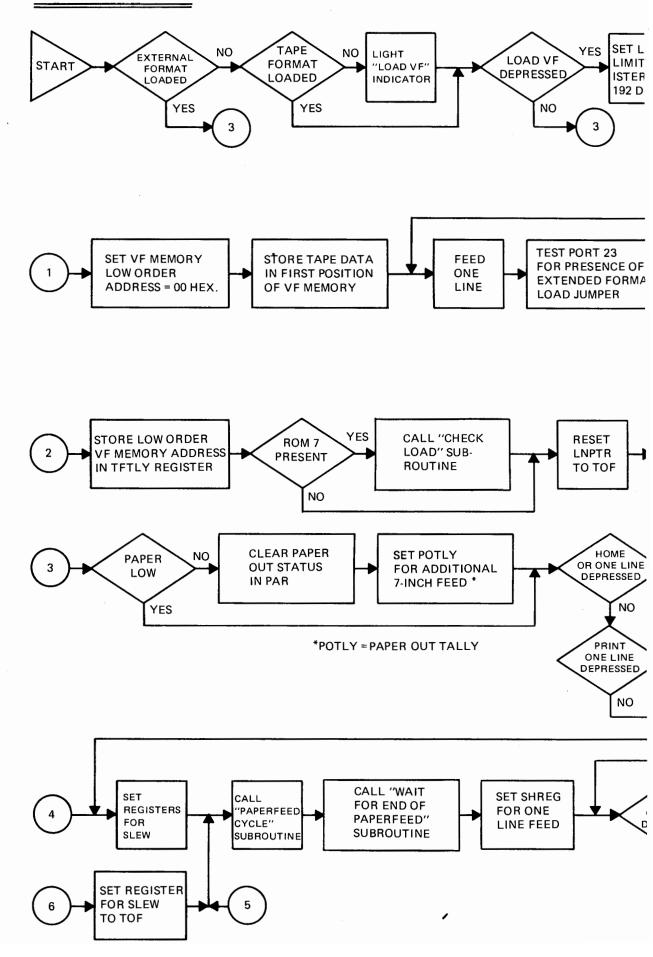

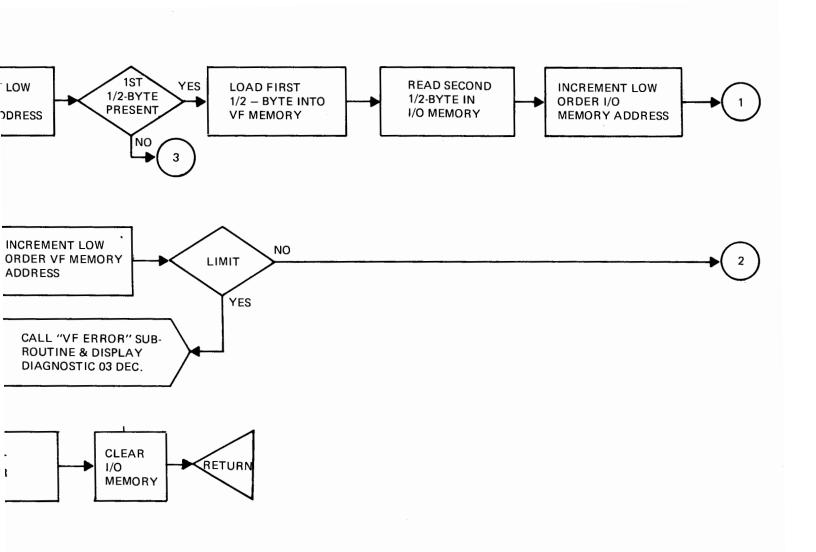

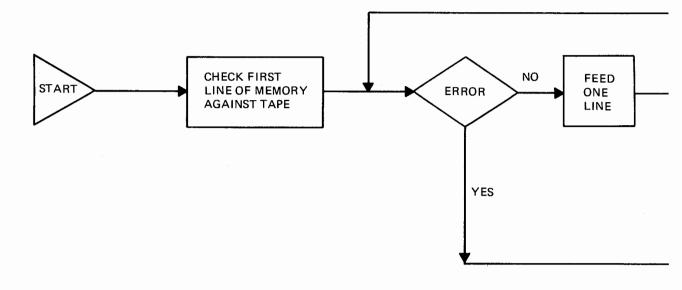

- Appendix A. Flow charts of a typical operating program used in CT-1260, CT-1290, and CT-1210 CHAINTRAIN™ Line Printers.

- Appendix B. Tables that show how to interpret the binary error

codes displayed by the Diagnostic LED's at the rear of the printer whenever "CALL SERV" or "VF ERROR" are illuminated on the right-hand control panel.

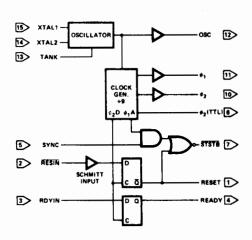

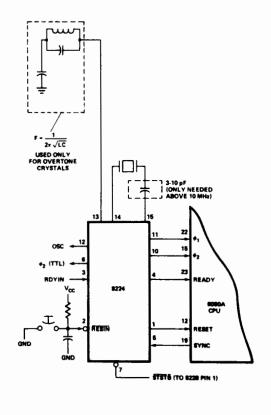

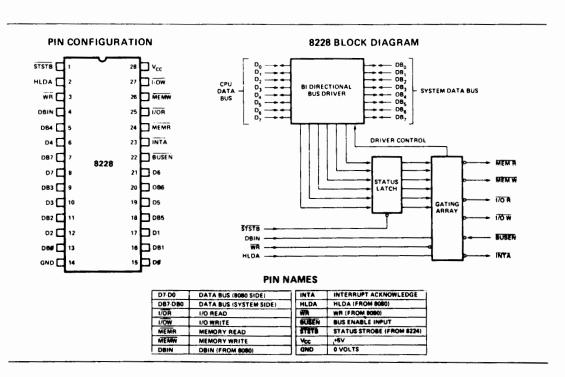

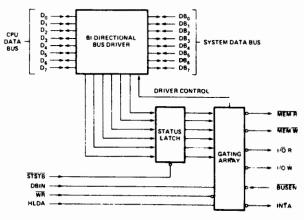

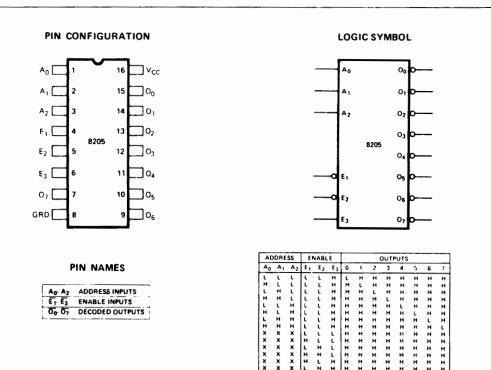

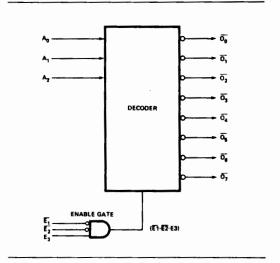

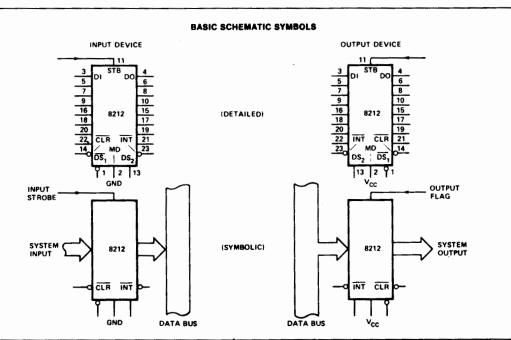

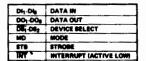

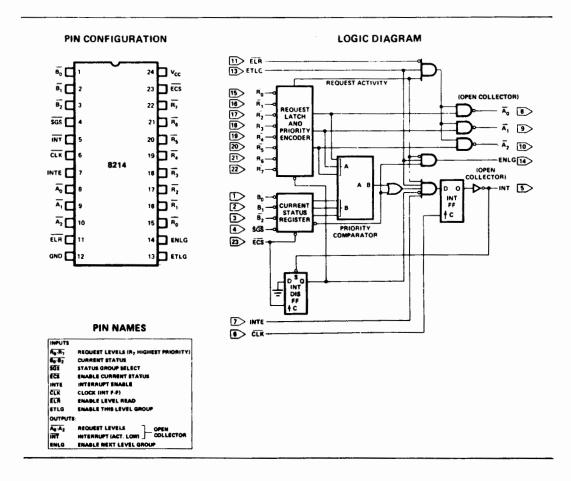

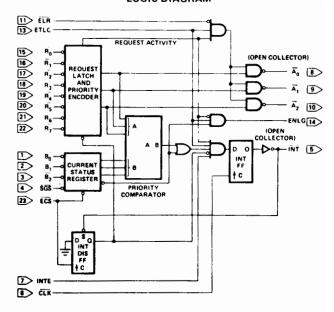

- Appendix C. Intel data sheets for the following: the 8080A "Eight-bit Microprocessor" (CPU), the 8224 "Clock Generator and Driver," the 8228 "System Controller and Bidirectional Bus Driver," the 8205 "High Speed 1 of 8 Binary Decoder," the 8212 "Parallel 8-bit I/O Port," and the 8214 "Priority Interrupt Control Unit" (PICU).2

- Appendix D. List of abbreviations used in this manual and on the Circuit Diagrams (CD's) found in the Illustrated Parts

Breakdown and Circuit Diagrams manual (DPC Form 1200-4).

#### 1.2.2 CD and IPB References

CD and IPB references in this manual point to Circuit Diagrams (CD's) and Illustrated Parts Breakdowns (IPB's) contained in the <u>Illustrated Parts Breakdown and Circuit Diagrams</u> manual (DPC Form 1200-4). Such references are liberally scattered throughout this manual to encourage familiarity with that important document.

A reference such as "IPB 26-28" should be understood to mean IPB Figure 26, Index Number -28, which calls out the 1/2" Strobe Sensor in an exploded view drawing of an 8-Channel Vertical Format Unit (VFU).

A reference such as "CD 3.0.0" should be understood to mean one drawing (DWG. NO. C40006, Sheet 1 of 6) in a series of six drawings that show in

<sup>&</sup>lt;sup>2</sup>The data sheets in Appendix C have been reprinted by permission of the Intel Corporation, 3065 Bowers Avenue, Santa Clara, CA. 95051.

schematic form the circuitry on the Traffic Control Board. A reference such as "CD 3.X.X" should be understood to mean the entire series of six drawings.

The <u>Illustrated Parts Breakdown and Circuit Diagrams</u> manual (DPC Form 1200-4) contains the following basic set of CD's:

| Series | Dwg. No.  | <u>Description</u>                                                                                                                     |

|--------|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0.X.X  | C40020-22 | Motherhood Connectors J-201, J-202, J-211, J-212, J-213, and J-214.                                                                    |

| 1.X.X  | C40004    | DPC Standard I/O Board.                                                                                                                |

| 2.X.X  | C40002    | Controller (CPU) Board.                                                                                                                |

| 3.X.X  | C40006    | Traffic Control Board.                                                                                                                 |

| 4.0.0  | C40012    | Paperfeed Stepper Drive Board                                                                                                          |

| 5.0.0  | 40025     | LSI Hammer Driver Board.                                                                                                               |

| 6.0.0  | C40010    | Power Control Board.                                                                                                                   |

| 7.0.0  | D40028    | Control Panel Switch Wiring.                                                                                                           |

| 11.0.1 | D40015    | CT-1290, CT-1210, and CT-1200 Power Supply manufactured by Power Supplies Incorporated (PSI). This supply carries the number PSI 1196. |

| 11.0.1 | D40023    | CT-1290, CT-1210, and CT-1200 Power Supply manufactured by North Electric Company (NECO). This supply carries the number NECO 8806A.   |

| 11.0.1 | D40016    | CT-1260 Power Supply manufactured by Power Supplies Incorporated (PSI). This supply carries the number PSI 1207.                       |

| 12.0.1 | 40026     | Power Distribution Diagram.                                                                                                            |

Individual copies of the <u>Illustrated Parts Breakdown and Circuit Diagrams</u> manual may contain additional CD drawings to reflect the actual configuration of your particular printer. Any CD reference in this manual should be

understood to refer only to the drawings listed above rather than to any additional drawings.

#### 1.3 FIELD SERVICE PHILOSOPHY

CT-1260, CT-1290, and CT-1210 printers are complete, self-contained, microprocessor-controlled back-impact line printers that produce hardcopy output one-line-at-a-time from stored digital data sent from an external device. From a Field Service point of view, the use of a programmable microprocessor-based Control System has two important advantages.

First, it simplifies troubleshooting by permitting expanded self-diagnostic capability in the form of five Diagnostic LED's, located on the Controller Board (CD 2.3.0 and IPB 67-16). The LED's, which display a binary error code whenever "CALL SERV" or "VF ERROR" is illuminated on the right-hand control panel, are visible through a clear plastic panel at the rear of the printer. The diagnostic codes (listed in Appendix B) give you a powerful tool for locating the cause of almost any malfunction.

Second, because microprocessor-control permits most individual printer characteristics to be "programmed-in" instead of being "hard-wired," printers in this series have the minimum possible number of model- and option-related differences at an electrical hardware level. This results in circuitry that is more flexible and easier to understand.

Expanded diagnostic capability and consistent, easily understood electrical hardware make Field Service a relatively simple matter of mechanical and electrical adjustment, parts repair and replacement, and board substitution—all of which can be carried out logically and efficiently once the general principles of operation are understood.

Although a familiarity with the operation of the operation of the 8080A CPU and its support devices would be helpful to readers of this manual, an intimate knowledge of these components—or the operating program that "drives"

them--is not needed to perform competent Field Service: testing down to the chip level is not practical when servicing a microprocessor-controlled printer in the field.

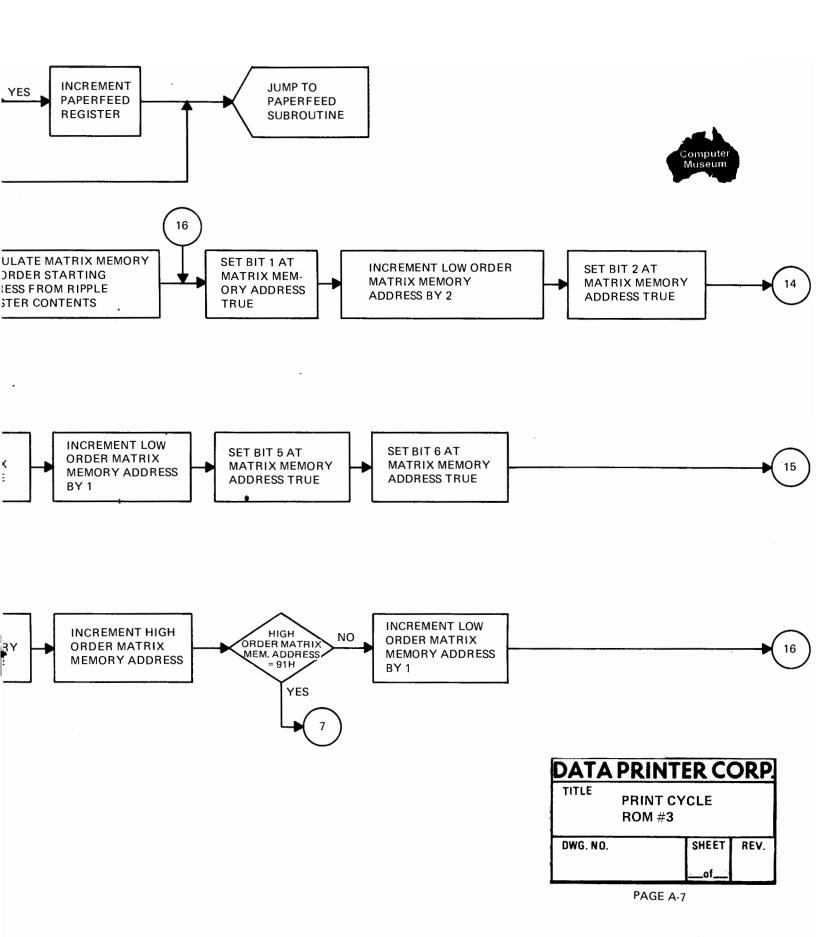

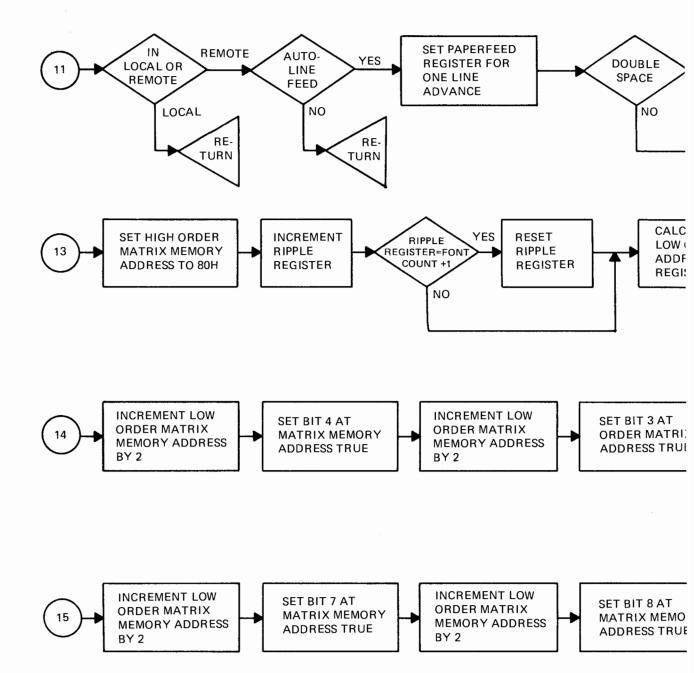

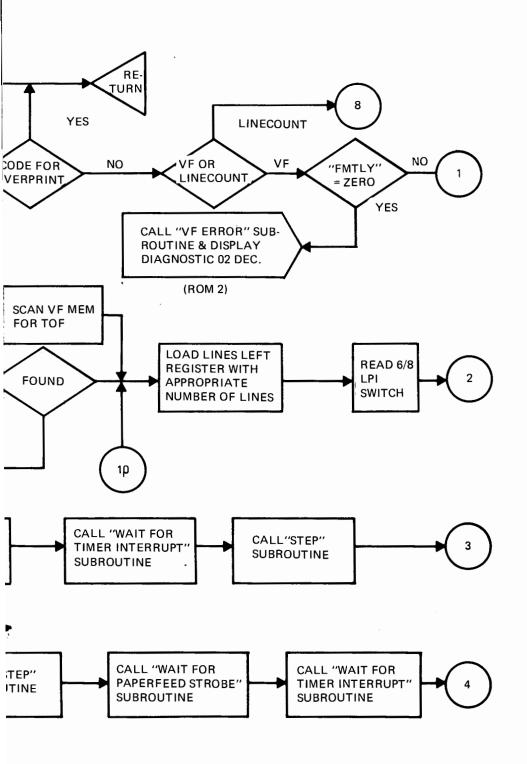

For the most part, major differences among CT-1260, CT-1290, and CT-1210 printers are confined to the area of "firmware"—the Read Only Memories (or ROM's) that contain the operating program that tells the CPU what to do. That program—which "particularizes" each printer according to model and equipment selected—is contained in six 512-byte ROM's that are located on the Controller Board (CD 2.2.0 and IPB 67-41). A seventh position for one additional ROM is available for program expansion. If present, that ROM will usually contain a "check load" subroutine that permits the CPU to verify the accuracy of vertical format data loaded from punched tape. Although Field Service does not require an intimate knowledge of a particular printer's operating program, you should have a general idea of what that program does. To that end, the operation of a typical operating program is presented in simplified flow chart form in Appendix A.

#### 1.4 MODEL IDENTIFICATION

The DPC 1200 Series is made up of four standard models, each of which can be reconfigured through the selection of optional equipment. The four basic model numbers are CT-1260, CT-1290, CT-1210, and CT-1200. The last two digits in each of these numbers reflect the rate of throughput that is achieved by that model when it is configured with 64-character "arrays": CT-1260 (600 LPM), CT-1290 (900 LPM), CT-1210 (1000 LPM), and CT-1200 (1200 LPM).  $^3$

<sup>&</sup>lt;sup>3</sup>In all models, however configured, the CHAINTRAIN™ type carrier transports a font containing 384 characters. These are divided into an integral number of identical <u>arrays</u>, each of which contains one each of the characters included in the font.

Other array sizes (48, 96, and 128) are available as an option on each of the four models. Array size is indicated by means of a hyphenated suffix appended to the basic model number stamped on the nameplate: CT-12XX-48 (a DPC 1200 Series printer equipped with eight 48-character arrays, where XX = 60, 90, 10, or 00), CT-12XX-64 (a DPC 1200 Series printer equipped with six 64-character arrays), CT-12XX-96 (one equipped with four 96-character arrays), and CT-12XX-128 (three 128-character arrays).

The primary reason for the difference in the rate of throughput between different models equipped with arrays of the same size is a difference in the speed of the type carrier: CT-1260 (110 IPS), CT-1290 (185 IPS), CT-1210 (220 IPS), and CT-1200 (256 IPS).  $^4$

Because the speed of each model's type carrier remains constant regardless of array size, decreasing array size produces a corresponding increase in a model's rate of throughput. Conversely, increasing array size produces a corresponding decrease in a model's rate of throughput. The various rate of throughput that can result are illustrated in Table 1-1.

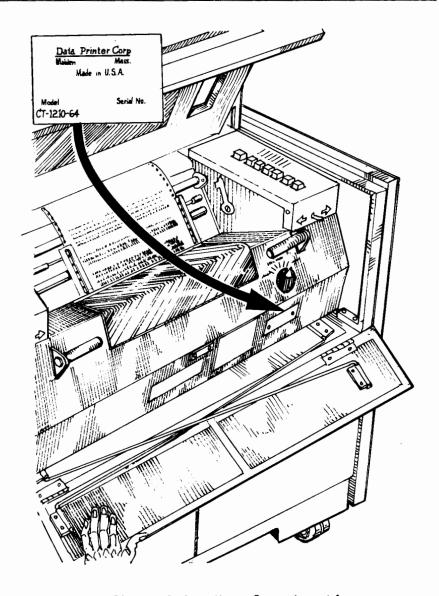

Your printer's model number is stamped on a nameplate mounted on the front yoke cover as shown in Figure 1-1. The nameplate can be seen after lifting the canopy and pulling down the hinged front panel located above the paper bay doors at the front of the machine. Check your model number and keep it in mind as you read.

#### CAUTION

If your printer is a CT-1200, you are reading the wrong manual. The principles of operation for that model are found in DPC Form 1200-2.

<sup>&</sup>lt;sup>4</sup>IPS stands for inches per second.

TABLE 1-1

Throughput in Lines per Second (LPS)

| Model<br>Number | -48     | Array Si:<br>-64 | ze<br>-96 | -128   |

|-----------------|---------|------------------|-----------|--------|

| CT-1260         | 760 LP  | 600 LP           | 430 LP    | 330 LP |

| CT-1290         | 1100 LP | 900 LP           | 670 LP    | 530 LP |

| CT-1210         | 1200 LP | 1000 LP          | 750 LP    | 600 LP |

| CT-1200         | 1450 LP | 1200 LP          | 900 LP    | 725 LP |

Figure 1-1. Nameplate Location.

# CHAPTER 2 PRINT SYSTEM OPERATION

#### 2.1 INTRODUCTION

A thorough understanding of Print System operation is a prerequisite for understanding many of the more complex operations of the Control System. In the subsections that follow, the Print System is treated as three function-related subsystems: (1) the Print Mechanism (2.2), (2) the Ribbonfeed Mechanism (2.3), and (3) the Paperfeed Mechanism (2.4). Each is examined in detail in order to lay the groundwork for an adequate understanding of the Control System.

#### 2.2 PRINT MECHANISM

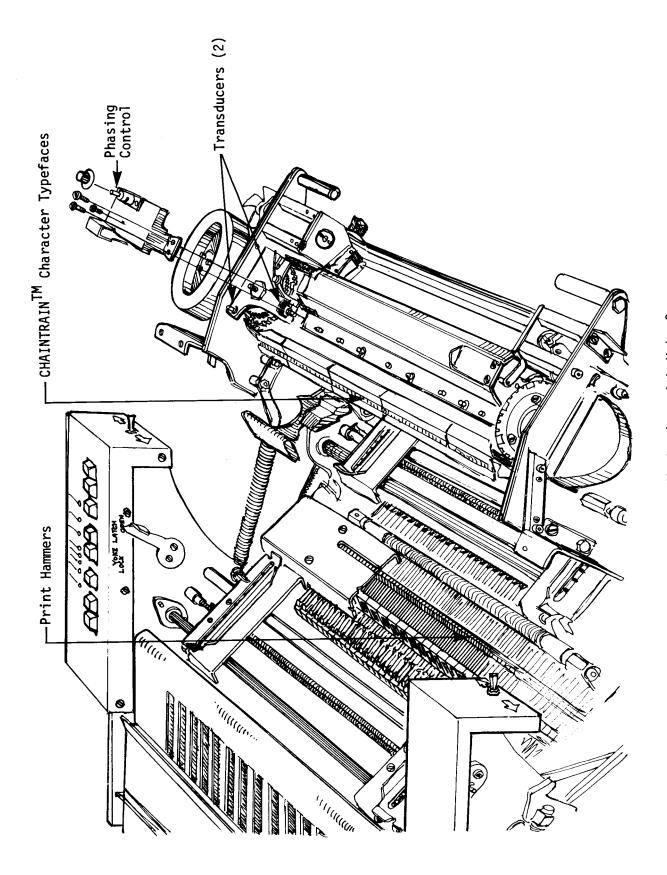

The Print Mechanism consists of two basic subassemblies: (1) a bank of print hammers and their corresponding actuators, mounted on a stationary frame at the back (non-print) side of the paper path; and (2) the DPC CHAINTRAIN™ lateral type carrier (or "chain") and its associated components, mounted on a movable yoke at the front (print) side of the paper path (Figure 2-1).

The yoke can be "opened"--that is, swung away from the hammer bank on the frame--in order to permit paper loading and facilitate servicing. Closing the yoke brings print hammers, paper, ribbon, and chain into proximity so printing can take place. Operation of the printer in the Run Mode requires the yoke to be locked in the closed position by means of a yoke latch lever, located on the right-hand side of the frame assembly.

Paper is held stationary and ribbon is fed continuously during data printout. Printing is accomplished by firing print hammers at appropriate times

into the backside of the paper form. The hammers compress column-sized sections of paper and ribbon against selected characters on the chain, thereby

creating solid character print impressions on the paper forms. Back-impact

printing such as this takes place "on the fly" as character typefaces on the

chain are driven laterally past the hammer bank at constant speed. DPC type-

Figure 2-1. Print Mechanism with Yoke Open.

face design precludes the possibility of print quality degradation due to "dynamic growth".  $^{\!\! 1}$

The Control System monitors chain speed, tracks character positions, and determines hammer firing times in response to impulses generated by two variable reluctance transducers that are mounted on an adjustable plate at the right-hand end of the chain assembly. The position of these transducers can be adjusted by means of a PHASING CONTROL, which allows hammer firing time to be advanced or retarded as needed to achieve the best overall print quality. An IMPRESSION CONTROL, also located on the yoke, permits the operator to adjust print hammer striking force in response to ribbon wear or a change in paper form thickness when different forms are loaded.

#### 2.2.1 Yoke Latch and Interlock Switches

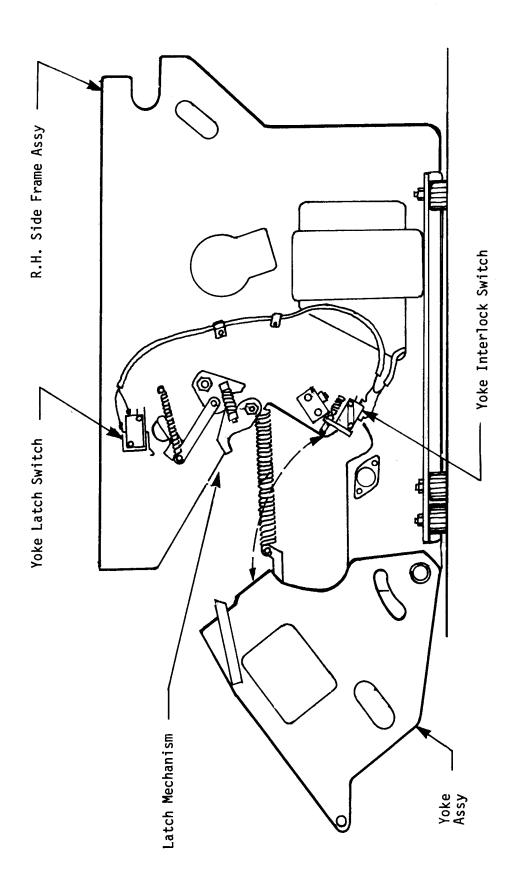

Two switches allow the Control System to monitor yoke and latch position (Figure 2-2). Moving the yoke into printing position closes a yoke interlock switch and latching it in that position closes a yoke latch switch. The switches, which are connected in series (CD 7.0.0), interface with the Control System as shown on CD 1.4.1. Operation in the Run Mode will not be initialized or maintained by the Control System if either switch is open.

For maintenance purposes, it is often convenient to operate the printer in the Run Mode with the yoke in the open position. This is easily accomplished by pulling out the plunger on the yoke interlock switch and closing the yoke latch lever. When this is done, both switches will be closed and the Control System will operate normally even though the yoke remains in the open position.

<sup>&</sup>lt;sup>1</sup>Dynamic growth refers to the broadening of the character imprint that takes place during the brief instant hammer, paper, and ribbon are in contact with a selected character typeface on the moving chain.

RIGHT-HAND SIDE OF PRINTER MECHANISM (CABINET REMOVED)

Figure 2-2. Yoke Latch and Interlock Switches.

#### CAUTION

When operating the printer open-yoked, always put the PRINT/INHIBIT switch in the INHIBIT position to prevent hammer firing. Hammer firing with the yoke open can result in damage to the print hammers. Note: INHIBIT is ignored when operating in the Remote Mode.

On any printer equipped with the "DPC Standard Interface" that means <u>always</u> <u>put the bottom toggle switch on the test panel in the up position</u> in order to inhibit hammer firing ("SW-1" on IPB 72-18). Regardless of the type of interface, putting the PRINT/INHIBIT switch into the INHIBIT position when operating in the Local Mode will result in the illumination of "PRINT INHIBIT" on the right-hand operator control panel.

#### 2.2.2 Print Hammers and Actuators

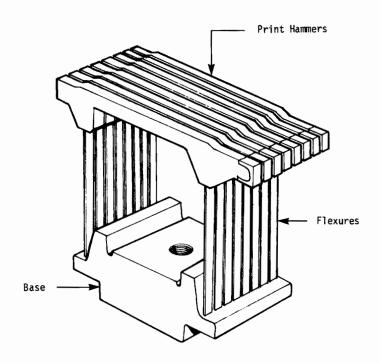

All DPC 1200 Series printers come equipped with a hammer bank composed of seventeen 8-up hammer modules, arranged end-to-end on a hammer ban/bumper as shown in IPB 42. Each module consists of eight "single-duty," "free-flight" print hammers and their supporting flexures molded into a plastic base (Figure 2-3). The seventeen modules provide a potential typeline of 136 columns (8 x 17 = 136) spaced ten-columns-to-the-inch. Printers configured for the standard 132 column typeline simply lack actuators corresponding to the last four hammers in the rightmost module (columns 133 through 136). The missing actuators cause those hammers to be recessed--a certain indication that a printer is configured with a 132 column typeline.

Just as one hammer is dedicated to each column position, one electromechanical actuator is dedicated to each of the 132 (136 optional) hammers in-

<sup>&</sup>lt;sup>3</sup>Single-duty refers to the fact that each print hammer is dedicated to a single column position. Free-flight means that the hammer flies free of the actuator that drives it before it hits the chain.

Figure 2-3. Eight-Up Hammer Module.

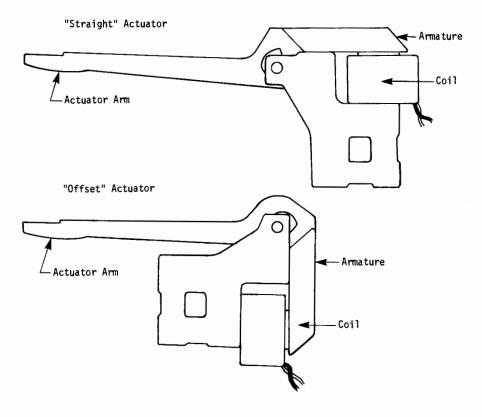

Figure 2-4. Straight and Offset Hammer Actuators.

Figure 2-5. Actuator Tip Interlace Pattern.

Front View

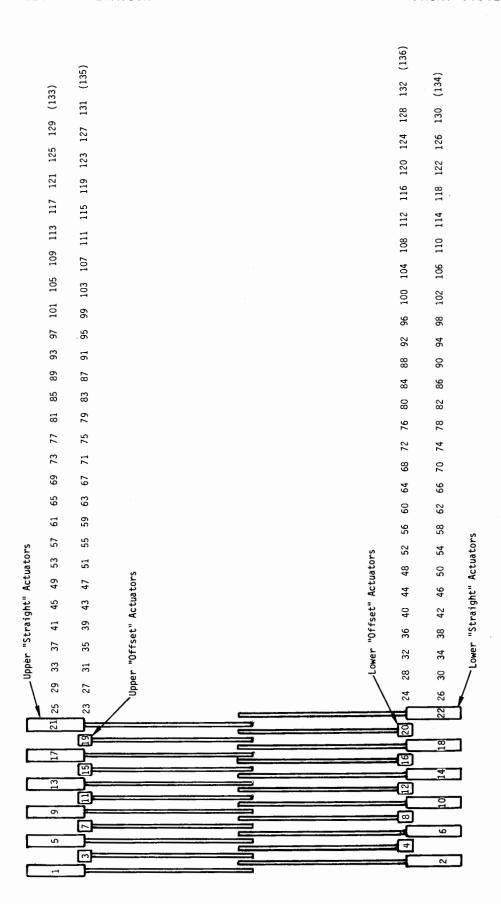

cluded in the chosen typeline. In order to accommodate the necessary size of the actuator coils, actuators are constructed in both "straight" and "offset" configurations (Figure 2-4) so they can be mounted on the frame in four rows, each of which contains 33 (34 optional) actuators (IPB 39). Figure 2-5 shows the way in which the tips of the actuator arms interlace to accommodate 132 (or 136) hammers in the hammer bank. The hammer bank is wedded to the frame as shown in IPB 38.

Horizontal alignment of the print hammers with the average position of the actuator arm tips is accomplished by adjusting an eccentric located in the right-hand side platen support (IPB 42). Vertical alignment of the hammers with the characters on the chain is accomplished by adjusting set screws in both the right- and left-hand side platen supports (IPB 42).

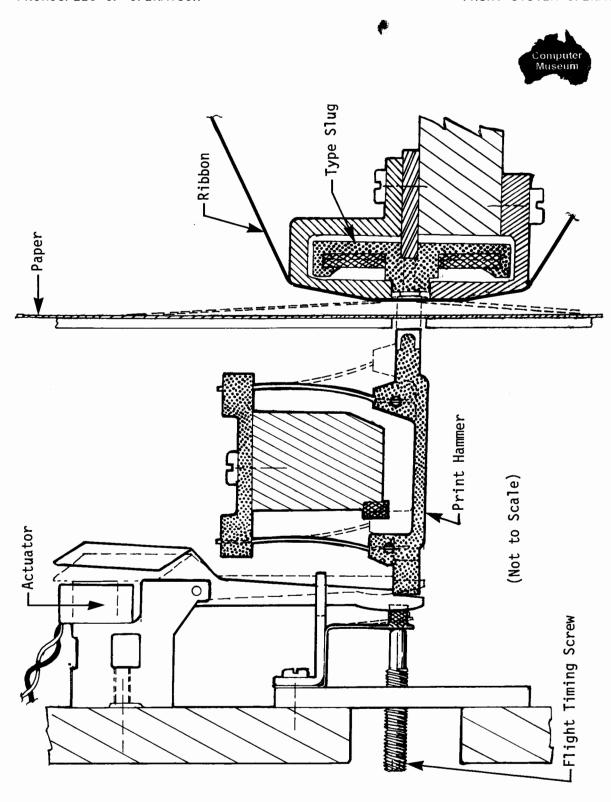

The resting position of a typical print hammer is shown in Figure 2-6. Under pressure from its supporting flexures, the hammer holds the actuator arm firmly against its corresponding finger on the stop comb bumper. The hammer is fired by briefly energizing the coil in its corresponding actuator. The resulting armature stroke is transferred to the hammer by the actuator arm, which drives the hammer forward toward the chain. Upon completion of the stroke, the accelerated hammer flies free of the actuator tip and pushes paper and ribbon against a selected character on the chain. It then rebounds driving the no-longer-energized actuator back against the stop comb bumper and comes to rest in its original resting position ready to be fired again.

The Control System must fire hammers in advance of actual alignment in order to give the hammers time to travel to the chain. The interval between actuation and impact is called "flight time" and must be equal for all hammers if print quality is to be maintained. When that is the case and the PHASING CONTROL is properly adjusted, no "side clipping" will occur. Any side clip

<sup>&</sup>lt;sup>4</sup>Side clipping refers to left- or right-hand side cut off of the character imprint.

Figure 2-6. Hammer in Resting Position.

ping that cannot be removed by adjusting the PHASING CONTROL is a certain indication that the flight timing of the hammer corresponding to the clipped column position diverges from the overall flight time norm.

Character typefaces move from right (column 132/136) to left (column 1) accross the typeline at constant speed during a print operation. Therefore, right-hand clipping indicates a hammer that prints too soon (flight time too short); and left-hand clipping indicates a hammer that prints too late (flight time too long).

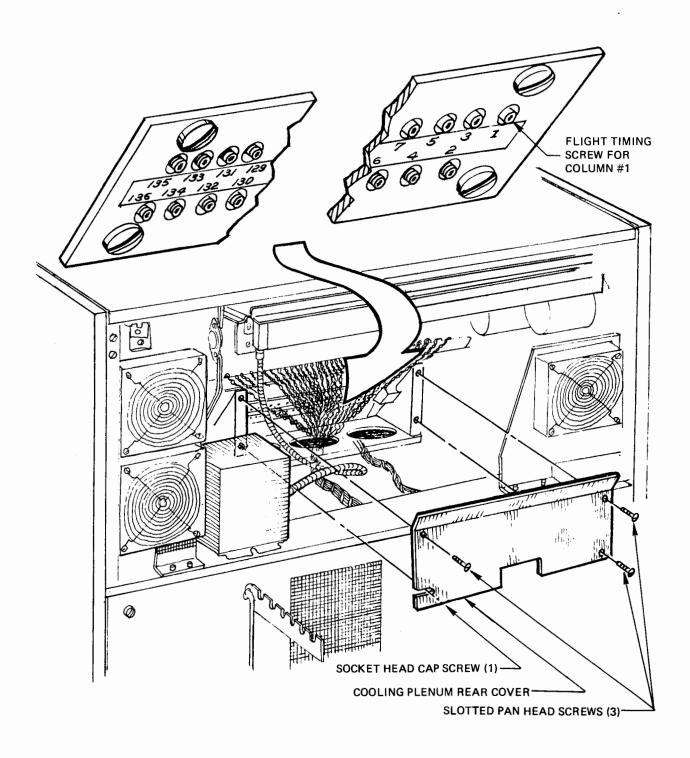

Individual hammer flight time can be adjusted by means of 132 (or 136) flight timing screws, which are accessible from the rear of the printer mechanism. The screws are conveniently arranged on the backside of the frame into two rows divided by a strip label that shows the corresponding hammer/column positions. CT-1290 and CT-1210 printers have a cooling plenum mounted on the backside of the frame assembly that obscures the flight timing screws. The screws may be accessed by removing the rear panel of the plenum as shown in Figure 2-7.

Adjustment of a flight timing screw affects the resting position of its corresponding actuator/hammer pair (Figure 2-6). Lefthand clipping can be removed by turning the appropriate screw clockwise to reduce flight time by moving the resting position closer to the chain. Conversely, right-hand clipping can be removed by turning the screw counter-clockwise to increase flight time by moving the resting position away from the chain. Sufficient tension is preloaded into the hammer flexures at time of manufacture to guarantee return to the same resting position after each firing so that consistency in flight time can be maintained.

All flight timing screws are carefully adjusted at the factory after a thorough run-in period. They will not require frequent attention during the life of the machine. A few may need to be touched up occasionally as part of your quarterly PM routine; and, of course, replacement of actuators or hammer modules will necessitate readjustment of the timing screws affected.

Figure 2-7. Location of Flight Timing Screws.

#### CAUTION

Excessive adjustment of a flight timing screw can result in parts failure. Follow the instructions in subsection 3.5.1.4.3 of the Maintenance instructions manual (DPC Form 1260/90/10-3) carefully when retiming a hammer.

A good rule of thumb to follow is this. If the clipping problem cannot be improved by turning the flight timing screw less than one full turn, return the flight timing screw to its original position and look for the presence of an electrical or mechanical problem.

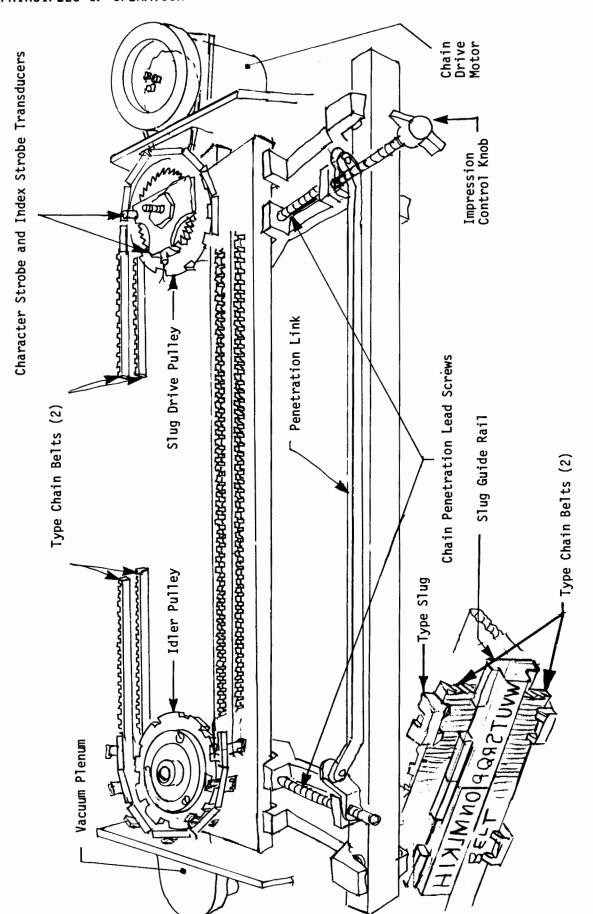

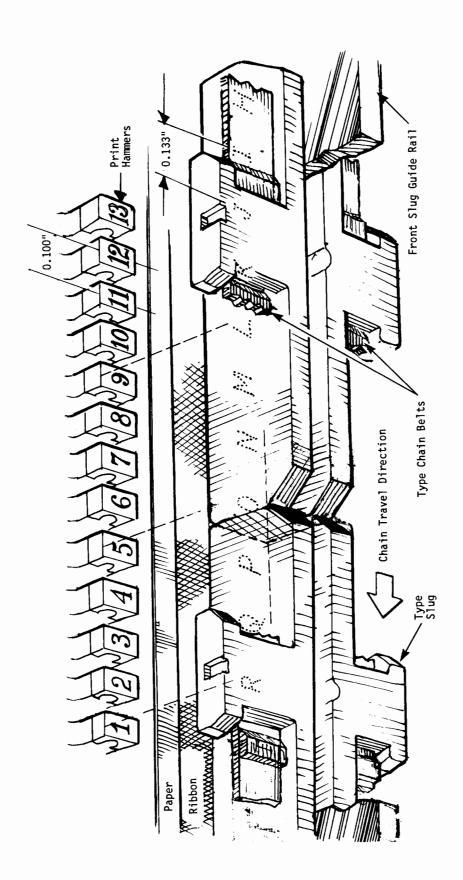

#### 2.2.3 DPC CHAINTRAIN Type Carrier

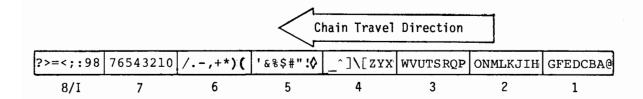

The CHAINTRAIN<sup>™</sup> lateral type carrier transports forty-eight 8-character type slugs, which are mounted end-to-end on motor-driven double belt loop (Figure 2-3). The resulting 384-character "chain" (48 x 8 = 384) can be divided into an integral number of identical arrays having 48, 64, 96, or 128 characters each. The chain can transport three 128-character arrays (3 x 128 = 384), four 96-character arrays (4 x 96 = 384), six 64-character arrays (6 x 64 = 384), or eight 48-character arrays (8 x 48 = 384). Every array on the chain contains one each of the characters in the chosen font arranged in a fixed sequence "known" to the Control System. Figure 2-9 shows the arrangement of the characters on the eight type slugs that make up one standard 64-character array (8 x 8 = 64).

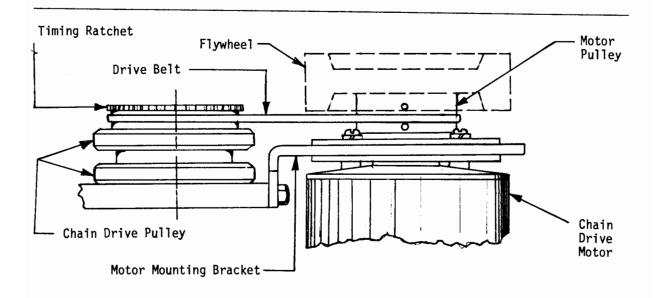

The chain is driven at constant speed by means of a motor/flywheel drive assembly coupled to a slug drive pulley by a rubber drive belt as shown in Figure 2-10. Chain speed is determined by the size of the motor pulley, which must be appropriate to the motor and model on which it is used (see IPB 43 and 46). Throughput is a function of chain speed and array size.

The Control System activates the run and start windings of the chain drive motor by means of optically-coupled triac circuitry on the "Power Control Board" (CD 6.0.0 and IPB 56-2).

Figure 2-8. DPC CHAINTRAIN" Lateral Type Carrier.

# DPC CHAINTRAIN<sup>TM</sup> Arrangement Standard 64-Character Subset of USASCII (Printout Representation)

Figure 2-9. Typical 64-Character Array.

Figure 2-10. Motor/Flywheel Drive Assembly.

Type slugs are pushed from right to left across the typeline in order to prevent alignment problems due to gapping when the chain is run at high speed. The same chain travel direction is maintained on all models in this series for purposes of consistency.

Different chain speeds produce different amounts of dynamic growth in the printout. The faster the chain speed, the greater the dynamic growth. Careful DPC typeface design compensates for this by exercising appropriate amounts of surface area from the vertical lands of the character typefaces. Therefore, type slugs are model-specific: be careful when ordering replacement slugs.

Heavy duty slugs, with character type faces fabricated from specially hardened steel are required equipment on CT-1200 printers. They are available as an option on the other models.

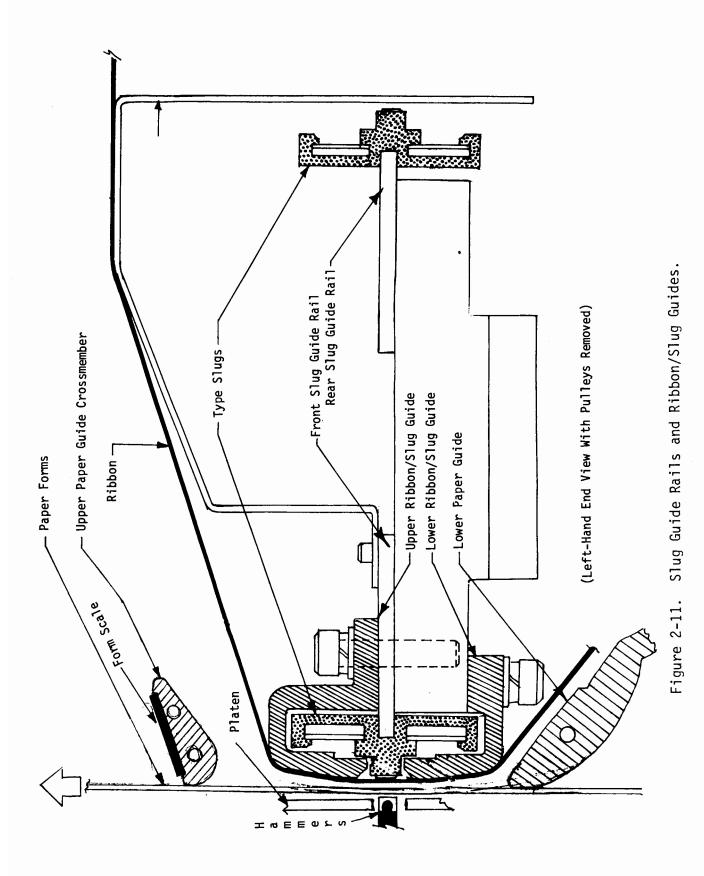

Chain stability and print quality are maintained by two kinds of slug restraints—slug guide rails, and ribbon/slug guides—shown in Figure 2-11.

The front and rear monorail tracks, called slug guide rails, prevent vertical displacement of the type slugs, that would produce destructive instability in the chain. The front guide rail also serves as an anvil when characters on the chain are struck by the hammers. The channels in the backs of the type slugs, which mate with these rails, are oiled by a wick-fed lubricant contained in a bottle at the left front side of the chain assembly (IPB 52-14).

Front upper and lower ribbon/slug guides, the second type of slug restraint shown in Figure 2-11, prevent horizontal displacement of the slugs, which would cause random variations in flight time that would show up as side clipping. They also keep the ribbon from dragging across the chain when it is started or stopped. A mylar ribbon shield is attached to the upper and lower ribbon/slug guides at the right-hand side of the chain to prevent fraying of the right-hand edge of the ribbon.

5/15/79

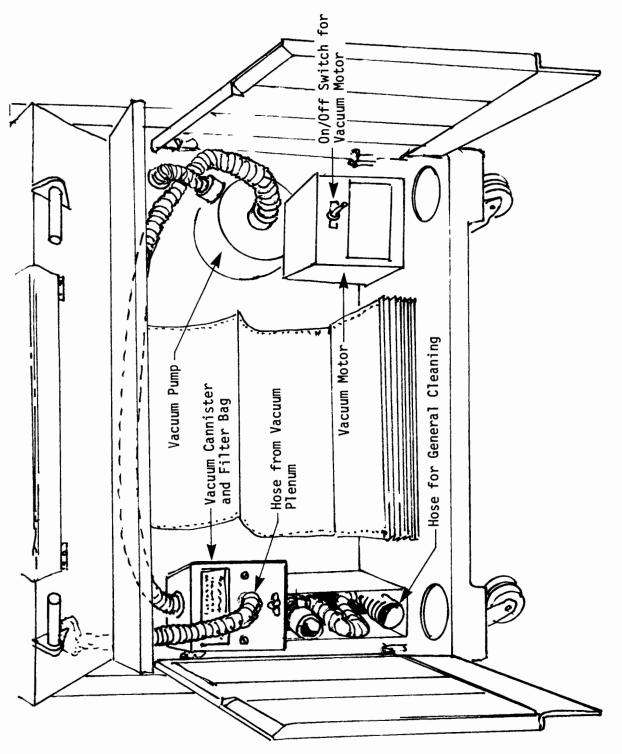

Figure 2-12. Vacuum Cleaning System.

Ribbon particles and paper dust are the unavoidable by-products of any impact printing process. Because they accumulate quickly in printers run at high rate throughput, a vacuum plenum is required equipment on CT-1210 (Figure 2-8). It is optional on the CT-1290 and not available--or necessary--the CT-1260.

The vacuum plenum is connected by means of a hose to a vacuum cleaning system that is located beneath the printer mechanisms, behind the paper bay doors (Figure 2-12). Wired in parallel with the run windings of the chain drive motor, the vacuum motor is turned on and off simultaneously with the chain (regardless of the position of the vacuum cleaning system's ON/OFF switch) in order to guarantee continuous cleaning whenever the machine is printing (CD 12.0.1).

A vacuum cleaning system without the vacuum plenum is available as an option for routine clean up of the printing mechanism on CT-1260 Printers. Its vacuum motor is not wired in parallel with the run windings of the chain drive motor.

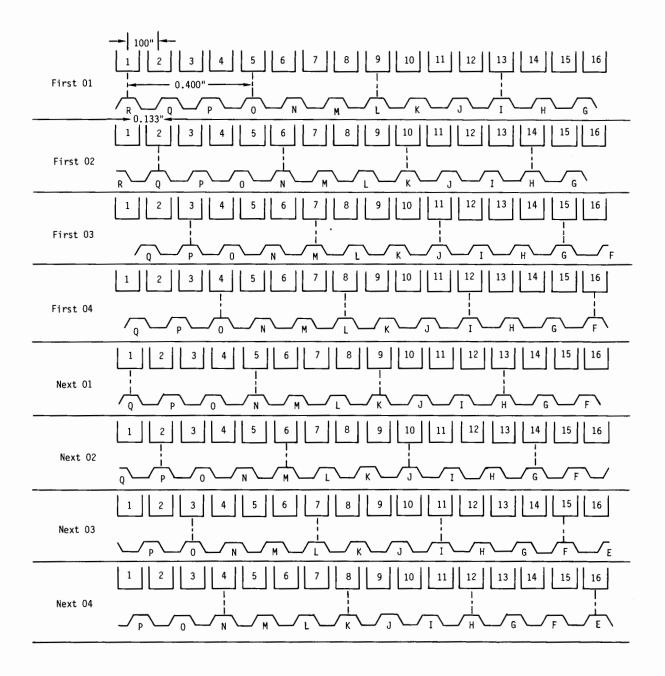

#### 2.2.4 Hammer-to-Character Alignment

All print hammers in the hammer bank are uniformly spaced 0.100-inch center-to-center to guarantee a ten-columns-to-the-inch typeline. To avoid "ghosting", characters on the chain must be spaced more widely to produce something other than a 1:1 alignment ratio between hammers and characters. DPC 1200 Series printers have characters spaced at 0.133-inch center-to-center. This results in a 4:3 hammer-to-character alignment ratio, in which

<sup>&</sup>lt;sup>5</sup>Ghosting refers to the unintentional partial printing of the character before and after the selected character on the chain. Because the paper/ribbon sandwich compressed against the selected character by the print hammer is of necessity wider than one single column position, ghosting would be unavoidable on a back impact printer having a 1:1 alignment ratio.

Figure 2-13. Four-to-Three Alignment Ratio.

Figure 2-14. Two Consecutive Four Phase Alignment Sequence.

only one-fourth of the print hammers in the hammer bank can be aligned with the characters on the chain at any given instant (Figure 2-13).

The chief consequence of selecting a 4:3 alignment ratio is the fact that alignment of "some character" with every print hammer necessarily takes place in four successive phases as shown in Figure 2-14. As the characters on the chain are pushed at constant speed from right-to-left past the print hammers alignment "streams" repeatedly left-to-right within four-column segments of the typeline in a constant succession of four phase alignment sequences. Figure 2-14 shows two such consecutive four phase alignment sequences covering the first sixteen columns of the typeline.

Each time a new four phase alignment sequence occurs, "some next character" in the font becomes available for printout in each column position (compare "Phase 1" to "Next Phase 1," "Phase 2" to "Next Phase 2," and so forth in Figure 2-14). Thus, every character in an N-character font will be presented for printout to every column position in "N" four phase alignment sequences. For example, every character in a 64-character font will be presented to every column position each time the chain moves through 64 four phase alignment sequences (256 discrete single phase alignments). Clearly, then, the printing of a single line is a serial process.

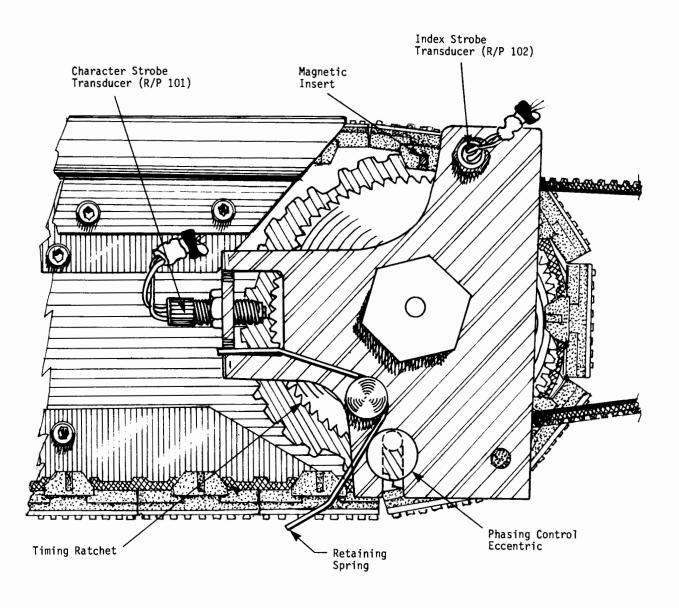

#### 2.2.5 Character and Index Strobe Transducers

The Control System tracks character positions, monitors chain speed, and determines print hammer firing times by means of two variable reluctance transducers ("RP-101" and "RP-102" on CD 7.0.0) that are mounted in tandem on an adjustable pick-up mounting plate at the right-hand end of the chain assembly (Figure 2-15).

Transducer RP-101 generates an analog Character Strobe (CSTB) pulse each time the chain moves a distance equivalent to one character. It does this by sensing the passage of teeth on a timing ratchet mounted on top of the slug drive pulley. Each CSTB signals onset of the next four phase alignment sequence.

Figure 2-15. CSTB and INDEX Variable Reluctance Transducers.

Transducer RP-102 generates an analog Index Strobe (INDEX) pulse each time the chain moves a distance equivalent to one array. It does this by sensing the passage of magnetic inserts strategically placed in the upper part of one type slug in the same position in each array (For Example slug #8 in Figure 2-9). Each INDEX pulse signals the onset of the next series of "N" four phase alignment sequences, where "N" equals array size. Thus each CSTB pulse is meaningful for purposes of character position tracking only by virtue of its order of occurance after a preceding INDEX pulse.

#### CAUTION

Careful adjustment of the CSTB (RP-101) and INDEX (RP-102) transducers is essential for proper operation. These adjustments are described in detail in section 3.5.1.2.3 of the Maintenance Instructions (DPC Form 1260/90/10-3).

# 2.2.6 Impression Control

One purpose of the IMPRESSION CONTROL (IPB 52) is to allow the operator to fine-adjust hammer-to- chain distance (called "penetration") to prevent embossing or punch-through when using single-part forms and to compensate for lightness of impression on the top (visible) form when using multi-part forms.

Another purpose of the IMPRESSION CONTROL is to allow the operator to compensate for improper print impression density due to ribbon wear. Hence, the lables "LIGHT" and "DARK" adjacent to the extreme left- and right-hand positions of the IMPRESSION CONTROL.

Altering penetration by means of the IMPRESSION CONTROL changes print hammer flight time uniformaly across the typeline and therefore, may, produce side clipping. Any clipping that results can be removed by readjusting the PHASING CONTROL, described in the next section.

The IMPRESSION CONTROL and the PHASING CONTROL function interactively although there is no mechanical or electrical linkage between the two. The IMPRESSION CONTROL should always be adjusted first to provide the best print

impression obtainable for the particular forms and ribbon being used. Following that, the PHASING CONTROL should be adjusted to remove any side clipping that may have resulted from adjusting the IMPRESSION CONTROL. When multi-part paper forms are in use, operators should remember to check the back as well as the top form for proper phasing and print density.

# 2.2.7 Phasing Control

Because adjustment of the IMPRESSION CONTROL introduces changes in flight time, fire pulse lead time must be operator-adustable within certain narrow limits in order to permit removal of any side clipping that results from readjustment of the IMPRESSION CONTROL.

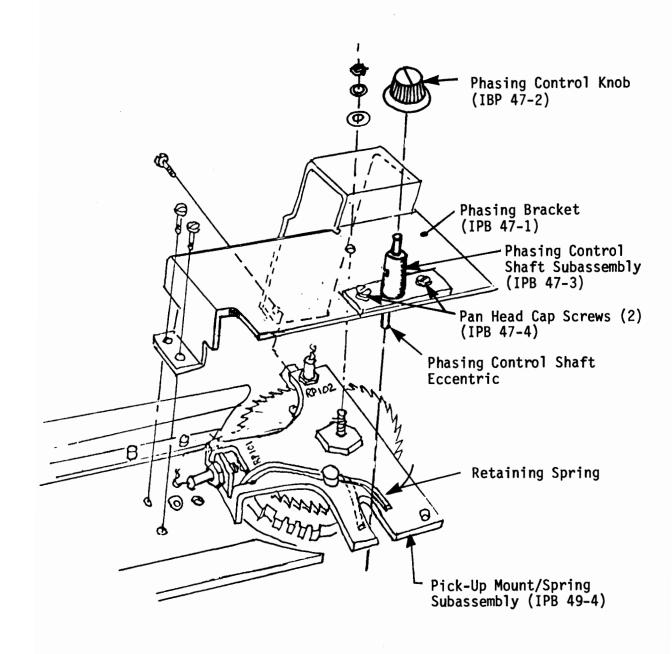

Fine adjustment of hammer firing time is accomplished by means of a PHAS-ING CONTROL that permits movement of the CSTB and INDEX transducers in tandem about a common axis. As shown in Figure 2-16, a phasing bracket subassembly is mounted above the pick-up mount/spring subassembly that carries the CSTB and INDEX transducers. After pushing the retaining spring on the pick-up mount to the left, the eccentric at the bottom of the phasing control shaft is inserted into the slot in the pick-up mount/spring subassembly. Once the phasing control bracket subassembly is bolted in place, rotating the PHASING CONTROL knob will cause the pick-up mount to rotate by means of the eccentric that rides in the pick-up mount slot. The setting of the PHASING CONTROL is held in place by the retaining spring on the pick-up mount.

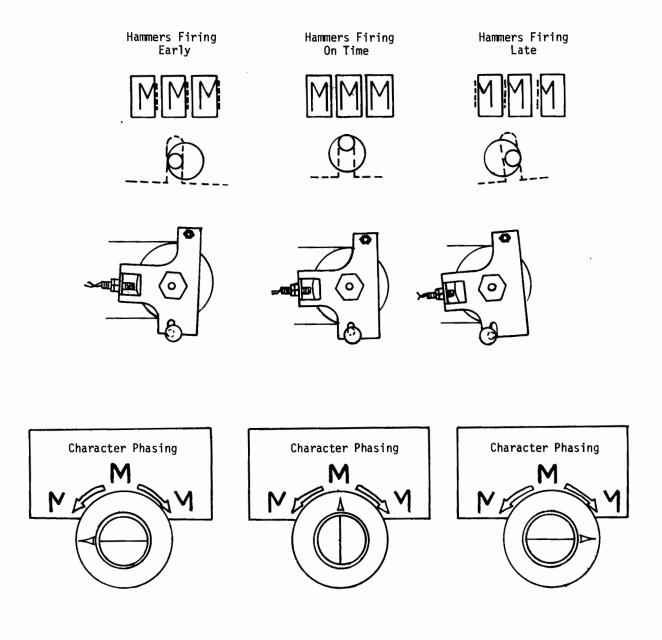

Figure 2-17 shows the effect of rotating the PHASING CONTROL from left to right. When the knob is rotated to the left, the pick-up mount is rotated to the right, advancing hammer firing time. Conversely, when the knob is rotated to the right, the pick-up mount is rotated to the left retarding hammer firing time.

During factory assembly, the pan head screws (shown in Figure 2-16) are backed off slightly to permit lateral adjustment of the phasing control shaft subassembly. With the PHASING CONTROL knob centered so the eccentric is in its neutral top-of-slot position, the phasing control shaft subassembly is

Figure 2-16. Phasing Control Assembly.

Figure 2-17. Phasing Control Operation.

shifted in the appropriate direction to center characters in their column positions as shown in the drawings down the center of Figure 2-17. The pan head screws are then tightened securely and the PHASING CONTROL knob removed and reinstalled in the same position after the right-hand yoke cover is mounted in place.

Once this is done, turning the PHASING CONTROL knob to the left will produce right-hand side clipping; conversely, turning it to the right will produce left-hand side clipping. That is the meaning of the "CHARACTER PHASING" decals shown in Figure 2-17. If the phasing control shaft is properly centered it will be impossible to phase-in another character when the PHASING CONTROL knob is rotated to its extreme right or left position. The decal is useful when centering the phasing assembly as described in Section 3.5.1.4.2 ("Character Phasing Adjustment") of the Maintenance Instructions (DPC Form 1260/90/10-3). The decal DOES NOT show the direction in which to turn the PHASING CONTROL knob in order to cure side clipping.

#### CAUTION

When performing this adjustment follow the maintenance instructions carefully: it is not only possible to phase in an entirely different character but also possible to damage print hammers and slugs.

The diamond-shaped character on slug #5 (Figure 2-9) occupies the position of the space code and can never print when the phasing control shaft is properly positioned laterally. If the diamond shows up when printing a RIPPLE pattern, it is a certain indication that the phasing control shaft subassembly is out of adjustment.

Now for a simple rule: keep your eyes on the copy and turn the PHASING CONTROL knob to the <u>right</u> to eliminate <u>right</u>-hand side clipping or to the <u>left</u> to eliminate <u>left</u>-hand side clipping.

Remember: clipping that cannot be removed by means of the PHASING CONTROL is an indication that the flight time of the hammer corresponding to the clipped column position is out of adjustment.

# 2.2.8 Hammer Driver Cabling

Each hammer actuator is energized by means of a dedicated constant current hammer driver, a typical example of which is shown at the bottom of CD 5.0.0 ("LSI Hammer Driver Board"). Regardless of the length of the typeline (132 or 136 columns), thirty-four discrete constant current hammer drivers are contained on each of the four hammer driver boards used in any DPC 1200 Series printer.

Each board is dedicated exclusively to hammers of a single phase. Because all actuators in any given row on the frame assembly correspond to print hammers of the same phase, actuator cabling is straightforward as illustrated in Table 2-1.

The leads from all actuators in any given row terminate in a single plug that mates with double-sided tabs at the top edge of the hammer driver board dedicated to that phase (row). Plug, bay position, and phase numbering have been made consistent to minimize confusion when servicing these components.

It is impossible to remove a hammer driver board from the logic bay without first removing the actuator cabling plug attached to it at the top. When reinserting a hammer driver board, make sure it is securely seated so that a break in the series of hammer driver interlock connections (CD 5.0.1 "Hammer Driver Interconnection Wiring") will not generate an alarm. Remember, also, to reinsert the proper actuator cabling plug, which is keyed to prevent improper insertion.

2-28

TABLE 2-1

HAMMER ACTUATOR CABLING

| PHASE | ACTUATOR ROW   | COLUMN POSITIONS                                                                                                       | PLUG  | LOGIC BAY<br>POSITION |

|-------|----------------|------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|

| Ø1    | Upper Straight | 1, 5, 9, 13 · · · 129, (133) 2, 6, 10, 14 · · · 130, (134) 3, 7, 11, 15 · · · 131, (135) 4, 8, 12, 16 · · · 132, (136) | P-221 | 1                     |

| Ø2    | Lower Straight |                                                                                                                        | P-222 | 2                     |

| Ø3    | Upper Offset   |                                                                                                                        | P-223 | 3                     |

| Ø4    | Lower Offset   |                                                                                                                        | P-224 | 4                     |

#### 2.3 RIBBONFEED MECHANISM

The Ribbonfeed Mechanism can be broken down into two major components: (1) a ribbon drive assembly (IPB 43-37) and its associated motor (IPB 43-34), which are mounted at the right, front side of the yoke; and (2) a ribbon sensing assembly (ipb 43-38), which is mounted at the left, front side of the yoke. These mechanisms automatially control the feeding, reversing, and skewing of mandrel-wound, towel-form ribbon over the faces of the upper and lower ribbon/slug guides.

## 2.3.1 Ribbonfeeding and Reversing

Ribbon drive direction is determined by upper and lower ribbon reversing dogs on the ribbon drive assembly. When the upper reversing dog is pushed forward by the ribbon reversing bar attached to the end of the ribbon fed from the upper mandrel, drive is supplied to the upper hub, and the lower hub is declutched. Ribbon is then wound on to the upper mandrel until the lower ribbon reversing bar pushes the lower reversing dog forward. When that happens, ribbon is fed in the opposite direction from the upper mandrel to the lower. The upper hub is declutched, and take-up drive is supplied to the lower mandrel. Ribbon drag in both the upper and lower mandrel hubs is adjustable

as explained in Section 3.5.3 of the <u>Maintenance Instruction</u> manual (DPC Form 1260/90/10-3). Two different ribbon drive assemblies are available according to the length of the typeline selected.

# 2.3.2 Ribbon Skewing

Ribbon is skewed back and forth across the typeline in order to maximize ribbon life. Skewing is controlled automatically by the ribbon sensing assembly. Whenever the left-hand edge of the ribbon trips the mechanical ribbon sensor, the skew position of the upper and lower left-hand mandrel hubs is changed causing ribbon to track in the opposite direction. This mechanism is not adjustable but does require careful, periodic cleaning as described in Section 3.5.3 of the Maintenance Instruction manual (DPC Form 1260/90/10-3).

#### 2.4 PAPERFEED MECHANISM

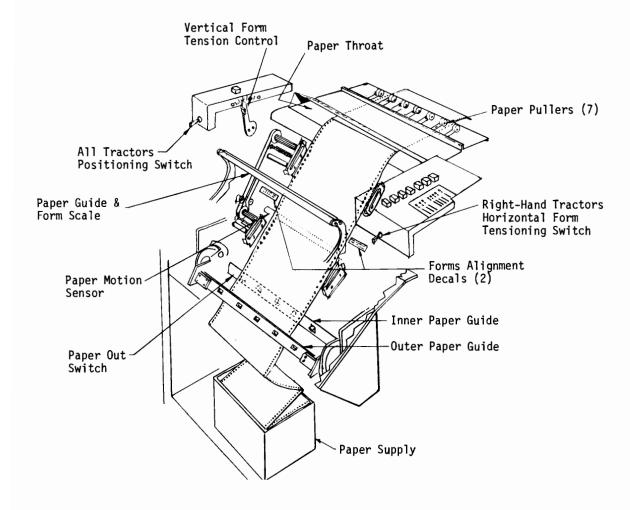

Printout is recorded on standard fanfold, sprocket-fed, single- or multipart paper forms. Paper enters the printer at the front from an enclosed space directly below the yoke and exits the printer at the rear into a paper receptical (Figure 2-18). Paperfeeding is a microprocessor-controlled process that is accomplished by phase switching a stepper motor, which is coupled to pin-feed paper tractors, through the exact number of steps needed to advance paper to the next desired linespace. A single line advance at 6 LPI takes approximately 15 milliseconds in all models, however configured. Paper slewing occurs at the rate of 20 or 40 IPS depending on the model or option selected.

The Paperfeed Mechanism in all CT-1260, CT-1290, CT-1210 models consists of the following subsystems: (1) two pairs of motor-driven paper tractors (2.4.1); (2) a FORM TENSION Control (2.4.2); (3) a manually-switched, motorized tractor positioning system (2.4.3); (4) a retractable PAPER GUIDE/SCALE

Figure 2-18. Paperfeed Path.

(2.4.4); (5) a DC stepper motor tractor drive system (2.4.5); (6) an INFINITE FORMS POSITION CONTROL (2.4.6); (7) a paper low switch (2.4.7); (8) a paper motion sensor (2.4.8); and (9) a paper receptical (2.4.9).

Individual printers in this series may also have the following: (1) a motor-driven paper puller (2.4.10); (2) a static eliminator (2.4.11); (3) an 8- or 12-channel Vertical Format Unit (VFU) punched tape reader (2.4.12), and (4) a 6/8 LPI switch, which permits operator selection of 6 or 3 LPI spacing (2.4.13).

Each component in the Paperfeed Mechanism will be dealt with in turn in the subsections indicated above.

## 2.4.1 Paper Tractors

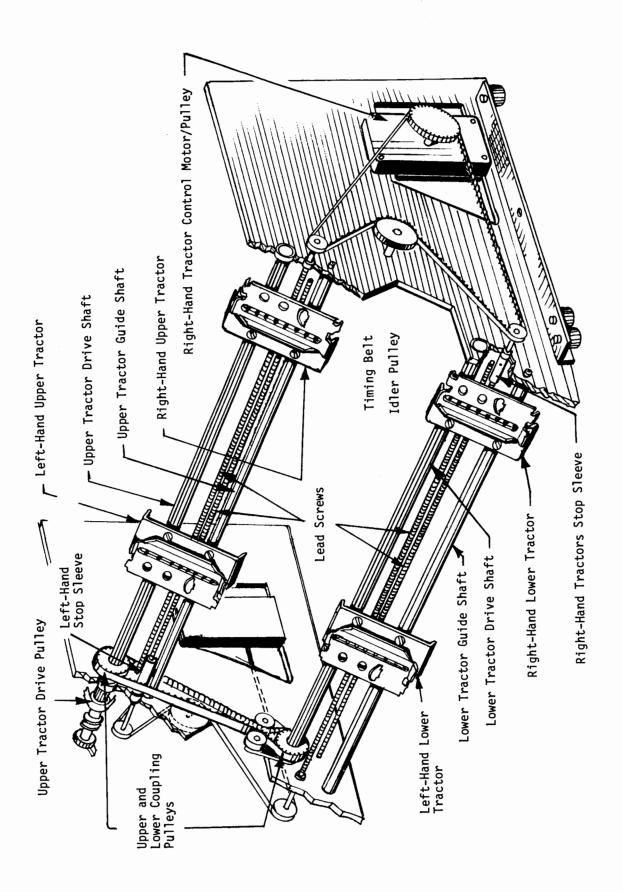

Two pairs of motor-driven, pin-feed paper tractors--one pair of which is mounted above and the other below the hammer bank--hold paper stationary during printout and transport paper vertically during a paperfeed operation (Figure 2-19). Each pair consists of a left-hand (IPB 36 A/B) and a right-hand (IPB 37) tractor, both of which share a common tractor guide shaft and a common splined drive shaft (IPB 28, Dwg. 1 of 2). The upper and lower tractor drive shafts are coupled by means of upper and lower toothed pulleys and a timing belt. The four tractors are driven in tandem by way of an upper tractor drive pulley (IPB 34-7), which is located on the outside of the left-hand side frame assembly.

The upper and lower tractors use different tractor frame bushings (IPB 36-15/16 and 37-15/16) so that the bushing's 1/4-20 "tap thru's" and clearance holes will be properly aligned with the tractor positioning system lead screws. Except for the different bushings, the upper and lower right-hand tractors are identical in all printers in this series. The same is true of the upper and lower left-hand tractors except on CT-1260 printers, which have a paper low switch incorporated as an intergral part of the lower left-hand tractor assembly (IPB 36B).

Figure 2-19. Paperfeed Tractors.

## 2.4.2 Vertical Form Tension Control

Vertical form tensioning is accomplished manually by means of an adjustable idler pulley/lever assembly that affects the position of the lower tractor drive shaft—and, thereby, the position of the lower tractor feed pins—relative to the stationary position of the upper tractor drive shaft and feed pins (Figure 2-20). The setting of the handle/pointer is retained by a detent mechanism located on the outside of the left-hand side frame assembly (IPB 29).

## 2.4.3 Tractor Positioning System

A manually switched, motor-driven lead screw tractor positioning system permits movement of all tractors in tandem, left or right, for forms positioning (margin set up) and movement of the upper and lower right-hand tractors, left or right, for horizontal forms tensioning (Figure 2-19).

The ALL TRACTORS switch turns on both the left- and right-hand tractor positioning motors simutaneously for forms positioning. The RIGHT-HAND TRACTORS switch turns on only the right-hand tractor motor for horizontal forms tensioning. The ALL TRACTORS switch ("S-111" on CD 12.0.1) is located in front, below the left-hand control panel. The RIGHT-HAND TRACTORS switch ("S-107" on CD 12.0.1) is located in front, below the right-hand control panel. Both are three-position, spring-loaded switches that return to a neutral center position (motors "off") when released. In order to prevent damage to the positioning system through operator error, the switches are wired so that the RIGHT-HAND TRACTORS switch is disabled whenever the ALL TRACTORS switch is toggled out of its neutral ("off") position.

The position of the upper and lower right-hand tractors is controlled by a right-hand tractor control motor ("B-104" on CD 12.0.2), mounted inside the right-hand side frame assembly (IPB 30-3). The motor drives the right-hand tractor positioning lead screws by means of toothed pulleys and a timing belt as shown in Figure 2-19. The position of the left-hand tractors is controlled in a similar way by a left-hand tractor control motor ("B-103" on CD

Figure 2-20. Vertical Form Tension Control.

12.0.1), mounted inside the left-hand side frame assembly (IPB 29-4).

Left- and right-hand tractor stop sleeves (Figure 2-19) prevent damage to components mounted inside either side frame assembly if an operator inadvertantly runs the tractors too far to the right or left. Running a tractor up against either stop sleeve produces an audible alarm that is the result of drive belt slippage on the lead screw drive pulleys. It may also cause misalignment of the upper and lower tractors on that side and should, therefore, be avoided. A similar alarm will be produced with similar results if the right- and left-hand tractors are run together.

The tractors motors can be operated whenever "ON" is illuminated. After power-up, their operation takes place independently of the Control System.

# 2.4.4 Paper Guide/Scale

The retractable Paper Guide/Scale (IPB 43 and 48) serves three purposes. First, the forms scale cross members (IPB 48-3 and -4) prevent smudging by keeping paper from contacting the ribbon when the printer is idling or feeding paper. Second, the forms scale (IPB 48-17) that is mounted on the upper paper guide cross member allows the operator to properly position the left- and right-hand margins opposite the print hammers, which are obscured by the paper forms. The third purpose of the paper guide--one which is dealt with more fully in section 2.4.8. below--involves a presser foot (IPB 48-5) that is mounted on the left-hand side of the lower paper guide cross member. When the yoke is closed and latched, the spring fingers on the presser foot assure proper contact between the paper forms and a roller assembly that is part of the paper motion sensing mechanism.

# 2.4.5 Stepper Motor Tractor Drive System

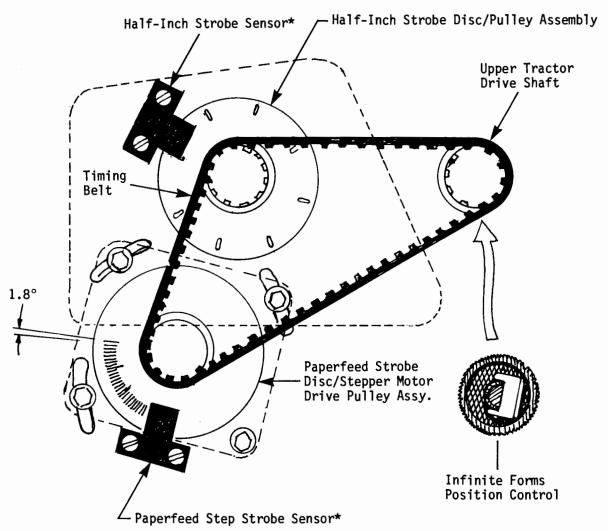

Paperfeeding is accomplished by phase-switching a DC stepper motor, which is coupled to the tractors by way of the upper tractor drive pulley, through the number of steps required to move paper to the next desired linespace (Figure 2-21). The motor, which is driven by the Control System through com-

# \*NOTE

Careful adjustment of the Step Strobe and Half-Inch Strobe sensors is essential for proper operation. These adjustments are described in detail in sections 3.5.2.3.3. and 3.5.2.4 of the Maintenance Instructions manual (DPC Form 1260/90/10-2).

Figure 2-21. Stepper Motor Tractor Drive System.

mands sent to the Paperfeed Stepper Drive Board (CD 4.0.0), is moved in discrete steps of  $1.8^{\circ}$  by progressively switching pairs of its four phase windings. Two hundred steps are needed for one revolution ( $1.8^{\circ}$  x 200 =  $360^{\circ}$ ).

The motor-to-tractor gear ratio is such that 48 steps are required to move paper through a distance of one inch. Thus, when the printer is configured to transport paper at 6 LPI, movement of one line requires 8 steps; conversely, when the printer is configured to transport paper at 8 LPI, movement of one line requires 6 steps.

To make paper slewing possible, the stepper motor is operated in a closed-loop fashion with step strobe pulses ("(-) PF STB" on CD 7.0.0 and 3.2.0) being returned to the Control System by means of a timing disc attached to the stepper motor shaft (Figure 2-21). These pulses force-feed the Control System the positional data needed to accurately control the Paperfeed Mechanism. Thus, the commutation of the pairs of motor windings--which is timed to lead the actual shaft position by variable amounts as the mechanism is accelerated and decelerated during a paper slew operation--can be performed in perfect synchronism with the rotating motor shaft.

High speed slew (40 IPS, rather than 20 IPS) is accomplished by the Control System program forcing the mechanism to take an extra step during acceleration and, then, skipping one step during deceleration.

A half-inch strobe ("(-) 1/2 IN STB" on CD 7.0.0 and 3.3.0) is generated once every 24 steps by means of a half-inch strobe disc and its associated optical sensor as shown in Figure 2-21. Half-inch strobe pulses are used during system initialization to establish a starting Top of Form (TOF) position and, thereafter, to validate positioning of the mechanism.

In addition to transporting paper vertically during a line-feed or slew operation, the paperfeed stepper motor performs a second important tasks: it holds paper stationary while printing takes place and while the machine is idling. The Control System accomplishes this automatically whenever at ther end of a feed operation it removes "INC I (+)" from the Paperfeed Stepper

Drive Board (CD 4.0.0). When "INC I (+)" is removed, a chopper circuit on that board applies a reduced power level to the last pair of windings energized during the preceding paperfeed operation.

## 2.4.6 Infinite Forms Position Control

Alignment of the actual top line of the paper form with the nominal Top-of-Form (TOF) position set up and held stationary by the Control System is accomplished by means of the INFINITE FORMS POSITION CONTROL (IPB 34). This control makes it possible to declutch the upper tractor drive shaft from the stepper motor drive system so that the vertical position of the paper forms can be adjusted independently of the holding position of the stepper motor. Pulling out the cam lever releases the pressure exerted on the upper tractor drive pulley by the inner and outer cones (IPB 34-3 and -10) making it possible to move paper up or down without disturbing the holding position of the stepper motor. Forms alignment decals on the paper platen (IPB 38-3), which show the position of the typeline relative to the left- and right-hand margins on the paper forms, permit operators to accurately align the actual paper TOF with the nominal TOF position of the printer mechanism.

# 2.4.7 Paper Low Switch (CD 7.0.0)

As already noted, the paper low switch is an integral part of the lower left-hand tractor on CT-1260 printers (IPB 36B). Normally open, the switch is closed whenever paper is installed in the tractor and the pressure plate is closed. The switch will open again when the bottom of the last remaining form passes through, releasing the switch button. This occurs on CT-1260 printers when 6.5 inches of the last form remains in the printer.

The paper low switch used in CT-1290 and CT-1210 printers operates in a similar way. Located in the paper throat gap (IPB 28), it generates a paper low signal when 8.5 inches of the last form remains in the printer. Normally open, the switch closes whenever paper is installed between the inner and outer paper guides and the yoke is closed and latched. The outer paper guide presses paper against five sensing fingers that protrude through corresponding

slots in the inner paper guide. The fingers cause the pivot bar on which they are mounted to rotate, which in turn causes the paper low switch set screw in the contact arm at the left-hand end of the pivot bar to close the paper low switch. When the bottom of the last remaining form passes through the throat gap, the sensing fingers pass through the corresponding slots in both the inner and outer paper guides, opening the switch and generating a paper low signal ("(-)PAPER LOW" on CD 1.4.1).

The paper low switch, regardless of model, interfaces with the Control System as shown on CD 7.0.0, 0.1.1, 1.4.1, 1.2.0, and 3.3.0. When the switch opens, IC-12A on CD 1.4.1 generates "(-) PAPER LOW", which turns on "PAPER LOW" on the right-hand control panel. At the same time, IC-11A generates "(-) PAPER LOW", which is sent to "DI-5" of input port 12 to the external device (via IC-6A on CD 1.2.0) as "(+) PAPER LOW". When feeding paper, the Control System polls input port 12 for "(-) PAPER LOW" once every line. When it finds "(-) PAPER LOW", it allows printing and feeding to continue for an additional 5-inches (CT-1260) or 7-inches (CT-1290 and CT-1210) before looking for TOF. When it finds TOF it illuminates "STOP," "ALARM," and "PAPER OUT," and it refuses to permit operation in the RUN Mode until "PAPER LOW" is cleared by loading more paper forms.

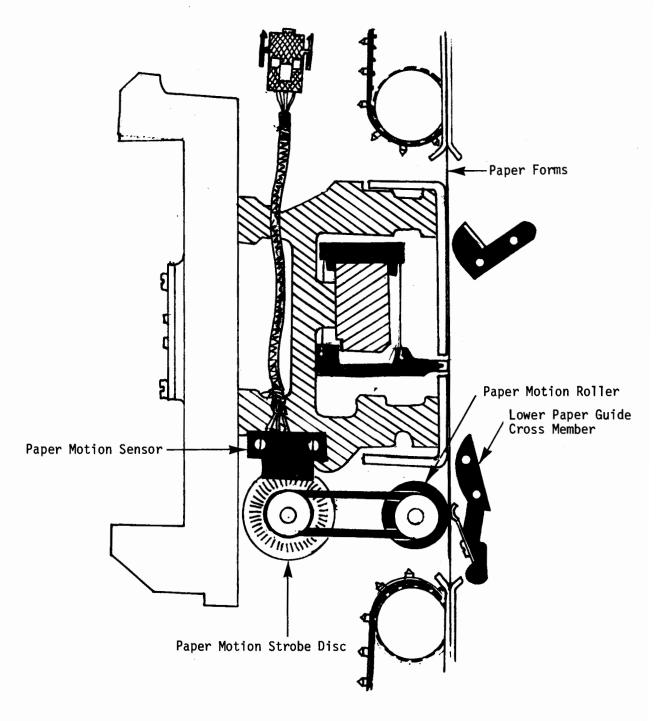

## 2.4.8 Paper Motion Sensor

The paper motion sensor is mounted on the hammer bank as shown in IPB 42. It consists of a roller and associated drive pulley that is coupled to a paper motion disc by means of an 0-ring drive belt. When the yoke is closed, paper is pressed against the paper motion roller by means of the presser foot on the lower paper guide cross member, which causes paper motion to be transmitted to the paper motion strobe disc (Figure 2-22).

The disc rotates with paper motion and interrupts the light path in the paper motion optoelectrical sensor (CD 7.0.0). The first slot-to-no-slot transition produces a positive edge that triggers the paper motion latch ("IC-40A") on CD 3.3.0. The latch responds by making a "logical 1" available to "DI-8" of input port 12, thus, indicating that paper motion has occured.

(Left-Hand Side View)

Figure 2-22. Paper Motion Sensor

At the end of every paperfeed operation (be it merely a single line advance of a slew-to-channel feed), the Control System polls input port 12 to verify that paper motion has occured. If a "logical l" is not present at "DI-8", the Control System will illuminate "PAPER JAM", "STOP," and "ALARM" on the right-hand control panel and take the printer off-line. The jam must be corrected and the reset switch (ALARM) depressed to return the printer to normal operation.

When a paper low occurs it "fakes" a paper motion signal in order to permit the last form to be printed even though no paper motion signal can be generated once the tail end of the last form gets past the paper motion roller. It does this by using "(-) PAPER LOW" to hold the paper motion latch ("IC-40A" on CD 3.3.0) in the set state so that the Control System will think that paper motion has occured.

# 2.4.9 Paper Receptical

Two types of paper recepticals are used on DPC 1200 Series printers. The first type, a simple paper basket (IPB 1), is standard equipment on CT-1260 and not available on the others. The second, a paper catcher (IPB 2), is standard on CT-1290 and CT-1210 and optional on the CT-1260. Both are equipped with a ground cord, which must be inserted into the jack at the lower left rear of the printer to prevent stacking problems due to static build up

## 2.4.10 Paper Puller

A motor-driven paper puller is required standard equipment on CT-1210 models and optional on CT-1260 and CT-1290 models unless they are programmed for the optional 40 IPS slew speed, in which case a paper puller is required. The paper puller consists of a pressure roller assembly (IPB 60) and a corresponding drive roller assembly (IPB 61) that are located near the paper exit point on the main platen assembly (IPB 59) at the top, rear of the machine. The drive roller is coupled to a small AC motor (IPB 33) by means of pulleys and a timing belt. The paper puller motor is turned on whenever "ON" is illuminated (CD 12.0.2).

The paper puller will not affect print quality when the printer is holding paper stationary because friction drive is applied to the non-print side of the paper. This mechanism is adjustable and may require periodic service as described in Section 3.5.2.8 of the <u>Maintenance Instructions</u> manual (DPC Form 1260/90/10-3).

#### 2.4.11 Static Eliminator

Available as an option on all models, an air-ioizing static eliminator is recommended whenever the printers are operated in a dry environment (IPB Option). It consists of a lugged static bar and an accompanying HV trans former capable of delivering 7 KV RMS to the bar. The lugs on the bar leak a charge to the paper, which eliminates paper drag due to static build up. The static bar should be cleaned weekly as instructed in Table 3-7 in the Maintenance Instruction manual (DPC 1260/90/10-3).

#### CAUTION

Before attempting to clean the lugged static eliminator bar, ALWAYS (1) turn off the Primary Circuit Breaker and (2) unscrew and disconnect the HV cable at the static eliminator transformer.

## 2.4.12 Vertical Format Units