## HP 9800 Computer Systems

1

# MC68000 User's Manual

# MC68000

16-BIT MICROPROCESSOR User's Manual .

# MC68000

## 16-BIT MICROPROCESSOR User's Manual

### **Third Edition**

PRENTICE-HALL, Inc., Englewood Cliffs, N.J. 07632

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

Library of Congress Catalog Number 81-85502 ISBN 0-13-566695-3 (pbk.) ISBN 0-13-566703-8 (case) ISBN 0-13-566703-2 (limited ed.) ISBN 0-13-566760-7 (special ed.)

Editorial/production supervision: Karen Skrable Manufacturing buyer: Gordon Osbourne

© 1982, 1980, 1979 by Motorola Inc.

All rights reserved. No part of this book may be reproduced in any form or by any means without permission in writing from the publisher.

Motorola reserves the right to make changes to any products herein to improve functioning or design. Although the information in this document has been carefully reviewed and is believed to be reliable, Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

This manual does not define a specific assembly programming language. The language and notation used within this manual is a register transfer language explained in Appendix B.

Printed in the United States of America

10 9 8 7 6 5 4 3

ISBN 0-13-566695-3 {PBK.} ISBN 0-13-566703-8 {CASE} ISBN 0-13-566737-2 {LIMITED ED.} ISBN 0-13-566760-7 {SPECIAL ED.}

Prentice-Hall International, Inc., London Prentice-Hall of Australia Pty. Limited, Sydney Prentice-Hall of Canada, Ltd., Toronto Prentice-Hall of India Private Limited, New Delhi Prentice-Hall of Japan, Inc., Tokyo Prentice-Hall of Southeast Asia Pte. Ltd., Singapore Whitehall Books Limited, Wellington, New Zealand

### TABLE OF CONTENTS

' Paragraph No.

Title

### Page No.

### Section 1 General Description

| 1,1   | Introduction                                | 1 |

|-------|---------------------------------------------|---|

| 1.2   | Overview                                    | 1 |

| 1.3   | Software Development                        | 5 |

| 1.3.1 | Consistent Structure                        |   |

| 1.3.2 | Structured Modular Programming              | 5 |

| 1.3.3 | Improved Software Testability               |   |

| 1.3.4 | Future Flexibility                          |   |

| 1.3.5 | Memory Management of Large Addressing Space |   |

| 1.3.6 | Improved Code Density and Speed             |   |

| 1.3.7 | Software Support and M6800 Compatibility    |   |

### Section 2

### **Data Organization and Addressing Capabilities**

| 2.1      | Introduction                                 | 13 |

|----------|----------------------------------------------|----|

| 2.2      | Operand Size                                 | 13 |

| 2.3      | Data Organization in Registers               | 13 |

| 2.3.1    | Data Registers                               |    |

| 2.3.2    | Address Registers                            |    |

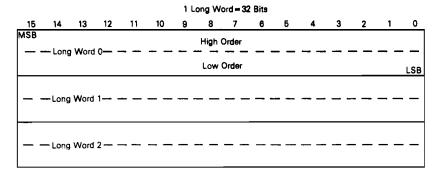

| 2.4      | Data Organization in Memory                  |    |

| 2.5      | Addressing                                   | 15 |

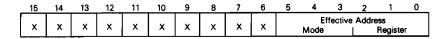

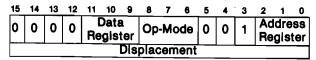

| 2.6      | Instruction Format                           |    |

| 2.7      | Program/Data References                      |    |

| 2.8      | Register Notation                            |    |

| 2.9      | Address Register Indirect Notation           |    |

| 2.10     | Register Specification                       | 17 |

| 2.11     | Effective Address                            | 17 |

| 2.11.1   | Register Direct Modes                        |    |

| 2.11.1.1 | Data Register Direct                         |    |

| 2.11.1.2 | Address Register Direct                      |    |

| 2.11.2   | Memory Address Modes                         | 18 |

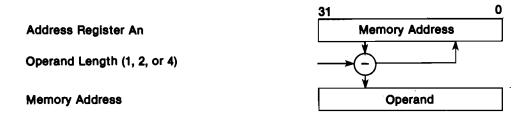

| 2.11.2.1 | Address Register Indirect                    | 18 |

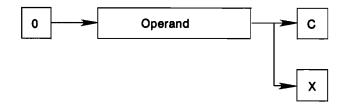

| 2.11.2.2 | Address Register Indirect with Postincrement | 18 |

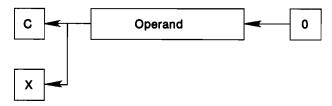

| 2.11.2.3 | Address Register Indirect with Predecrement  | 18 |

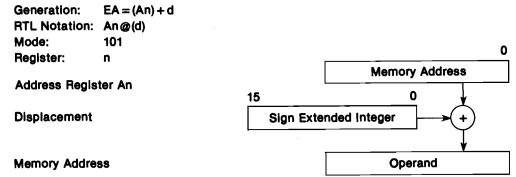

| 2.11.2.4 | Address Register Indirect with Displacement  | 19 |

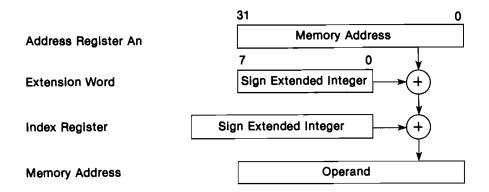

| 2.11.2.5 | Address Register Indirect with Index         | 19 |

| 2.11.3   | Special Address Modes                        | 20 |

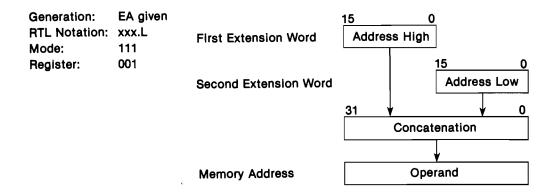

| 2.11.3.1 | Absolute Short Address                       | 20 |

| 2.11.3.2 | Absolute Long Address                        |    |

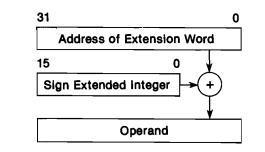

| 2.11.3.3 | Program Counter with Displacement            |    |

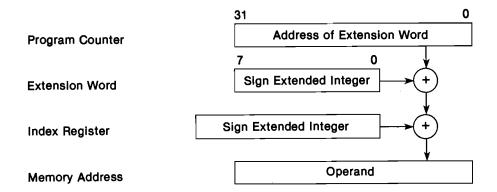

| 2.11.3.4 | Program Counter with Index                   | 21 |

| 2.11.3.5 | Immediate Data                               | 22 |

| 2.11.4   | Effective Address Encoding Summary           |    |

| 2.12     | Implicit Reference                           |    |

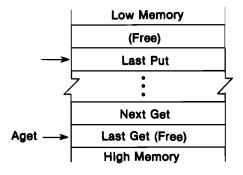

| 2.13     | Stacks and Queues                            |    |

| 2.13.1   | System Stack                                 | 23 |

| 2.13.2   | User Stacks                                  | 24 |

| 2.13.3   | Queues                                       | 25 |

Paragraph No.

Title

Page No.

### Section 3 Instruction Set Summary

| 3.2 Data Movement Operations        | 27 |

|-------------------------------------|----|

|                                     |    |

| 3.3 Integer Arithmetic Operations   | 27 |

| 3.4 Logical Operations              |    |

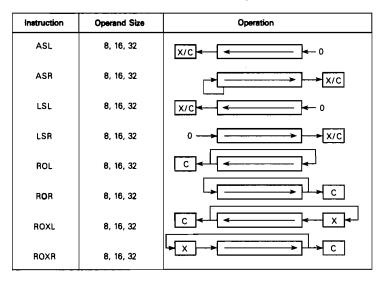

| 3.5 Shift and Rotate Operations     |    |

| 3.6 Bit Manipulation Operations     |    |

| 3.7 Binary Coded Decimal Operations |    |

| 3.8 Program Control Operations      |    |

| 3.9 System Control Operations       |    |

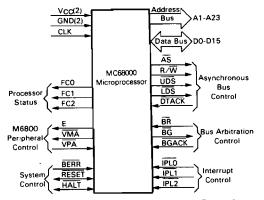

### Section 4 Signal and Bus Operation Description

| 4.1     | Introduction                            | 33 |

|---------|-----------------------------------------|----|

| 4.2     | Signal Description                      | 33 |

| 4.2.1   | Address Bus (A1 through A23)            | 33 |

| 4.2.2   | Data Bus (D0 through D15)               | 33 |

| 4.2.3   | Asynchronous Bus Control                | 34 |

| 4.2.3.1 | Address Strobe (AS)                     | 34 |

| 4.2.3.2 | Read/Write (R/W)                        | 34 |

| 4.2.3.3 | Upper and Lower Data Strobes (UDS, LDS) | 34 |

| 4.2.3.4 | Data Transfer Acknowledge (DTACK)       | 34 |

| 4.2.4   | Bus Arbitration Control                 | 34 |

| 4.2.4.1 | Bus Request (BR)                        |    |

| 4.2.4.2 | Bus Grant (BG)                          | 34 |

| 4.2.4.3 | Bus Grant Acknowledge (BGACK)           | 35 |

| 4.2.5   | Interrupt Control (IPLO, IPL1, IPL2)    | 35 |

| 4.2.6   | System Control                          | 35 |

| 4.2.6.1 | Bus Error (BERR)                        | 35 |

| 4.2.6.2 | Reset (RESET)                           | 35 |

| 4.2.6.3 | Halt (HALT)                             | 35 |

| 4.2.7   | MC6800 Peripheral Control               |    |

| 4.2.7.1 | Enable (E)                              |    |

| 4.2.7.2 | Valid Peripheral Address (VPA)          |    |

| 4.2.7.3 | Valid Memory Address (VMA)              | 36 |

| 4.2.8   | Processor Status (FC0, FC1, FC2)        | 36 |

| 4.2.9   | Clock (CLK)                             | 36 |

| 4.2.10  | Signal Summary                          | 37 |

| 4.3     | Bus Operation                           |    |

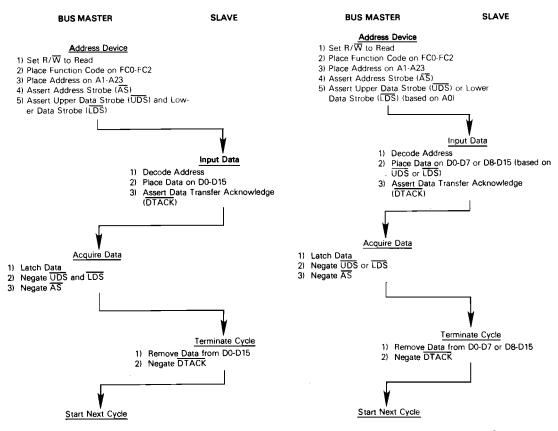

| 4.3.1   | Data Transfer Operations                |    |

| 4.3.1.1 | Read Cycle                              | 38 |

| 4.3.1.2 | Write Cycle                             | 39 |

| 4.3.1.3 | Read-Modify-Write Cycle                 |    |

| 4.3.2   | Bus Arbitration                         | 45 |

| 4.3.2.1 | Requesting the Bus                      | 45 |

| 4.3.2.2 | Receiving the Bus Grant                 |    |

| 4.3.2.3 | Acknowledgement of Mastership           | 47 |

| 4.3.2.4 | Bus Arbitration Control                 | 47 |

#### Title Paragraph No. Page No. 4.3.3 Bus Error and Halt Operation......47 4.3.3.1 4.3.3.2 4.3.3.3 4.3.3.4 4.3.4 4.3.5

### Section 5 Exception Processing

| 5.1   | Introduction                             |        |

|-------|------------------------------------------|--------|

| 5.2   | Processing States                        |        |

| 5.3   | Privilege States                         |        |

| 5.3.1 | Supervisor State                         |        |

| 5.3.2 | User State                               |        |

| 5.3.3 | Privilege State Changes                  |        |

| 5.3.4 | Reference Classification                 |        |

| 5.4   | Exception Processing                     |        |

| 5.4.1 | Exception Vectors                        |        |

| 5.4.2 | Kinds of Exceptions                      |        |

| 5.4.3 | Exception Processing Sequence            |        |

| 5.4.4 | Multiple Exceptions                      | 62     |

| 5.5   | Exception Processing Detailed Discussion |        |

| 5.5.1 | Reset                                    |        |

| 5.5.2 | Interrupts                               |        |

| 5.5.3 | Instruction Traps                        |        |

| 5.5.4 | Illegal and Unimplemented Instructions   |        |

| 5.5.5 | Privilege Violations                     |        |

| 5.5.6 | Tracing                                  |        |

| 5.5.7 | Bus Error                                |        |

| 5.5.8 | Address Error                            |        |

|       |                                          | ······ |

### Section 6 Interface with M6800 Peripherals

| 6.1 | Introduction71                  |

|-----|---------------------------------|

| 6.2 | Data Transfer Operation71       |

| 6.3 | Interrupt Interface Operation74 |

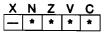

### Appendix A Condition Codes Computation

| A.1 | Introduction                     | 75 |

|-----|----------------------------------|----|

| A.2 | Condition Code Register          |    |

| A.3 | Condition Code Register Notation |    |

| A.4 | Condition Code Computation       |    |

| A.5 | Conditional Tests                |    |

Paragraph No.

Titie '

Page No.

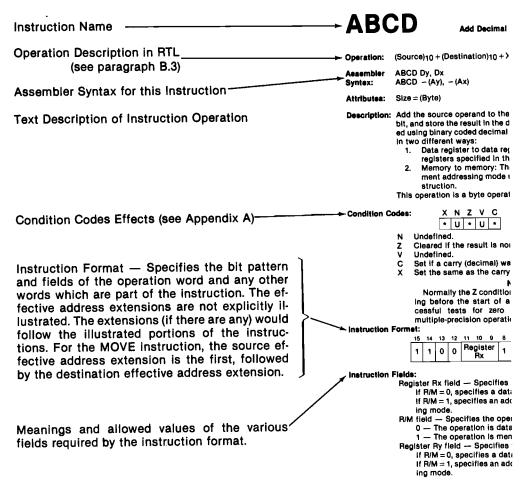

### Appendix B Instruction Set Details

| B.1 | Introduction                           |    |

|-----|----------------------------------------|----|

| B.2 | Addressing Categories                  |    |

| B.3 | Instruction Description                | 80 |

| B.4 | Register Transfer Language Definitions |    |

|     | Instructions (listed alphabetically)   |    |

|     |                                        |    |

### Appendix C Instruction Format Summary

| C.1  | Introduction                                                          | 183 |

|------|-----------------------------------------------------------------------|-----|

| C.2  | Bit Manipulation, Move Peripheral, Immediate Instructions             | 184 |

| C.3  | Move Byte Instruction                                                 | 186 |

| C.4  | Move Long Instruction                                                 |     |

| C.5  | Move Word Instruction                                                 |     |

| C.6  | Miscellaneous Instructions                                            |     |

| C.7  | Add Quick, Subtract Quick, Set Conditionally, Decrement Instructions. | 191 |

| C.8  | Branch Conditionally Instructions                                     |     |

| C.9  | Move Quick Instruction                                                |     |

| C.10 | OR, Divide, Subtract Decimal Instructions                             |     |

| C.11 | Subtract, Subtract Extended Instructions                              | 192 |

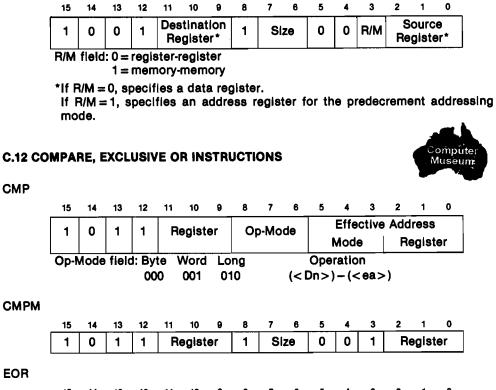

| C.12 | Compare, Exclusive OR Instructions                                    |     |

| C.13 | AND, Multiply, Add Decimal, Exchange Instructions                     |     |

| C.14 | Add, Add Extended Instructions                                        |     |

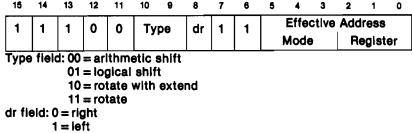

| C.15 | Shift/Rotate Instructions                                             |     |

|      |                                                                       |     |

### Appendix D instruction Execution Times

| D.1  | Introduction                                        |  |

|------|-----------------------------------------------------|--|

| D.2  | Effective Address Operand Calculation Timing        |  |

| D.3  | Move Instruction Clock Periods                      |  |

| D.4  | Standard Instruction Clock Periods                  |  |

| D.5  | Immediate Instruction Clock Periods                 |  |

| D.6  | Single Operand Instruction Clock Periods            |  |

| D.7  | Shift/Rotate Instruction Clock Periods              |  |

| D.8  | Bit Manipulation Instruction Clock Periods          |  |

| D.9  | Conditional Instruction Clock Periods               |  |

| D.10 | JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods |  |

| D.11 | Multi-Precision Instruction Clock Periods           |  |

| D.12 | Miscellaneous Instruction Clock Periods             |  |

| D.13 | Exception Processing Clock Periods                  |  |

|      |                                                     |  |

### Appendix E Prefetch

| E.1 | Introduction         | )5 |

|-----|----------------------|----|

| E.2 | Instruction Prefetch | )5 |

|     | Data Prefetch        |    |

|     |                      |    |

Paragraph No.

Titie

Page No.

### Appendix F MC68451 Memory Management Unit

| F.1       | Introduction                      | .207 |

|-----------|-----------------------------------|------|

| F.2       | Memory Segments                   | .207 |

| F.3       | Function Codes and Address Spaces | .208 |

| F.4       | Address Space Numbers             | .208 |

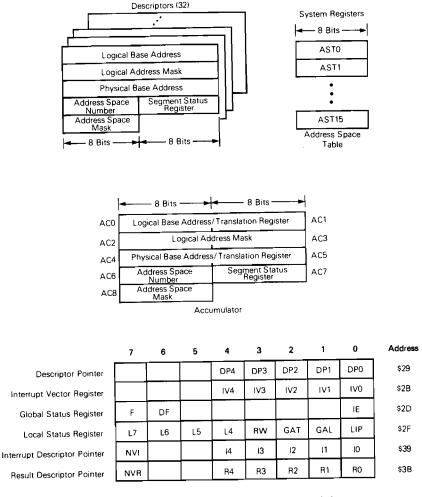

| F.5       | Descriptors                       | .209 |

| F.6       | MMU Register Description          | .210 |

| F.6.1     | Descriptors                       | .211 |

| F.6.1.1   | Logical Base Address              | .211 |

| F.6.1.2   | Logical Address Mask              | .211 |

| F.6.1.3   | Physical Base Address             | .212 |

| F.6.1.4   | Address Space Number              | .212 |

| F.6.1.5   | Address Space Mask                | .212 |

| F.6.1.6   | Segment Status Register           | .212 |

| F.6.2     | System Registers                  | .214 |

| F.6.2.1   | Address Space Table               | 214  |

| F.6.2.2   | Accumulator                       | .215 |

| F.6.2.3   | Global Status Register            | .215 |

| F.6.2.4   | Local Status Register             | .216 |

| F.6.2.5   | Descriptor Pointer                | 216  |

| F.6.2.6   | Result Descriptor Pointer         | 216  |

| F.6.2.7   | Interrupt Descriptor Pointer      | 218  |

| F.6.2.8   | Interrupt Vector Register         |      |

| F.7       | MMU Operations                    | 218  |

| F.7.1     | Operations Address Map            | 219  |

| F.7.2     | Local Operations                  | 221  |

| F.7.2.1   | Interrupt Acknowledge             | 221  |

| F.7.2.2   | Read System Register              | 221  |

| F.7.2.3   | Transfer Descriptor               | 221  |

| F.7.2.4   | Write Segment Status Register     |      |

| F.7.3     | Global Operations                 | 221  |

| F.7.3.1   | Write System Register             | 222  |

| F.7.3.2   | Load Descriptor Operation         | 222  |

| F.7.3.3   | Direct Translations               | 223  |

| F.8       | MMU Functional Description        |      |

| F.8.1     | MMU Functional States             |      |

| F.8.1.1   | Reset State                       |      |

| F.8.1.2   | Idle States                       | 226  |

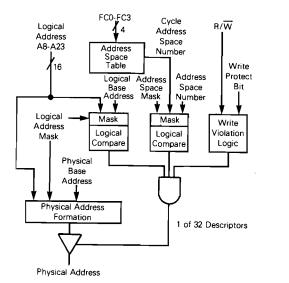

| F.8.2     | Normal Address Translation        |      |

| F.8.2.1   | Matching                          | 227  |

| F.8.2.2   | Translation                       | 227  |

| F.8.2.2.1 | Write Violation                   |      |

| F.8.2.2.2 | No Address Match                  |      |

| F.8.2.3   | External Translation              |      |

| F.8.2.3.1 | External Write Violation          |      |

| F.8.2.3.2 | Undefined Segment Excess          | 228  |

# Paragraph No.TitlePage No.F.9Software Considerations.228F.9.1Segment Mapping Example228F.9.2Segmentation230F.9.3Paging230F.9.4Initialization Software230F.9.5Context Switching231

### LIST OF ILLUSTRATIONS

| F | 806 | ) N | ю. |

|---|-----|-----|----|

|   |     |     |    |

| Figure No. | Title Page No.                                                       |    |

|------------|----------------------------------------------------------------------|----|

| -          | •                                                                    |    |

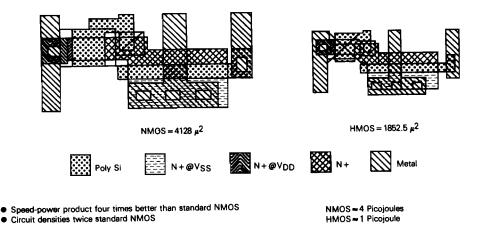

| 1-1        | HMOS Circuit Design Techniques1                                      |    |

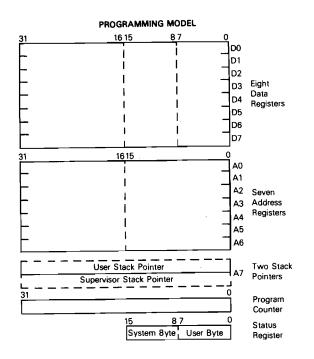

| 1-2        | Programming Model                                                    |    |

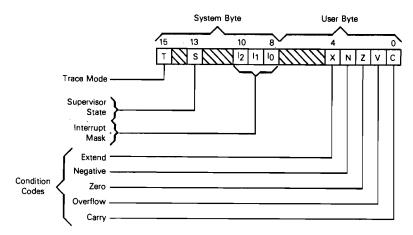

| 1-3        | Status Register                                                      |    |

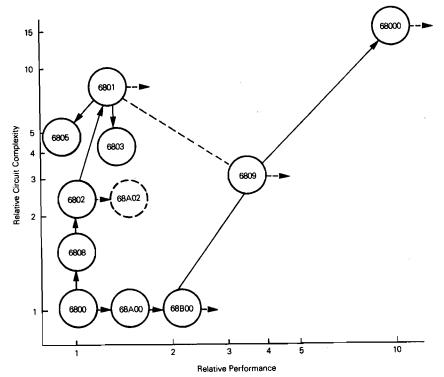

| 1-4        | Motorola's Microprocessor Evolution9                                 | ļ  |

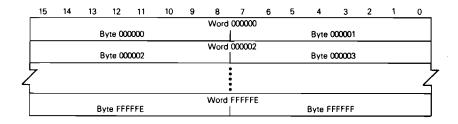

| 2-1        | Word Organization in Memory14                                        |    |

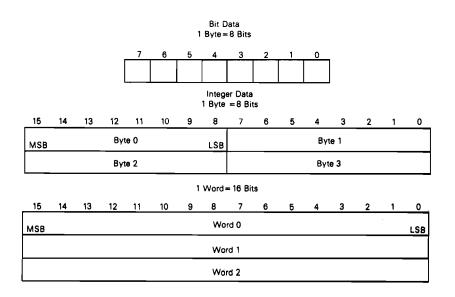

| 2-2        | Data Organization in Memory14                                        |    |

| 2-3        | Instruction Format                                                   | )  |

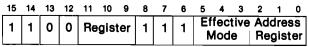

| 2-4        | Single-Effective-Address-Instruction Operation Word General Format17 |    |

| 4-1        | Input and Output Signals                                             | ļ  |

| 4-2        | Word Read Cycle Flow Chart                                           | J  |

| 4-3        | Byte Read Cycle Flow Chart                                           |    |

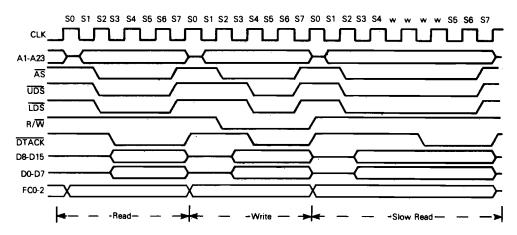

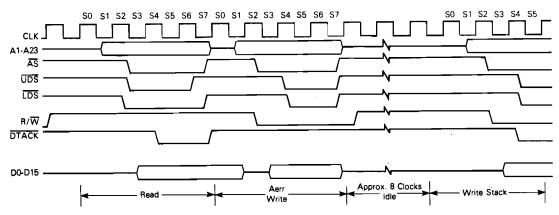

| 4-4        | Read and Write Cycle Timing Diagram40                                |    |

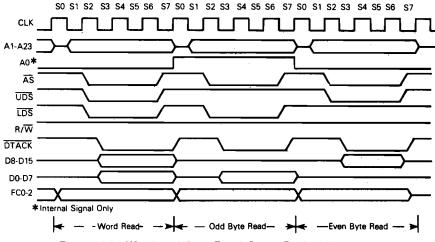

| 4-5        | Word and Byte Read Cycle Timing Diagram40                            | )  |

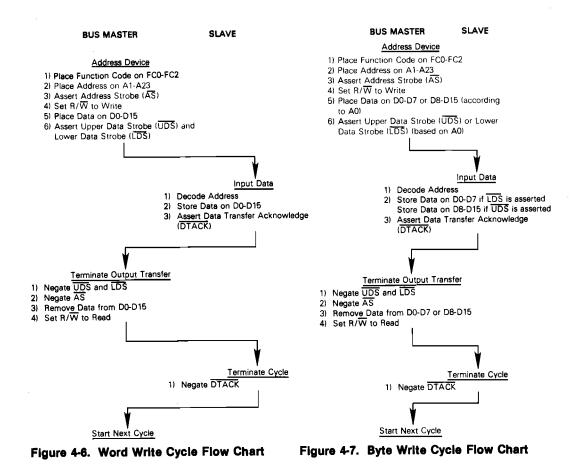

| 4-6        | Word Write Cycle Flow Chart41                                        |    |

| 4-7        | Byte Write Cycle Flow Chart41                                        |    |

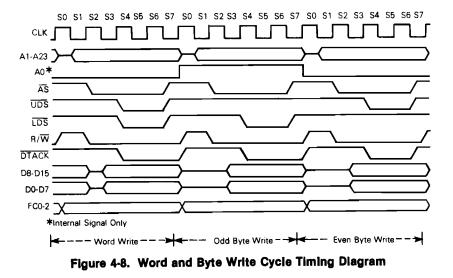

| 4-8        | Word and Byte Write Cycle Timing Diagram41                           |    |

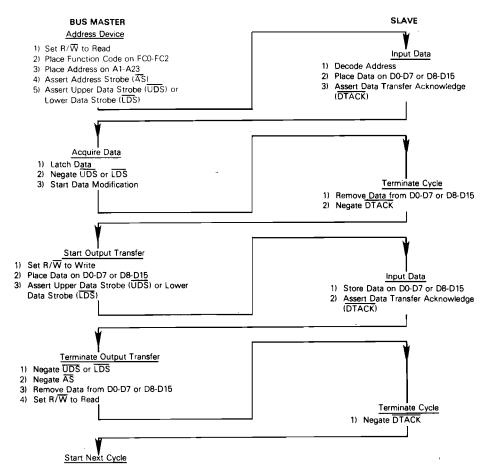

| 4-9        | Read-Modify-Write Cycle Flow Chart43                                 |    |

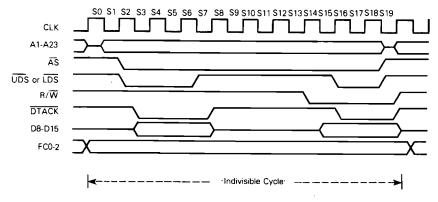

| 4-10       | Read-Modify-Write Cycle Timing Diagram44                             |    |

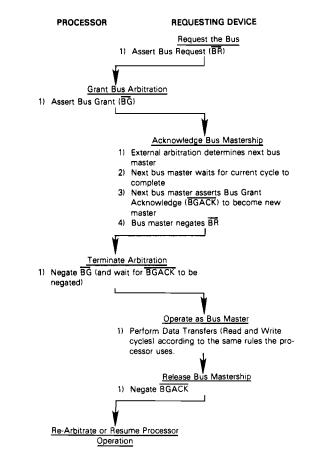

| 4-11       | Bus Arbitration Cycle Flow Chart46                                   |    |

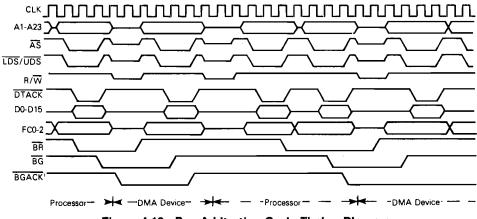

| 4-12       | Bus Arbitration Cycle Timing Diagram46                               |    |

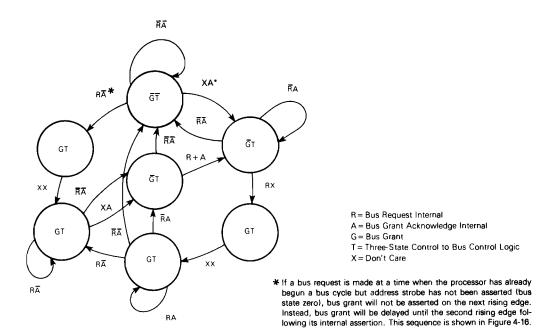

| 4-13       | Bus Arbitration Control State Diagram48                              |    |

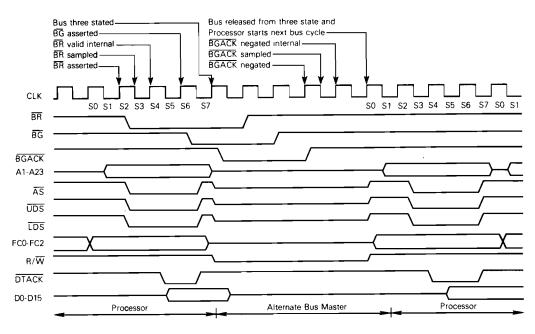

| 4-14       | Bus Arbitration Timing During Active Bus Cycle                       |    |

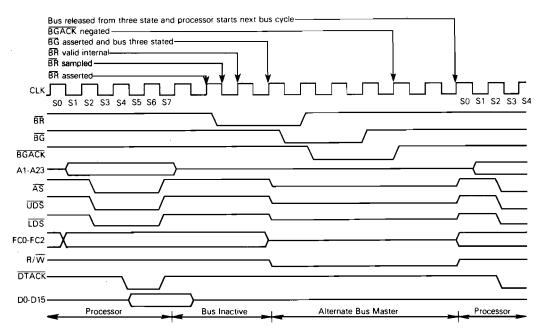

| 4-15       | Bus Arbitration Timing During Inactive Bus Cycle                     |    |

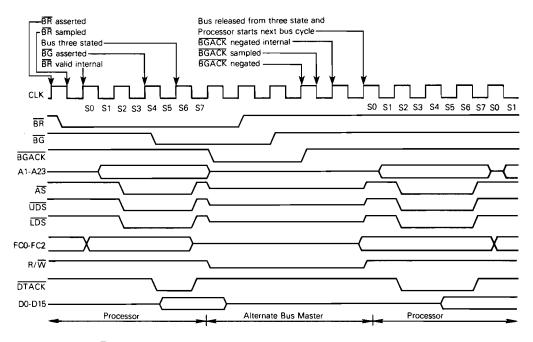

| 4-16       | Bus Arbitration Timing During Special Case                           |    |

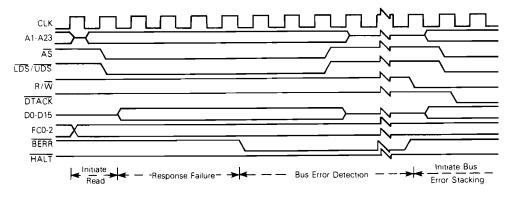

| 4-17       | Bus Error Timing Information                                         |    |

| 4-18       | Re-Run Bus Cycle Timing Diagram51                                    |    |

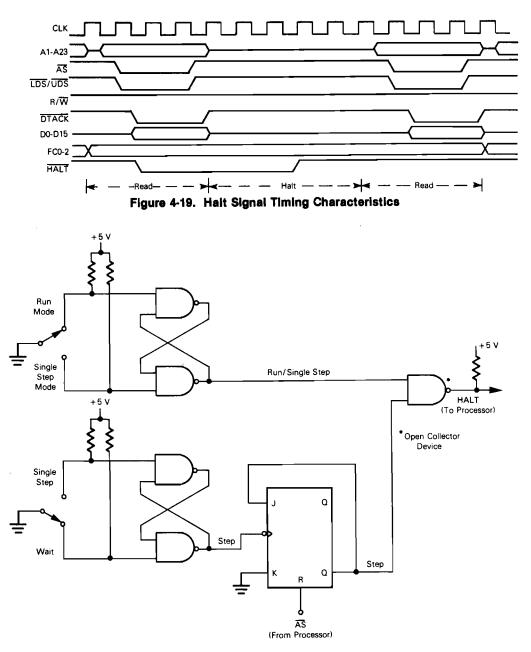

| 4-19       | Halt Signal Timing Characteristics                                   |    |

| 4-20       | Simplified Single-Step Circuit                                       |    |

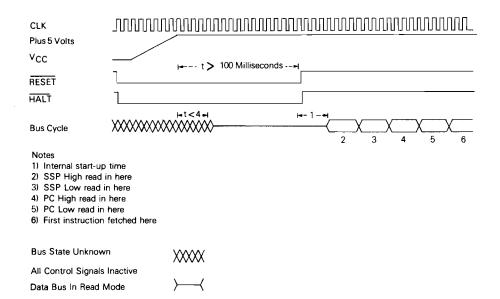

| 4-21       | Reset Operation Timing Diagram55                                     | I  |

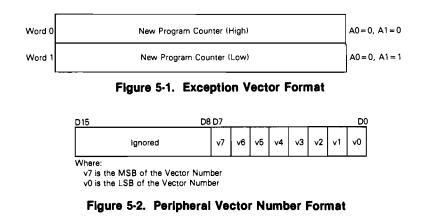

| 5-1        | Exception Vector Format60                                            | ł  |

| 5-2        | Peripheral Vector Number Format60                                    |    |

| 5-3        | Address Translated from 8-Bit Vector Number60                        |    |

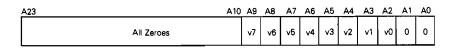

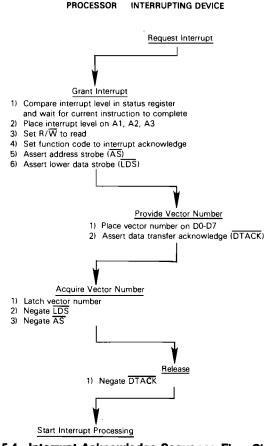

| 5-4        | Interrupt Acknowledge Sequence Flow Chart64                          |    |

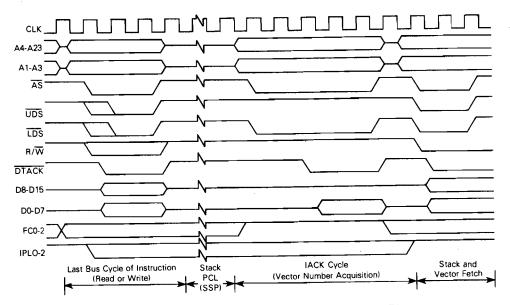

| 5-5        | Interrupt Acknowledge Sequence Timing Diagram65                      |    |

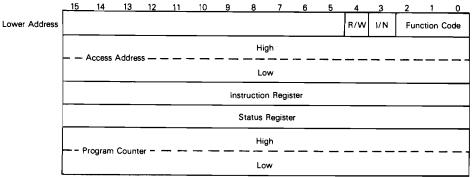

| 5-6        | Supervisor Stack Order for Bus or Address Error Exception            |    |

| 5-7        | Address Error Timing Diagram69                                       |    |

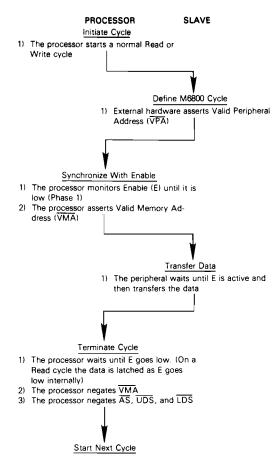

| 6-1        | M6800 Interfacing Flow Chart72                                       | ,  |

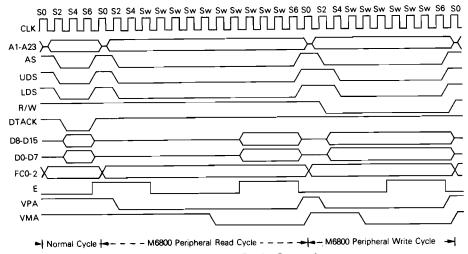

| 6-2        | M6800 Cycle Operation73                                              |    |

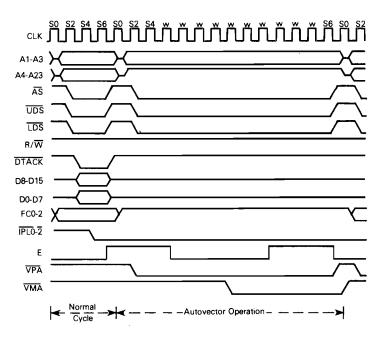

| 6-3        | Autovector Operation Timing Diagram74                                |    |

| B-1        | Instruction Format Description79                                     | I  |

| E-1        | Instruction Prefetch Example, Memory Contents                        | j  |

| E-2        | Instruction Prefetch Example                                         | j. |

| E-3        | MOVEM Example, Memory Contents                                       | į  |

|            |                                                                      |    |

### LIST OF ILLUSTRATIONS (Continued)

|            | (                                                               |          |

|------------|-----------------------------------------------------------------|----------|

| Figure No. | Titie                                                           | Page No. |

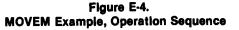

| E-4        | MOVEM Example, Operation Sequence                               | 206      |

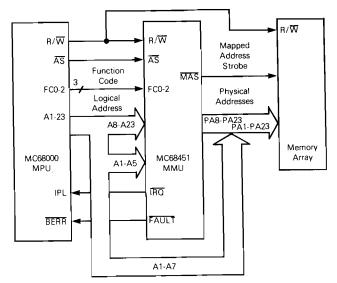

| F-1        | Memory Management Mechanism Block Diagram                       |          |

| F-2        | MC68451 MMU Functional Block Diagram                            |          |

| F-3        | MC68451 MMU Programmers Model                                   |          |

| F-4        | Schematic Representation for Address Matching                   |          |

| F-5        | Schematic Representation for Physical Address Generation        |          |

| F-6        | Address Space Table Organization                                |          |

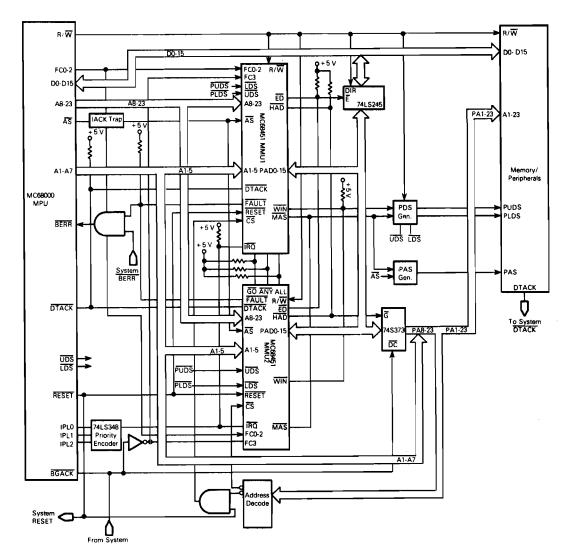

| F-7        | Sample Circuit Diagram a Two-MMU Memory Management<br>Mechanism |          |

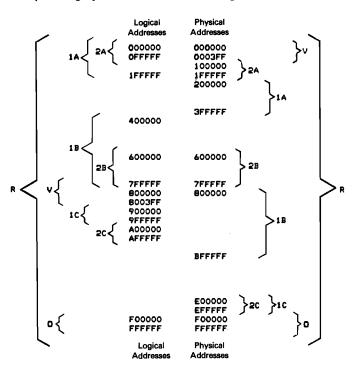

| F-8        | Address Map Example                                             |          |

### **LIST OF TABLES**

| Title         Page No.           1-1         Data Addressing Modes         4           1-2         Instruction Set         6           1-3         Variations of Instruction Types         7           2-1         Effective Address Encoding Summary         23           2-2         Implicit Instruction Reference Summary         23           3-1         Data Movement Operations         29           3-2         Integer Arithmetic Operations         29           3-3         Logical Operations         29           3-4         Shift and Rotate Operations         30           3-5         Bit Manipulation Operations         30           3-6         Binary Coded Decimal Operations         30           3-7         Program Control Operations         31           3-8         System Control Operations         31           3-4         Data Strobe Control of Data Bus         34           4-2         Function Code Outputs         36           4-3         Signal Summary         37           4-4         DTACK, BERR, HALT Assertion Results         54           5-1         Reference Classification         59           5-2         Exception Grouping and Priority         32     <                                                                    |             |                                                     |             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------|-------------|

| 1-2       Instruction Set       6         1-3       Variations of Instruction Types       7         2-1       Effective Address Encoding Summary       23         2-2       Implicit Instruction Reference Summary       23         3-1       Data Movement Operations       28         3-2       Integer Arithmetic Operations       29         3-3       Logical Operations       29         3-4       Shift and Rotate Operations       30         3-5       Bit Manipulation Operations       30         3-6       Binary Coded Decimal Operations       30         3-7       Program Control Operations       31         3-8       System Control Operations       31         3-4       Data Strobe Control of Data Bus       34         4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       Function Code Outputs       36         5-3       BERR and HALT Negation Results       54         5-4       BERR and HALT Negation Results       54         5-5       Exception Grouping and Priority       62         A-1       Conditional Tests       77         A-2       Conditional Tests       78 <th>Table No.</th> <th>Title</th> <th>Page No.</th>                                                                           | Table No.   | Title                                               | Page No.    |

| 1-2       Instruction Set       6         1-3       Variations of Instruction Types       7         2-1       Effective Address Encoding Summary       23         2-2       Implicit Instruction Reference Summary       23         3-1       Data Movement Operations       28         3-2       Integer Arithmetic Operations       29         3-3       Logical Operations       29         3-4       Shift and Rotate Operations       30         3-5       Bit Manipulation Operations       30         3-6       Binary Coded Decimal Operations       30         3-7       Program Control Operations       31         3-8       System Control Operations       31         3-4       Data Strobe Control of Data Bus       34         4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       Function Code Outputs       36         5-3       BERR and HALT Negation Results       54         5-4       BERR and HALT Negation Results       54         5-5       Exception Grouping and Priority       62         A-1       Conditional Tests       77         A-2       Conditional Tests       78 <td>1.1</td> <td>Data Addressing Modes</td> <td>4</td>                                                                        | 1.1         | Data Addressing Modes                               | 4           |

| 1-3       Variations of Instruction Types       7         2-1       Effective Address Encoding Summary       23         2-2       Implicit Instruction Reference Summary       23         3-1       Data Movement Operations       28         3-2       Integer Arithmetic Operations       29         3-3       Logical Operations       29         3-4       Shift and Rotate Operations       30         3-5       Bit Manipulation Operations       30         3-6       Binary Coded Decimal Operations       30         3-7       Program Control Operations       31         3-8       System Control of Data Bus       34         4-1       Data Strobe Control of Data Bus       34         4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       DTACK, BERR, HALT Assertion Results       54         5-1       Reference Classification       59         5-2       Exception Vector Assignment       61         5-3       Exception Grouping and Priority       62         A-1       Conditional Tests       78         B-1       Effective Address Encoding Summary       183         C-2       Effective A                                                                                                                   | ••          | Instruction Set                                     | 6           |

| 2-2       Implicit Instruction Reference Summary       23         3-1       Data Movement Operations       28         3-2       Integer Arithmetic Operations       29         3-3       Logical Operations       29         3-4       Shift and Rotate Operations       30         3-5       Bit Manipulation Operations       30         3-6       Binary Coded Decimal Operations       30         3-7       Program Control Operations       31         3-8       System Control Operations       31         3-1       Data Strobe Control of Data Bus       34         4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       DTACK, BERR, HALT Assertion Results       54         4-5       BERR and HALT Negation Results       54         5-1       Reference Classification       59         5-2       Exception Vector Assignment       661         5-3       Exception Grouping and Priority       62         A-1       Conditional Tests       78         B-1       Effective Address Operand Calculation Timing       197         C-2       Effective Address Operand Calculation Timing       197         C-2                                                                                                                | • -         |                                                     |             |

| 2-2       Implicit Instruction Reference Summary       23         3-1       Data Movement Operations       28         3-2       Integer Arithmetic Operations       29         3-3       Logical Operations       29         3-4       Shift and Rotate Operations       30         3-5       Bit Manipulation Operations       30         3-6       Binary Coded Decimal Operations       30         3-7       Program Control Operations       31         3-8       System Control Operations       31         3-1       Data Strobe Control of Data Bus       34         4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       DTACK, BERR, HALT Assertion Results       54         4-5       BERR and HALT Negation Results       54         5-1       Reference Classification       59         5-2       Exception Vector Assignment       661         5-3       Exception Grouping and Priority       62         A-1       Conditional Tests       78         B-1       Effective Address Operand Calculation Timing       197         C-2       Effective Address Operand Calculation Timing       197         C-2                                                                                                                | 2-1         | Effective Address Encoding Summary                  | 23          |

| 3-2       Integer Arithmetic Operations       29         3-3       Logical Operations       29         3-4       Shift and Rotate Operations       30         3-5       Bit Manipulation Operations       30         3-6       Binary Coded Decimal Operations       30         3-7       Program Control Operations       31         3-8       System Control Operations       31         3-4       Data Strobe Control of Data Bus       34         4-2       Function Code Outputs       36         4-3       Signal Summary.       37         4-4       DTACK, BERR, HALT Assertion Results       54         5-1       Reference Classification       59         5-2       Exception Vector Assignment       61         5-3       Exception Grouping and Priority       62         A-1       Condition Code Computations       77         A-2       Conditional Tests       78         B-1       Effective Address Encoding Summary       183         C-2       Effective Address Operand Calculation Timing       197         D-3       Move Long Instruction Clock Periods       198         D-4       Effective Address Operand Calculation Timing       197         D-2                                                                                                          | 2-2         | Implicit Instruction Reference Summary              | 23          |

| 3-3       Logical Operations       29         3-4       Shift and Rotate Operations       30         3-5       Bit Manipulation Operations       30         3-6       Binary Coded Decimal Operations       30         3-7       Program Control Operations       31         3-8       System Control Operations       31         3-7       Program Control Operations       31         3-8       System Control of Data Bus       34         4-1       Data Strobe Control of Data Bus       34         4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       DTACK, BERR, HALT Assertion Results       54         5-5       BERR and HALT Negation Results       54         5-1       Reference Classification       59         5-2       Exception Grouping and Priority       62         A-1       Conditional Tests       77         A-2       Conditional Tests       78         B-1       Effective Address Operand Calculation Timing       197         C-2       Effective Address Operand Calculation Timing       197         D-2       Move Dung Instruction Clock Periods       198         D-3       Move                                                                                                                   | •••         | Data Movement Operations                            |             |

| 34       Shift and Rotate Operations       30         35       Bit Manipulation Operations       30         36       Binary Coded Decimal Operations       30         37       Program Control Operations       31         38       System Control Operations       31         38       System Control Operations       31         34       Program Control Operations       31         34       Data Strobe Control of Data Bus       34         42       Function Code Outputs       36         43       Signal Summary       37         44       DTACK, BERR, HALT Assertion Results       54         45       BERR and HALT Negation Results       54         51       Reference Classification       59         52       Exception Vector Assignment       61         53       Exception Grouping and Priority       62         A-1       Conditional Tests       78         B-1       Effective Addressing Mode Categories       79         C-1       Operation Code Map       183         C-2       Effective Address Operand Calculation Timing       197         D-3       Move Long Instruction Clock Periods       198         D-4       Standard Instructi                                                                                                                   |             | Integer Arithmetic Operations                       |             |

| 3-5       Bit Manipulation Operations       30         3-6       Binary Coded Decimal Operations       30         3-7       Program Control Operations       31         3-8       System Control Operations       31         3-1       Data Strobe Control of Data Bus       34         4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       DTACK, BERR, HALT Assertion Results       54         4-5       BERR and HALT Negation Results       54         5-1       Reference Classification       59         5-2       Exception Vector Assignment       61         5-3       Exception Grouping and Priority       62         A-1       Conditional Tests       78         B-1       Effective Addressing Mode Categories       79         C-1       Operation Code Map       183         C-2       Effective Address Encoding Summary       183         C-3       Conditional Tests       184         D-1       Effective Address Operand Calculation Timing       197         D-2       Move Byte and Word Instruction Clock Periods       198         D-3       Move Long Instruction Clock Periods       198         D-                                                                                                          |             | Logical Operations                                  | 29          |

| 3-6       Binary Coded Decimal Operations       30         3-7       Program Control Operations       31         3-8       System Control Operations       31         3-4       Data Strobe Control of Data Bus       34         4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       DTACK, BERR, HALT Assertion Results       54         4-5       BERR and HALT Negation Results       54         4-5       BERR and HALT Negation Results       54         5-1       Reference Classification       59         5-2       Exception Vector Assignment       61         5-3       Exception Grouping and Priority       62         A-1       Condition Code Computations       77         A-2       Conditional Tests       78         B-1       Effective Addressing Mode Categories       79         C-1       Operation Code Map       183         C-2       Effective Address Encoding Summary       183         C-3       Conditional Tests       184         D-1       Effective Address Operand Calculation Timing       197         D-2       Move Byte and Word Instruction Clock Periods       198         D-3                                                                                                               | • •         | Shift and Hotate Operations                         |             |

| 3-7       Program Control Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | Bit Manipulation Operations                         | 30          |

| 3-8       System Control Operations       31         4-1       Data Strobe Control of Data Bus       34         4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       DTACK, BERR, HALT Assertion Results       54         4-5       BERR and HALT Negation Results       54         5-1       Reference Classification       59         5-2       Exception Vector Assignment       61         5-3       Exception Grouping and Priority       62         A-1       Condition Code Computations       77         A-2       Conditional Tests       78         B-1       Effective Addressing Mode Categories       79         C-1       Operation Code Map       183         C-2       Effective Address Operand Calculation Timing       197         D-2       Move Byte and Word Instruction Clock Periods       198         D-3       Move Long Instruction Clock Periods       201         D-4       Standard Instruction Clock Periods       201         D-5       Immediate Instruction Clock Periods       201         D-6       Single Operand Instruction Clock Periods       202         D-7       Shift/Rotate Instruction Clock Periods <td< td=""><td></td><td>Binary Coded Decimal Operations</td><td></td></td<>          |             | Binary Coded Decimal Operations                     |             |

| 4-1       Data Strobe Control of Data Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | Program Control Operations                          | 21          |

| 4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       DTACK, BERR, HALT Assertion Results       54         4-5       BERR and HALT Negation Results       54         5-1       Reference Classification       59         5-2       Exception Vector Assignment       61         5-3       Exception Grouping and Priority       62         A-1       Condition Code Computations       77         A-2       Conditional Tests       78         B-1       Effective Addressing Mode Categories       79         C-1       Operation Code Map       183         C-2       Effective Address Encoding Summary       183         C-3       Conditional Tests       184         D-1       Effective Address Operand Calculation Timing       197         D-2       Move Byte and Word Instruction Clock Periods       198         D-3       Move Long Instruction Clock Periods       198         D-4       Standard Instruction Clock Periods       201         D-7       Shift/Rotate Instruction Clock Periods       201         D-7       Shift/Rotate Instruction Clock Periods       202         D-9       Conditional Instruction Clock Periods       20                                                                                | 3-8         | System Control Operations                           |             |

| 4-2       Function Code Outputs       36         4-3       Signal Summary       37         4-4       DTACK, BERR, HALT Assertion Results       54         4-5       BERR and HALT Negation Results       54         5-1       Reference Classification       59         5-2       Exception Vector Assignment       61         5-3       Exception Grouping and Priority       62         A-1       Condition Code Computations       77         A-2       Conditional Tests       78         B-1       Effective Addressing Mode Categories       79         C-1       Operation Code Map       183         C-2       Effective Address Encoding Summary       183         C-3       Conditional Tests       184         D-1       Effective Address Operand Calculation Timing       197         D-2       Move Byte and Word Instruction Clock Periods       198         D-3       Move Long Instruction Clock Periods       198         D-4       Standard Instruction Clock Periods       201         D-7       Shift/Rotate Instruction Clock Periods       201         D-7       Shift/Rotate Instruction Clock Periods       202         D-9       Conditional Instruction Clock Periods       20                                                                                | 4-1         | Data Strobe Control of Data Bus                     | 34          |

| 4-3       Signal Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                                                     |             |

| 4.4       DTACK, BERR, HALT Assertion Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | · —         | Signal Summary                                      | 37          |

| 4-5       BERR and HALT Negation Results       .54         5-1       Reference Classification       .59         5-2       Exception Vector Assignment       .61         5-3       Exception Grouping and Priority       .62         A-1       Condition Code Computations       .77         A-2       Conditional Tests       .78         B-1       Effective Addressing Mode Categories       .79         C-1       Operation Code Map       .183         C-2       Effective Address Encoding Summary       .183         C-3       Conditional Tests       .184         D-1       Effective Address Operand Calculation Timing       .197         D-2       Move Byte and Word Instruction Clock Periods       .198         D-3       Move Long Instruction Clock Periods       .198         D-4       Standard Instruction Clock Periods       .200         D-5       Immediate Instruction Clock Periods       .201         D-7       Shift/Rotate Instruction Clock Periods       .202         D-9       Conditional Instruction Clock Periods       .202         D-9       Conditional Instruction Clock Periods       .202         D-9       Conditional Instruction Clock Periods       .202         D-1                                                                         |             | DTACK, BERR, HALT Assertion Results                 | 54          |

| 5-2       Exception Vector Assignment       61         5-3       Exception Grouping and Priority       62         A-1       Condition Code Computations       77         A-2       Conditional Tests       78         B-1       Effective Addressing Mode Categories       79         C-1       Operation Code Map       183         C-2       Effective Address Encoding Summary       183         C-3       Conditional Tests       184         D-1       Effective Address Operand Calculation Timing       197         D-2       Move Byte and Word Instruction Clock Periods       198         D-3       Move Long Instruction Clock Periods       199         D-4       Standard Instruction Clock Periods       199         D-5       Immediate Instruction Clock Periods       200         D-6       Single Operand Instruction Clock Periods       201         D-7       Shift/Rotate Instruction Clock Periods       202         D-9       Conditional Instruction Clock Periods       202         D-10 <td>4-5</td> <td>BERR and HALT Negation Results</td> <td>54</td> | 4-5         | BERR and HALT Negation Results                      | 54          |

| 5-2       Exception Vector Assignment       61         5-3       Exception Grouping and Priority       62         A-1       Condition Code Computations       77         A-2       Conditional Tests       78         B-1       Effective Addressing Mode Categories       79         C-1       Operation Code Map       183         C-2       Effective Address Encoding Summary       183         C-3       Conditional Tests       184         D-1       Effective Address Operand Calculation Timing       197         D-2       Move Byte and Word Instruction Clock Periods       198         D-3       Move Long Instruction Clock Periods       199         D-4       Standard Instruction Clock Periods       199         D-5       Immediate Instruction Clock Periods       200         D-6       Single Operand Instruction Clock Periods       201         D-7       Shift/Rotate Instruction Clock Periods       202         D-9       Conditional Instruction Clock Periods       202         D-10 <td>5-1</td> <td>Reference Classification</td> <td>59</td>       | 5-1         | Reference Classification                            | 59          |

| 5-3       Exception Grouping and Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | Exception Vector Assignment                         | 61          |

| A-2       Conditional Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             | Exception Grouping and Priority                     | 62          |

| A-2       Conditional Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A-1         | Condition Code Computations                         | 77          |

| C-1Operation Code Map183C-2Effective Address Encoding Summary183C-3Conditional Tests184D-1Effective Address Operand Calculation Timing197D-2Move Byte and Word Instruction Clock Periods198D-3Move Long Instruction Clock Periods198D-4Standard Instruction Clock Periods199D-5Immediate Instruction Clock Periods200D-6Single Operand Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods203D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • • •       | Conditional Tests                                   | 78          |

| C-1Operation Code Map183C-2Effective Address Encoding Summary183C-3Conditional Tests184D-1Effective Address Operand Calculation Timing197D-2Move Byte and Word Instruction Clock Periods198D-3Move Long Instruction Clock Periods198D-4Standard Instruction Clock Periods199D-5Immediate Instruction Clock Periods200D-6Single Operand Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods203D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B-1         | Effective Addressing Mode Categories                | 79          |

| C-2Effective Address Encoding Summary183C-3Conditional Tests184D-1Effective Address Operand Calculation Timing197D-2Move Byte and Word Instruction Clock Periods198D-3Move Long Instruction Clock Periods198D-4Standard Instruction Clock Periods199D-5Immediate Instruction Clock Periods200D-6Single Operand Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods201D-8Bit Manipulation Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods203D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                                     |             |

| C-3Conditional Tests184D-1Effective Address Operand Calculation Timing197D-2Move Byte and Word Instruction Clock Periods198D-3Move Long Instruction Clock Periods198D-4Standard Instruction Clock Periods199D-5Immediate Instruction Clock Periods200D-6Single Operand Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods204D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | Operation Code Map                                  | 183         |

| D-1Effective Address Operand Calculation Timing197D-2Move Byte and Word Instruction Clock Periods198D-3Move Long Instruction Clock Periods198D-4Standard Instruction Clock Periods199D-5Immediate Instruction Clock Periods200D-6Single Operand Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods204D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             | Effective Address Encoding Summary                  | 183         |

| D-2Move Byte and Word Instruction Clock Periods198D-3Move Long Instruction Clock Periods198D-4Standard Instruction Clock Periods199D-5Immediate Instruction Clock Periods200D-6Single Operand Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods201D-8Bit Manipulation Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods204D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C- <u>3</u> | Conditional Tests                                   | 184         |

| D-2Move Byte and Word Instruction Clock Periods198D-3Move Long Instruction Clock Periods198D-4Standard Instruction Clock Periods199D-5Immediate Instruction Clock Periods200D-6Single Operand Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods201D-8Bit Manipulation Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods204D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D-1         | Effective Address Operand Calculation Timing        | 197         |

| D-3Move Long Instruction Clock Periods198D-4Standard Instruction Clock Periods199D-5Immediate Instruction Clock Periods200D-6Single Operand Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods201D-8Bit Manipulation Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods204D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             | Move Byte and Word Instruction Clock Periods        | 198         |

| D-4Standard Instruction Clock Periods199D-5Immediate Instruction Clock Periods200D-6Single Operand Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods201D-8Bit Manipulation Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods204D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D-3         | Move Long Instruction Clock Periods                 | 198         |

| D-5Immediate Instruction Clock Periods200D-6Single Operand Instruction Clock Periods201D-7Shift/Rotate Instruction Clock Periods201D-8Bit Manipulation Instruction Clock Periods202D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods204D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             | Standard Instruction Clock Periods                  | 1 <b>99</b> |

| D-7Shift/Rotate Instruction Clock Periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                                                     |             |

| D-7Shift/Rotate Instruction Clock Periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D-6         | Single Operand Instruction Clock Periods            | 201         |

| D-8Bit Manipulation Instruction Clock Periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D-7         | Shift/Rotate Instruction Clock Periods              | 201         |

| D-9Conditional Instruction Clock Periods202D-10JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods203D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods204D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             | Bit Manipulation Instruction Clock Periods          | 202         |

| D-11Multi-Precision Instruction Clock Periods203D-12Miscellaneous Instruction Clock Periods204D-13Move Peripheral Instruction Clock Periods204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D-9         | Conditional Instruction Clock Periods               | 202         |

| D-12 Miscellaneous instruction Clock Periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D-10        | JMP, JSR, LEA, PEA, MOVEM Instruction Clock Periods | 203         |

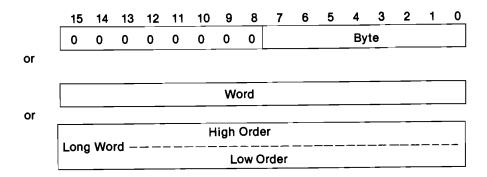

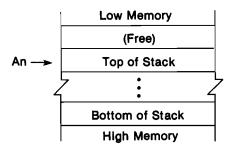

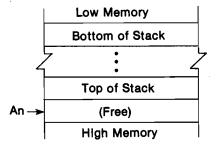

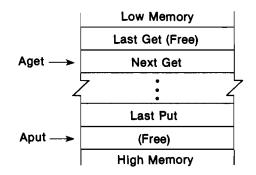

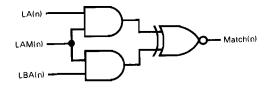

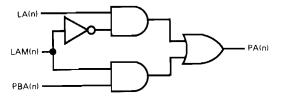

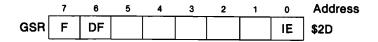

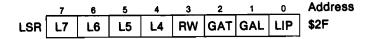

| D-13 Move Peripheral Instruction Clock Periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D-11        |                                                     |             |