# The Hewlett-Packard Digital Symposium & Exhibition

### HP Computer Museum www.hpmuseum.net

For research and education purposes only.

## 1.A Logic Analyzer Look at High Level Software

**Gail Hamilton** of Colorado Springs R&D Lab designed the 8085 and 6502 personality modules for Model 1611A Logic State Analyzer. Gail has a B.S.E.E./C.S. from U. of Colorado and is working on a Masters in Engineering Administration from Stanford.

|  |  | ~ |

|--|--|---|

|  |  |   |

### A Logic Analyzer Look at High Level Software

by Gail Hamilton

### **Abstract**

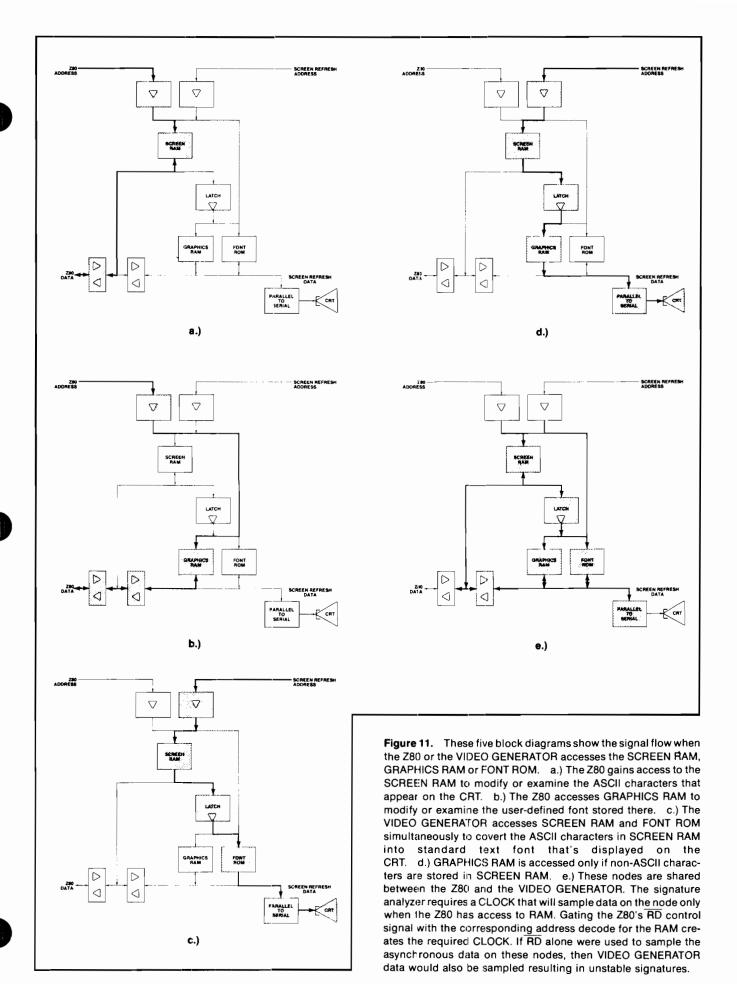

Computer system software is distinctly hierarchical in nature and measurement interest ranges from the instruction level to the system level. The first generation of logic state analyzers had the ability to look at the digital signal levels on the address and data buses. With the second generation, the capability to analyze software was extended through sequential triggering techniques and assembly language program tracing. Relevant information concerning the execution characteristics of software at these various levels can be determined using one of these second generation analyzers, the HP Model 1610A/B Logic State Analyzer. In addition, the utilization of a controller and HP-IB provides powerful postprocessing, as well as automated setup. This paper describes methods of measuring higher level software modules in a computer system with currently available instrumentation.

### Introduction

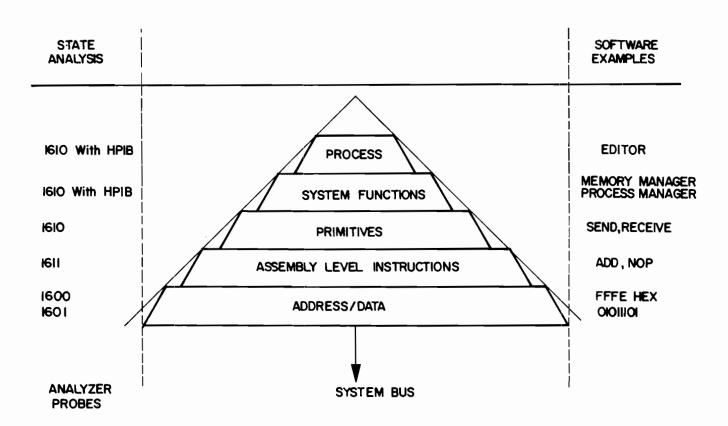

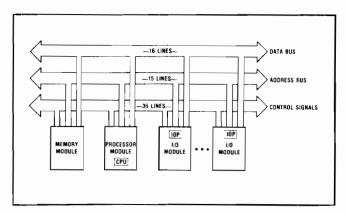

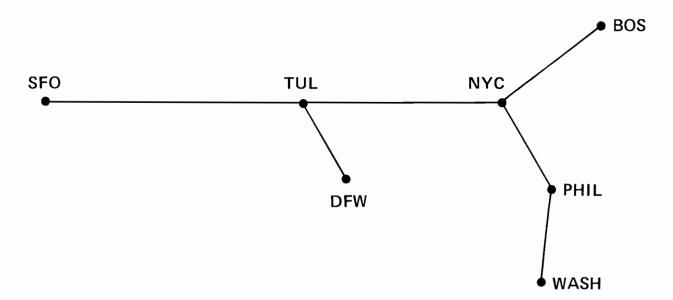

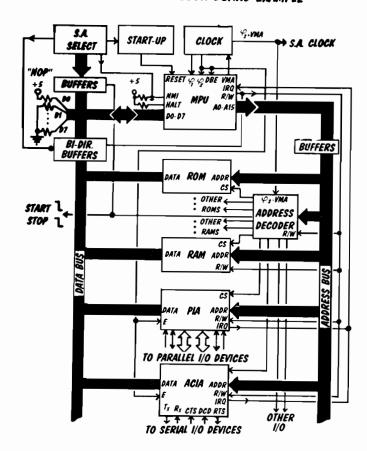

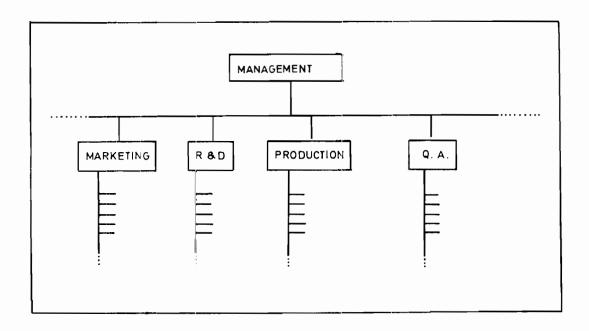

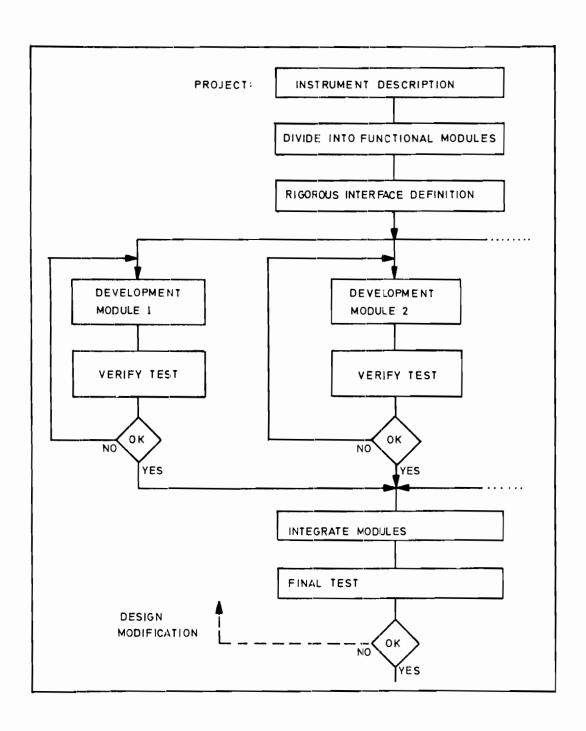

In a computer system there are usually many discrete levels of the software hierarchy that can be observed. Depending on the complexity of the system, there could be only one or many levels. A system that could only be programmed in machine code might possibly have one level, whereas an operating system such as UNIX would have five. In a system that has both an operating system environment and a user environment, the software hierarchy of interest would have the same basic elements with a slightly different emphasis. As an example, many operating systems have the hierarchy depicted in Figure 1. In the domain of the user, the lowest level of interest would probably be the instruction level, while the highest level might be the program or job level. The software hierarchy is built on the reduction of detail and the increase of abstraction.

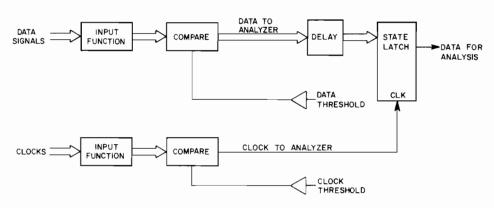

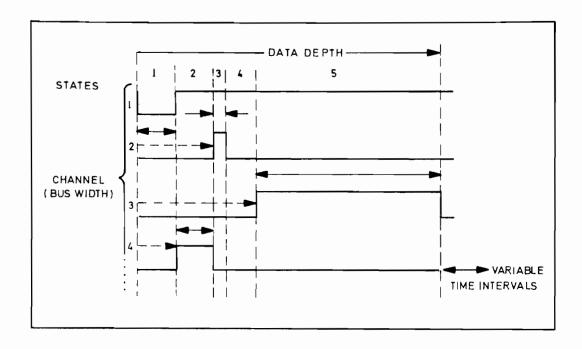

In order to look at these various levels of abstraction, logic state analyzers have evolved with a parallel hierarchy in the measurement domain. They too must reduce the data by removing the nonessential detail for the appropriate level of abstraction. The ability to analyze software depends on how well the instrument can look at two major areas. The first is qualitative and is more of the "what" is the software doing. For this type of information, a dynamic trace or sequential time list of events is appropriate. The second aspect is quantitative and answers the question "how": how much, how often, and how long.

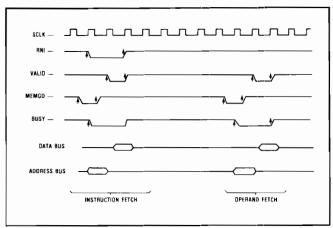

State analyzers provide passive probing at the hardware level, but they must provide sufficient data to decode the activity that occurs at the higher levels. The lowest level in the hierarchy are the addresses and data that can be derived directly from signal levels on the bus. For measurements in the software domain, a logic analyzer must translate the digital signal levels on the computer system's bus into three fields. The first field is the control signals to and from system devices, the second field is the addresses which refer to specific locations, and the third field is the data that is associated with the address.

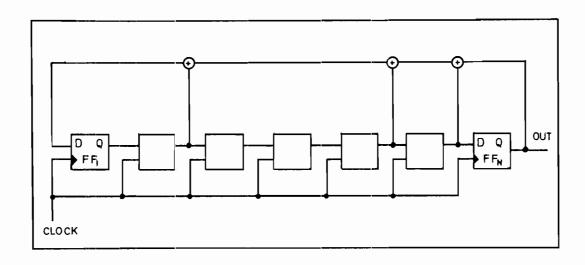

It was in 1973, when the first parallel logic state analyzer was introduced, that computer system designers had a measurement tool that gave them a view of their software that many had never seen before. The 1601 had the ability to capture a sequence of digital words, but didn't attempt to transform them in any way, but instead displayed the sequence of events as a table of 1's and 8's. The 1601 wasn't able to make any quantitative measurements.

With the introduction of the 1600, the capabilities were broadened by adding more bits of data, but the data display did not change significantly. It is interesting to note, that as early as the time of the 1600, there were attempts to recognize these higher levels. The MAP mode was added to the 1600 which gave a more comprehensive view of the system. In the MAP mode, each event on the system bus had a unique position on the CRT display. As a sequence of events was observed, the instrument traced lines from dot to dot. The MAP mode also gave an indication of the relative frequency or occurrence of any state - the more often a state is repeated, the brighter its dot. This was the first time that an attempt was made to provide a quantitative measurement. For example, the mode gave a highly visible indication of which memory addresses were used most often and which were not used at all. A user, then, could recognize a particular pattern of word sequences as being significant. Even the ability to transform the binary code into a more compact form, such as octal or hexadecimal, was not available until the introduction of the 1611A microprocessor analyzer at the end of 1976.

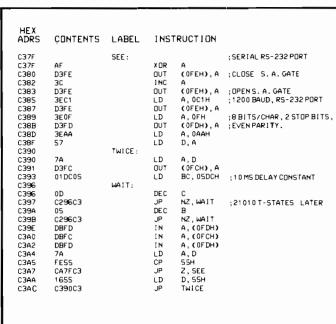

The 1611 was the first logic state analyzer to actually transform the sequence of digital words into something more meaningful than a tabular form of signal levels. The major contribution of this instrument was its ability to convert the machine language of a microprocessor into assembly language (refer to Figure 2). In other words, the 1611 focuses at the second level of the software hierarchy, namely, the instruction level. The instrument displays the microprocessor's instructions and makes it easier to interpret snapshots of executing program steps. Two quantitative measurements are provided in the 1611. The 1611 has the ability to measure the time between two events and count the number of states between two events. With the instrument in the continuous trace mode, it also provides statistical parameters, such as minimums and maximums.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ĥ   | DDRESS        | DATA | EXT  | ERNAL  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------|------|------|--------|

| TRIGGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ER  | 1000          | 02   | 999  | 900101 |

| DISABL<br>TRIGR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 106D<br>R=240 | 80   | XXX  | (X0010 |

| BORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | OPC | ODEZDĂT       |      | EXT  | RHAL   |

| 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NOP |               |      | 1000 | 0101   |

| 1001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | HOP |               |      | 1000 | 0101   |

| 1002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NOP |               | 9    | 3000 | 0101   |

| 1003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LOX | 9999          | , (  | 9000 | 1101   |

| 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00  | READ          |      | 3998 | 0001   |

| 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13  | READ          | 6    | 9000 | 0111   |

| 1006                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LDA | A 00.         | × €  | 9000 | 1101   |

| 0013                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00  | READ          | Ę    | 3000 | 0001   |

| 1008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TAB |               | Ę    | 9000 | 1101   |

| 1009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NOP |               | Ę    | 9000 | 0101   |

| 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NOP |               | €    | 9999 | 0101   |

| 1008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NOP |               | E    | 9999 | 0101   |

| 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSR | A             | 6    | 9000 | 1001   |

| 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MOP |               |      | 1000 | 0101   |

| 100E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NOP |               |      | 9000 | 0101   |

| 100F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | AND | A #78         | ę    | 9000 | 1001   |

| The second secon |     |               |      |      |        |

### FIGURE 2

It certainly was becoming apparent that hardware measurements of a complicated system had little to offer the software designer unless they could be related to events and states at a software level. Similar to all of the logic state analyzers, the 1610A/B collects data at the lowest level, but much of the upper level activity can be inferred using the techniques presented in the paper. Contributions of the 1610A/B, in terms of sequential triggering, selective trace, sequence restart, and the time/state count are crucial to making these higher level measurements. The time/state count of the 1610 is similar to what is available in the 1611, but these metrics are available for every event that is observed.

All of the current state analyzers, then, are optimized for making measurements at different levels in the hierarchy. By qualifying the incoming data, the unnecessary detail is suppressed for the appropriate level. Essentially, the micro-events are being probed in all these cases and the only difference lies in the data reduction and data display portions of the instrument.

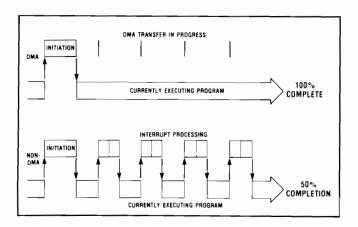

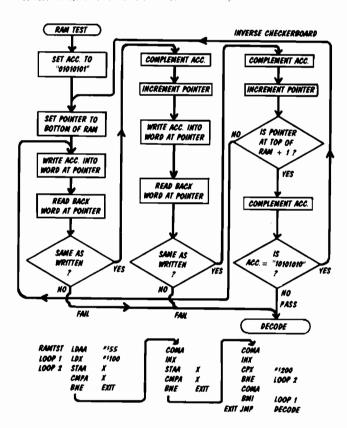

### What Measurements and Why

One of the first and most important questions that needs to be answered is what quantitative measurements need to be made, given that these software levels can be recognized. In analyzing software modules of a computer system, the two most significant quantities to be measured are time and frequency. Especially of interest is the time required to perform various functions or the time spent waiting to perform those functions. For example, you might want to know the instruction mix of a particular routine; how many ADD's, how many NOP's, etc. It is possible that a frequently used instruction could be implemented in microcode differently so as to provide faster execution. The knowledge of the execution time and frequency of usage of critical subroutines might be important as well. Another measurement that has value is a memory map, similar to what was being done qualitatively with the 1600 MAP mode. By partitioning regions of memory into buckets of address ranges, the total time or frequency that a software module spends executing in each partition can be accumulated.

The second question, and of equal importance, is why do these measurements need to be made and of what importance are they? If the utilization of these routines can be monitored, then a profile of system activity can be created. Bottlenecks occur when the relationship among the various resources becomes unbalanced. By knowing where these areas are that create inefficiencies, a programming team can concentrate resources on those regions where the greatest benefit will be gained from the smallest investment. It should be recognized that the implications of being able to maximize a programmer's utility are overwhelming. Current trends in programming methodology, such as the increasing use of structured programming and modular design, have amplified the need for tools that can detect and tune regions critical to performance. The question, "Where is the time spent?" can be answered by these measurement techniques. Even though these questions can be answered, a subjective judgement must still be made as to whether the amount of time spent on a given function is acceptable. Knowlege of where system overhead is located allows a designer to minimize those areas so that the time spent executing programs is maximized. By inferring the occurrence of significant logical events from the myriad of bus activities, higher level software can be observed and analyzed during actual execution.

### **How To Make the Measurements**

A few years ago HP responded to the need for a standard bus for their instruments with the Hewlett-Packard Interface Bus (HP-IB), which has since been adopted as an industry standard, IEEE-488. Many of the second generation analyzers are HP-IB controllable via a short mnemonic language. The ability of logic analyzers

to communicate over HP-IB allows programmable control of the analyzer, and combining this with an intelligent controller provides considerable flexibility. Many of the measurements that have been discussed previously, can be made using this capability.

There are many advantages to having an intelligent controller. The calculator can reduce data and provide statistical summaries with means, standard deviations, minimums, and maximums. It can also compile distribution data and calculate parameters such as correlation coefficients. The calculator can reduce the collected data before it is stored or displayed and also facilitate on-line modification of measurements.

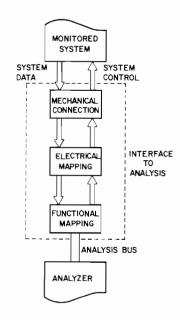

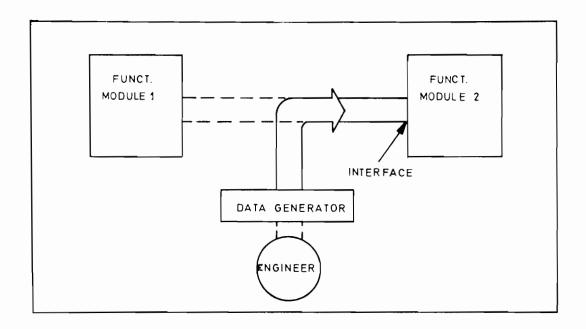

There are two ways that the measurement system can observe the system under test. One choice is to have the measurement system be completely transparent to the system that is being observed and the other is to have the measurement system play an interactive role. For example, the measurement system could have the ability to halt the processor to make some real-time calculations or make changes in the setup based on the current input.

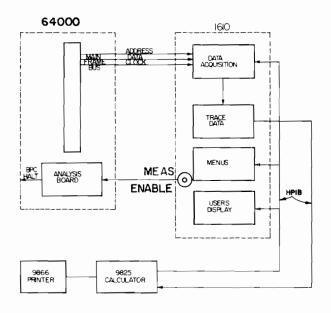

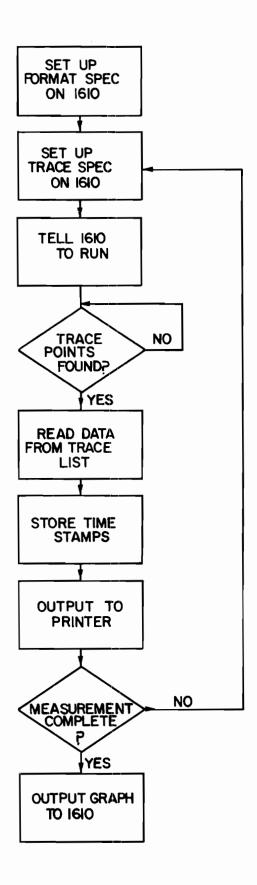

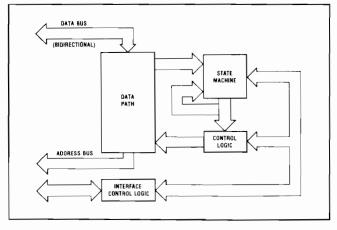

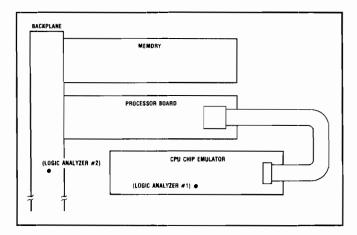

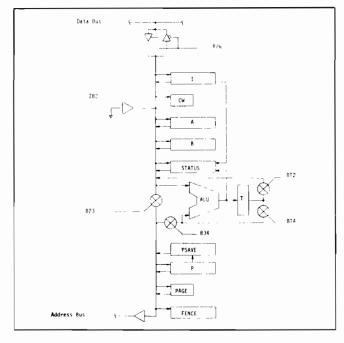

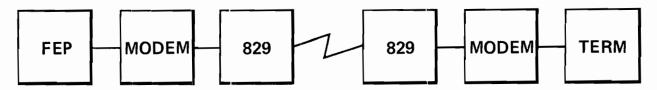

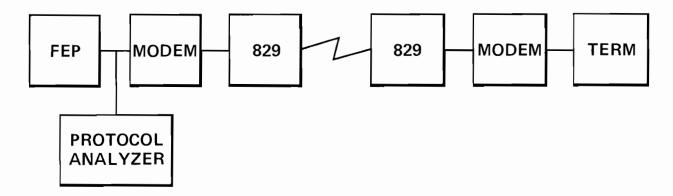

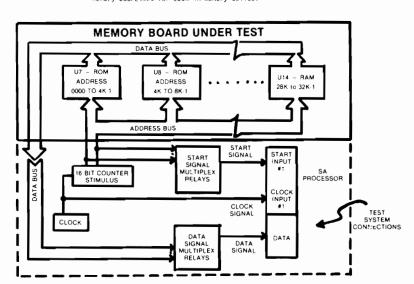

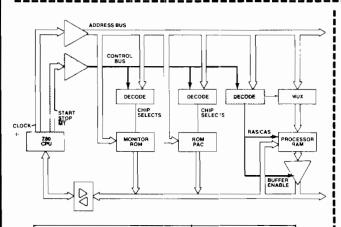

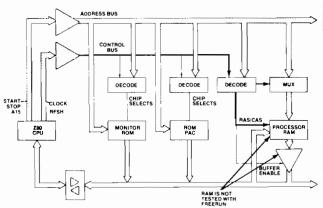

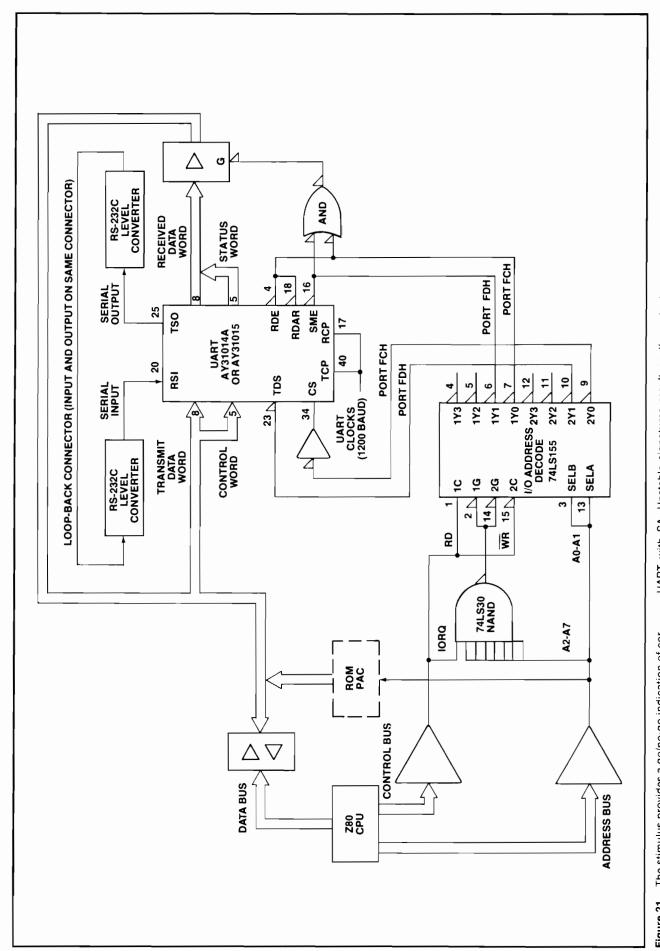

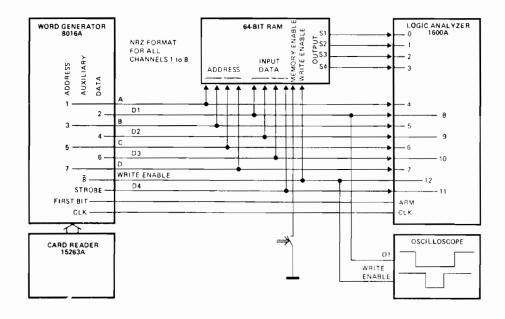

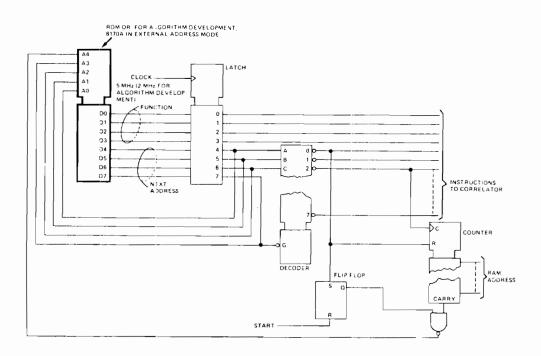

The block diagram in Figure 3 is one example of how the measurement system could be configured. In this case, the system under test is the HP 64000 Logic Development System. Two instruments, the 1610A/B and the HP Model 9825 Calculator are required; the 9866B printer can be used to interface to either the 1610AB or the 9825. The printer provides hard copy of Trace Lists as well as Format or Trace specifications if it is directly connected to the logic analyzer.

Software Measurement System

FIGURE 3

In general, the

sequence of events needed to make some of these measurements are as follows:

- The calculator sets up the 1610A/B Format and Trace Specifications.

- 2. The calculator tells the 1610A/B to Run (begin looking for the Trace points).

- 3. When the trace points are found, the 1610A/B generates a signal telling the processor in the system under test to halt and displays the results in a Trace List. If there were no interaction with the system under test, the 1610A/B would only display the Trace List.

- 4. The calculator then reads the data from the Trace List, stores the pertinent information, and depending on the particular measurement, may output to the 9866B printer.

- 5. The calculator then sets up 1610A/B to make another measurement. The new setup could be dependent on the data obtained in the previous trace.

- 6. After all the measurements are completed, the user display capability of the 1610A/B is employed to graph the results.

The 9825 calculator is only one example of the type of controller that could be used in this measurement system. The only requirement is that it be able to communicate over HP-IB. This type of measurement system can be a valuable tool for the optimization and analysis of software.

### Two Measurement Examples

Two measurement examples will be illustrated in this section. The first emphasizes how the analyzer recognizes these higher level software modules. The second describes measurements made on a system that led to considerable performance improvement in an operating system.

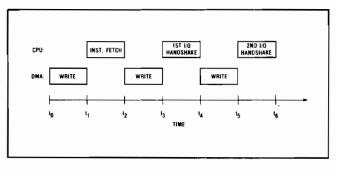

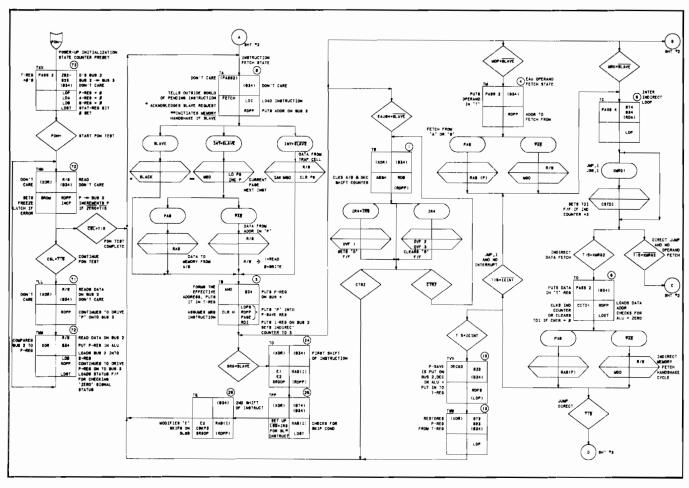

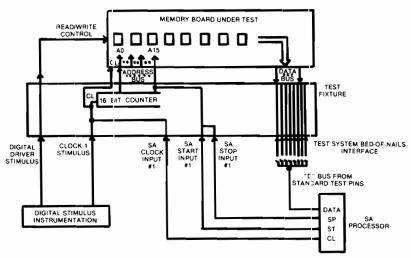

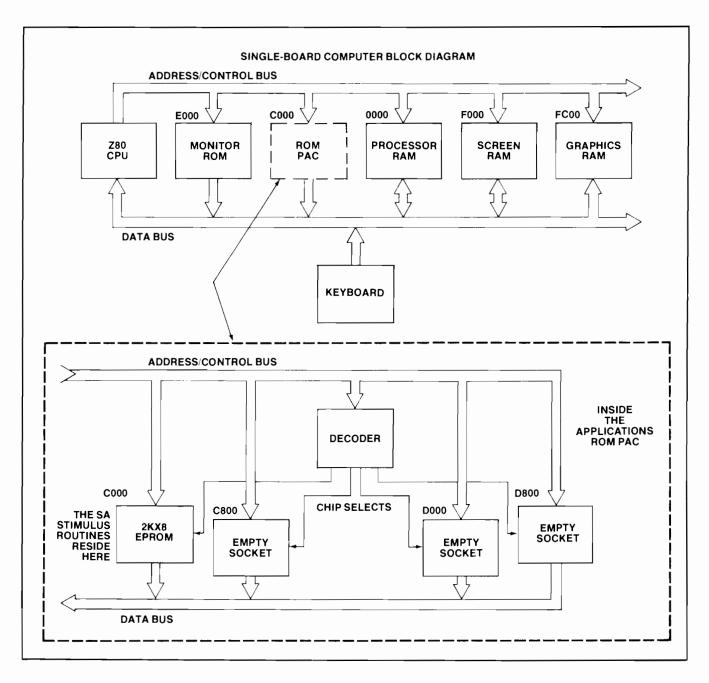

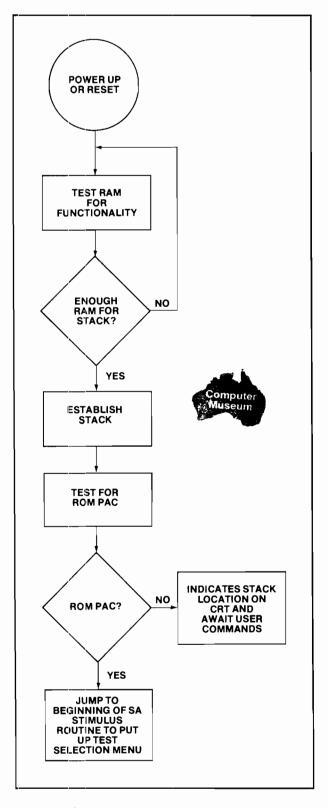

In the first example, the computer system under test is the HP 64000 Development System. The HP 64000 uses a 16-bit processor, called the BPC, that was designed inhouse. The method used in this operating system to map external storage to physical main memory is that of manual segmentation, otherwise known as an overlay technique. With this type of memory management, program modules must be mutually exclusive and each program module must call the operating system to load and execute the next overlay.

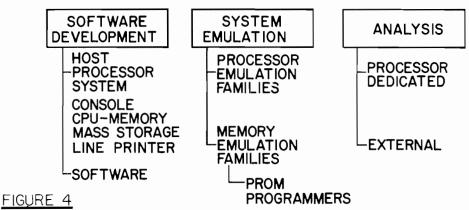

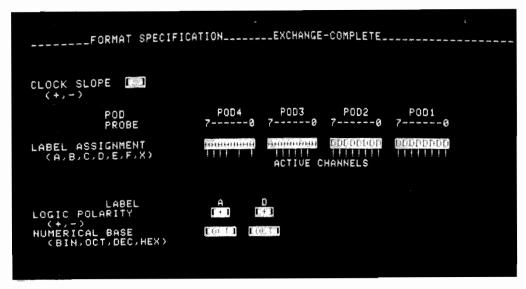

The Assembler for 8080 code was chosen as one of the high level software modules to be analyzed. Some measurements were also made on the operating system module called LOADEXEC. The 8080 Assembler

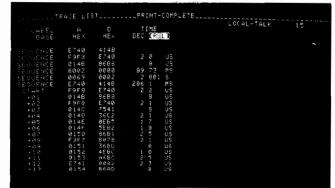

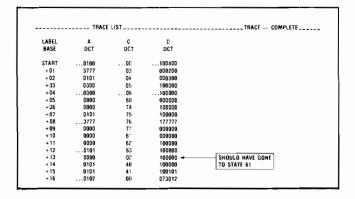

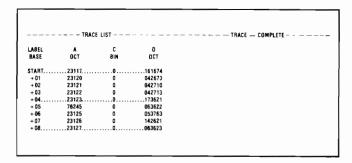

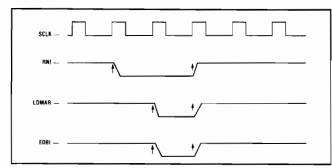

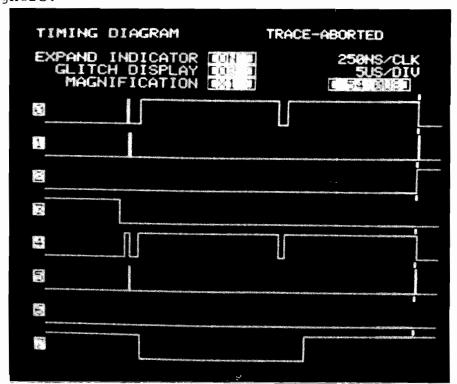

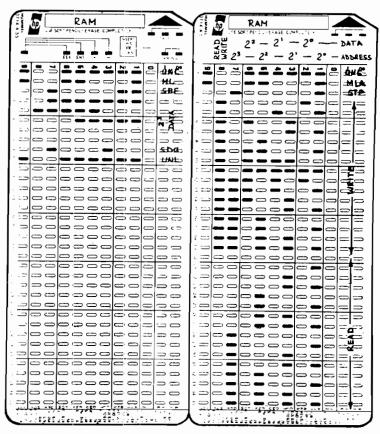

written for the 64000 System has five overlays. Depending on the options that were called for by the user, it is possible that not all five overlays would be brought into memory. The task of the 1610A/B was to identify the modules, know when they were executing, and measure the execution time. Format specifications on the 1610A/B were set up to look at the 16 bits of address and the 16 bits of data available on the BPC bus. Shown in Figure 4 is an example of the Trace Specification to identify Pass 2 of the assembler. (A) is the beginning address of the LOADEXEC routine and (B) is the starting address of the overlay. (C) is an address that is written to by the assembler module and identifies which module is being executed. For example, the data word would be 0003 if the third overlay were being executed. This was a software testpoint that had been inserted by the designer. It is also possible to identify the module by its name, since the name is passed as a parameter to the LOADEXEC routine. Three sequence terms would be needed on the analyzer to recognize the routine in this way since the name is packed into three 16-bit data words. In this case the three sequence terms for the name recognition would come before (B). The last term (D) signals the end of the overlay since it is the starting address of the LOADEXEC routine which is called at the end of each assembler module. A Trace List that was obtained for the second overlay is shown in Figure 5. Since the Count

FIGURE 4

FIGURE 5

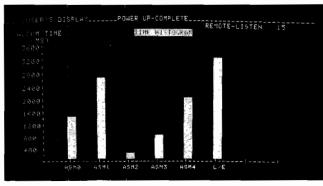

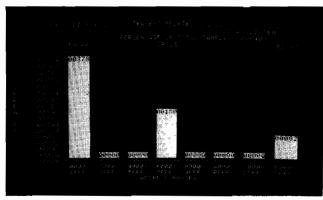

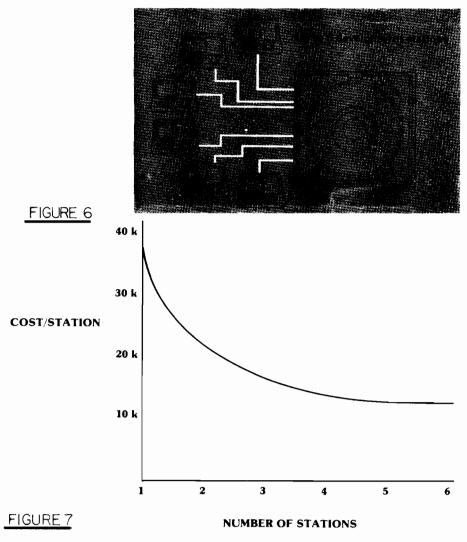

function of Time was selected in the Trace Specification, the trace list displays a relative time between each sequence term. This time information, as well as the data word identifying the particular overlay, is what is used by the controller. Figure—shows the flow of the 9825 program that was written for this example. After the measurement is completed, the results are displayed in the form of a time histogram (see Figure 7) which is done with the user display capability of the HP-IB interface for the 1610A/B. The execution times of these software modules were measured during the assembly of a single program. An accumulation of these execution times was also done during the assembly of ten different 8080 programs.

FIGURE 7

9825 Program Flow FIGURE 6

Measurements were also made on particular subroutines that were called during the assembly process. For these software modules, the frequency of usage was an important parameter. Time measurements were still made, but the distribution of times for the modules was of special interest. Figure 8 shows a distribution of times for five software modules that was printed on the 9866B.

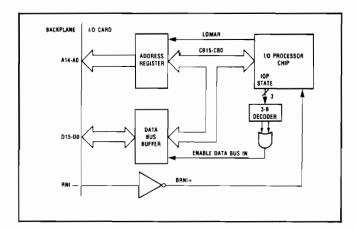

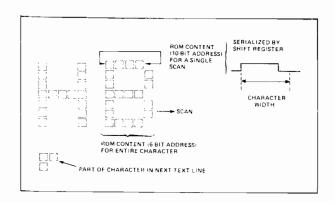

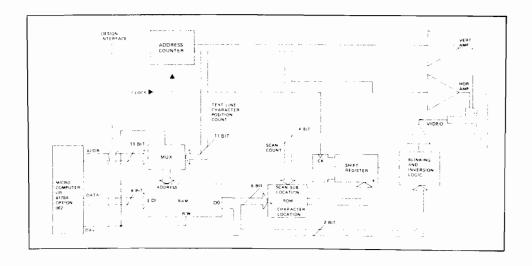

Another measurement that has been made on the 64000 System with a similar setup is a memory map of address space which partitions addresses into eight different buckets. The address range of the buckets is user-definable and the display is again a histogram (see Figure 9). The display shows the total number of addresses acquired, the exact number of addresses which fell within the specified range, and the number of addresses as a percentage of the total acquired addresses for each bucket. For this measurement the 1610A/B traces on the address = XXXX (Don't Cares) and the analyzer takes samples of what is happening on the address bus. There is no interaction with the BPC processor in this case.

FIGURE 9

(TIME in MS)

|                                                                                                                                | EXFRESS1                                                                        | ASM.SCAN                                                                                                        |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                        | tEXPRESS                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|                                                                                                                                | E - HOU THE BOX D A LOCK COLOR OF THE                                           | , 200 100 10. 10. 10. 10. 10. 10. 10. 10. 1                                                                     |                                  | THE REPORT OF THE PART OF THE | FIG. 500 Sec. 10. C.                                                                                               | a non ann ann ann ann an an ann ann ann                                                         |

| 1<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>8<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0.03560 0.03790 0.03810 0.03570 0.03570 0.03570 0.03570 0.03570 0.03570 0.03570 | 0.50520 0.18720 0.18720 0.18580 0.20750 0.22930 0.21810 0.35250 0.18720 0.18880 0.18880 0.18870 0.18750 0.18750 |                                  | 0.30670 0.47990 0.47950 0.50580 0.47500 0.62160 0.50640 0.50640 0.50640 0.50860 0.47630 0.47630                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.34230<br>0.51780<br>0.51760<br>0.54150<br>0.54070<br>0.68250<br>0.65730<br>0.57620<br>0.54230<br>0.54230<br>0.54230<br>0.54230<br>0.54230<br>0.54230 | 0.84750 0.70500 0.70430 0.72870 0.69650 0.88660 0.78660 0.72590 0.72590 0.72590 0.72980 0.73010 |

| di me                                                                                                                          | tool at the high built for the                                                  |                                                                                                                 | STATISTICAL                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ED a 1.1. II. SDOIL SD                                                                                                                                 | KIN MEDICAL KING                                                                                |

|                                                                                                                                |                                                                                 |                                                                                                                 | Son't III de Son't de Son't [fou | . worthing t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |                                                                                                 |

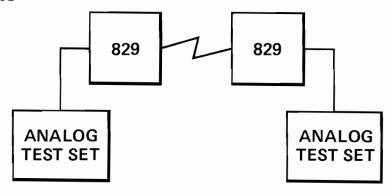

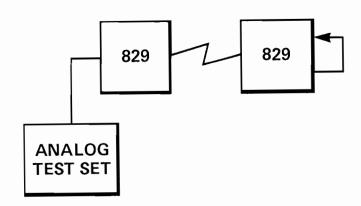

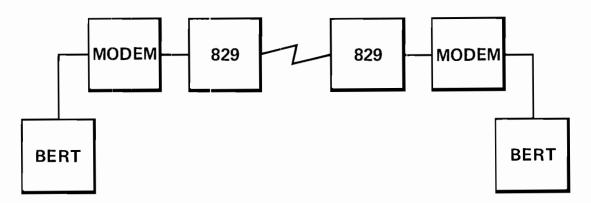

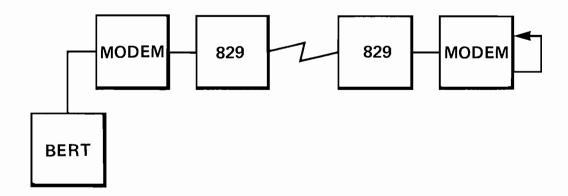

|                                                                                                                                | 707                                                                             | Fi                                                                                                              |                                  | MINIMUM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MARIM                                                                                                                                                  | UM                                                                                              |