## HP 98032A Installation and Service

## 98032A 16-Bit Interface Installation and Service Manual

## **Table of Contents**

| Chapte | er 1: General Information            |

|--------|--------------------------------------|

| Int    | troduction1                          |

|        | Operation 1                          |

|        | echnical Specifications 1            |

| Int    | terface Options                      |

|        | ardware Description                  |

|        |                                      |

| Chapte | er 2: Installation Considerations    |

| Int    | troduction 3                         |

|        | elect Code 3                         |

|        | elect Code Interrupt Considerations4 |

|        | necking Interface Operations4        |

| Op     | otion Interface Installation         |

| Sta    | andard Interface Installation        |

| Ва     | asic Installation Steps 5            |

| Da     | ata Handshake 5                      |

|        | The Two Modes of Handshake           |

| Mo     | odes of Operation 8                  |

| Se     | electing Timing Capacitor            |

| Ca     | able Preparation                     |

|        | Procedure                            |

| Re     | ecommended Driver Circuits11         |

|        | Data Lines                           |

|        | Other Lines                          |

| Re     | ecommended Receiver Circuits         |

| Co     | onfiguring the Logic                 |

| Da     | ata Input Lines                      |

|        | Associated Configuration Jumpers     |

| Da     | ata Output Lines16                   |

|        | Associated Configuration Jumpers     |

| Pe     | eripheral Control Line18             |

|        | Associated Configuration Jumpers     |

| Pe     | eripheral Flag Line                  |

|        | Associated Configuration Jumpers     |

## HP Computer Museum www.hpmuseum.net

For research and education purposes only.

| Peripheral Status Line                      | 20 |

|---------------------------------------------|----|

| Associated Configuration Jumpers            | 20 |

| Extended Status Input Lines                 | 20 |

| Extended Control Output Lines               | 21 |

| Input/Output Direction Control Line         | 21 |

| Peripheral Reset Line                       | 22 |

| External Interrupt Request Line             | 22 |

| Grounding                                   | 23 |

| Jumper Reference                            | 24 |

| Chapter 3: Service                          |    |

| Introduction                                | 25 |

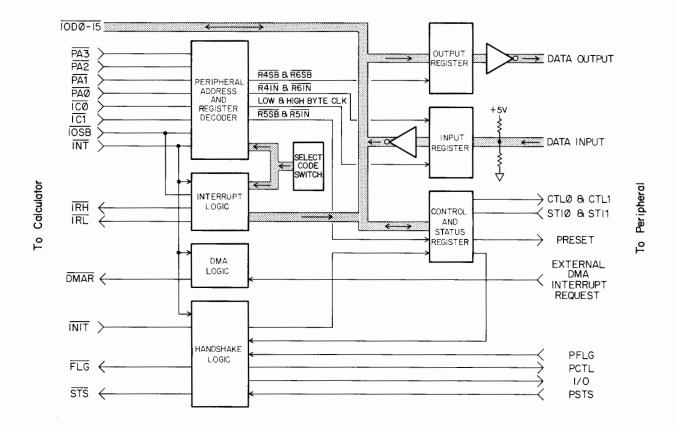

| Block Diagram Description                   |    |

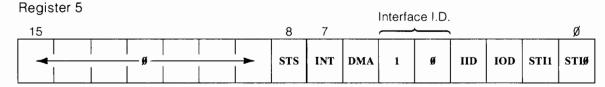

| Registers                                   |    |

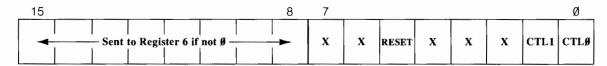

| Program Control of the Registers            |    |

| Control Circuits                            |    |

| Interface Operational Test                  |    |

| Troubleshooting and Repair                  |    |

| Broken Trace Repair                         |    |

| Recommended Equipment                       |    |

| Equipment Set Up                            |    |

| Procedure                                   |    |

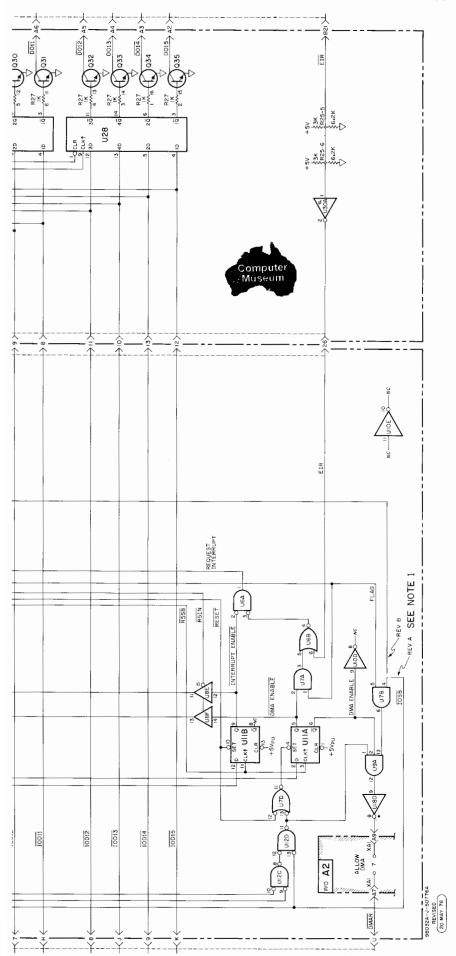

| Theory of Operation                         | 31 |

| Input Data Register                         | 31 |

| Output Data Register                        |    |

| Handshake Logic                             | 33 |

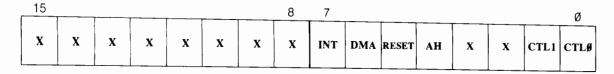

| Control and Status Register                 | 35 |

| Peripheral Address Decoder                  | 36 |

| Register Decoder                            | 36 |

| Interrupt Logic                             | 37 |

| Direct Memory Access Logic                  | 38 |

|                                             |    |

| Appendix A: Test Connector Diagram          | 45 |

| Appendix B: Interface Option Cable Diagrams | 47 |

| Appendix C: Jumpers to Simulate HP 11202A   | 71 |

| Figures |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

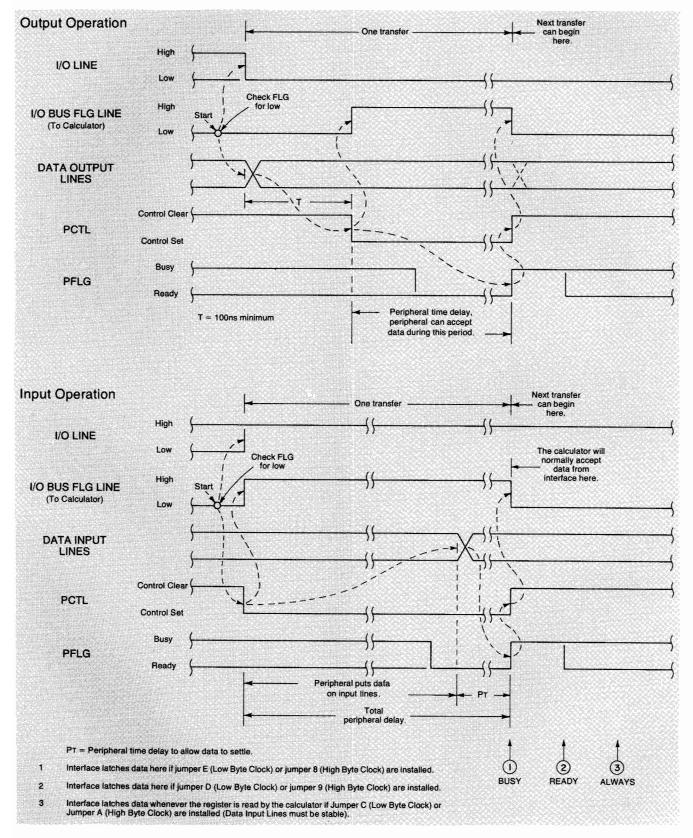

| 2-1.    | Full Mode Timing Diagram 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

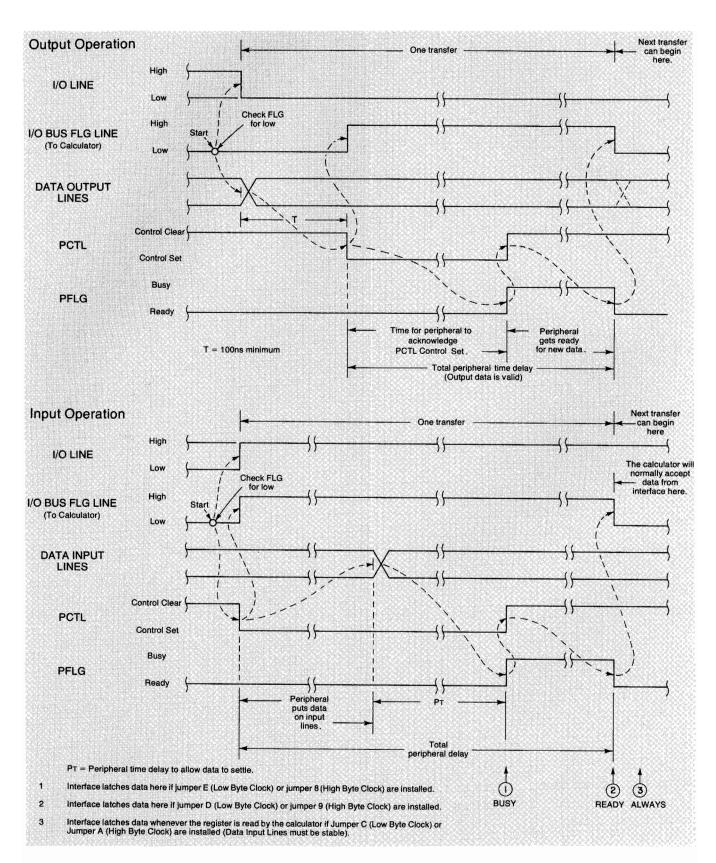

| 2-2.    | Pulse Mode Timing Diagram 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

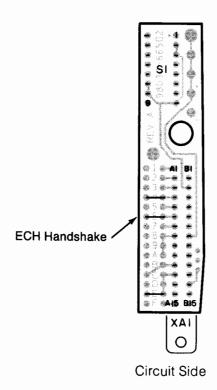

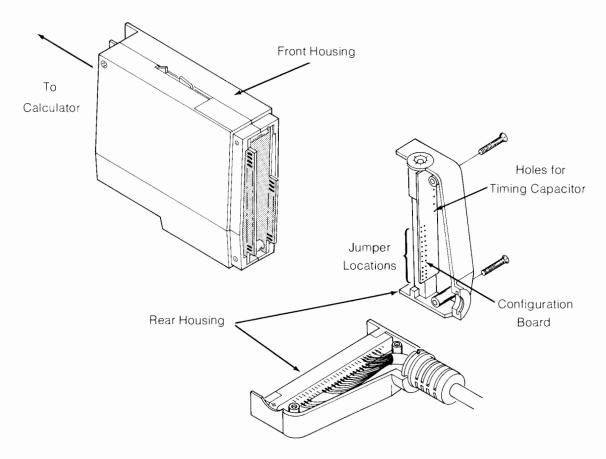

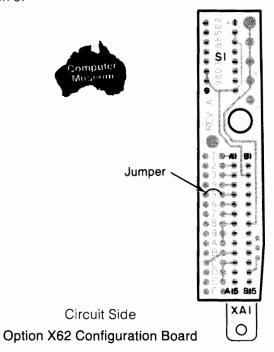

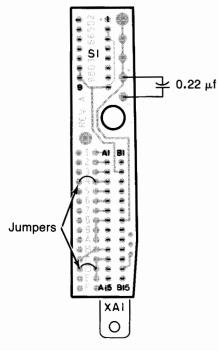

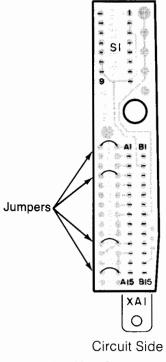

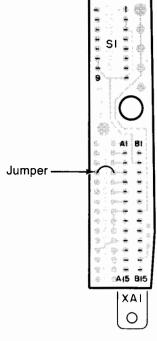

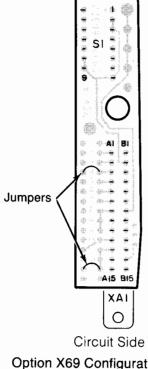

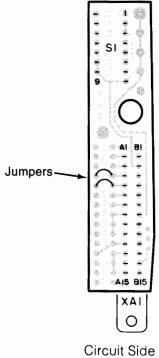

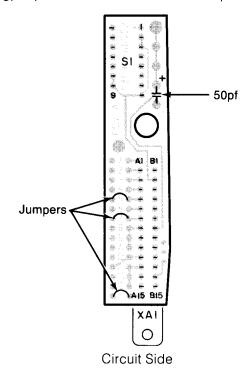

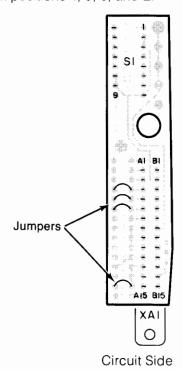

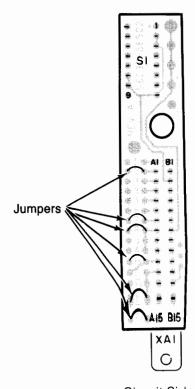

| 2-3.    | Configuration Board 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

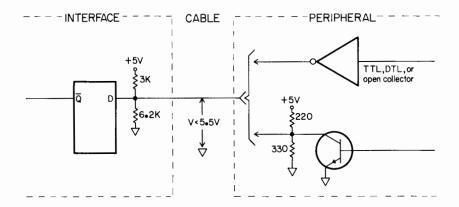

| 2-4.    | Recommended Peripheral Driver Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

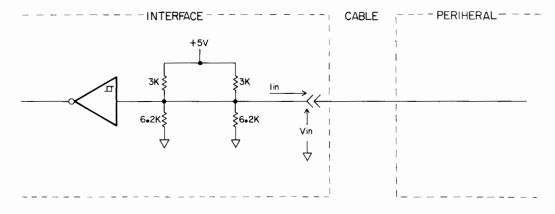

| 2-5.    | Interface PFLG, PSTS, and EIR Receiver Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

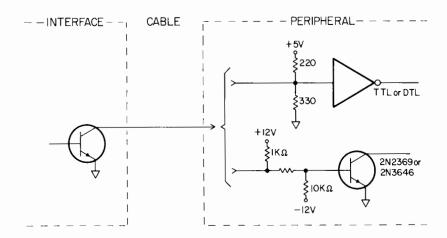

| 2-6.    | Recommended Peripheral Receiver Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

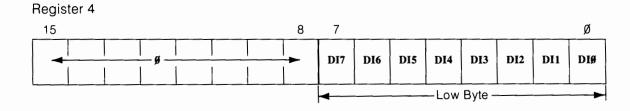

| 2-7.    | Data Input Bit Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

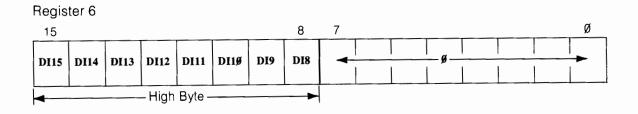

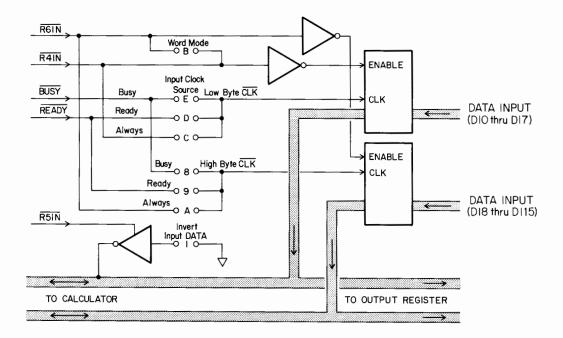

| 2-8.    | Data Input Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

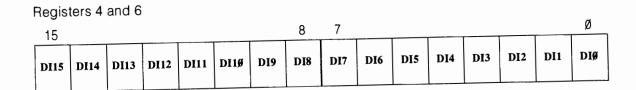

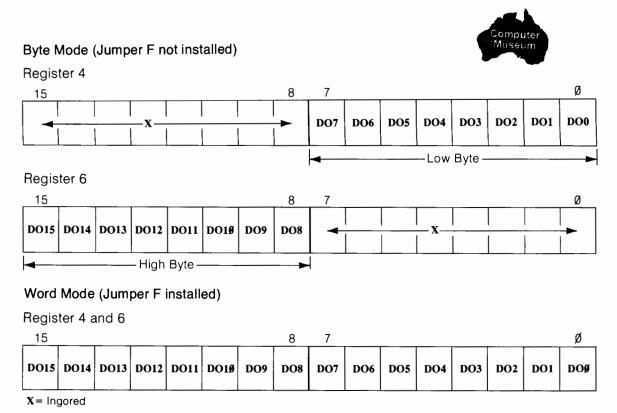

| 2-9.    | Data Output Bit Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

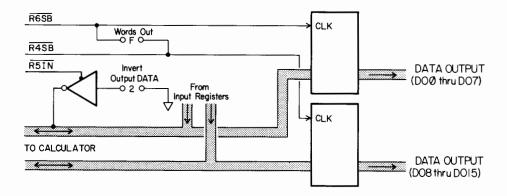

| 2-10.   | Data Output Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

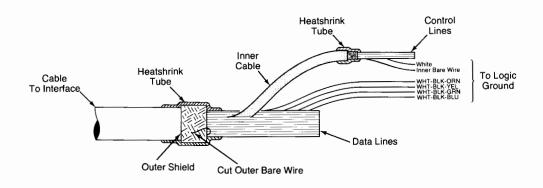

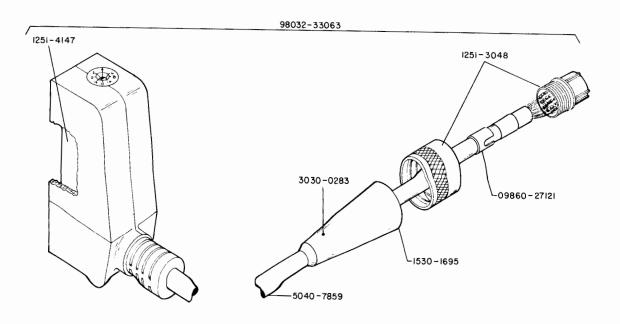

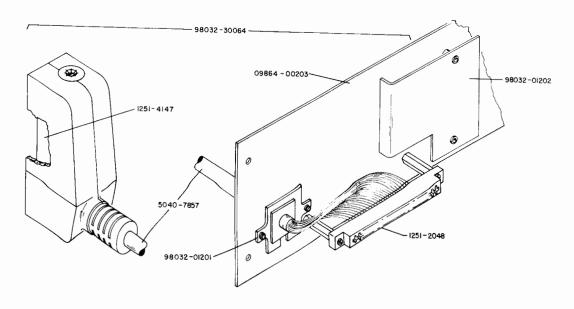

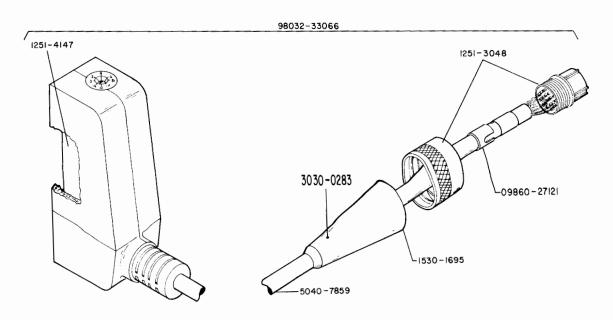

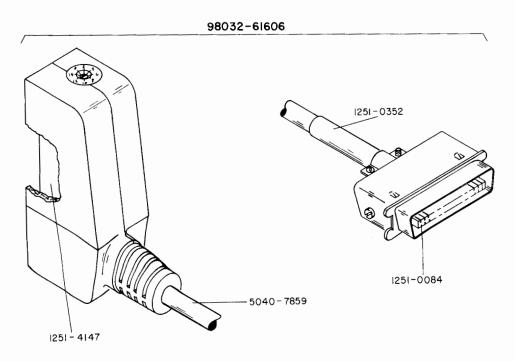

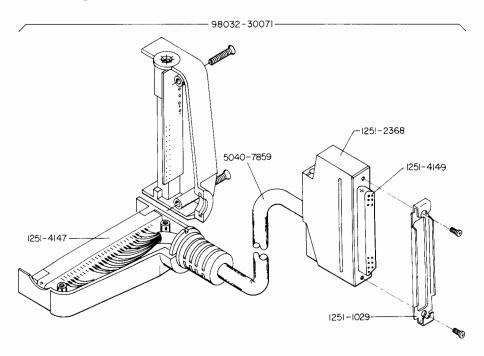

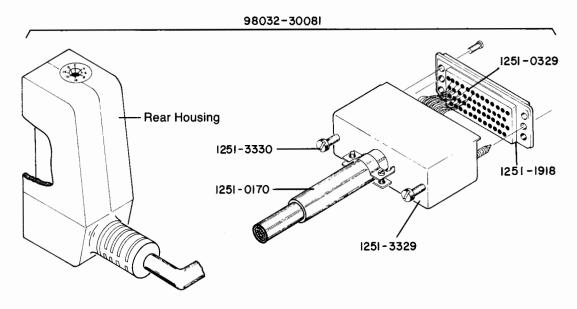

| 2-11.   | Cable Preparation and Ground Wires23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3-1.    | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

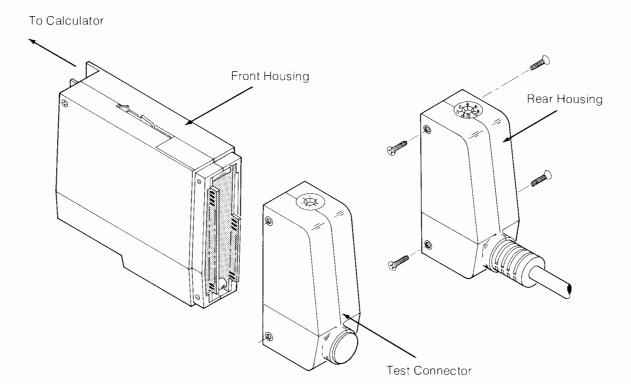

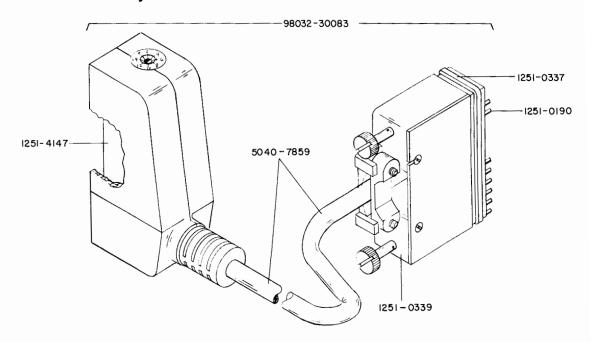

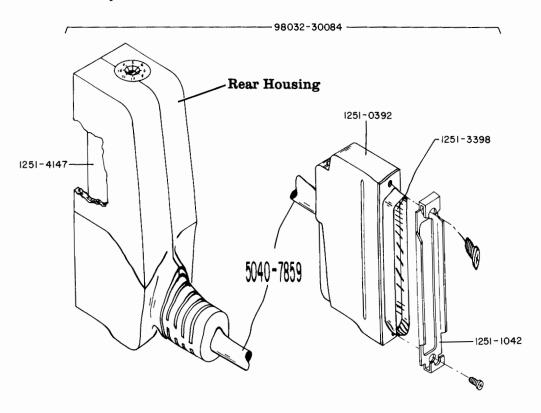

| 3-2.    | Test Connector Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

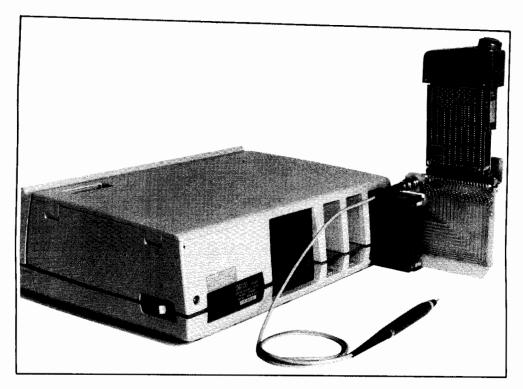

| 3-3.    | Interface Test Set Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

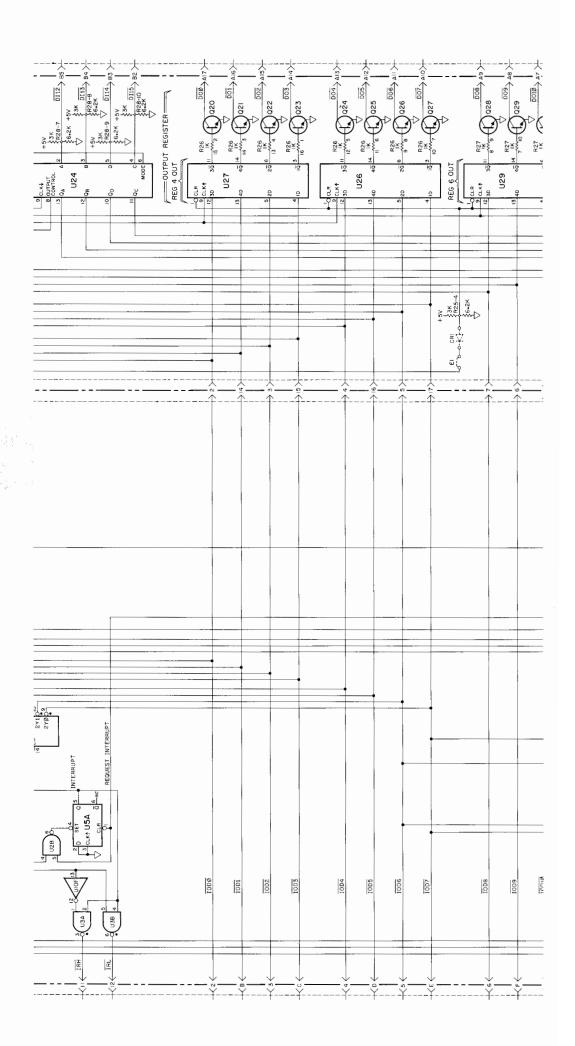

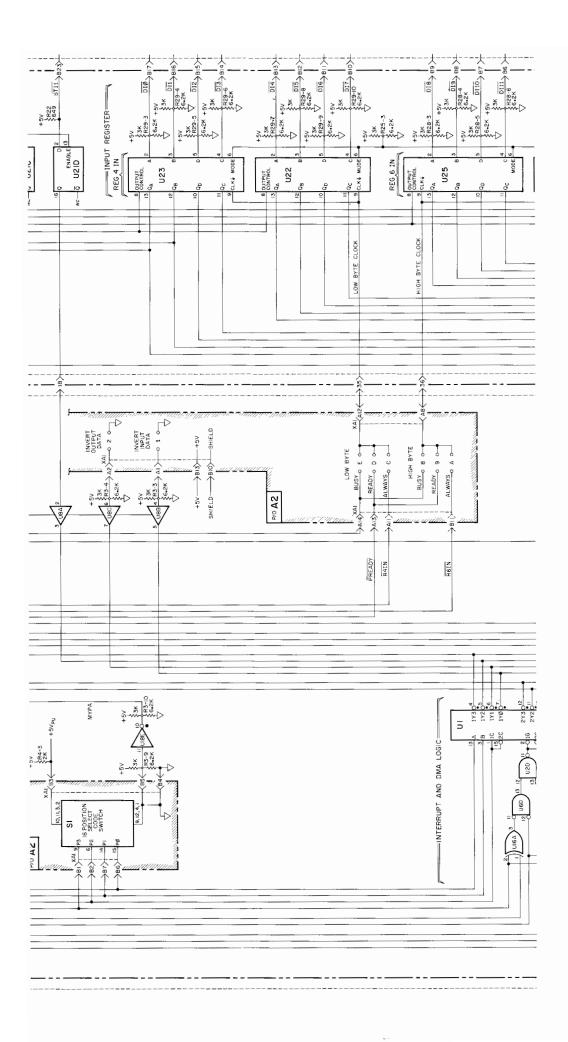

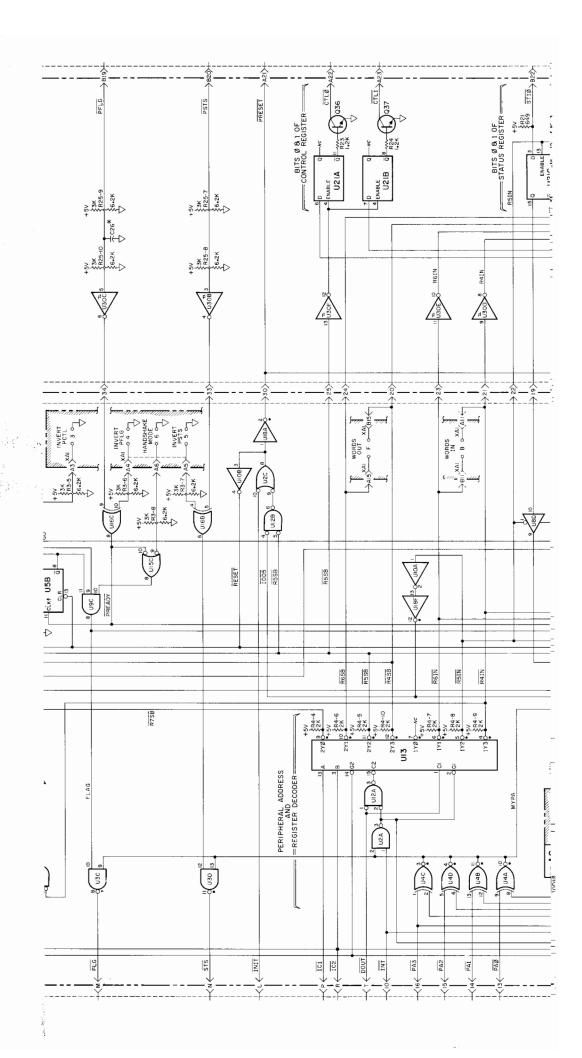

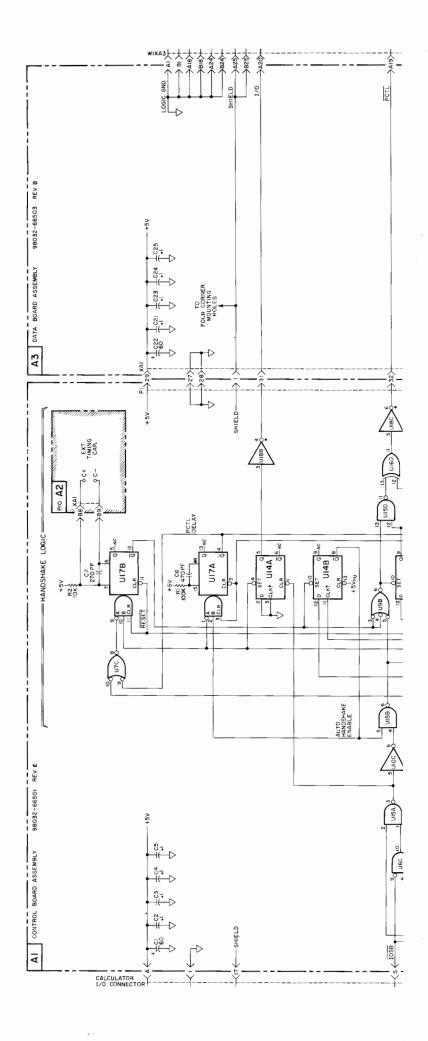

| 3-4.    | 98032A Interface Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Tables  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1-1.    | Interface Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2-1.    | Handshake Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2-2.    | Data Input Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2-3.    | Data Output Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2-4.    | Peripheral Control Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2-5.    | Peripheral Flag Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2-6.    | Peripheral Status Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2-7.    | ZATO TO CONTRACT THE CONTRACT T |

| 2-8.    | Extended Control Output Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2-9.    | I/O Direction Control Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2-10.   | Preset Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2-11.   | Enternal Interrupt Request Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2-12.   | Configuration Jumpers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3-1.    | Register Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3-2.    | Replaceable Parts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# Chapter **1**General Information

#### Introduction

The HP 98032A I/O Interface is a general-purpose interface which provides 16-bit data exchange between HP Desktop Computers (System 25/35/45) and a peripheral device. The terms "Desktop Computer" and "Calculator," as used in this manual, are synonymous. The interface transfers data in a "full-duplex" mode. That is, it can have data on the output lines and be inputting data at the same time.

The hardware and software characteristics of the interface are extremely flexible. The data exchange timing and logic can be "configured", by the use of jumpers, to meet a wide variety of peripheral requirements.

The interface is shipped from the factory either as an Option or Standard Interface. The Option Interface is pre-configured for operation with a given calculator peripheral. The Standard Interface is to be configured by you, to meet your peripheral's requirements.

## I/O Operation

The firmware for input/output operations is contained in the Desktop Computer I/O ROM. See the appropriate I/O ROM Manual for descriptions and syntax of the I/O statements required to operate the interface.

## **Technical Specifications**

Data Input Lines: 16 latched, DI0 – DI15

Data Output Lines: 16 open collector, DO0 - DO15

Control Lines: PCTL, PFLG

Signal Levels: TTL and open collector

Temperature Range: 0 ° to 45 °C Ambient

Power: +5 Volts 300ma, obtained from the Calculator

Dimensions: Approximately  $16.3 \times 8.9 \times 3.8 \text{ cm} (6.4 \times 3.5 \times 1.5 \text{ in})$

Cable Length: Standard – 4.5m (15')

Options -2.0m(6.5')

## Interface Options

The 98032A option interfaces are shipped from the factory with the proper configuration jumpers and cable connector installed. This enables you to connect your peripheral to the Desktop Computer without having to configure the interface. Wiring diagrams of the option connectors and configuration jumpers are provided in appendix B. See the following table.

| Table 1-1. | Interface | Option | Diagrams |

|------------|-----------|--------|----------|

|------------|-----------|--------|----------|

| Peripheral                | Interface Options     |

|---------------------------|-----------------------|

| 6940A Multiprogrammer     | 040 - 340 - 440       |

| 9862A Plotter             | 062 - 162             |

| 9863A Paper Tape Reader   | 063 - 163             |

| 9864A Digitizer           | 064 - 164             |

| 9866A/B Thermal Printer   | 066 - 166 - 366 - 466 |

| 9869A Card Reader         | 069 - 169 - 369 - 469 |

| 9871A Impact Line Printer | 071 - 171 - 371 - 471 |

| 9881A Printer             | 081 - 181 - 381 - 481 |

| 9883A Paper Tape Reader   | 083 - 183 - 383 - 483 |

| 9884A Paper Tape Punch    | 084 - 184 - 384 - 484 |

| 9885A Flexible Disk       | 085 - 185 - 385 - 485 |

## Hardware Description

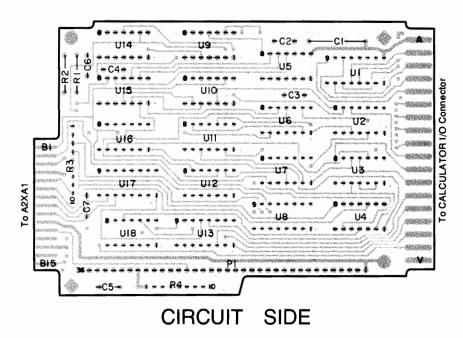

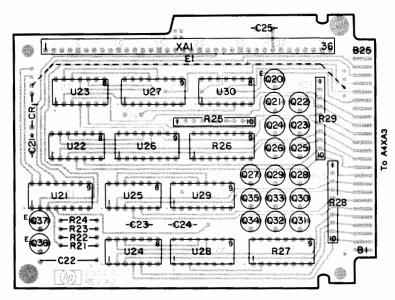

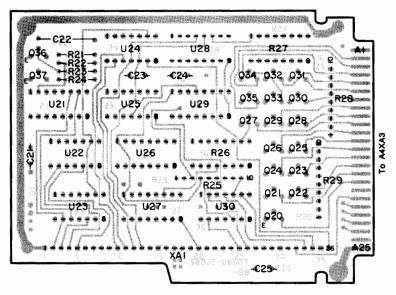

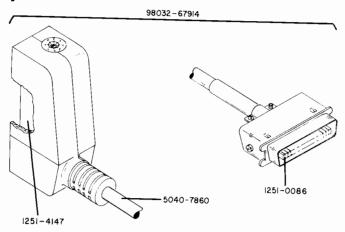

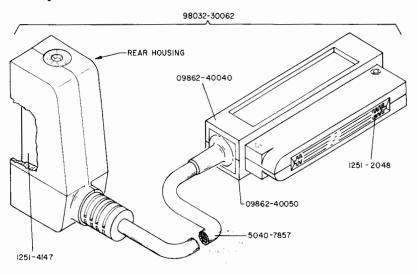

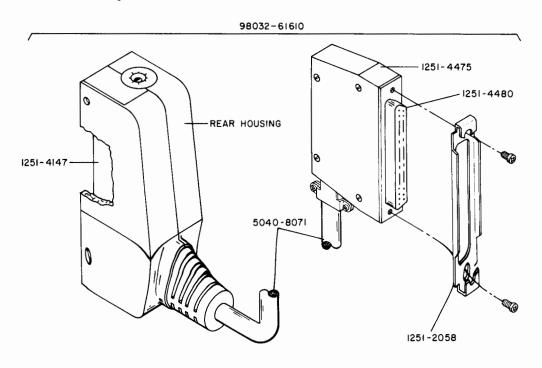

The Standard Interface consists of three circuit boards in a case. The case plugs into any one of the calculator I/O slots. A 4.5 meter (15 feet) unterminated shielded-cable is provided for connection to your peripheral.

The logic lines available to the user are:

- Sixteen latched data input lines.

- Sixteen latched data output lines.

- Three handshake lines.

- Two peripheral control lines.

- Three peripheral status lines.

- One line for DMA (Direct Memory Access) interrupt request.

- One line to reset the peripheral.

- Shield and ground connections.

## Chapter 2

## **Installation Considerations**

#### Introduction

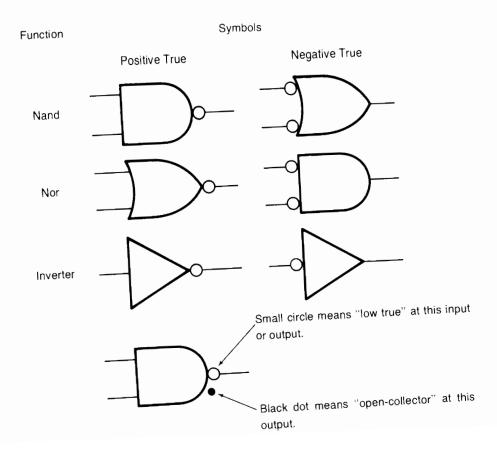

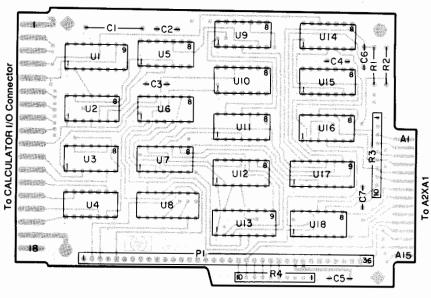

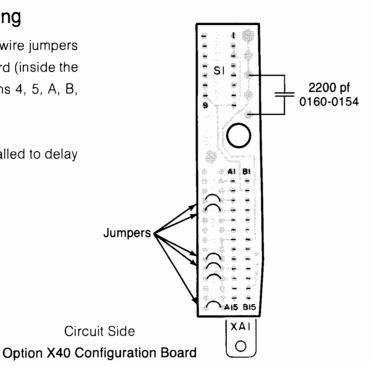

The complexity of the installation procedure depends on the device to be interfaced to the calculator. If the device is one of the calculator peripherals listed in Table 1-1, and you have the correct Option Interface, the procedure is quite simple. But if the device is one of your own, you will have to "configure" the Standard Interface to meet your needs. This involves installing the correct jumpers on the Configuration Board (see Figure 2-3) and installing a connector on the end of the cable.

#### Select Code

The select code should be checked for the proper setting as required by your system. The select code switch is accessible through a hole in the top of the interface case. If the interface is one of the options, the select code will be preset to the standard select code for the associated peripheral. The Standard Interface will be preset to select code 2. If it is necessary to change the setting, rotate the switch to the desired position using a small screwdriver. You should avoid using select codes reserved for the peripherals internal to the calculator. For example, the select codes shown below are used by the 9825A internal peripherals.

|             | 9825A Calculator    |

|-------------|---------------------|

| Select Code | Internal Peripheral |

| 0           | Keyboard/Display    |

| 1           | Cartridge           |

| 16          | Printer             |

Two interfaces should not be set to the same select code.

## Select Code Interrupt Considerations\*

In the interrupt mode, the 98032A operates on one of two priority levels. Interfaces set to Select codes 0 through 7 are on the low priority interrupt level and select codes 8 through 15 are on the high priority level. Devices requiring fast interrupt service should be set to the high level. Priority within a level is in order of the select code, with 7 and 15 having the highest priority.

## **Checking Interface Operations**

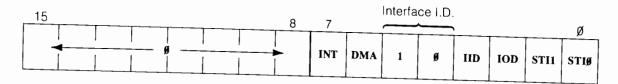

When an interface is installed it should be checked for proper operation. To do this, read the status from the appropriate select code. For correctly installed interfaces, the returned value will be equal to or greater than 288. If the interface is not inserted correctly or if the select code setting is incorrect a zero will be returned.

## Option Interface Installation

Each Option Interface is shipped from the factory with the proper configuration jumpers and cable connector for a given calculator peripheral (see Table 1-1). To connect one of the listed peripherals to the calculator follow the instructions supplied with the peripheral. Those instructions describe how to check the interface select code and make the necessary cable connections.

#### Standard Interface Installation

To install the Standard Interface with any other peripheral device it will be necessary to configure the interface to meet your needs. Configuring the interface is done by installing (soldering) the proper jumpers and if necessary a timing capacitor onto the Configuration Board (A-2). An appropriate cable connector should also be installed on the end of the cable.

In some cases, even though the configuration of the interface is very flexible, you may need to alter, or add to, the I/O logic of your device in order to make it compatible with the calculator I/O system.

<sup>\*</sup>An I/O ROM with interrupt capability is required to use the interrupt mode.

omputer

### Basic Installation Steps

The following basic installation steps are given, to aid you in connecting your peripheral to the calculator via the Standard 98032A Interface. The information necessary to implement these steps follows in the next sections of this chapter.

- 1. Determine the type of handshake that your peripheral will require.

- Select, if necessary, a timing capacitor.

- 3. Determine the logic lines that are to be used by your peripheral.

- 4. Install the proper configuration jumpers to obtain the proper logic (positive or negative true) and I/O handshake.

- 5. Connect the cable to your device or install the proper cable connector on the cable.

- 6. Set the select code switch to the proper position.

- 7. Connect the system together and check from the calculator keyboard all intended I/O operations (refer to Checking Interface Operations).

- 8. If there is a failure in step 7, install the optional test connector (refer to Interface Operational Test) and check similar I/O operations. If this fails refer to the Service section of this manual. If the I/O operations on the test connector operate properly, the problem is probably in the cable wiring, choice of jumpers, or your peripheral.

### Data Handshake

Synchronization of data exchanged between the calculator and a peripheral is referred to as the "handshake". The handshake is accomplished via the PCTL, PFLG and I/O lines. The peripheral receives information about the data exchange on the PCTL and I/O lines and then responds on the PFLG line. The I/O line tells the peripheral which direction the data is to be transferred, low indicates a calculator output operation, high indicates a calculator input operation.

If your peripheral does not require a handshake, connect the PFLG line to the PCTL line and then isolate these wires. Install either jumper 3 or jumper 4, but NOT both. Refer to Configuring the Logic (page 12) and to Figure 2-3.

The handshake lines, their states and intended meanings are listed in Table 2-1.

Table 2-1. Handshake Lines

| LINE | STATE OR MNEMONIC | MEANING |

|------|-------------------|---------|

|      | L                 |         |

#### Output

| 1/0           | LOW           | Calculator output operation.                    |