## MAINTENANCE MANUAL

## 30001A

## CENTRAL PROCESSOR UNIT/INPUT OUTPUT PROCESSOR

(FOR HP 3000 COMPUTER SYSTEMS)

Printed-Circuit Assemblies:

30001-60001 30001-60002 30001-60003 30001-60005 30001-60006 30001-60007 30001-60008 30001-60009 30001-60016 30001-60021 Changed pages are designated by a change date in the lower corner of the page. Original pages do not indicate a change date. Insert latest changed pages and destroy superseded pages.

| PAGE NUMBER       | ISSUE      | PAGE NUMBER                                                | ISSUE      |

|-------------------|------------|------------------------------------------------------------|------------|

| Title             | . Original | 3-91                                                       |            |

| ii and iii        |            | 3-92 Blank                                                 |            |

| iv Blank          |            | 3-93                                                       |            |

| v thru xii        | . Original | 3-94 Blank                                                 |            |

| 1-1 thru 1-14     | . Original | 3-95                                                       |            |

| 2-1 thru 2-17     |            | 3-96 Blank                                                 |            |

| 2-18 Blank        | . Original | 3-97                                                       |            |

| 3-1 thru 3-40     |            | 3-98 Blank                                                 |            |

| 3-41              |            | 3-99                                                       |            |

| 3-42 Blank        |            | 3-100 Blank                                                |            |

| 3-43              |            | 3-101                                                      | . Original |

| 3-44 Blank        | . Original | 3-102 Blank                                                | . Original |

| 3-45              | . Original | 3-103                                                      | . Original |

| 3-46 Blank        | . Original | 3-104 Blank                                                |            |

| 3-47              | . Original | 3-105                                                      | . Original |

| .3-48 Blank       | . Original | 3-106 Blank                                                | . Original |

| 3-49              | . Original | 3-107                                                      | . Original |

| 3-50 Blank        | . Original | 3-108 Blank                                                | . Original |

| 3-51 thru 3-58    |            | 3-109                                                      | . Original |

| 3-59              |            | 3-110 Blank                                                |            |

| 3-60 Blank        |            | 3-111                                                      |            |

| 3-61              |            | 3-112 Blank                                                |            |

| 3-62 Blank        |            | 3-113                                                      |            |

| 3-63              |            | 3-114 Blank                                                |            |

| <b>3-64 Blank</b> |            | 3-115                                                      |            |

| 3-65              |            | 3-116 Blank                                                |            |

| 3-66 Blank        | . Original | 3-117                                                      |            |

| 3-67              |            | 3-118 Blank                                                |            |

| 3-68 Blank        |            | 3-119                                                      |            |

| 3-69              |            | 3-120 Blank                                                |            |

| 3-70 Blank        |            | 3-121                                                      |            |

| 3-71              |            | 3-122 Blank                                                | . Original |

| 3-72 Blank        |            | 3-123                                                      |            |

| 3-73              |            | 3-124 Blank                                                |            |

| 3-74 Blank        |            | 3-125                                                      |            |

| 3-75              |            | 3-126 Blank                                                |            |

| <b>3-76 Blank</b> |            | 3-127                                                      |            |

| 3-77              |            | 3-128 Blank                                                |            |

| 3-78 Blank        |            | 3-129                                                      |            |

| 3-79              |            | 3-130 Blank                                                | -          |

| <b>3-80 Blank</b> |            | 3-131                                                      | •          |

| 3-81              |            | 3-132 Blank                                                |            |

| <b>3-82 Blank</b> |            | 3-133                                                      |            |

| <b>3-83</b>       |            | <b>3-134 Blank</b>                                         |            |

| <b>3-84 Blank</b> |            | 3-135                                                      |            |

| <b>3-85</b>       |            | <b>3-136 Blank</b>                                         | •          |

| 3-86 Blank        | -          | <b>3-130 Mark 3 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - </b> |            |

| 3-80 Diank        |            | 3-137                                                      |            |

| 3-87              |            | <b>3-138 Diank</b>                                         | -          |

| 3-89              |            | 3-139                                                      |            |

| 3-89              |            |                                                            |            |

| 0-70 DIANK        | . Ouginar  |                                                            | · Onginal  |

# LIST OF EFFECTIVE PAGES (Continued)

| ISSUI    |   |   |   |   |   |   |   |   |   |   |   | R | Ef | B   | NUM   | PAGE N    | UE   | ISSU     |   |   |   |   |  |   |   |   |   | 1 | ER | B   | ENUM    |

|----------|---|---|---|---|---|---|---|---|---|---|---|---|----|-----|-------|-----------|------|----------|---|---|---|---|--|---|---|---|---|---|----|-----|---------|

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    |     |       | 3-183     | inal | . Origi  |   |   |   |   |  |   |   |   |   |   |    | ς.  | 2 Blank |

|          |   |   |   |   |   | • |   |   |   |   |   |   |    | ζ   | lank  | 3-184 B   |      | . Origi  |   |   |   |   |  |   |   |   |   |   |    |     | 3.      |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    |     |       | 3-185     | inal | . Origi  |   |   |   |   |  |   |   |   |   |   |    | c   | 4 Blank |

|          |   |   |   |   |   |   |   |   |   |   |   |   |    |     |       | 3-186 B   |      | . Origi  |   |   |   |   |  |   |   |   |   |   |    |     | 5.      |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    |     |       | 3-187     |      | . Origi  |   |   |   |   |  |   |   |   |   |   |    | C I | 6 Blank |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    | K   | lank  | 3-188 B   |      | . Origi  |   |   |   |   |  |   |   |   |   |   |    |     | 7.      |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    |     |       | 3-189     |      | . Origin |   |   |   |   |  |   |   |   |   |   |    | c   | 8 Blank |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    | s   | lank  | 3-190 B   | inal | . Origi  |   |   | , |   |  |   |   |   |   |   |    |     | 9.      |

| . Origin |   |   |   |   | • |   |   |   |   |   |   |   |    |     |       | 3-191     | inal | . Origin |   |   |   |   |  | • |   |   | • |   | •  | C I | 0 Blank |

| . Origin |   |   |   |   |   | • |   |   |   |   |   |   |    | C   | Blank | 3-192 B   | inal | . Origin | • |   |   |   |  |   |   |   |   |   |    |     | 1.      |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    |     |       | 3-193     | inal | . Origin |   |   |   |   |  | • |   |   | • |   |    | c   | 2 Blank |

| . Origin |   |   |   | • |   |   |   |   |   |   | • |   |    | s   | lank  | 3-194 B   | inal | . Origin |   |   |   |   |  |   |   |   |   |   |    |     | 3.      |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    |     |       | 3-195     | inal | . Origin | • | • |   |   |  |   |   |   |   |   |    | C I | 4 Blank |

| . Origin |   |   |   |   | • | • |   |   |   |   |   |   |    | C   | lank  | 3-196 B   | inal | . Origin |   |   | , |   |  |   |   |   | • |   |    |     | 5.      |

| . Origin |   |   | • |   | • | • |   |   |   |   |   |   |    |     |       | 3-197     | inal | . Origin | • |   |   |   |  |   | • |   | • |   |    | C   | 6 Blank |

| . Origin |   |   |   |   | • | • |   |   |   |   |   |   |    | s   | lank  | 3-198 B   | inal | . Origin |   |   | , |   |  |   |   |   |   |   |    | •   | 7.      |

| . Origin |   |   |   | • | • |   |   |   |   |   |   |   |    |     | •     | 3-199     | inal | . Origi  | • | • |   | • |  |   |   |   | • | • |    | c   | 8 Blank |

| . Origin |   |   |   | • | • | • |   |   |   |   |   |   |    | s   | lank  | 3-200 B   | inal | . Origin |   |   |   |   |  | • |   |   |   |   | •  | •   | 9.      |

| . Origin |   |   |   |   |   | • |   |   |   |   |   |   |    |     |       | 3-201     | inal | . Origi  | • |   |   |   |  |   | • |   | • |   |    | C   | 0 Blank |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    | K   | lank  | 3-202 B   | inal | . Origin |   | • | , |   |  |   |   |   |   |   |    |     | 1,      |

| . Origin |   |   |   | • |   | • |   |   |   |   |   |   |    |     |       | 3-203     | inal | . Origin |   |   |   |   |  |   |   |   |   |   |    | C   | 2 Blank |

| . Origin |   |   |   |   | • | • |   |   |   |   |   |   |    | S   | lank  | 3-204 B   | inal | . Origin | • |   |   |   |  |   | • |   |   |   |    |     | 3.      |

| . Origin |   |   |   |   |   | • |   |   |   | • |   |   |    | • ' |       | 3-205     | inal | . Origin |   |   |   |   |  |   | • |   |   |   |    | C I | 4 Blank |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    | c   | lank  | 3-206 B   | inal | . Origin |   |   |   |   |  |   |   |   |   |   |    |     | 5.      |

| . Origin |   |   |   | • |   | • |   |   |   |   |   |   |    |     |       | 3-207     | inal | . Origin |   |   |   |   |  |   |   | • |   |   |    | c   | 6 Blank |

| . Origin |   |   |   | • |   | • |   |   |   | ÷ |   |   |    | c   | lank  | 3-208 B   | inal | . Origin | • |   | , | • |  |   |   |   |   |   |    | •   | 7.      |

| . Origin |   |   |   |   |   |   |   |   | • | • | • |   |    |     |       | 3-209     | inal | . Origin |   |   |   | • |  | • |   |   |   |   |    | c   | 8 Blank |

| . Origin |   |   |   |   |   | • |   |   |   |   |   |   |    | s   | lank  | 3-210 B   | inal | . Origin |   |   |   |   |  |   |   |   |   |   |    | •   | 9.      |

| . Origin |   |   |   |   |   | • |   |   |   |   |   |   |    | •   | •     | 3-211     | inal | . Origin | • | • |   |   |  |   | • |   | • |   |    | C C | 0 Blank |

| . Origin |   |   |   | • |   | • |   |   |   |   |   |   |    | s   | lank  | 3-212 B   |      | . Origin | • | • |   |   |  |   | • | • |   |   | •  |     | 1.      |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    |     |       | 3-213     |      | . Origin | • | • |   | • |  |   | • | • |   |   | •  | C I | 2 Blank |

| . Origin |   |   |   |   | _ | _ |   |   |   |   |   |   |    | ζ   | lank  | 3-214 B   |      | . Origi  | • | • |   | • |  |   | • | • | • |   | •  | •   | 3.      |

| . Origin | • | · | • | • | • |   | • | • |   | • |   |   |    | -   |       | 3-215     |      | . Origiı | • | • |   | • |  |   | • |   |   | • | •  | C I | 4 Blank |

| . Origin | • | • | • | - | • | • | - | - | : | • | - |   | •  |     | llank | 3-216 B   |      | . Origi  | • | • |   | • |  | • | • | • | • |   |    | •   | 5.      |

| -        | • | - | - | - |   | - | - |   |   |   |   |   | •  | 7   | nalik | 3-210 D   | inal | . Origi  |   | • |   | • |  |   |   | • |   |   |    | C I | 6 Blank |

| . Origin |   |   |   |   |   |   |   |   | • |   |   | • | •  | •   | •     |           |      | . Origin | • |   |   |   |  |   |   |   | • |   | •  | •   | 7.      |

| . Origin |   |   |   |   |   |   |   |   | • |   | • | • | •  |     |       | 3-218 B   |      | . Origi  | • |   |   |   |  |   |   |   |   |   |    | C I | 8 Blank |

| . Origin |   | - |   |   |   |   |   |   | • |   | • | • | 9. |     |       | 4-1 thru  | inal | . Origin |   |   |   |   |  |   |   |   |   |   |    |     | 9.      |

| . Origin |   |   |   |   |   |   |   |   | • |   |   |   |    |     |       | 4-130 B   |      | . Origin |   |   |   |   |  |   |   |   |   |   |    | C C | 0 Blank |

| . Origin | • |   | • | • | • | • |   |   |   | • | • |   |    |     |       | Certifica | inal | . Origin | • |   |   |   |  |   |   | • |   |   |    |     | 1.      |

| . Origin |   |   |   |   |   |   |   |   |   |   |   |   |    |     | over  | Back Co   | inal | . Origin |   |   |   |   |  |   |   |   |   |   |    | c   | 2 Blank |

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

This manual contains maintenance information for the HP 30001A Central Processor Unit and Input/ Output Processor (CPU/IOP). The HP 30001A CPU/IOP is part of the HP 3000 Computer System.

The contents of this manual are organized in four sections as follows:

- a. Section I contains general information of the CPU/IOP physical features and specifications.

- b. Section II contains operating parameters for the CPU/IOP including a list of all machine instructions for the HP 3000 Computer System.

- c. Section III contains theory of operation for the CPU/IOP.

- d. Section IV contains servicing instructions including preventive maintenance information and troubleshooting instructions.

This manual should be retained and used with related documentation for the HP 3000 Computer Systems. The related documentation should include the following publications:

- a. HP 3000 Computer System Reference Manual, part no. 03000-90019.

- b. The following detailed diagram sets in the HP 3000 Computer System Detailed Diagrams Manual, part no. 03000-90023.

- 1) DD Set No. 200. Read-Only Memory Printed-Circuit Assembly (PCA), part no. 30001-60001.

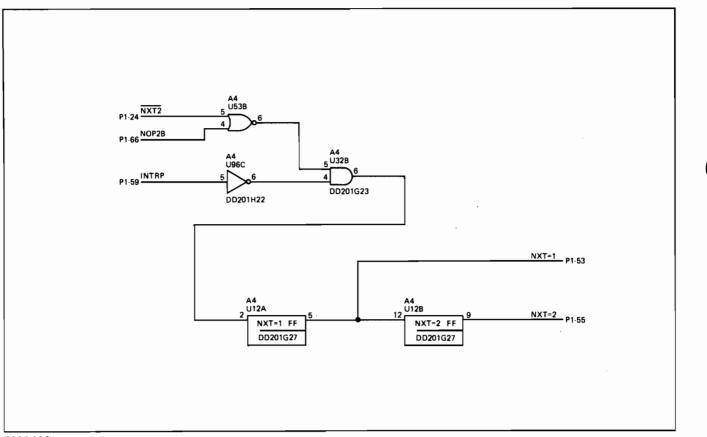

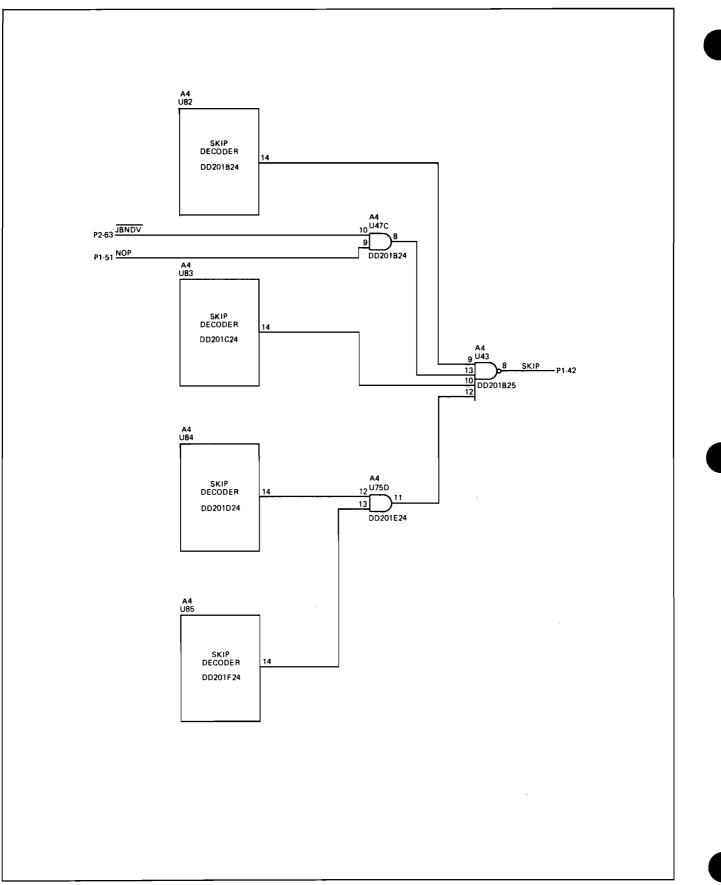

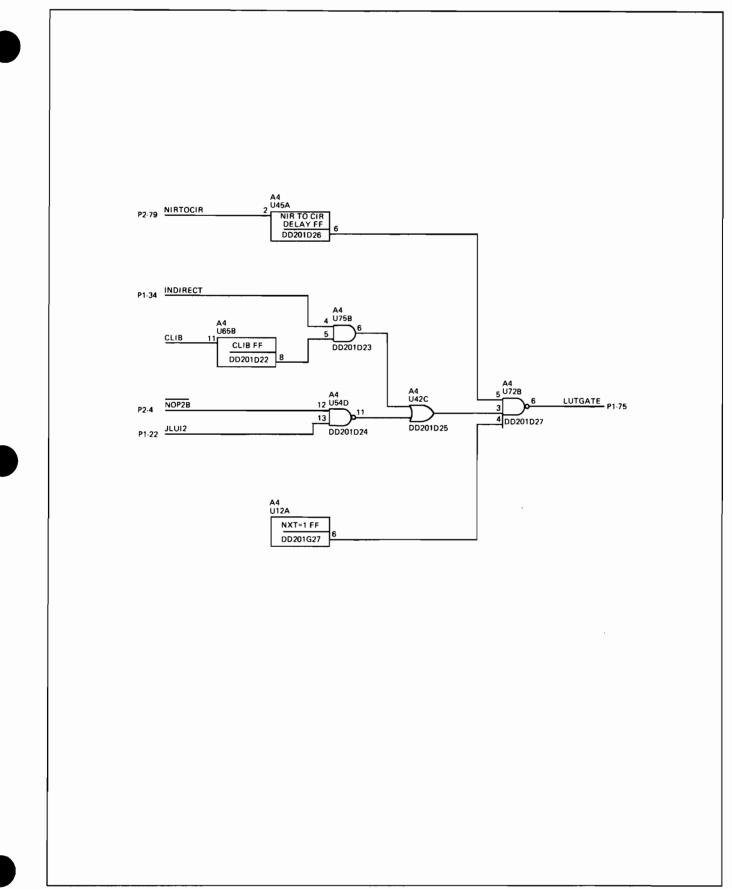

- 2) DD Set No. 201. Skip and Special Field PCA, part no. 30001-60002.

- 3) DD Set No. 202. Arithmetic and Logic Unit PCA, part no. 30001-60003.

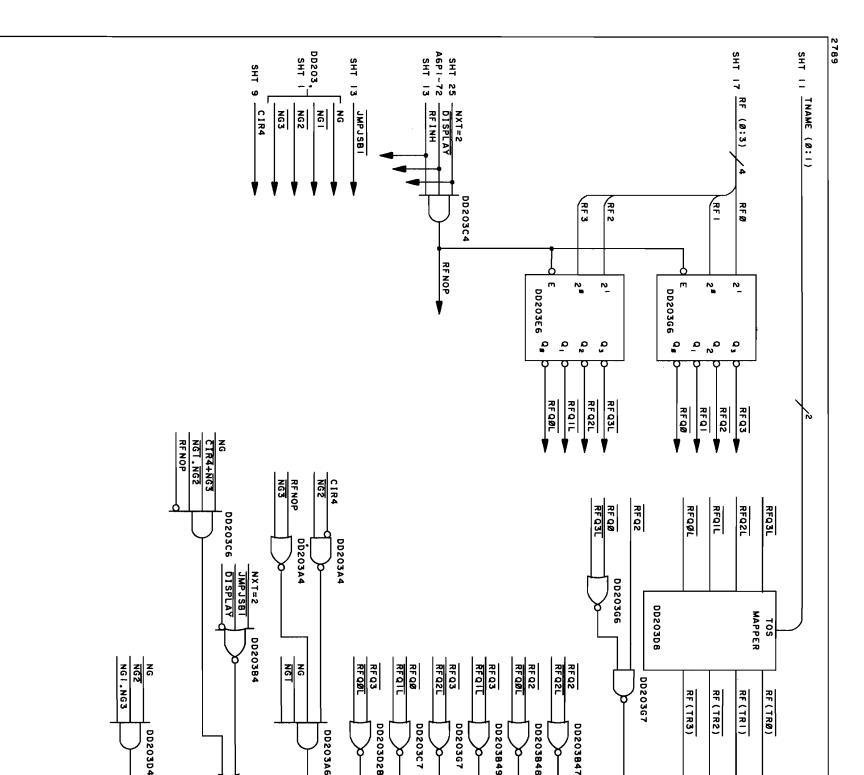

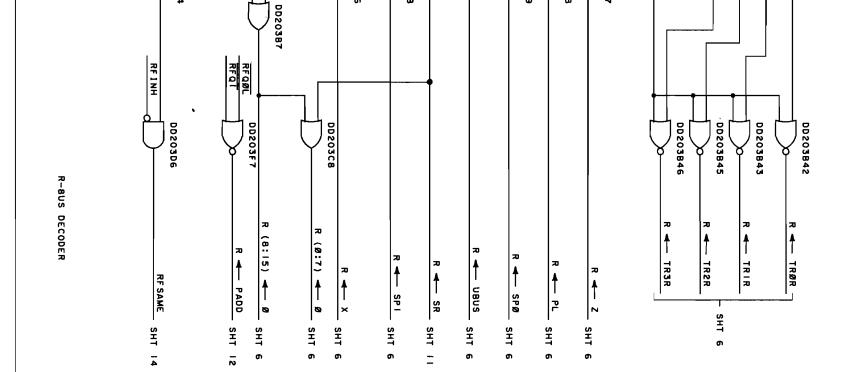

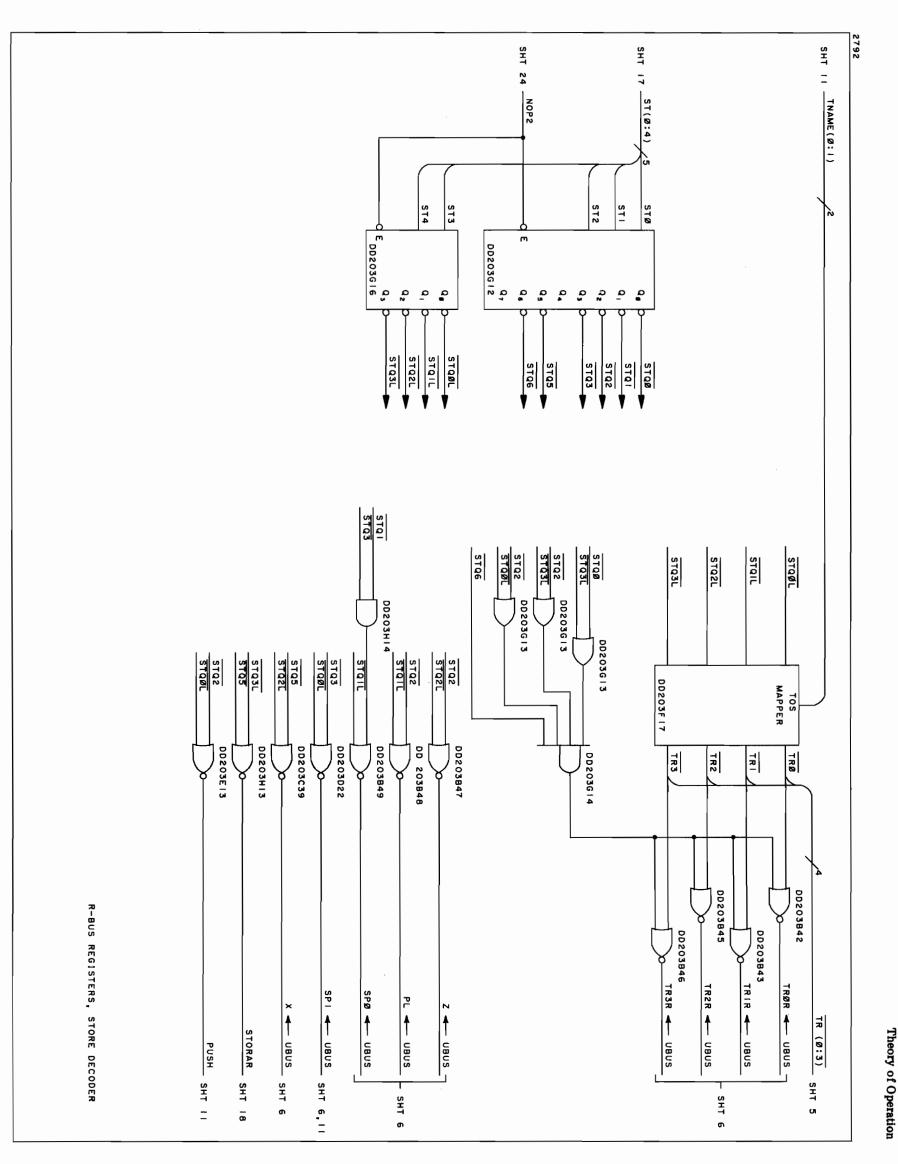

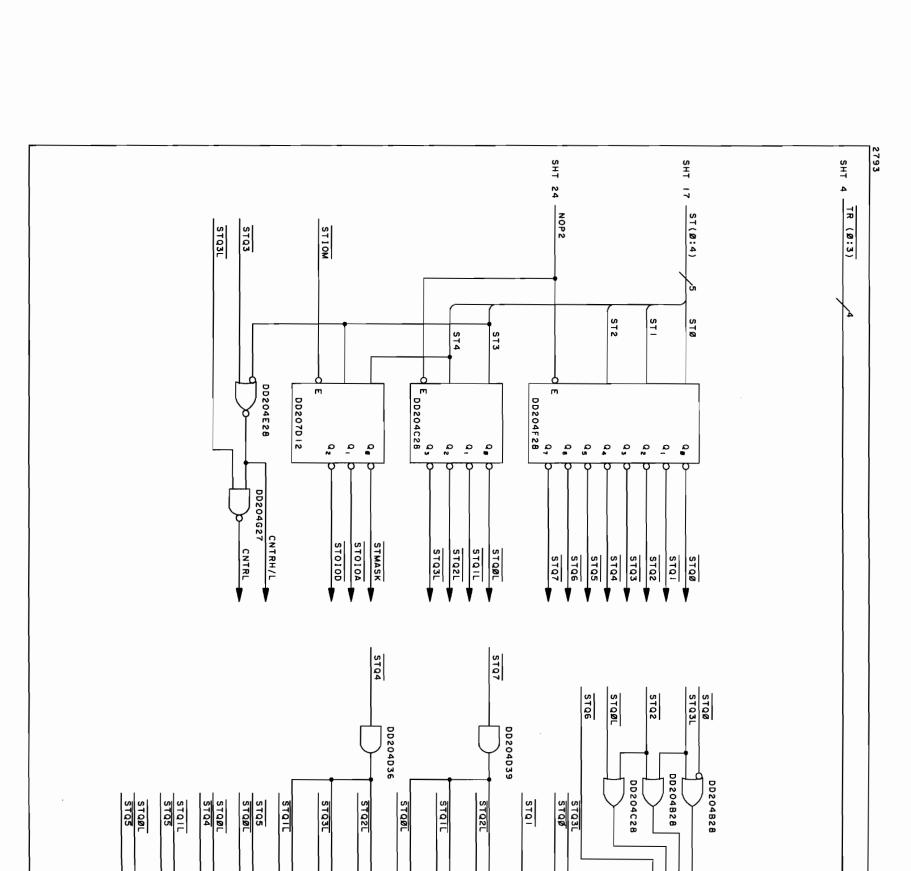

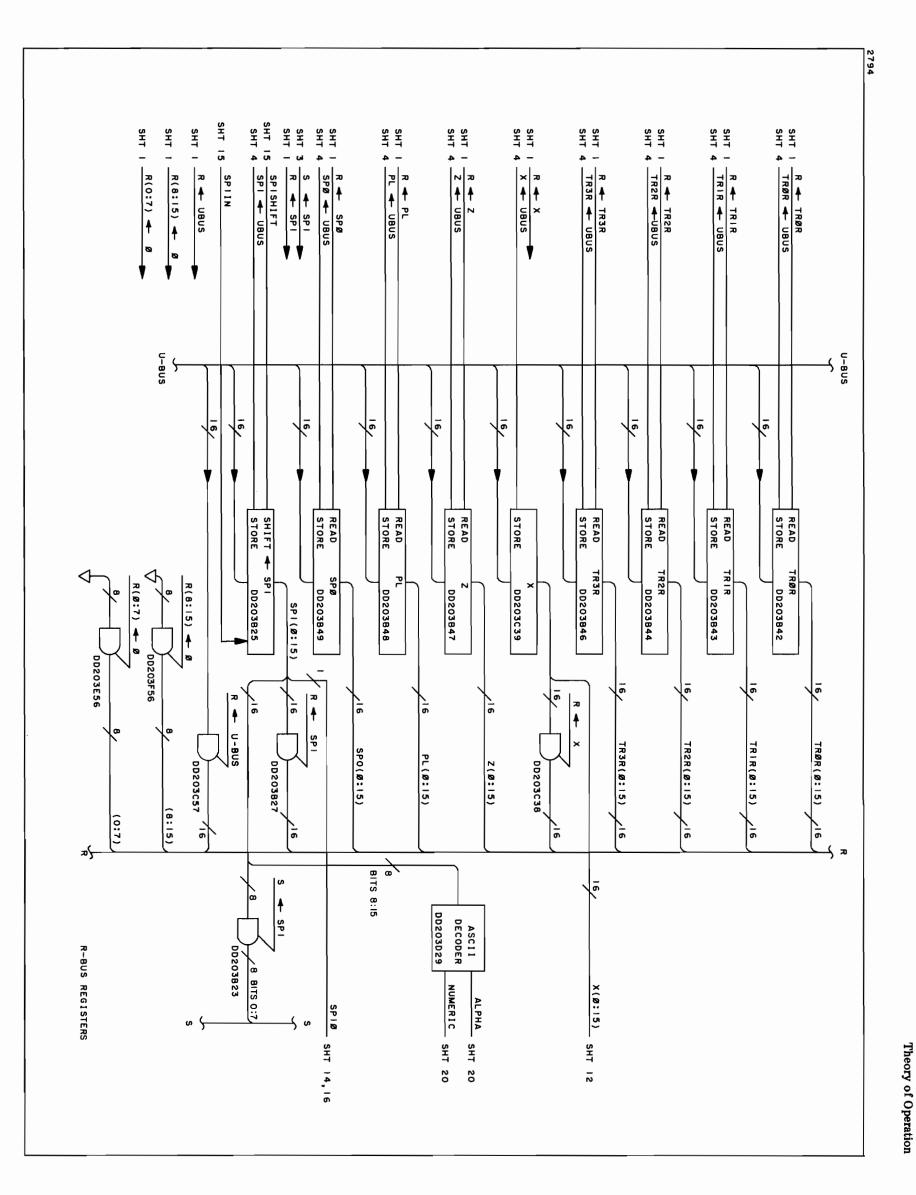

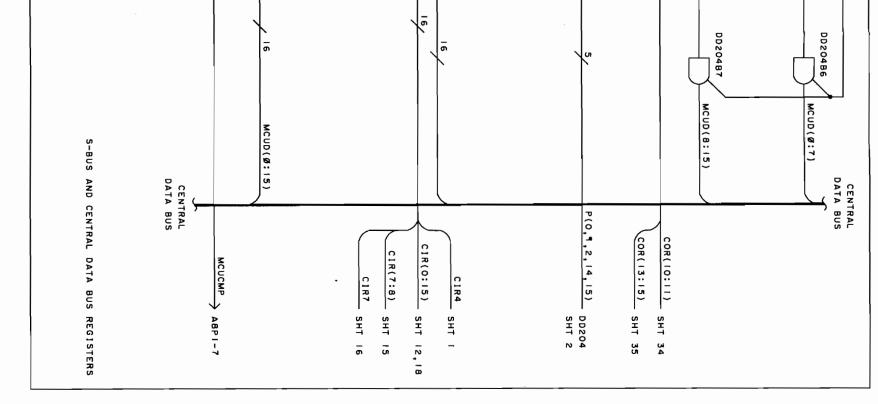

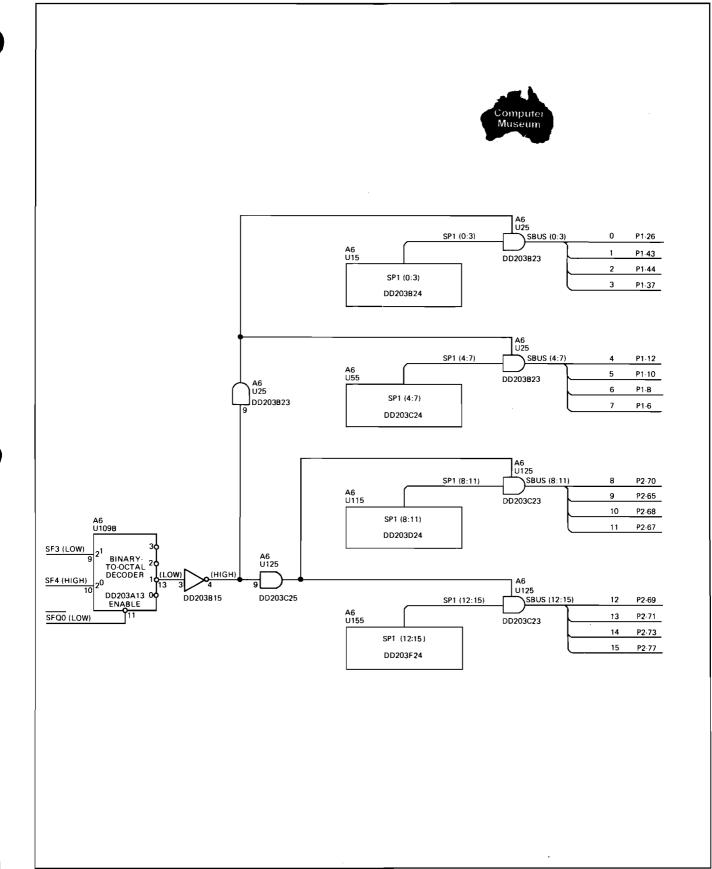

- 4) DD Set No. 203. R-Bus PCA, part no. 30001-60004.

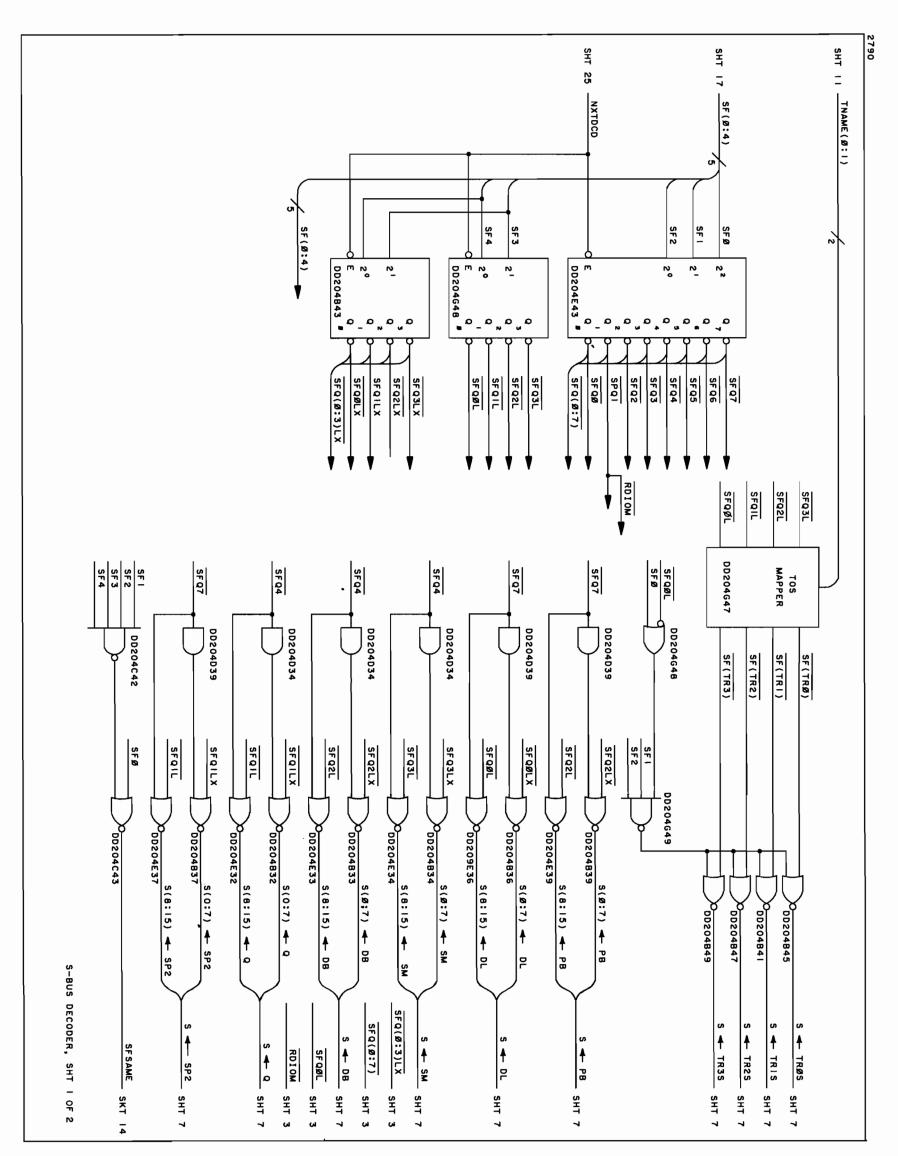

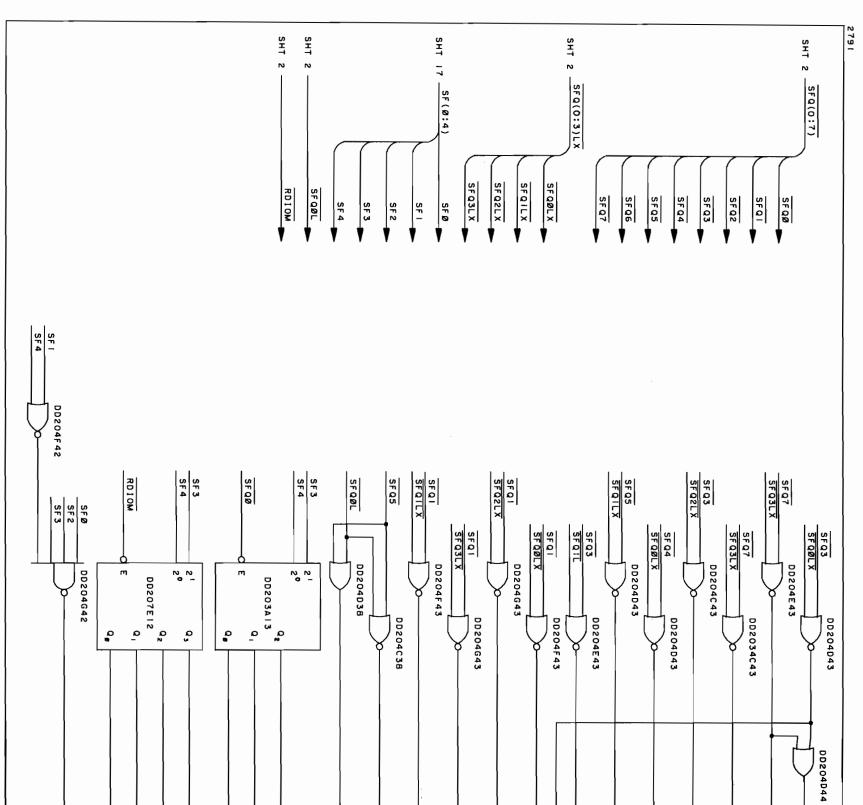

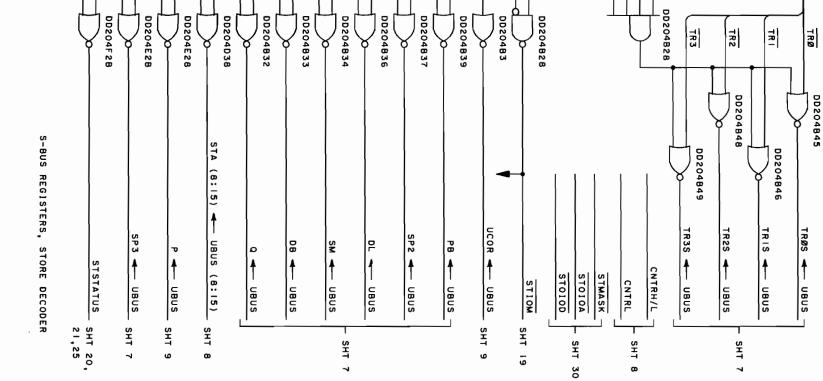

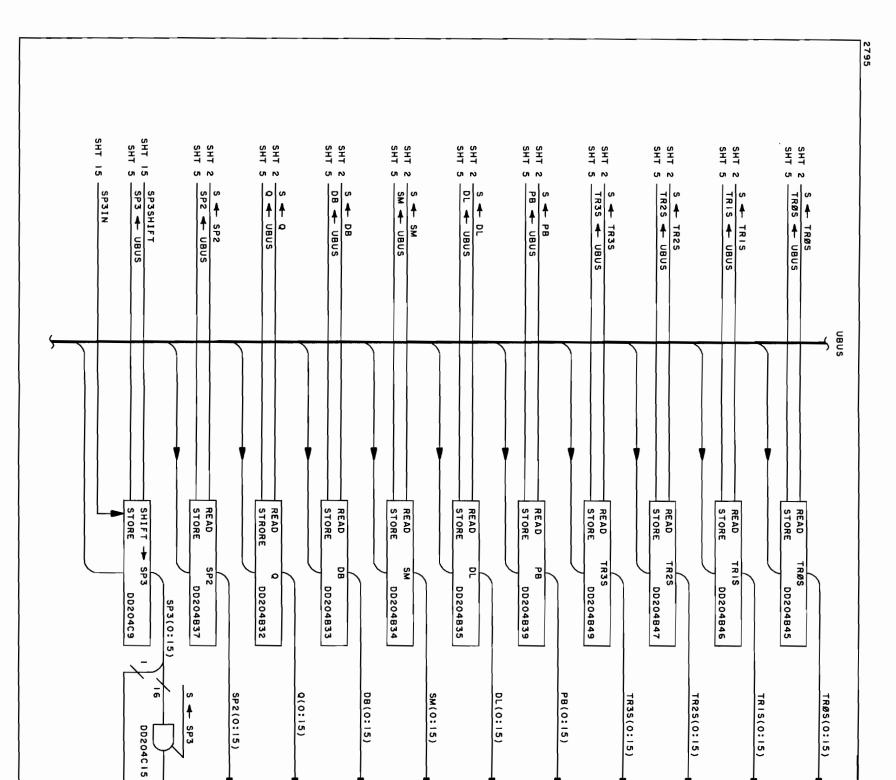

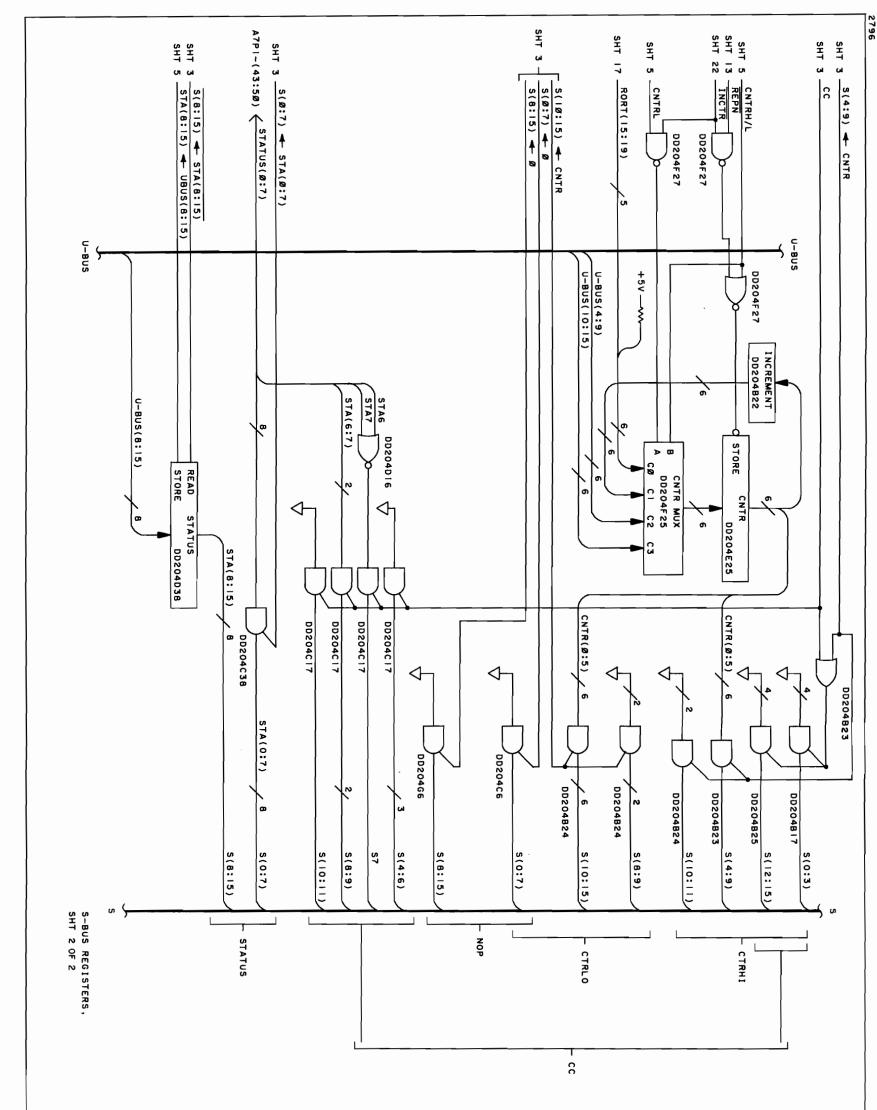

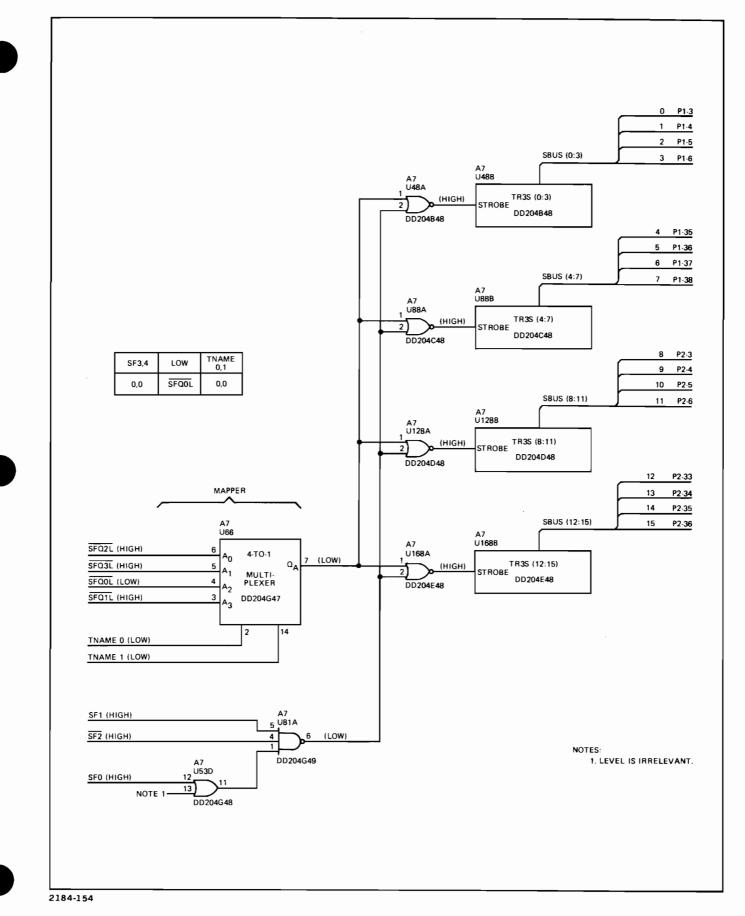

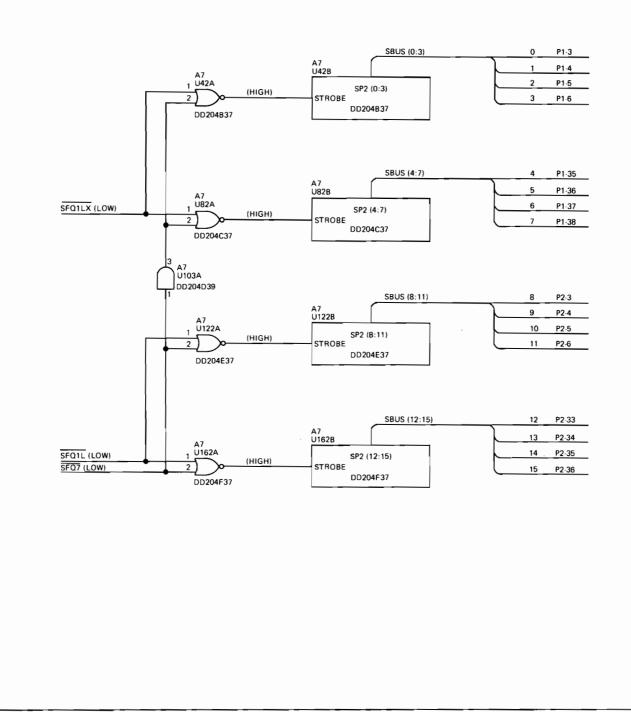

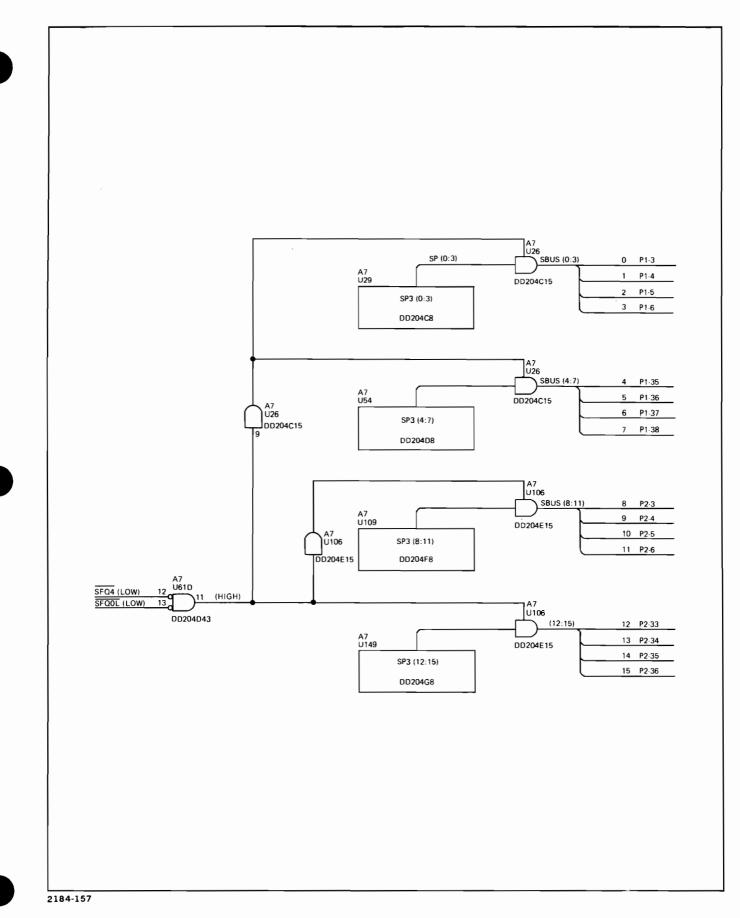

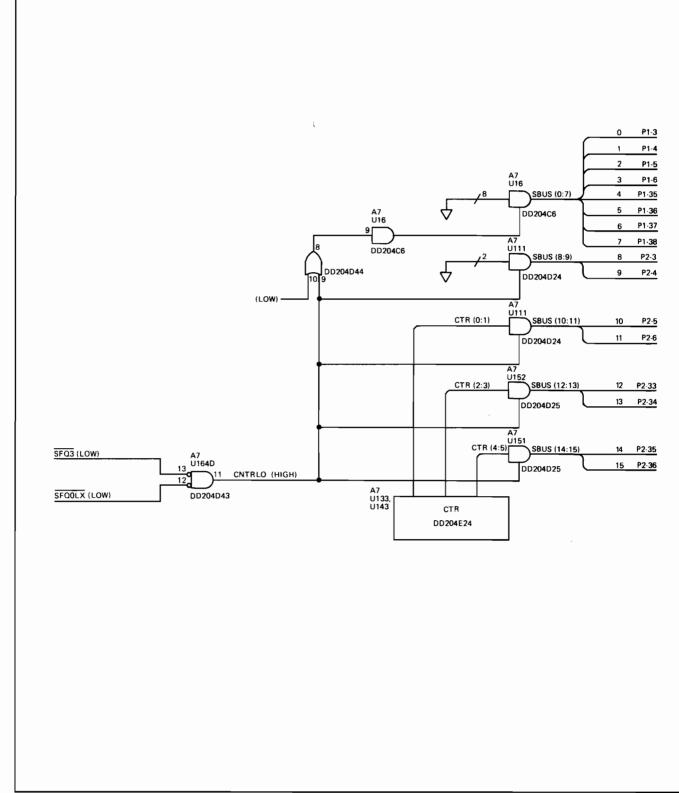

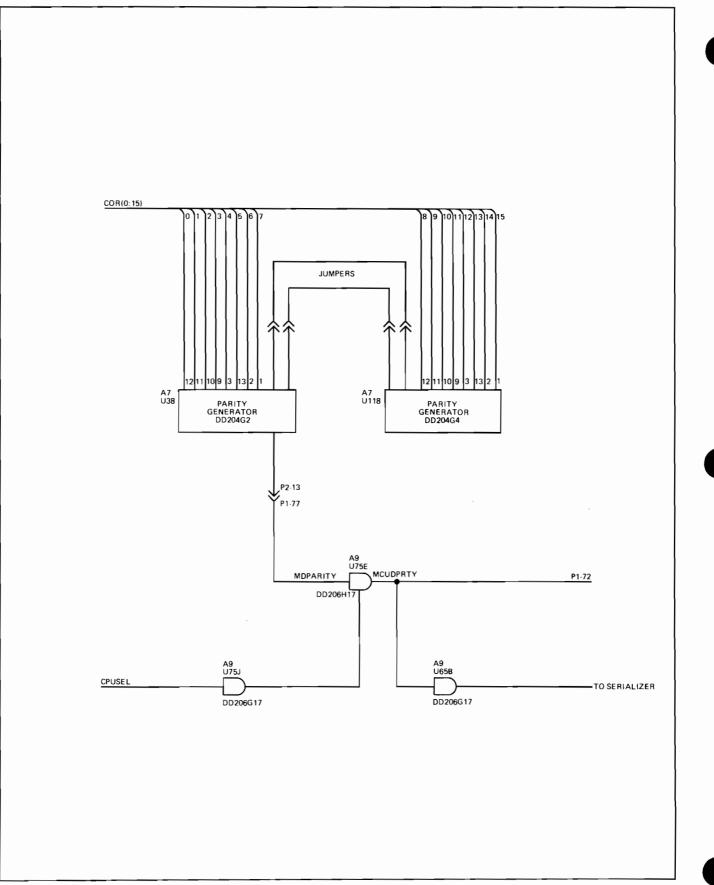

- 5) DD Set No. 204. S-Bus PCA, part no. 30001-60005.

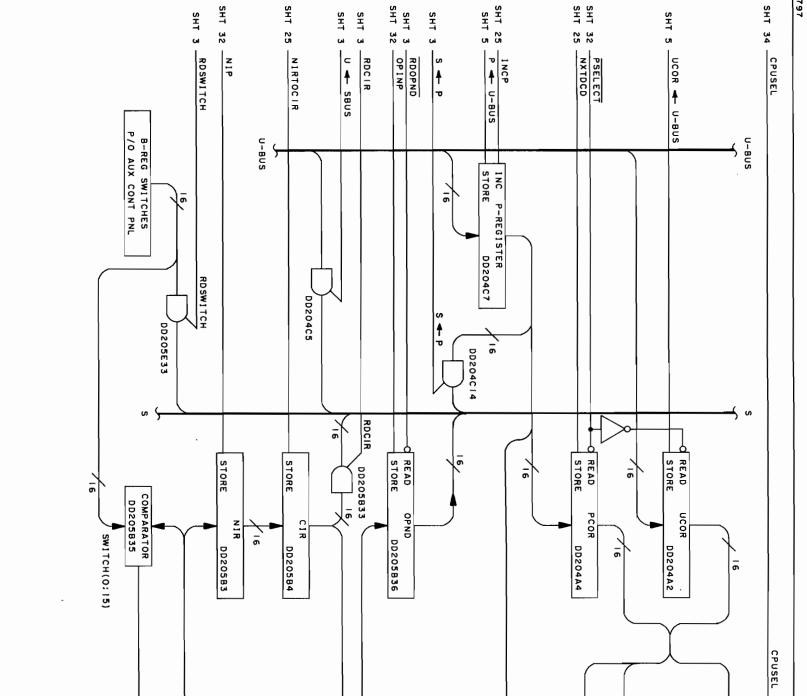

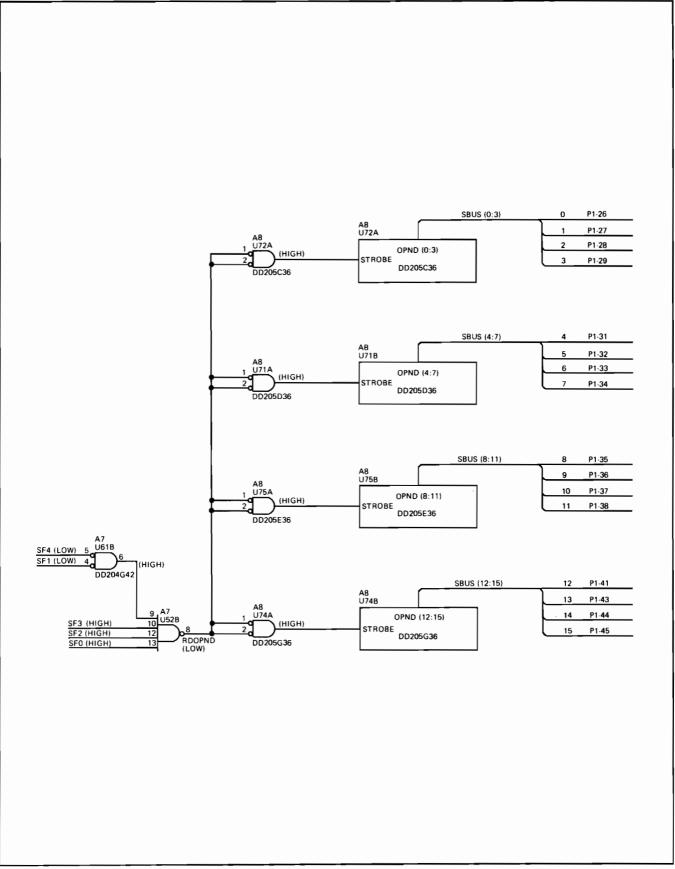

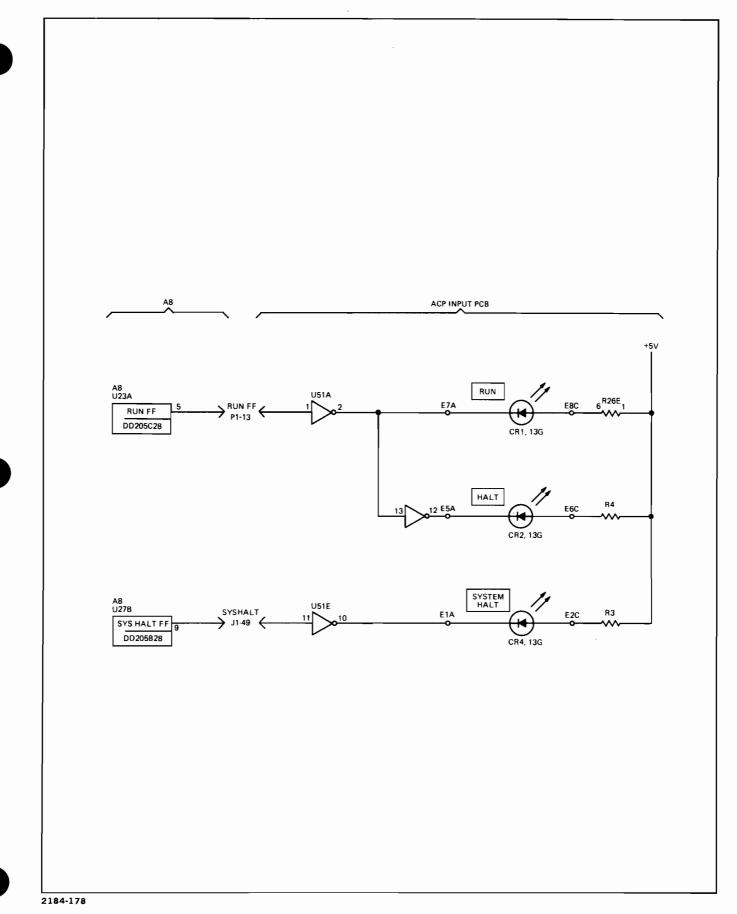

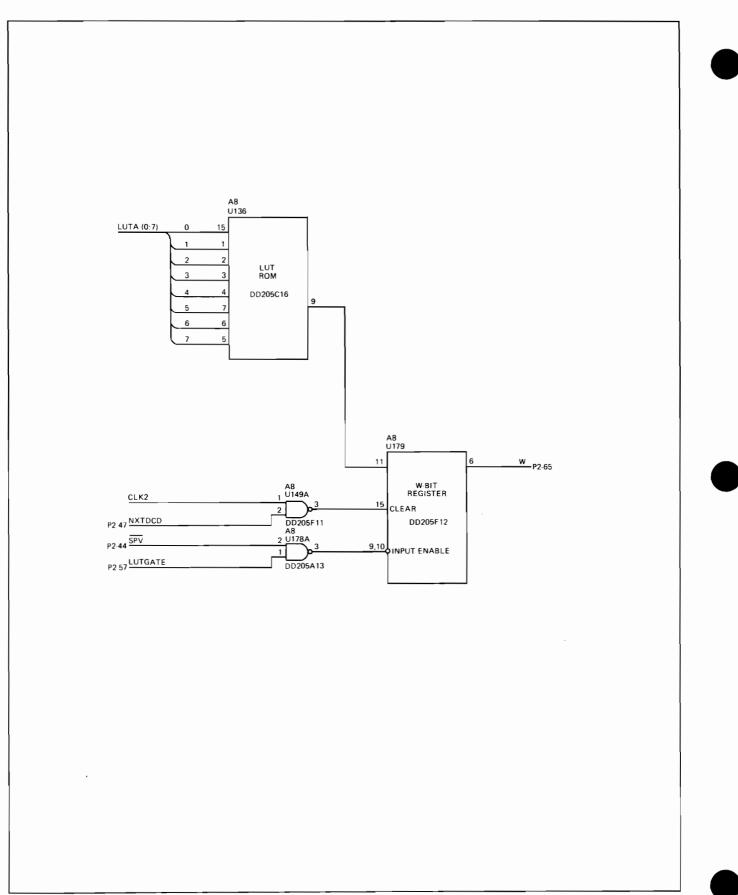

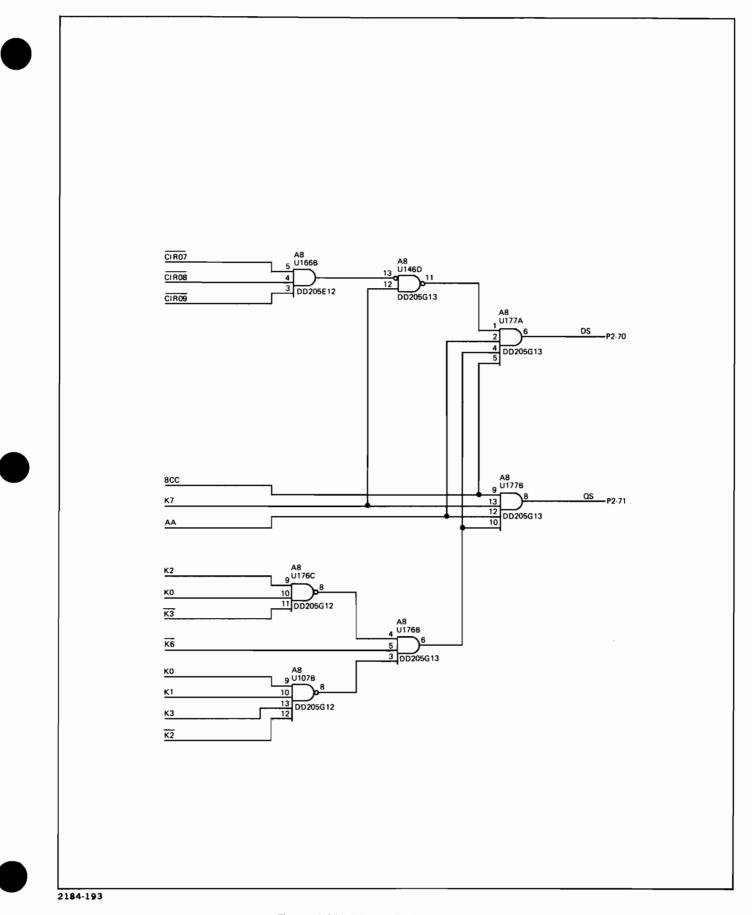

- 6) DD Set No. 205. Current Instruction Register PCA, part no. 30001-60006.

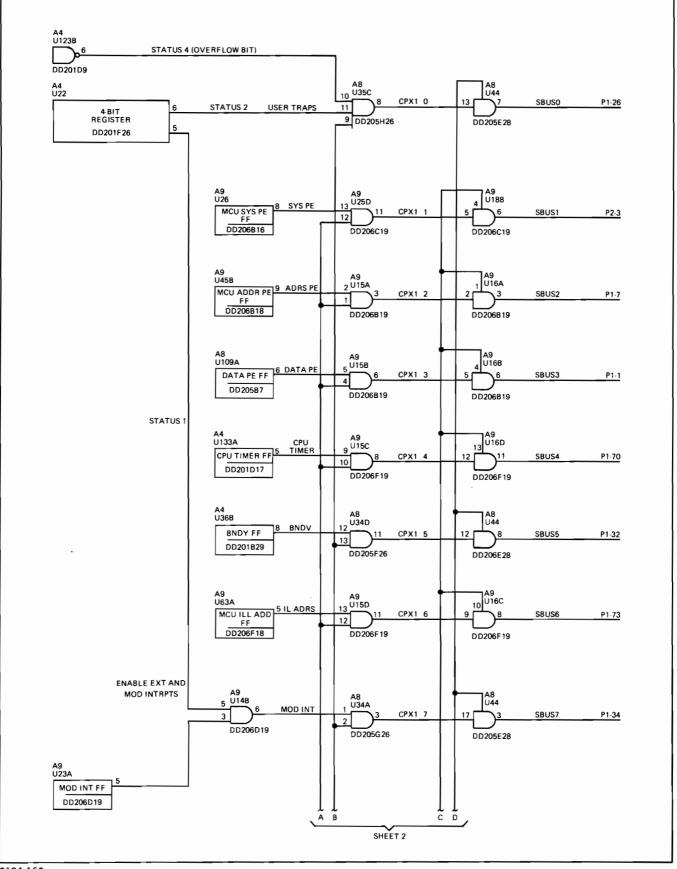

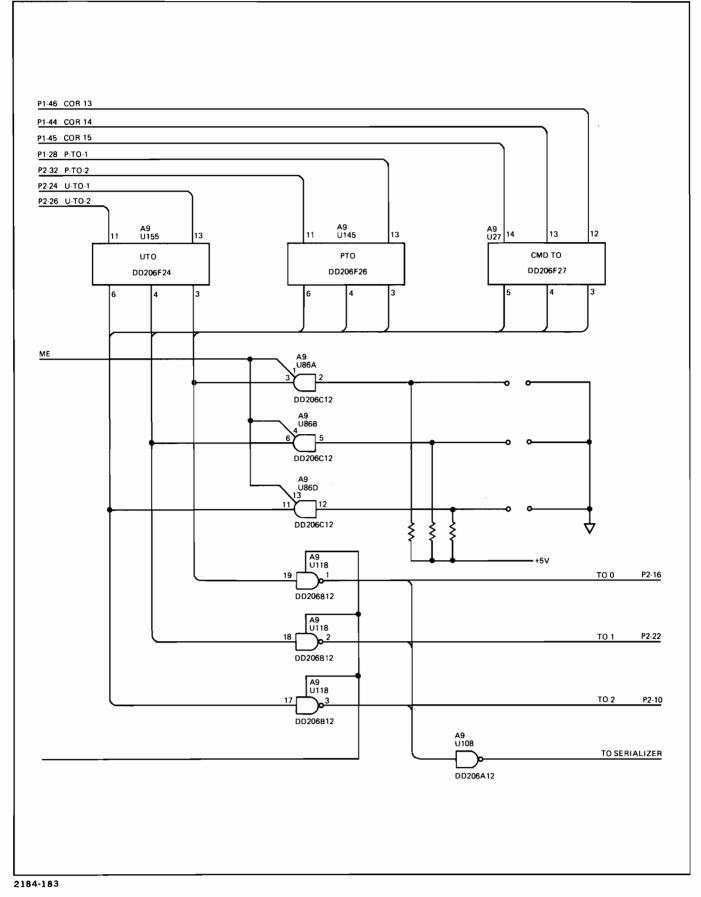

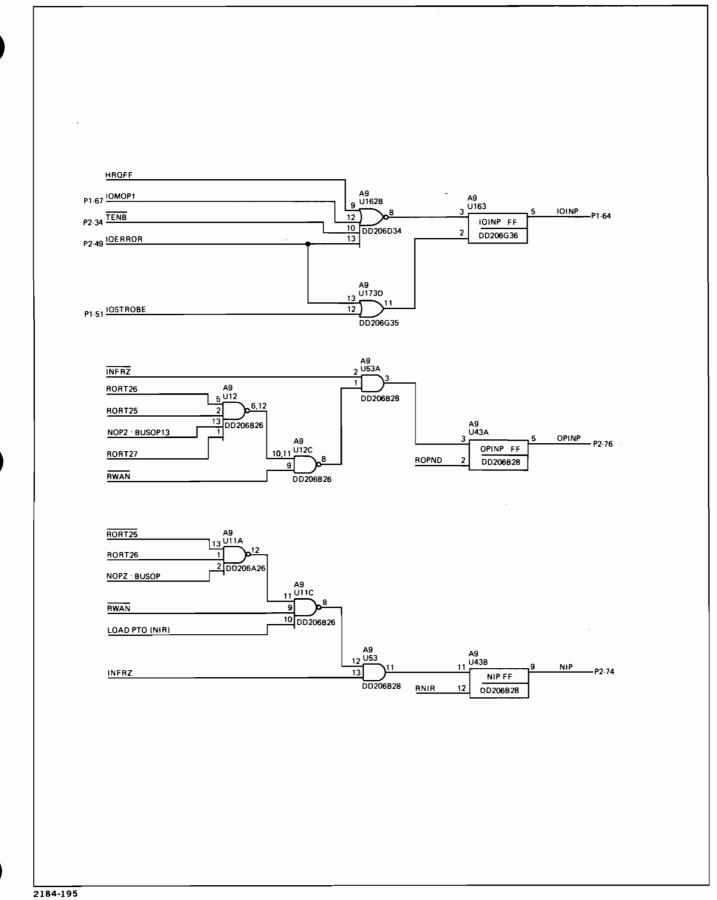

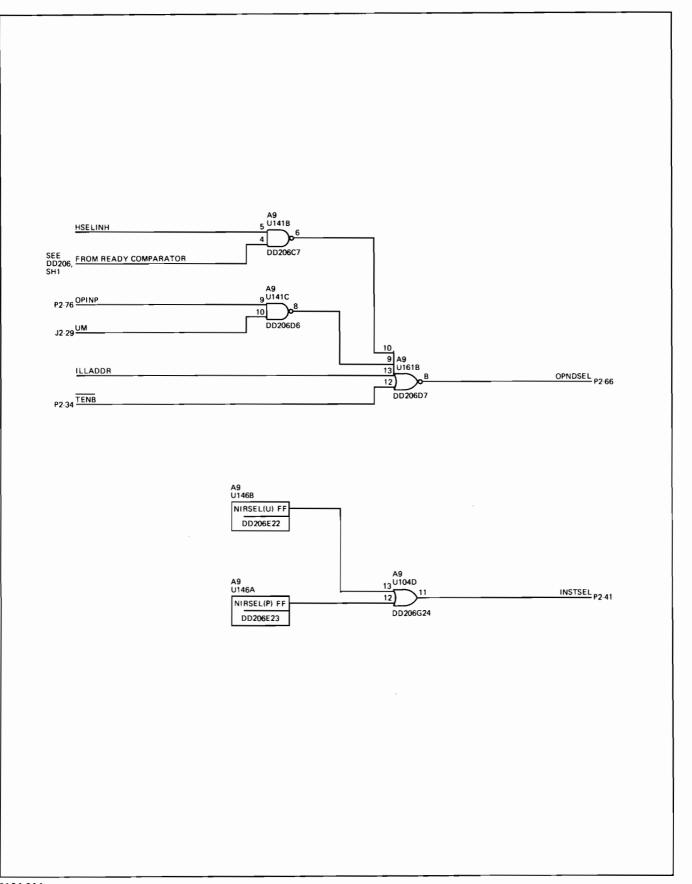

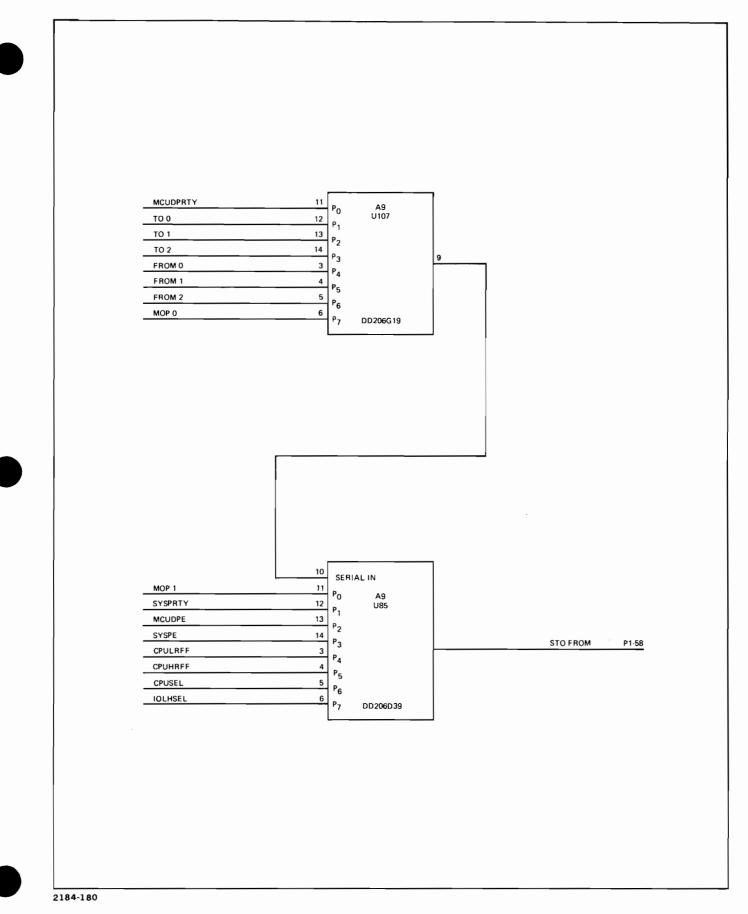

- 7) DD Set No. 206. Module Control Unit PCA, part no. 30001-60007.

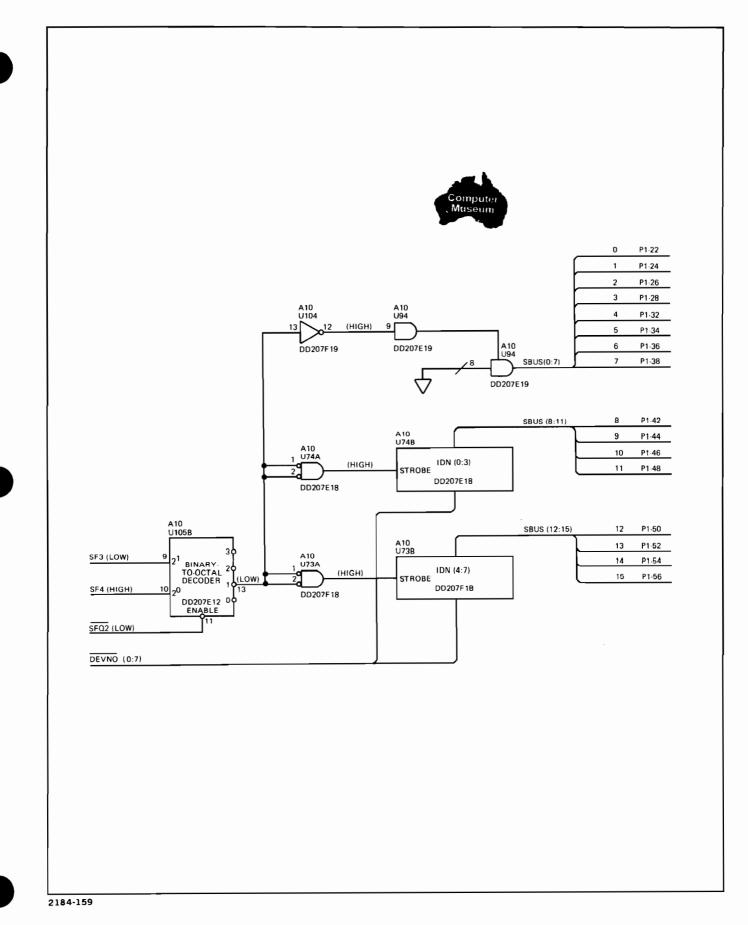

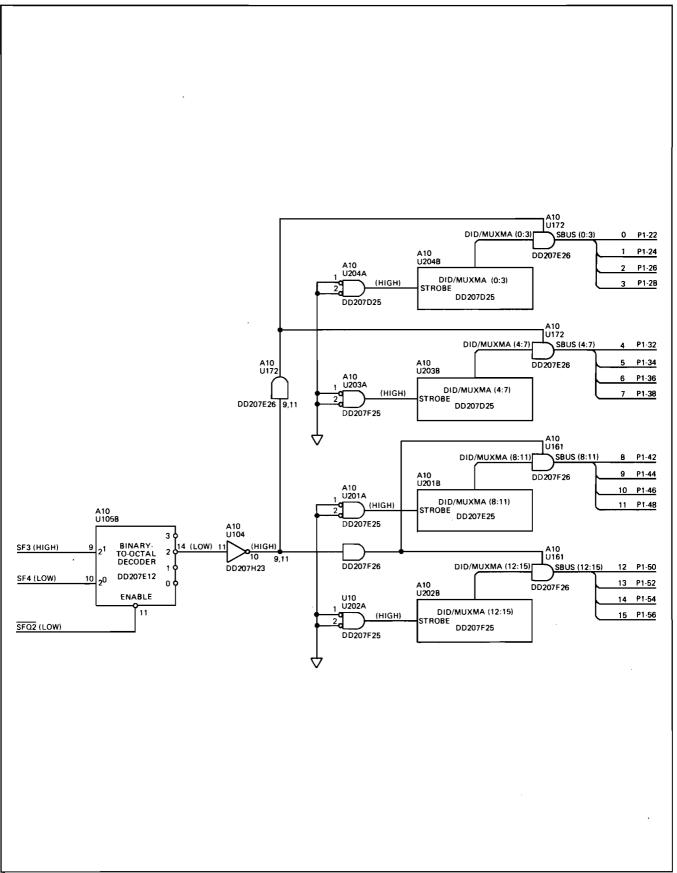

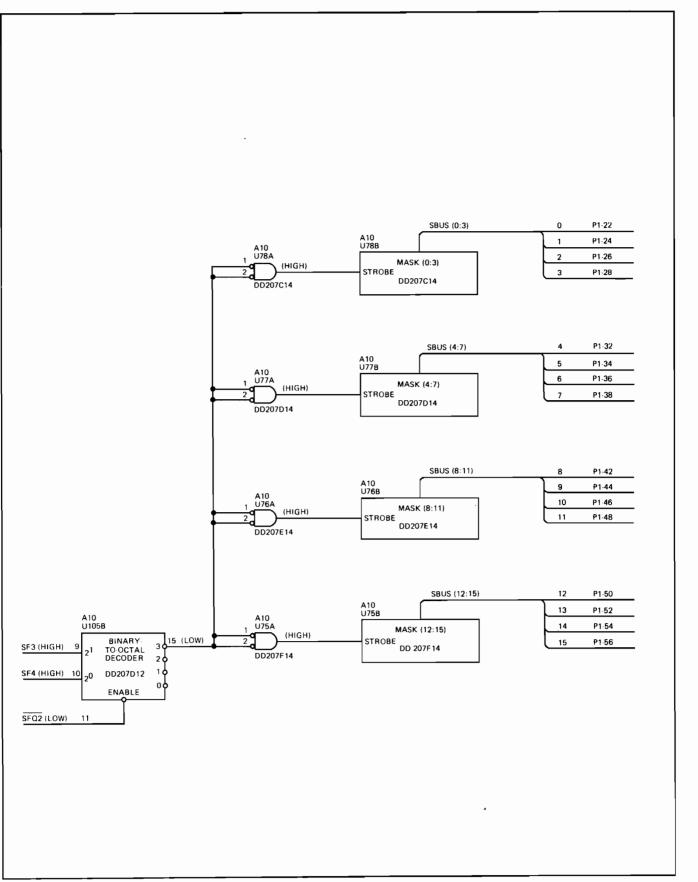

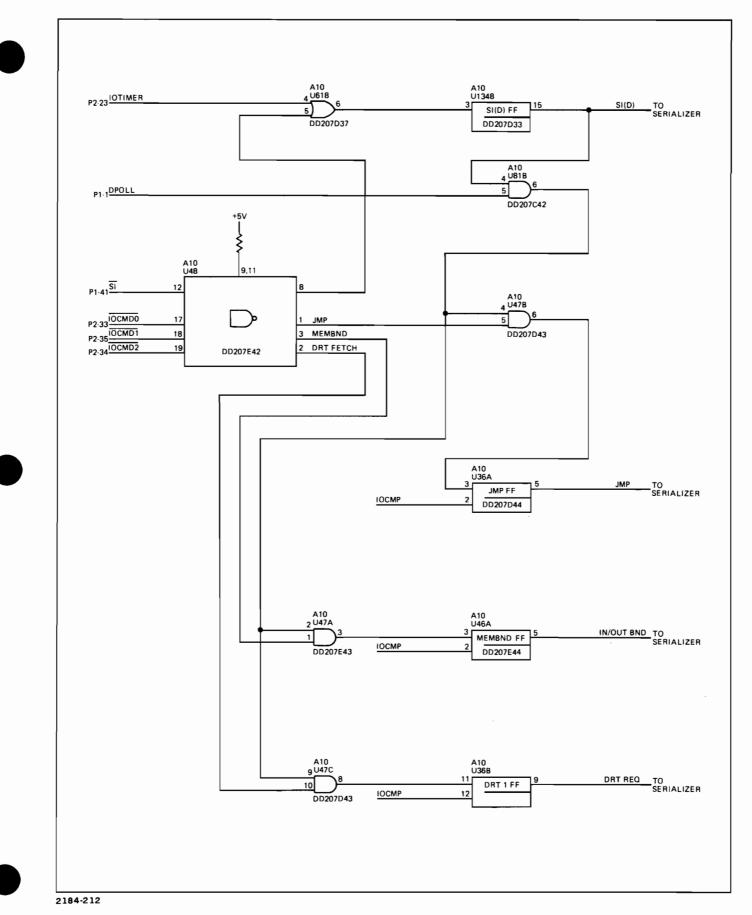

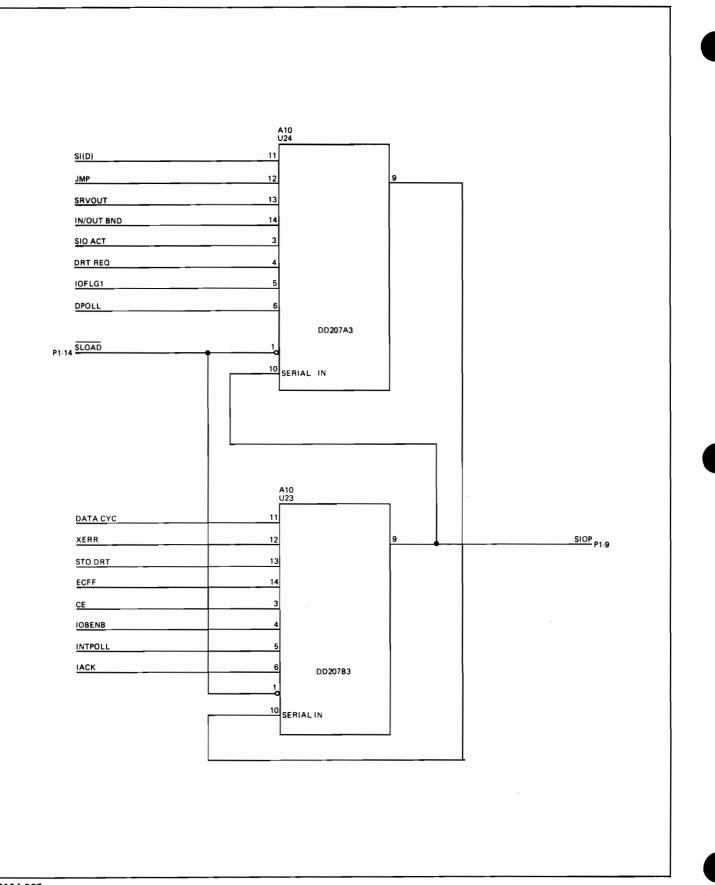

- 8) DD Set No. 207. Input/Output Processor PCA, part no. 30001-60008.

- 9) DD Set No. 208. Central Data Bus Terminator PCA, part no. 30001-60009.

- 10) DD Set No. 209. Input/Output Processor Bus Terminator PCA, part no. 30001-60016.

- 11) DD Set No. 210. Power Bus Terminator PCA, part no. 30001-60021.

- c. HP 3000 Computer System Illustrated Parts Breakdown (IPB) Manual, part no. 03000-90021.

- d. HP 3000 Manual of Stand-Alone Diagnostics, Stand-Alone HP 30001A CPU Diagnostic, part no. 03000-90027.

- e. HP 3000 Computer System Diagnostic Monitor, part no. 03000-90016.

- f. CPU Microprogram Listing Manual, part no. 03000-90022.

- g. CPU Microdiagnostic Listings, part no. 32300-90001A, 32300-90002A, 32300-90003A, 32300-90004A, and 32300-90005A.

- h. HP 3000 System Support Log.

- i. HP 30350A Auxiliary Control Panel Maintenance Manual, part no. 30350-90002 and Operator's Guide, part no. 30350-90001.

- j. HP 30035A Multiplexer Channel Maintenance Manual, part no. 30035-90001.

- k. HP 30005A/30006A Memory Subsystem Maintenance Manual, part no. 30005-90001.

- I. HP 30310A Power Supply Maintenance Manual, part no. 30310-90003.

## CONTENTS

| Secti | on                             |                                                                                                        | Pages  |

|-------|--------------------------------|--------------------------------------------------------------------------------------------------------|--------|

| I     | GENER                          | AL INFORMATION                                                                                         |        |

| •     | 1.1.                           | Introduction $\ldots$ | . 1-1  |

|       | 1-3.                           | General Description                                                                                    |        |

|       | 1-5.                           | Central Processor Unit                                                                                 | •      |

|       | 1- <b>0</b> .<br>1- <b>7</b> . |                                                                                                        | •      |

|       | 1-10.                          |                                                                                                        |        |

|       | 1-10.<br>1-12.                 | Equipment Description                                                                                  |        |

|       | 1-12.                          |                                                                                                        | • = -  |

|       | 1-15.                          |                                                                                                        |        |

|       | 1-17.                          |                                                                                                        | . 1-2  |

| II    |                                | TING PARAMETERS                                                                                        | _      |

|       | <b>2-1</b> .                   | Introduction                                                                                           |        |

|       | 2-3.                           | HP 3000 Computer System Instructions                                                                   |        |

|       | 2-6.                           | Stack Op Instructions                                                                                  |        |

| •     | 2-8.                           | Shift Instructions                                                                                     | . 2-1  |

|       | 2-10.                          | Branch Instructions                                                                                    | . 2-1  |

|       | 2-12.                          | Bit Test Instructions                                                                                  | . 2-1  |

|       | 2-14.                          | Move Instructions                                                                                      |        |

|       | 2-16.                          | Special Instructions                                                                                   |        |

|       | 2-18.                          | Immediate Instructions                                                                                 |        |

|       | 2-20.                          | Field Instructions                                                                                     | . 2-7  |

|       | 2-22.                          | Register Control Instructions                                                                          | 2-7    |

|       | 2-24.                          | Program Control Instructions                                                                           |        |

|       | 2-26.                          | I/O and Interrupt Instructions                                                                         |        |

|       | 2-20.<br>2-28.                 | Loop Control Instructions                                                                              |        |

|       | 2-20.<br>2-30.                 | Memory Address Instructions                                                                            |        |

|       | 2-30.<br>2-32.                 | Microinstruction Coding                                                                                | • = -  |

|       | 2-32.<br>2-35.                 | Format 1                                                                                               |        |

|       | 2-35.<br>2-37.                 | Format 2                                                                                               |        |

|       | 2-37.<br>2-39.                 | Format 2                                                                                               | . 2-10 |

|       |                                |                                                                                                        |        |

|       | 2-42.                          | Format 4                                                                                               |        |

|       | 2-44.                          | Format 5                                                                                               | . 2-12 |

| III   |                                | RY OF OPERATION                                                                                        |        |

|       | 3-1.                           | Introduction                                                                                           |        |

|       | 3-3.                           | System-Level Description                                                                               | . 3-1  |

|       | 3-8.                           | Block-Level Description                                                                                |        |

|       | 3-11.                          | Next Instruction Register                                                                              | . 3-3  |

|       | 3-13.                          | Current Instruction Register                                                                           |        |

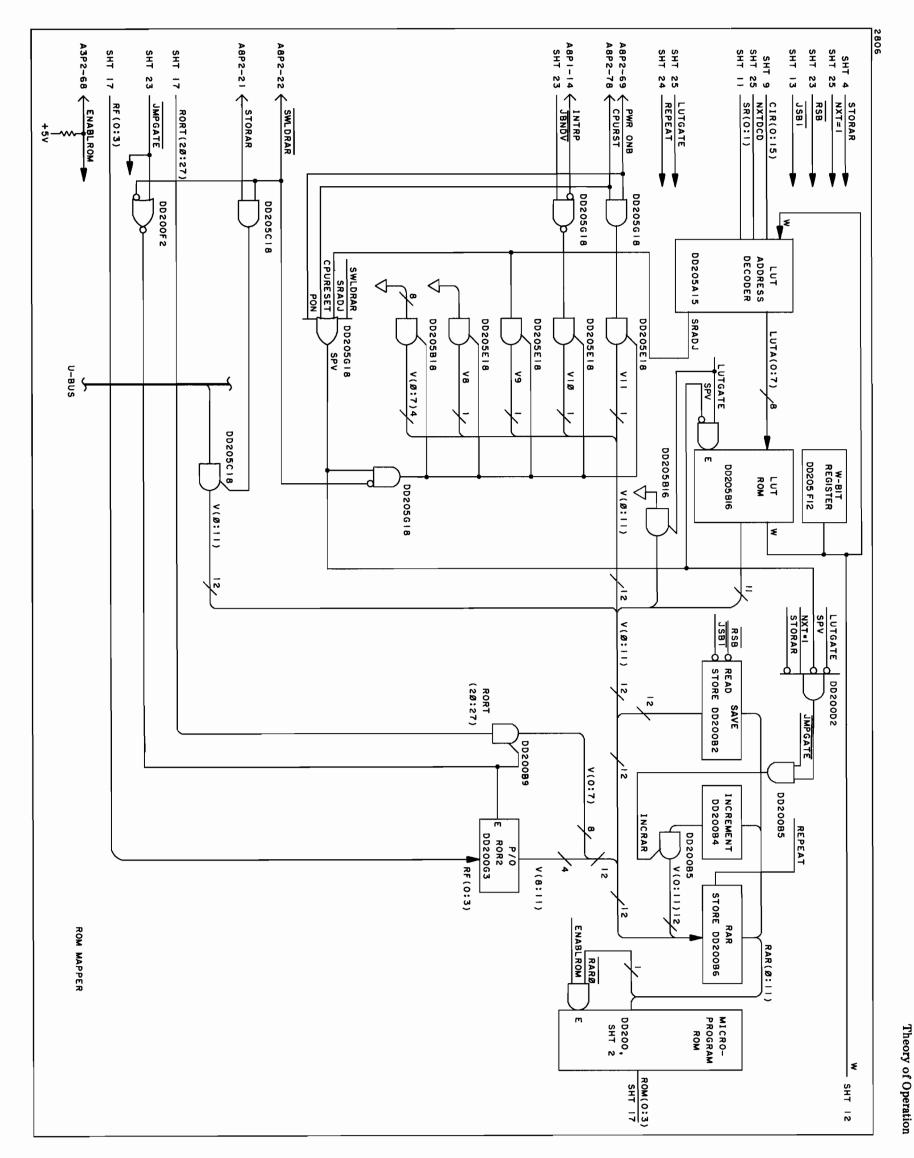

|       | 3-15.                          | <b>ROM Mapper</b>                                                                                      | . 3-3  |

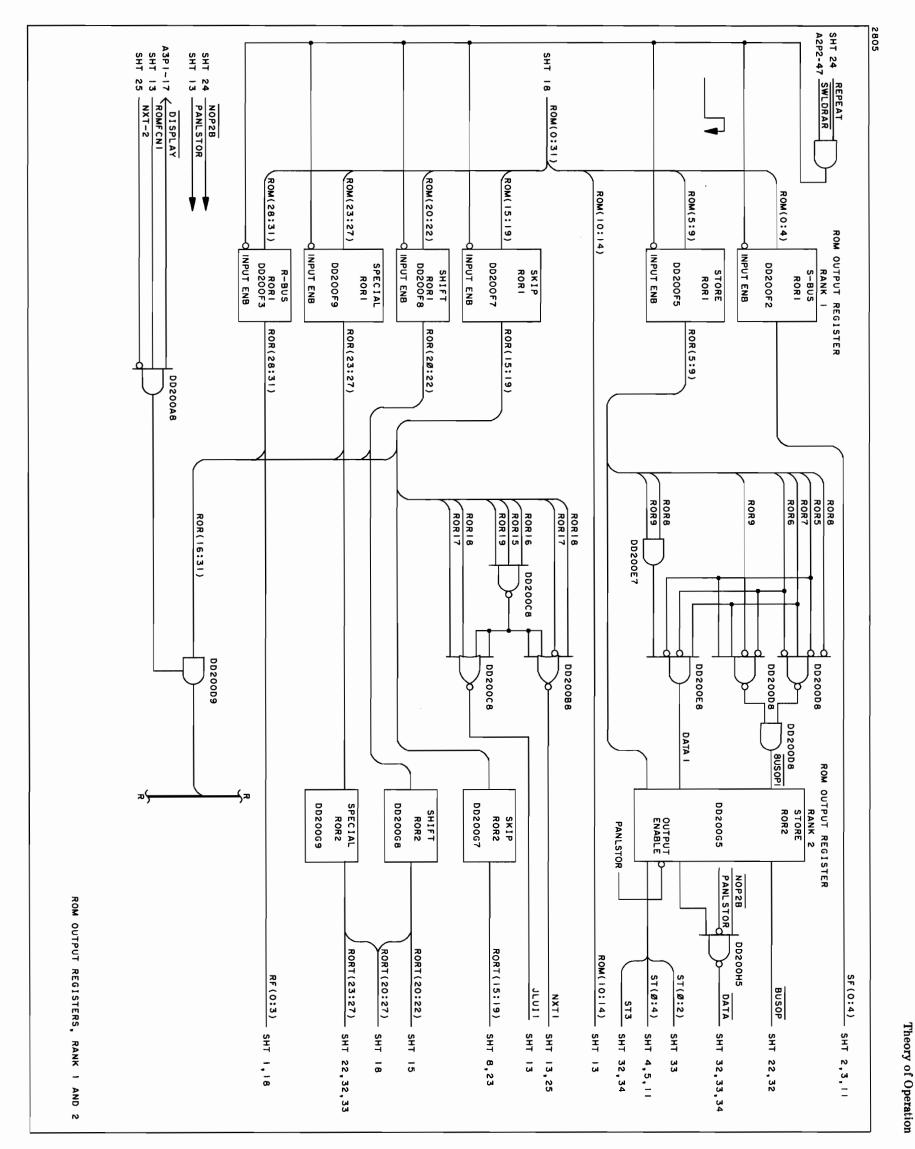

|       | 3-25.                          | ROM Output Register Rank 1                                                                             | . 3-4  |

|       | 3-28.                          | ROM Output Register Rank 2                                                                             |        |

|       | 3-30.                          | Microinstruction Field Decoders                                                                        |        |

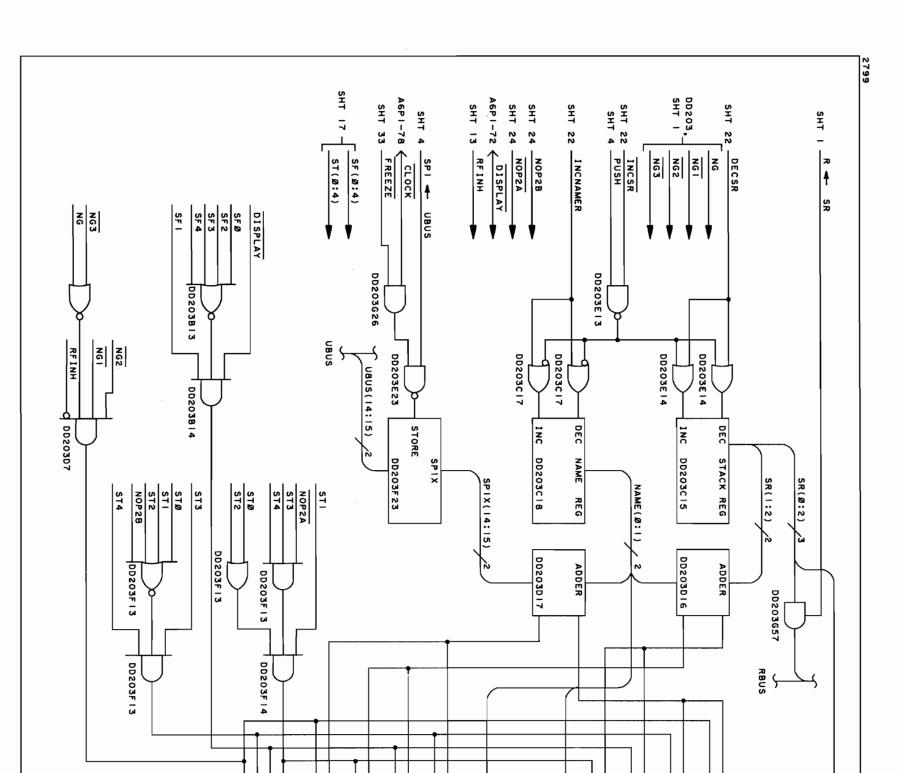

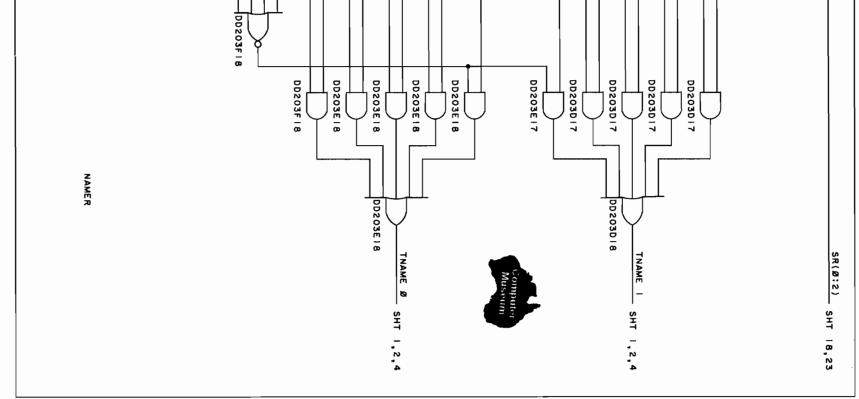

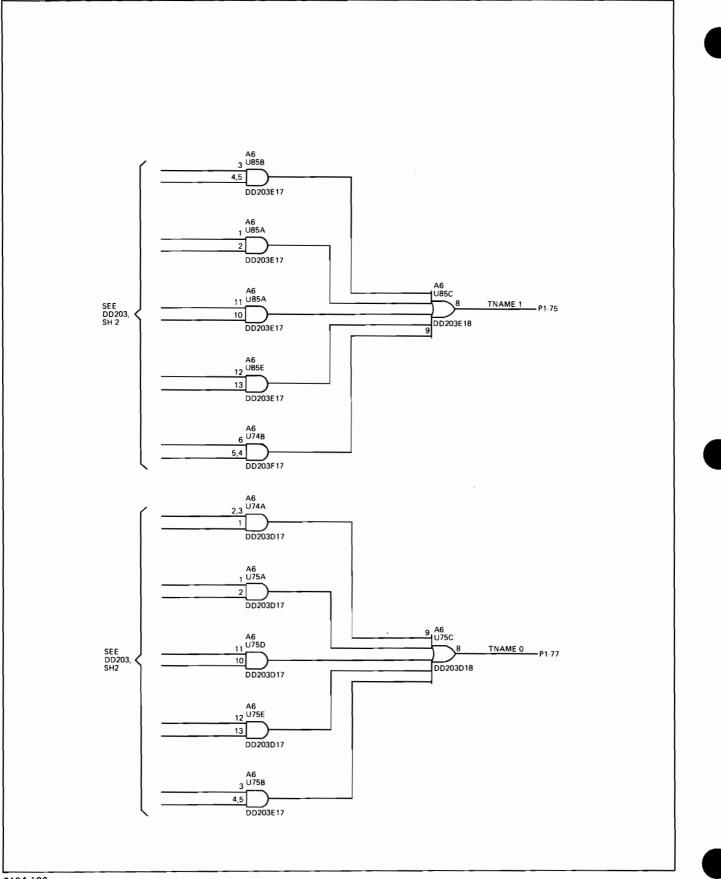

|       | 3-40.                          | Name Register                                                                                          |        |

|       | 3-44.                          | Top-Of-Stack Mappers                                                                                   |        |

|       | 3-46.                          | Top-Of-Stack Registers                                                                                 |        |

|       | 3-48.                          | Index Register                                                                                         |        |

|       | 3-50.                          | Stack Limit Register.                                                                                  | 3-31   |

|       | 3-52.                          | Program Limit Register                                                                                 |        |

|       | 3-52.<br>3-54.                 | Scratch Pad 0 Register                                                                                 |        |

|       | 3-54.<br>3-56.                 |                                                                                                        |        |

|       | 3-56.<br>3-58.                 | Scratch Pad 1X Register                                                                                |        |

|       |                                |                                                                                                        |        |

|       | 3-60.                          | Stack Register                                                                                         | . 3-31 |

|       | 3-62.                          | Program Base Register                                                                                  |        |

|       | 3-64.                          | Data Limit Register                                                                                    |        |

|       | 3-66.                          | Stack Memory Register                                                                                  | . 3-31 |

vii

## CONTENTS (Continued)

Section

| ion             | P                                                     | ages         |

|-----------------|-------------------------------------------------------|--------------|

| 3-68.           | Data Base Register                                    | 3-32         |

| 3-70.           | Q-Register                                            |              |

| 3-72.           | Scratch Pad 2 Register                                |              |

| 3-74.           | Scratch Pad 3 Register                                |              |

| 3-76.           | Program Counter Register                              |              |

| 3-78.           | Counter Register                                      |              |

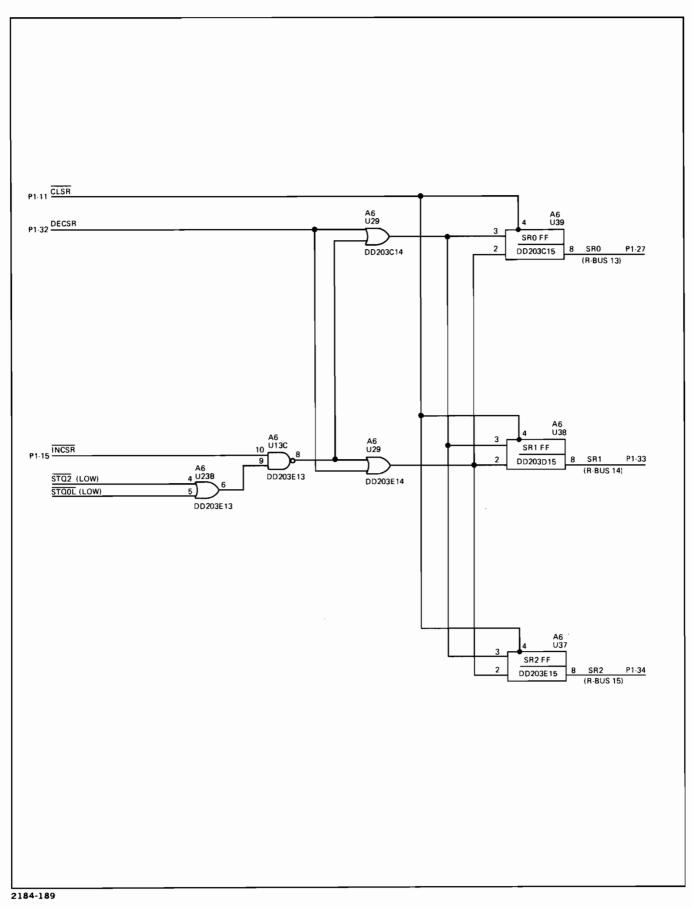

| <b>3-81</b> .   | Status Register                                       |              |

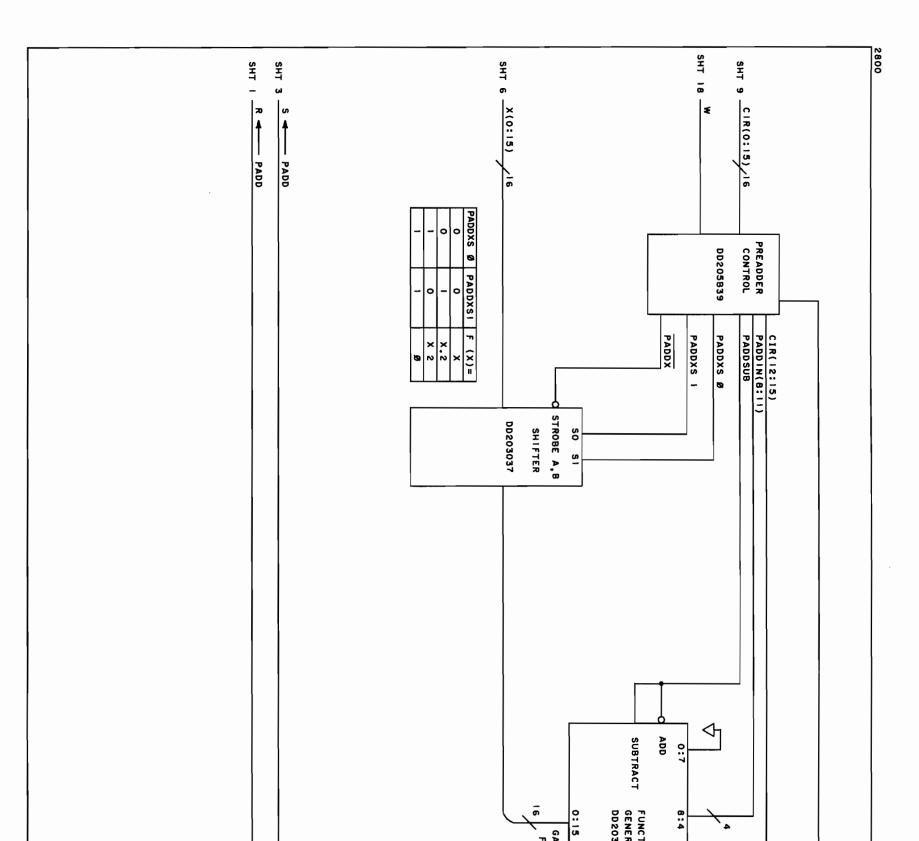

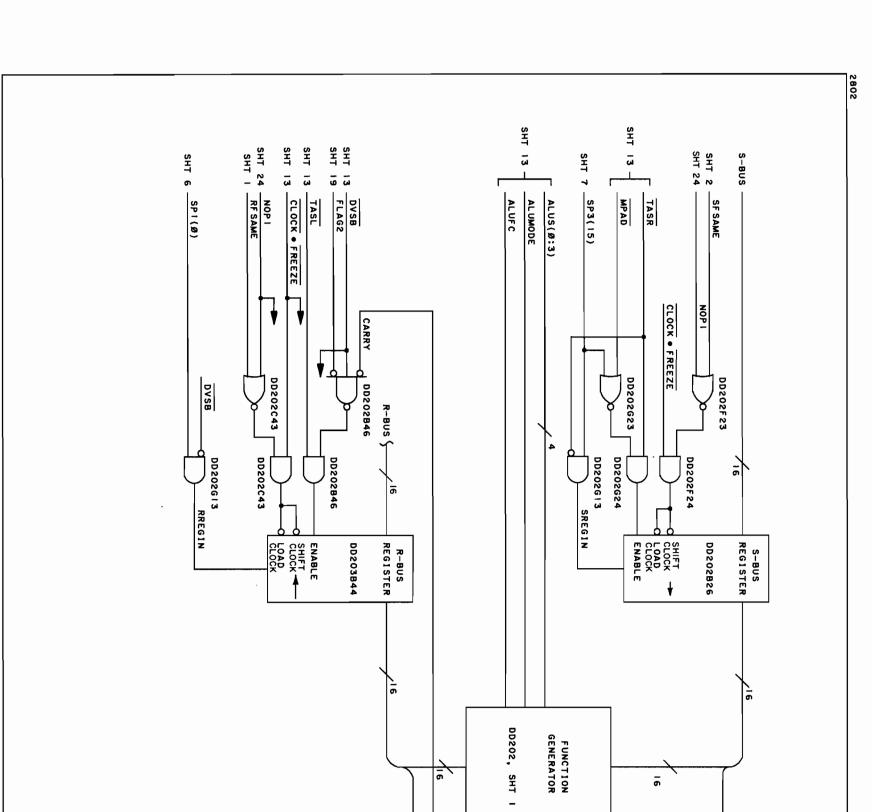

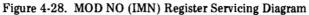

| <b>3-84</b> .   | Pre-Adder                                             |              |

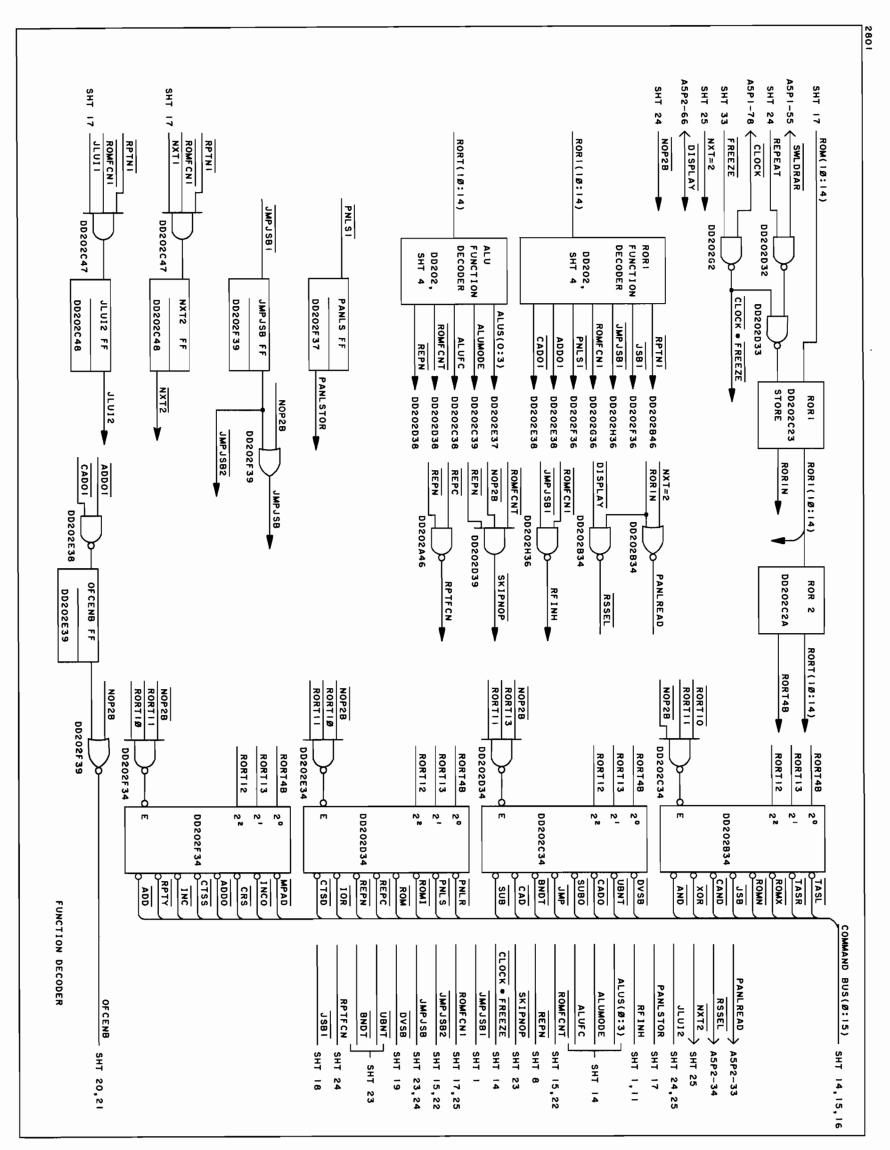

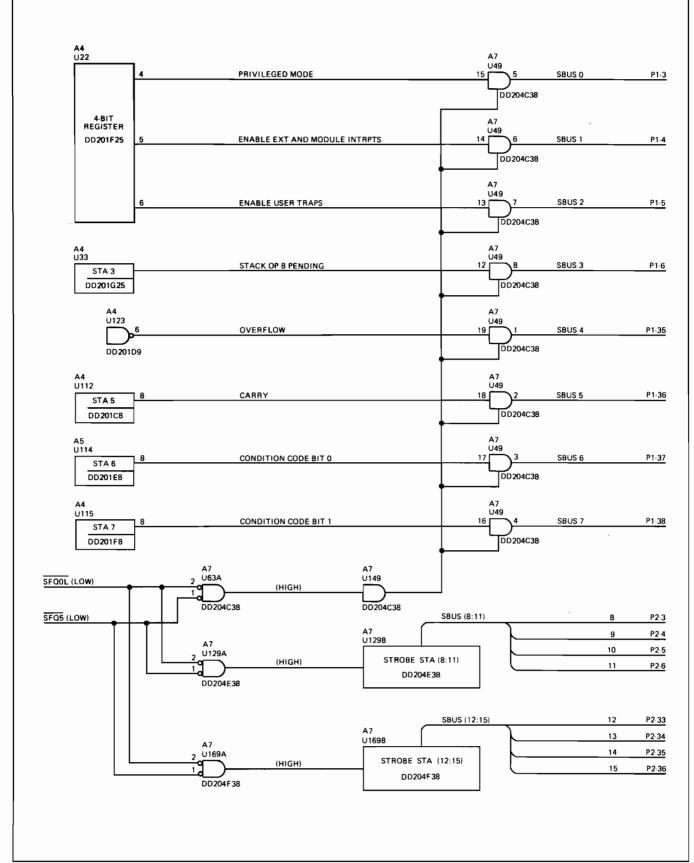

| 3-86.           | R-Bus Register                                        |              |

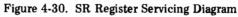

| 3-88.           | S-Bus Register                                        |              |

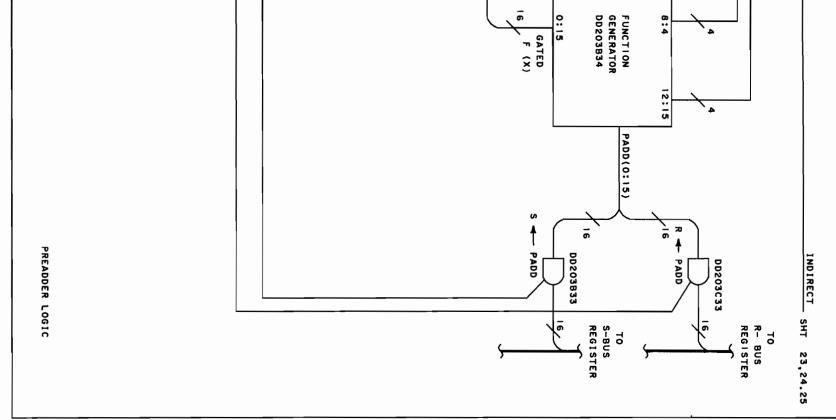

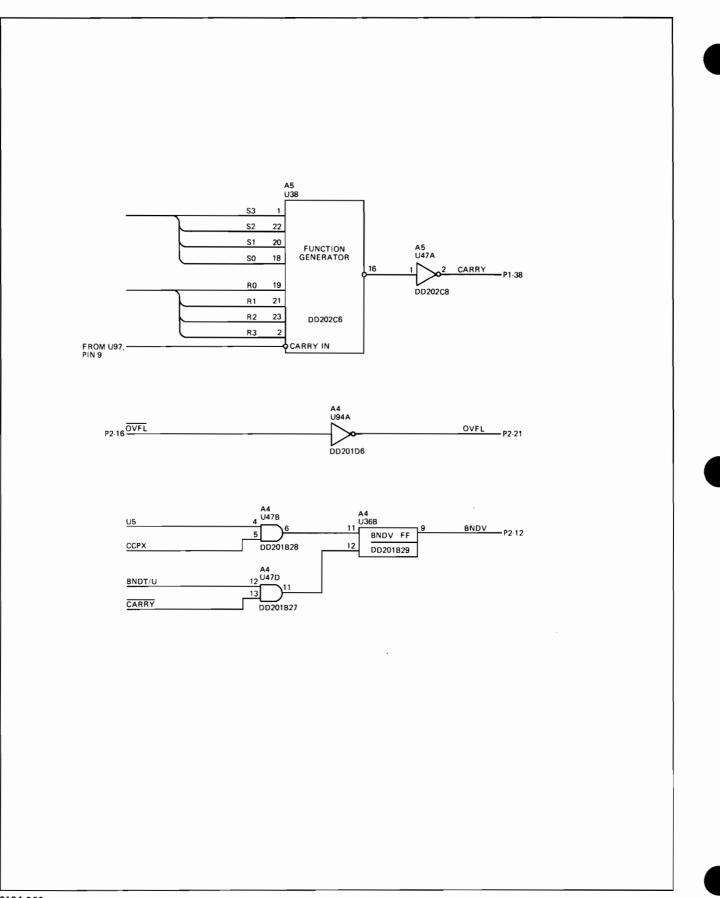

| <b>3-9</b> 0.   | ALU Function Generator                                |              |

| 3-92.           |                                                       |              |

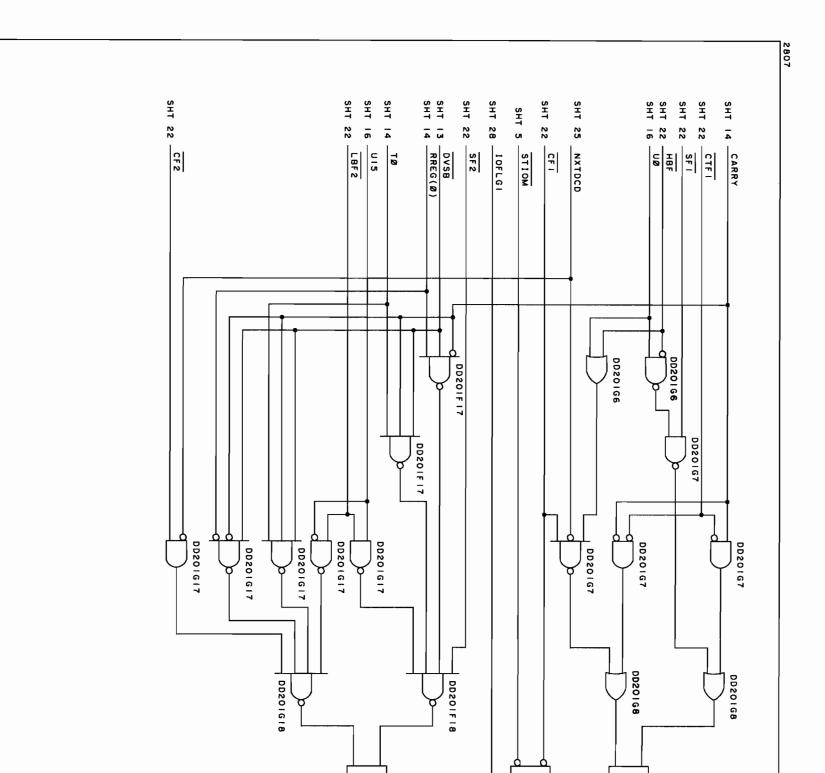

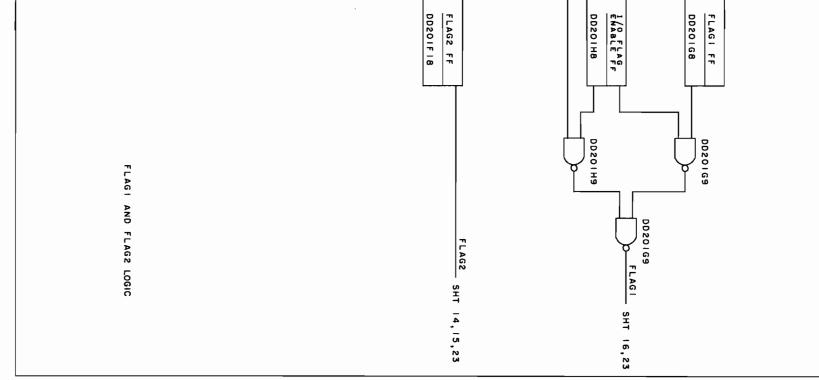

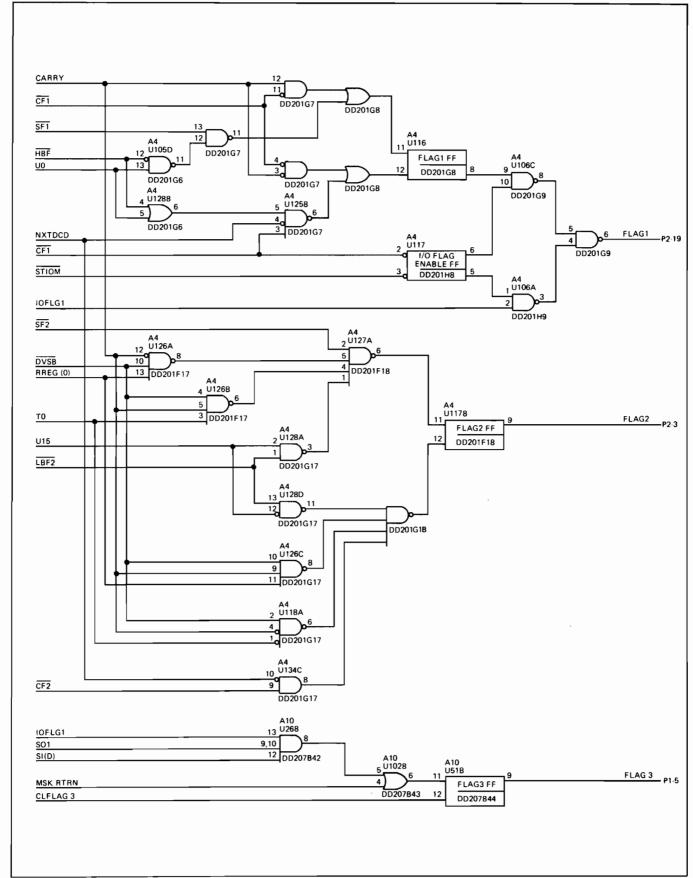

| 3-94.           | Flag 1 Register                                       |              |

| 3-94.           | Flag 2 Register                                       | 3-33<br>0 00 |

| 3-98.           |                                                       |              |

| 3-30.<br>3-100. | Mappers                                               |              |

|                 |                                                       |              |

| 3-102.          | P-CPU Output Register                                 |              |

| 3-104.          | P-Register or U-Bus Memory Operation Register         |              |

| 3-106.          | Command Memory Operation Register                     | 3-34         |

| 3-108.          | Command-To Register                                   |              |

| 3-110.          | P-To Register                                         |              |

| 3-112.          | U-To Register                                         |              |

| 3-114.          | P-To-Next Instruction Register                        |              |

| 3-116.          | U-To-Next Instruction Register                        |              |

| 3-118.          | U-To Operand Register                                 |              |

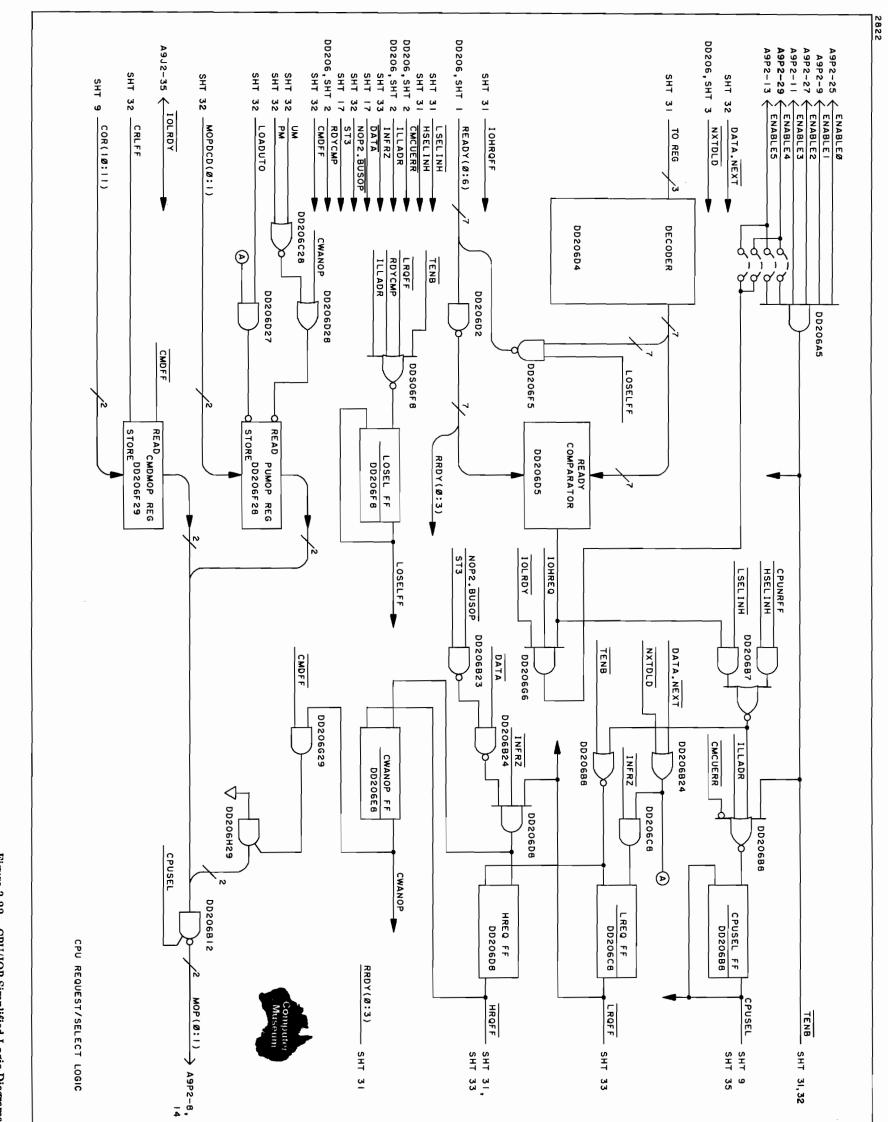

| 3-120.          | To-From Comparators                                   |              |

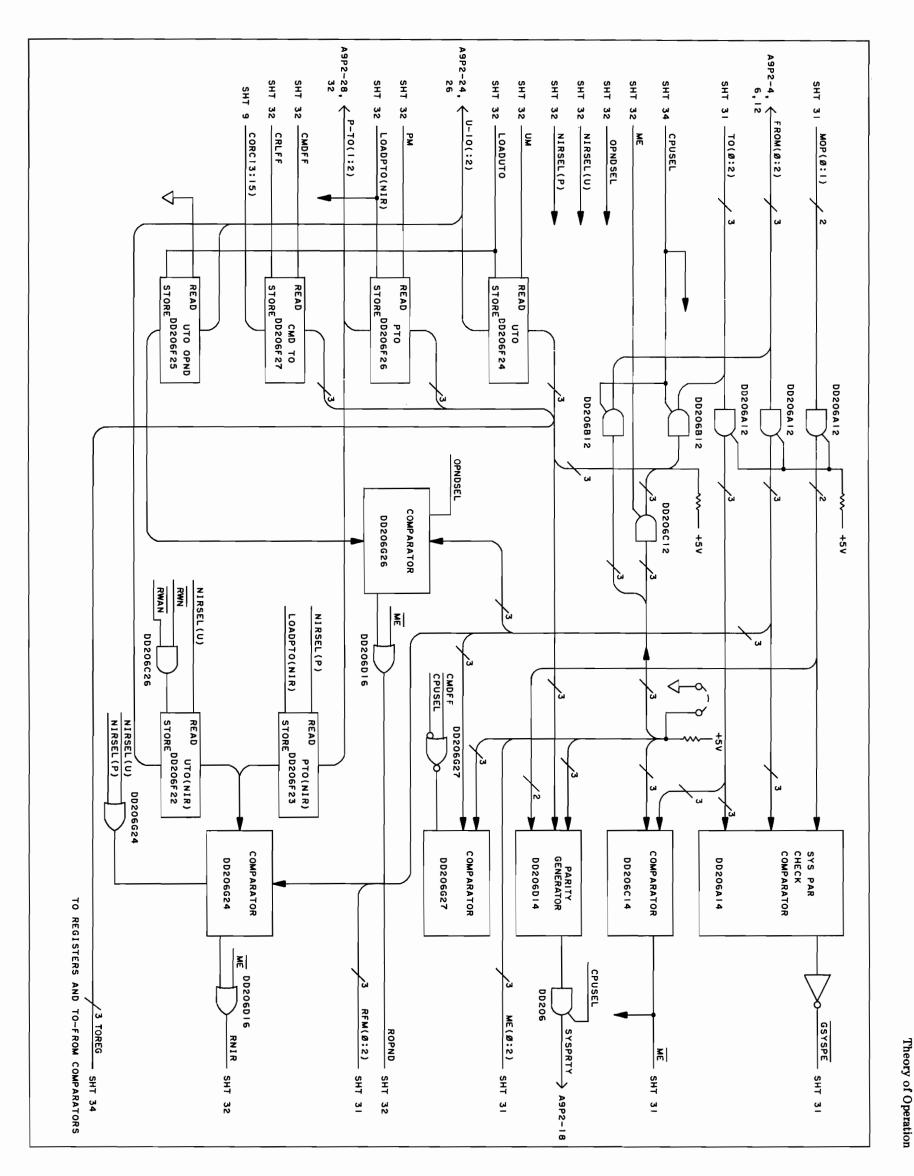

| 3-122.          | Ready Decoder and Comparator                          |              |

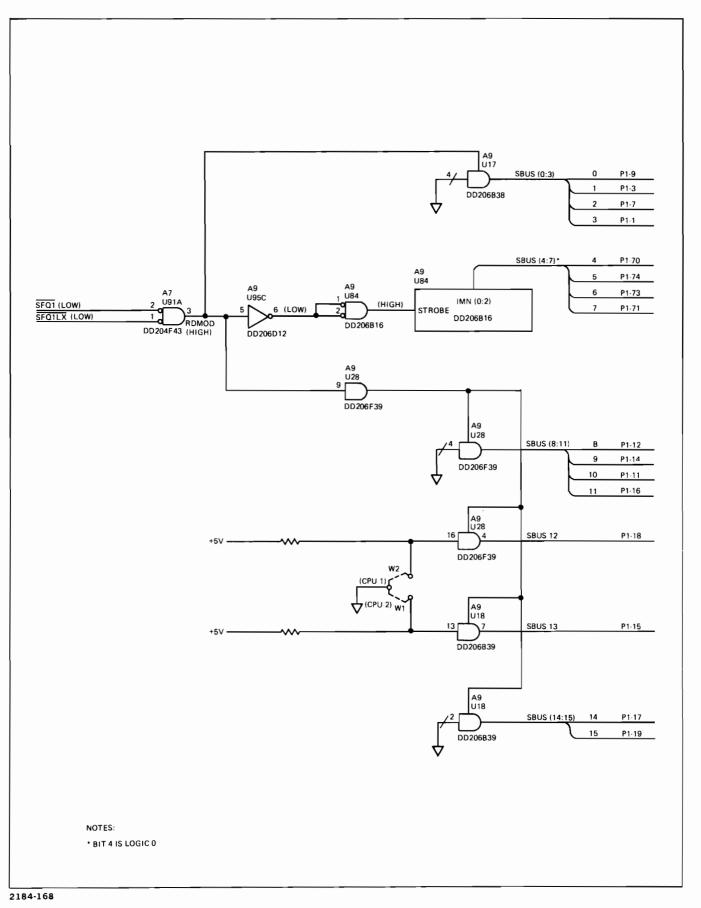

| 3-124.          | Interrupt Module Number Register                      |              |

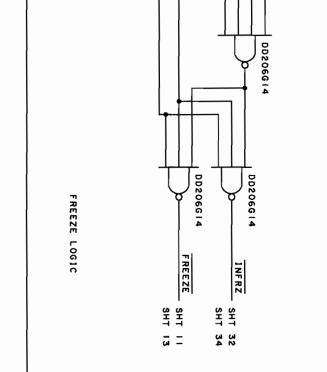

| 3-126.          | CPU Request/Select Logic                              |              |

| 3-128.          | Interrupt Device Number Register                      |              |

| 3-130.          | Input/Output Processor Control Register               |              |

| 3-132.          | Direct Output Data Register                           | 3-35         |

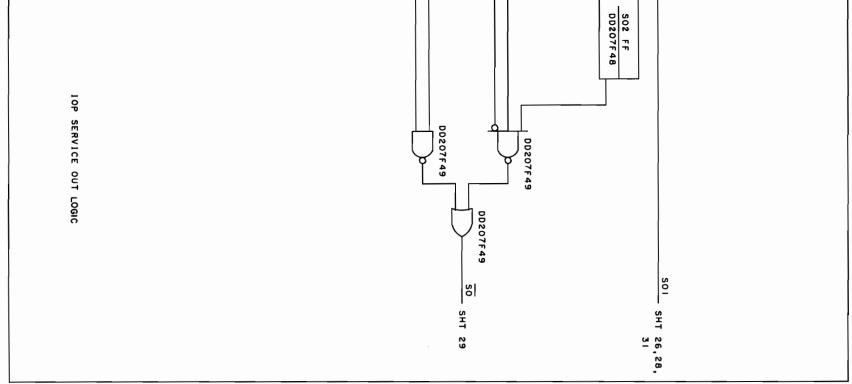

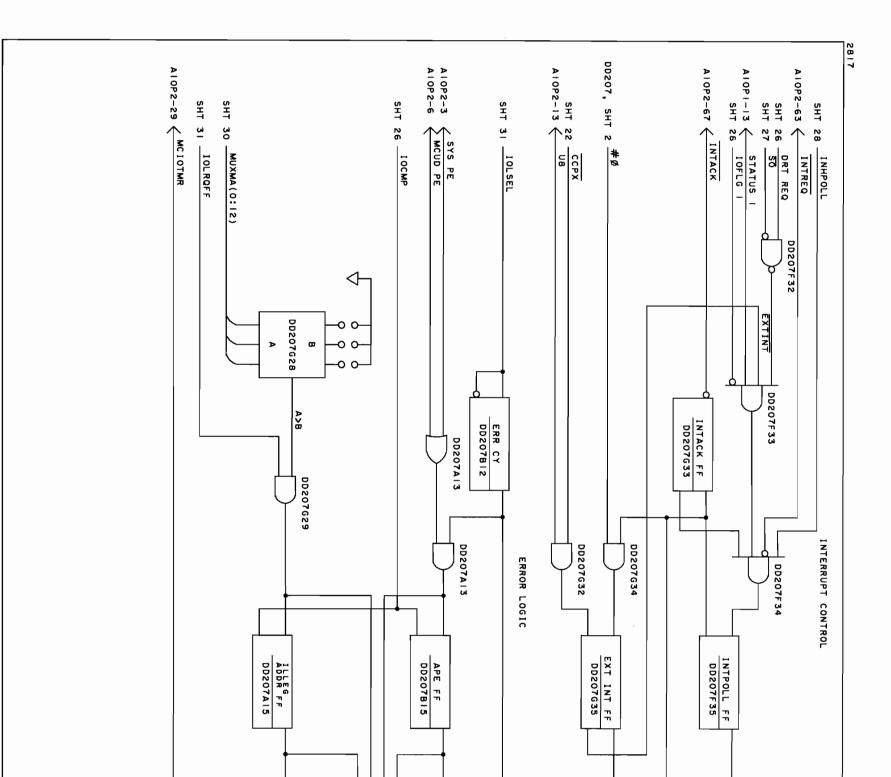

| 3-134.          | IOP Direct Control Logic                              | 3-36         |

| 3-136.          | Flag 3 Register                                       | 3-36         |

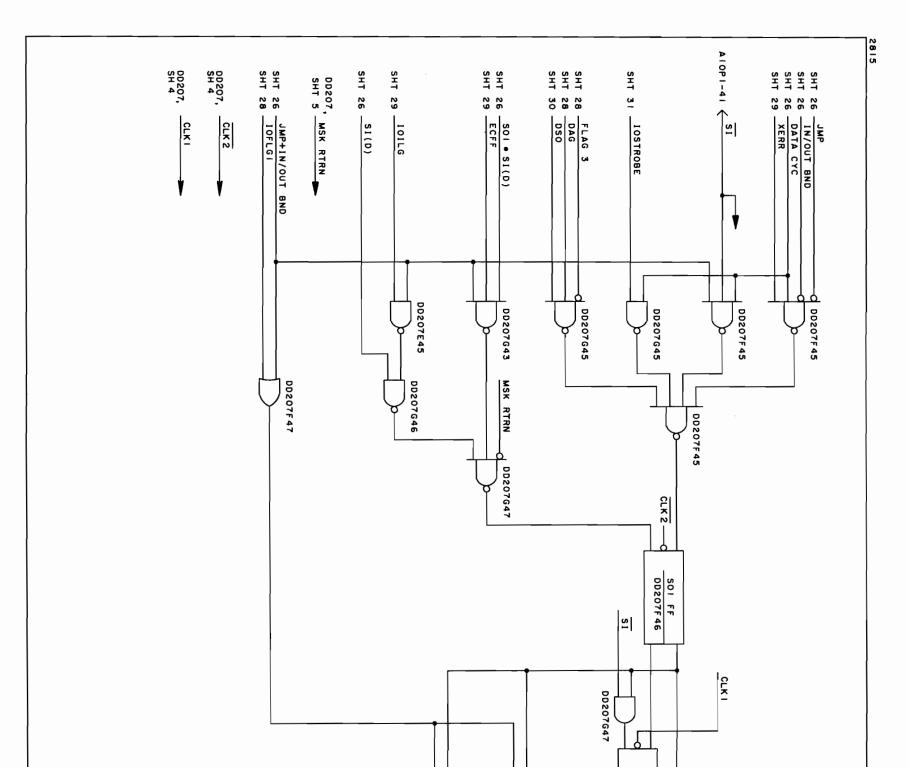

| 3-138.          | IOP Service Out Logic                                 |              |

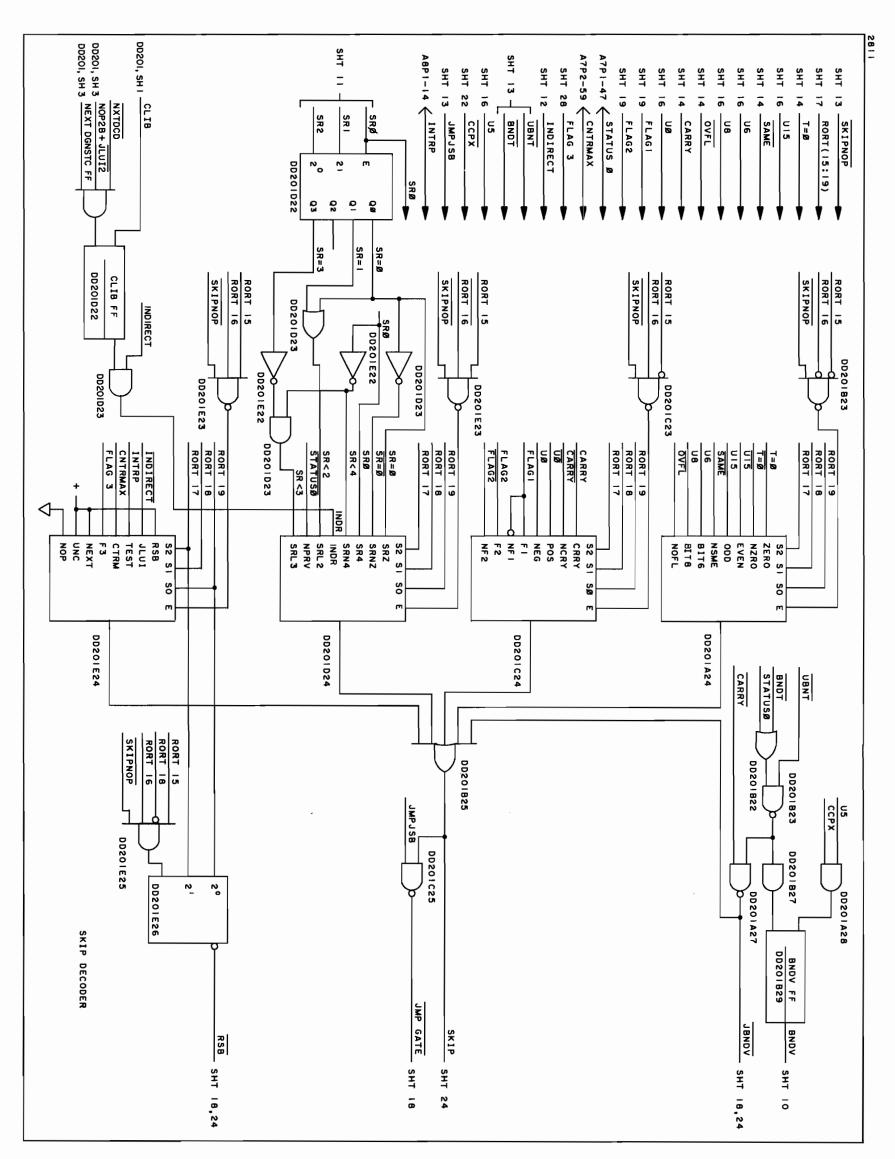

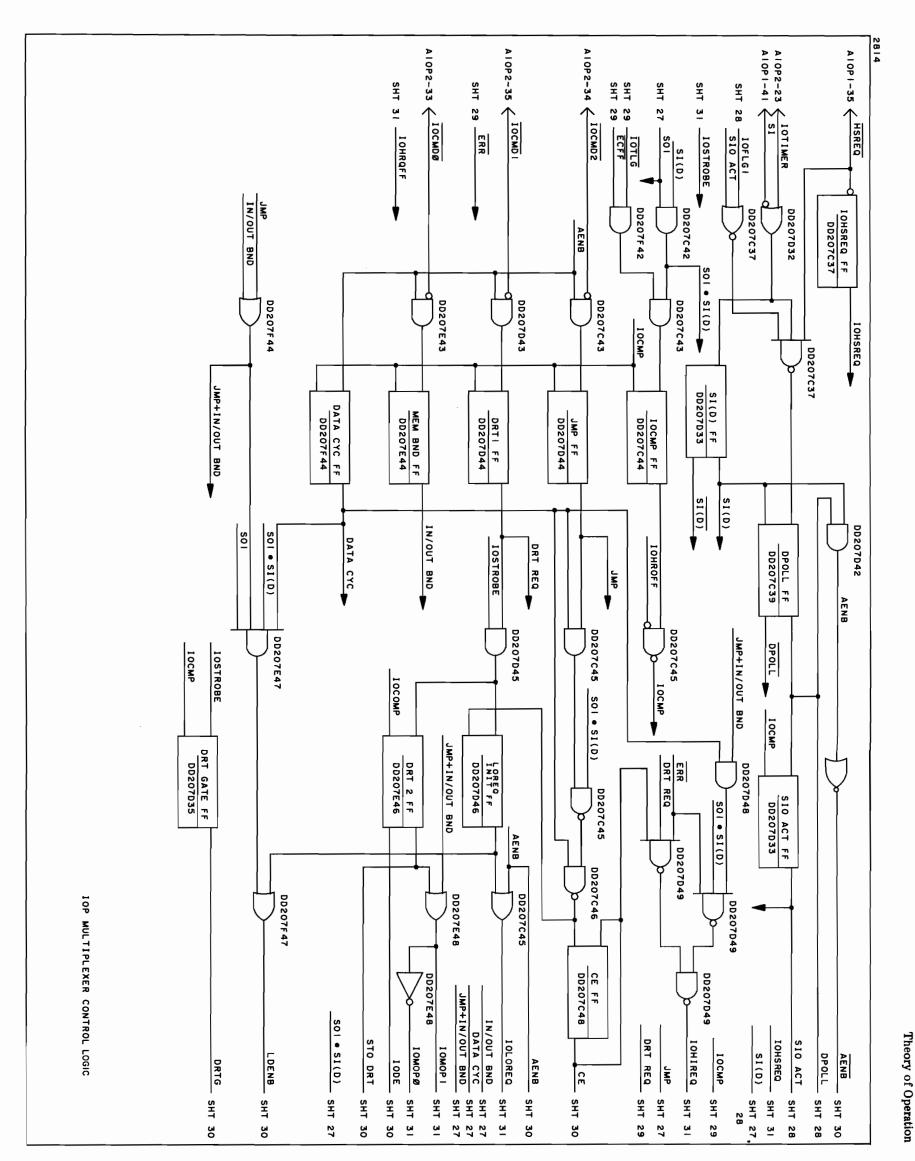

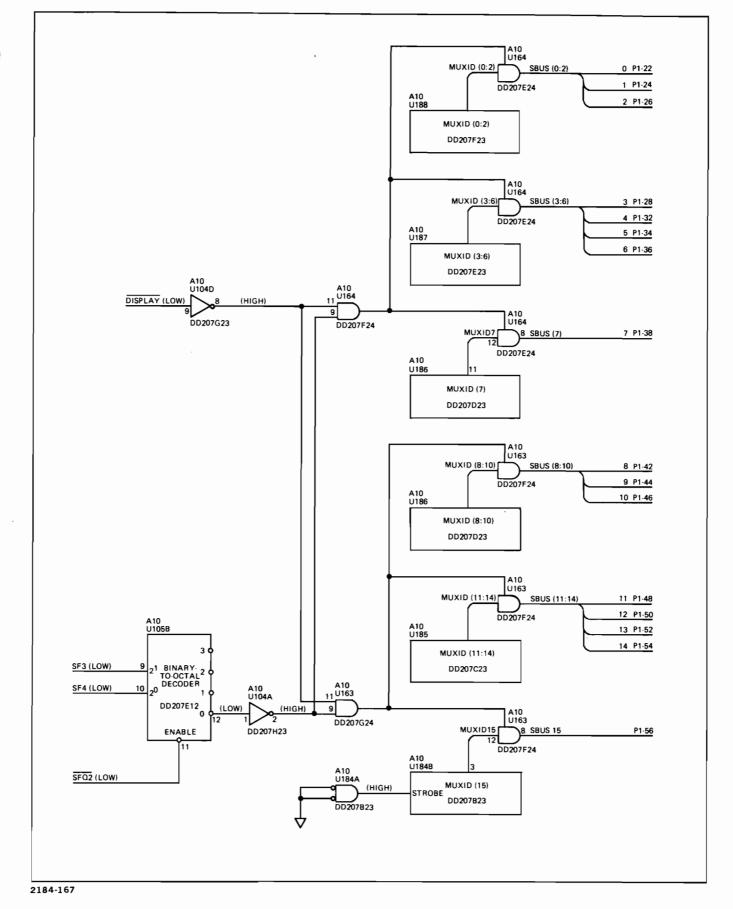

| <b>3</b> -140.  | IOP Multiplexer Control Logic                         |              |

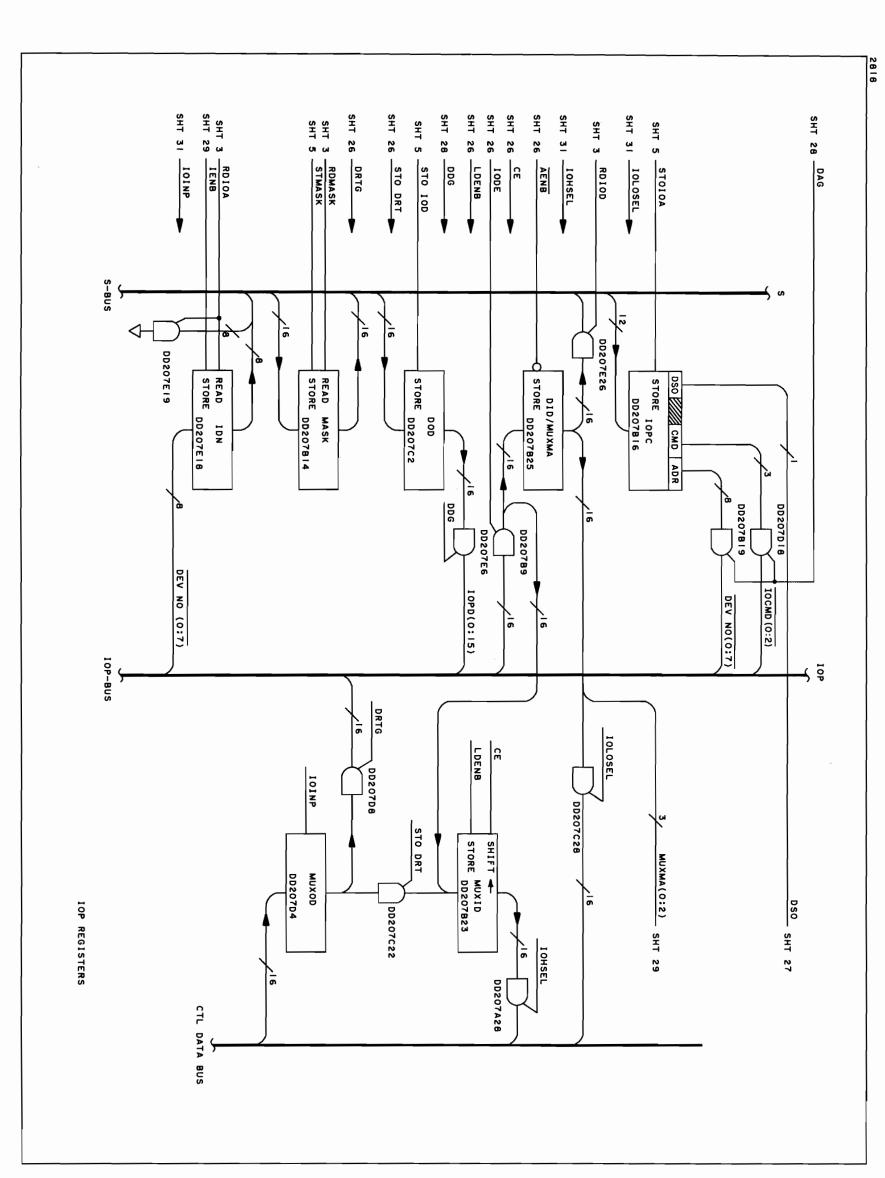

| 3-142.          | Multiplexed Input Data Register                       |              |

| 3-144.          | Multiplexed Output Data Register                      |              |

| 3-146.          | Direct Input Data/Multiplexed Memory Address Register |              |

| 3-148.          | Operand Register                                      |              |

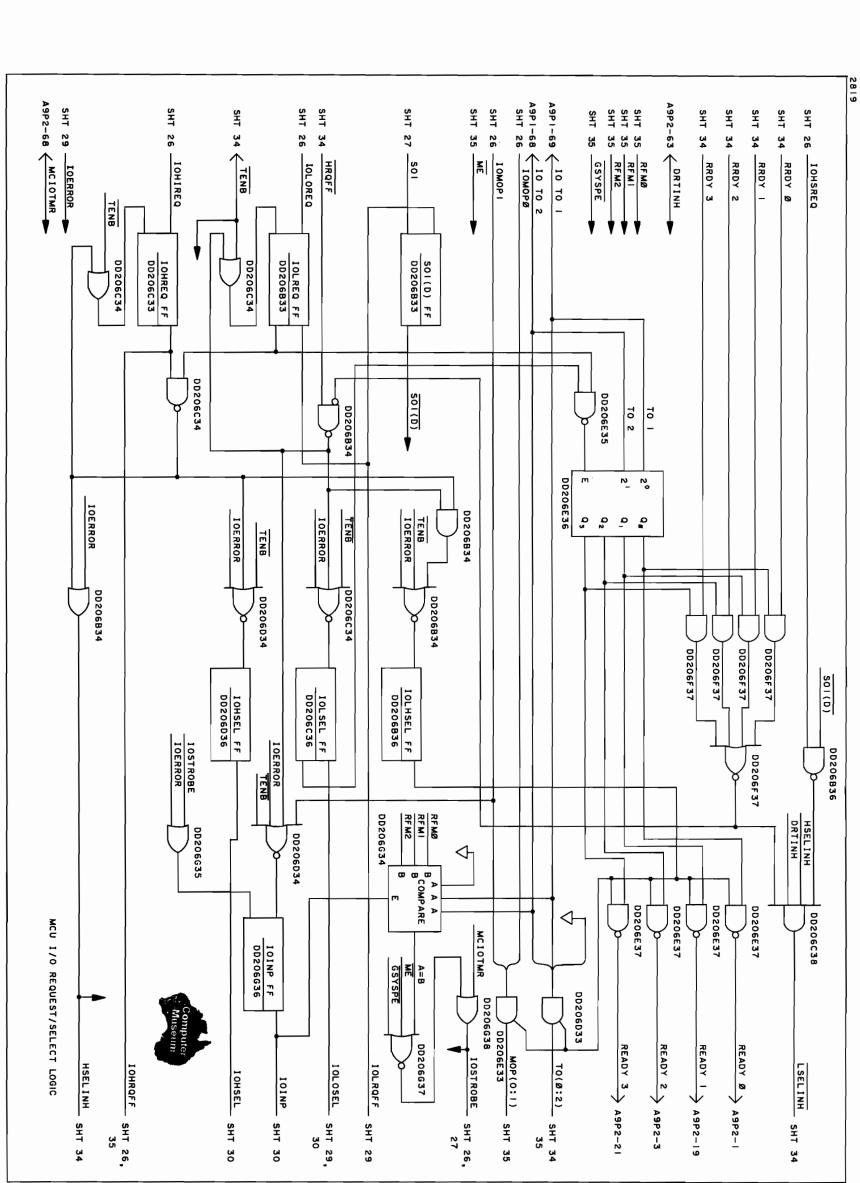

| <b>3-15</b> 0.  | MCU I/O Request/Select Logic                          |              |

| 3-152.          | MCU Error Logic                                       |              |

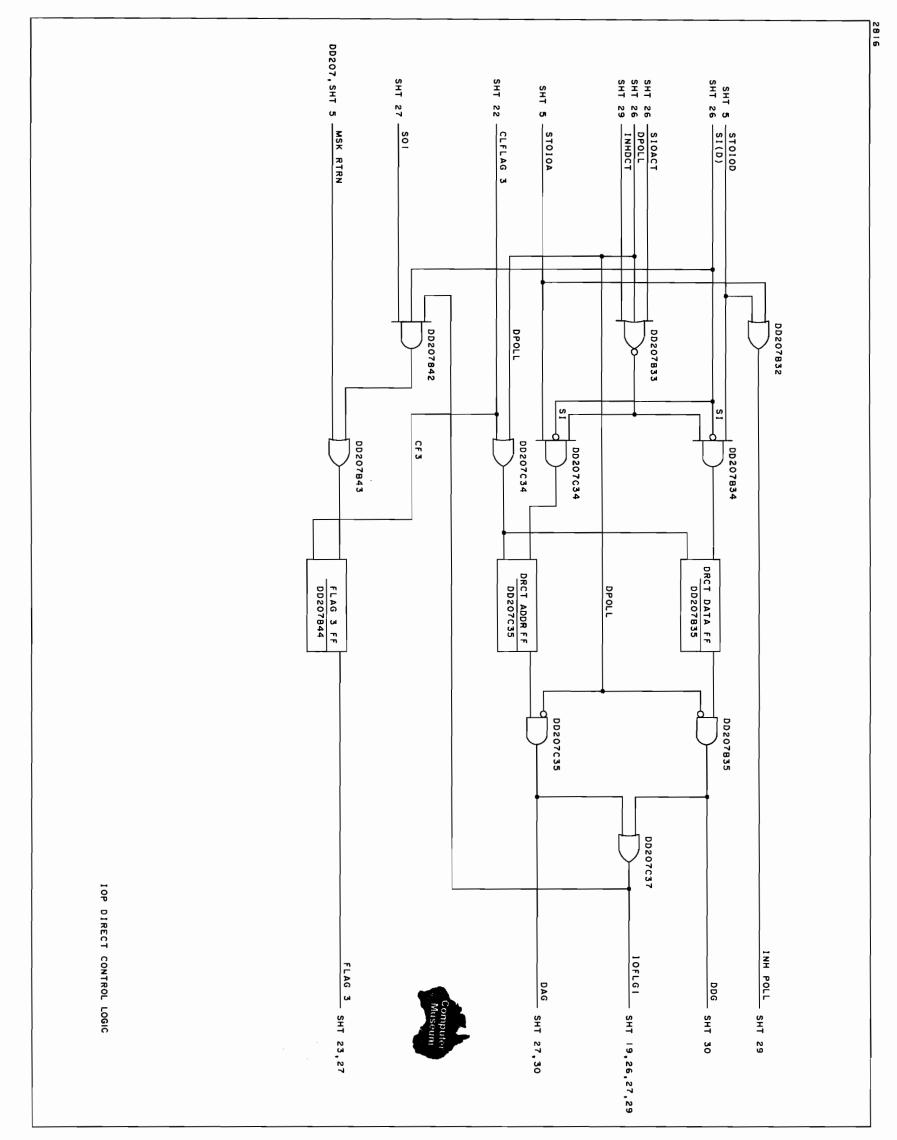

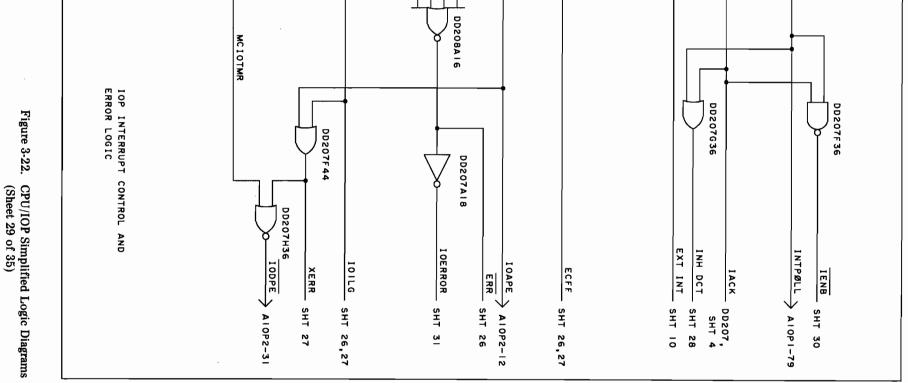

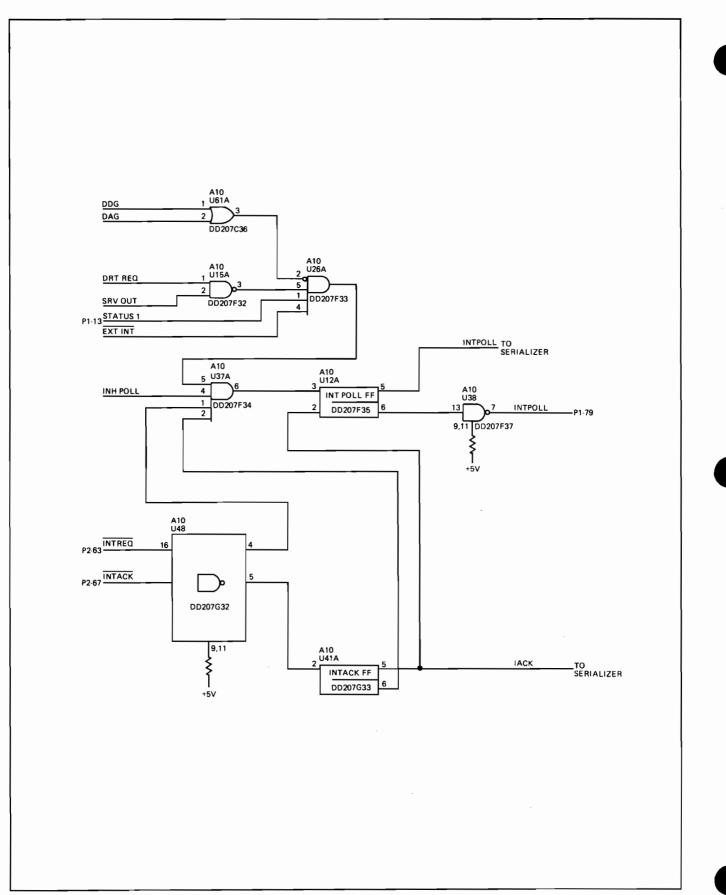

| 3-154.          | IOP Interrupt Control and Error Logic                 |              |

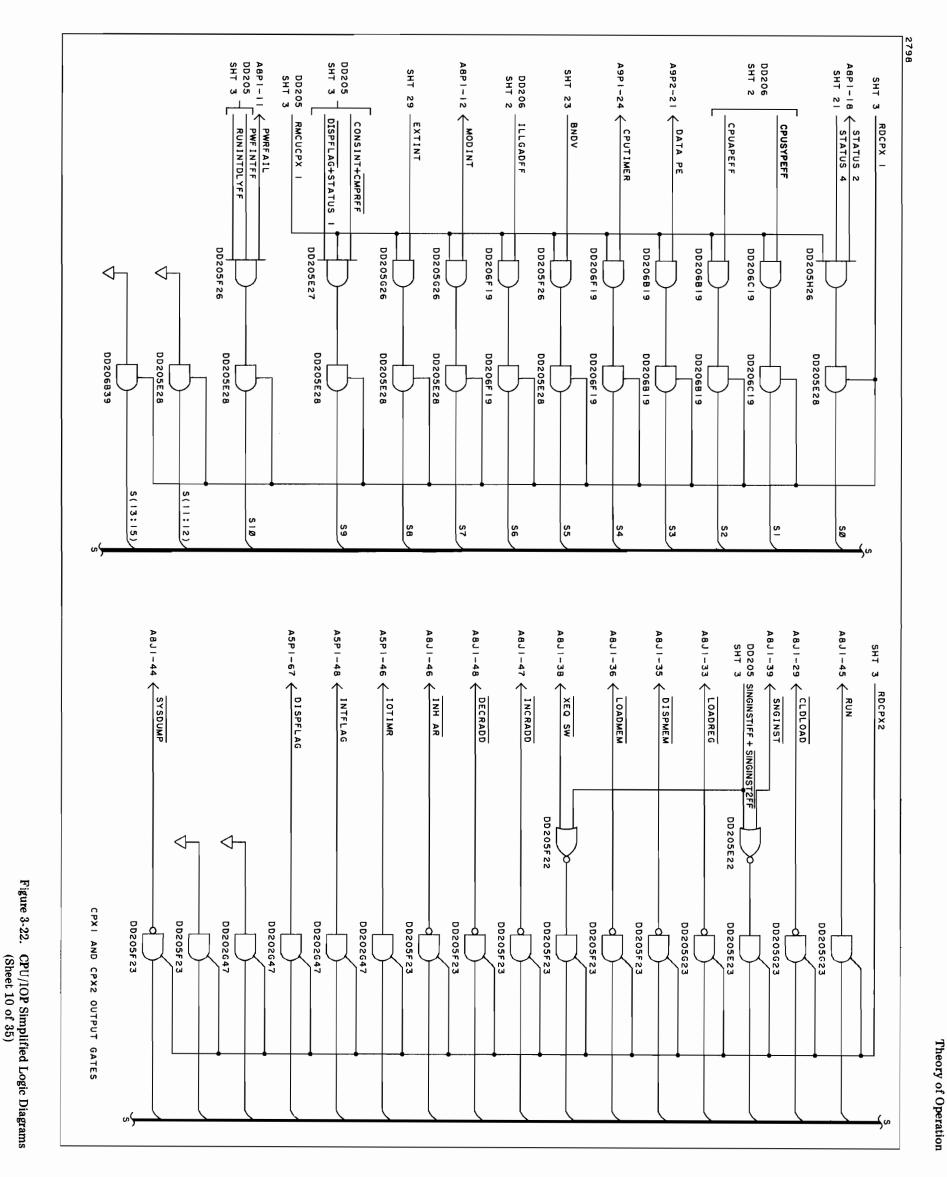

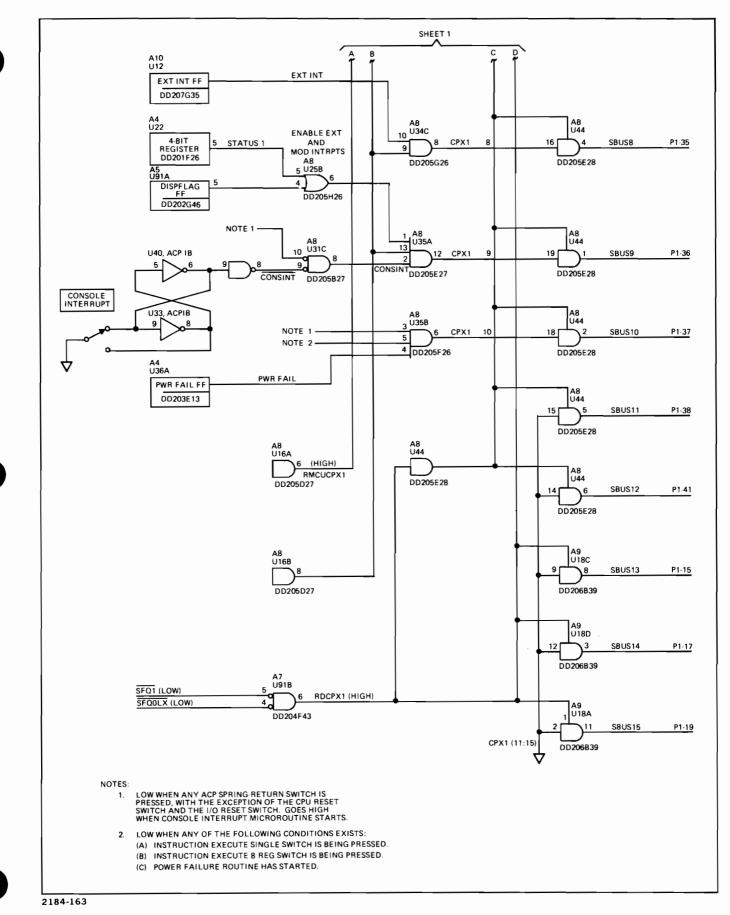

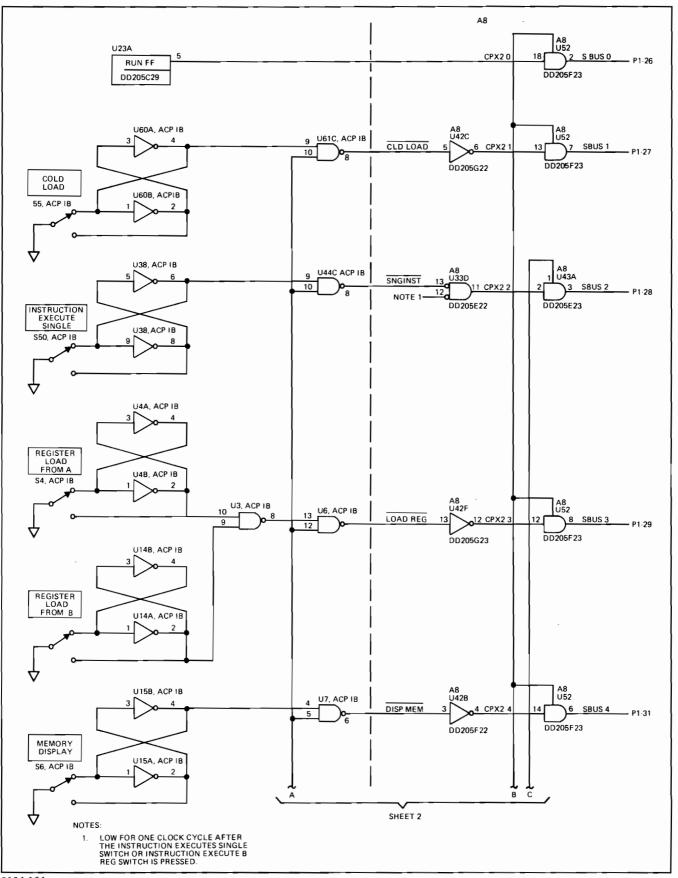

| 3-157.          | CPX1 Register                                         | 3-37         |

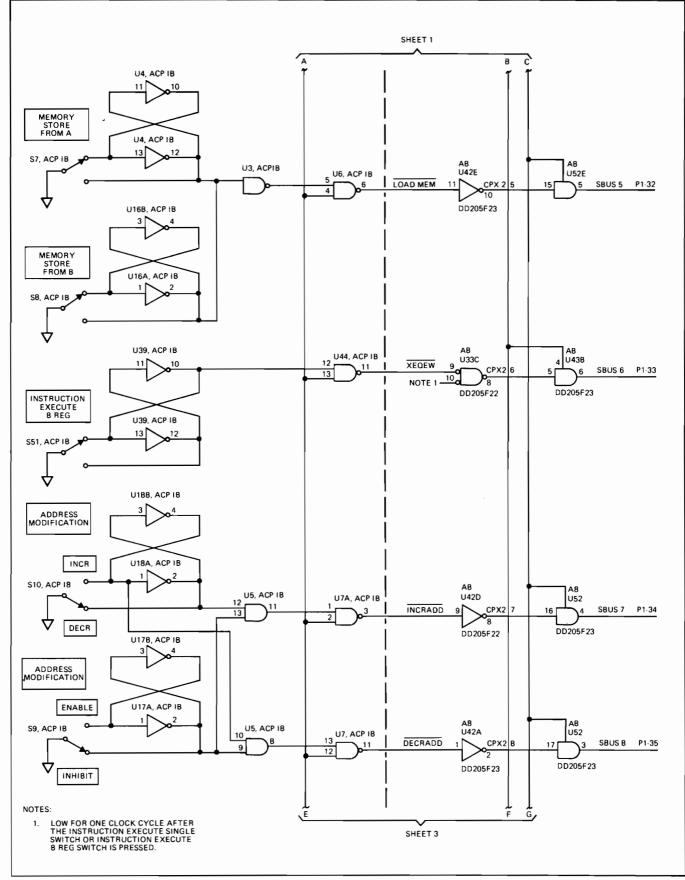

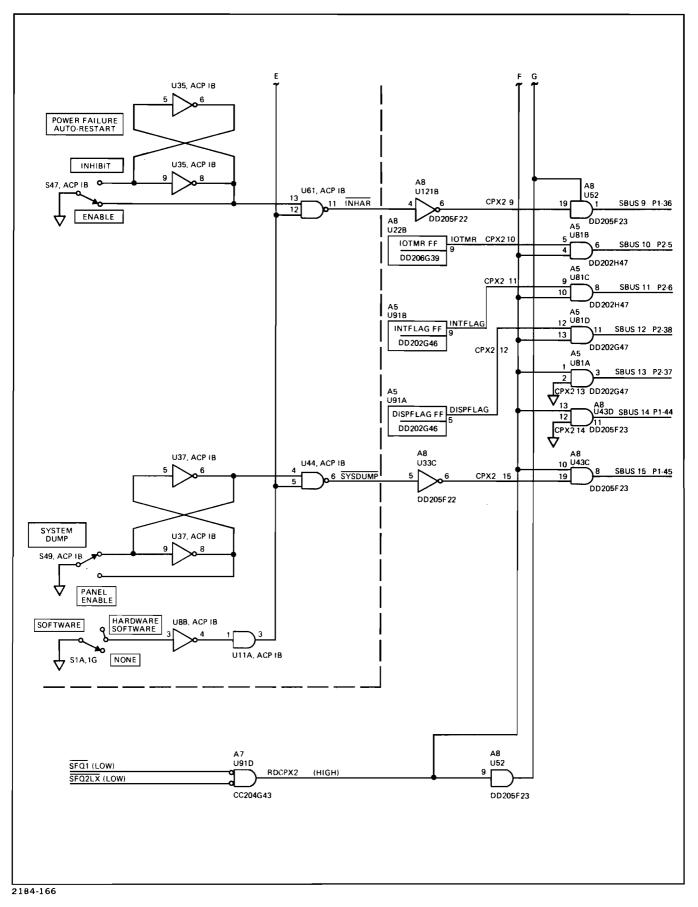

| 3-159.          | CPX2 Register                                         | 3-37         |

| 3-161.          | Mask Register                                         |              |

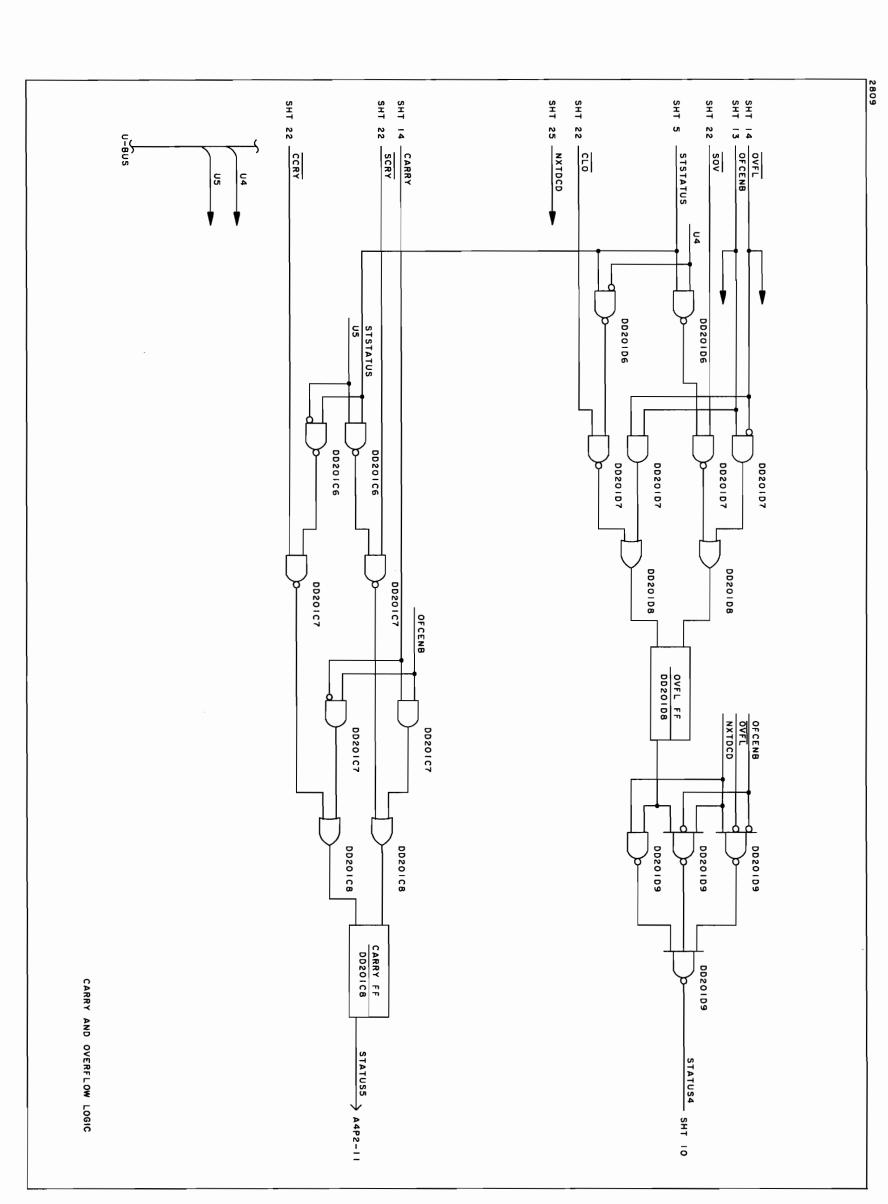

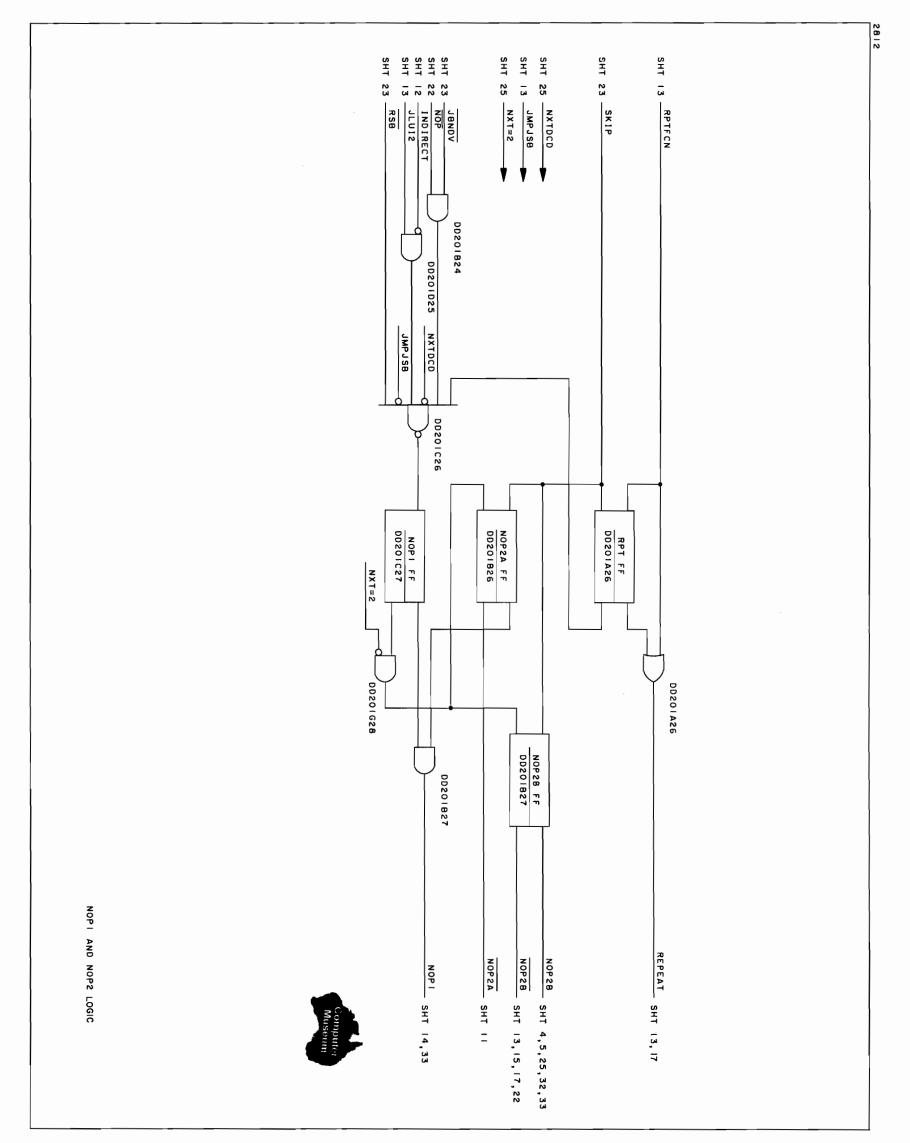

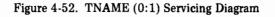

| 3-164.          | NOP1, NOP2 Logic                                      | 3-38         |

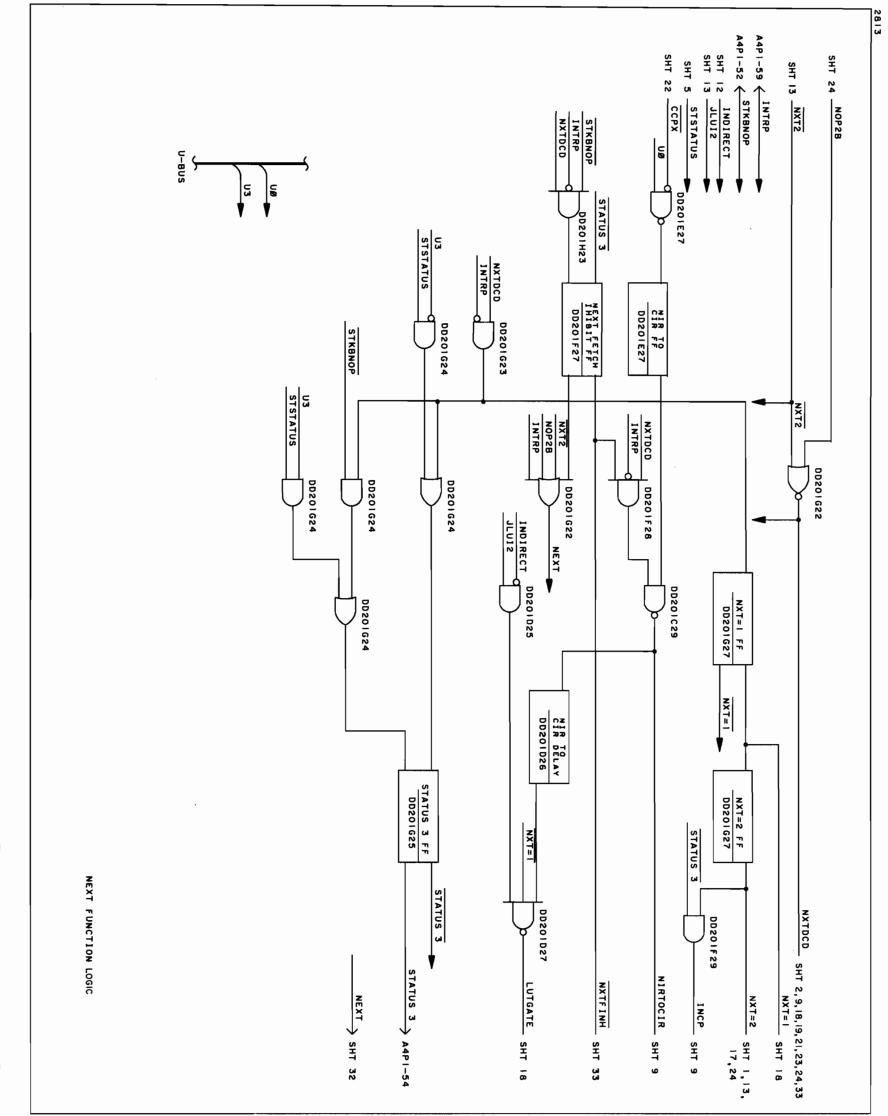

| 3-166.          | Next Logic                                            |              |

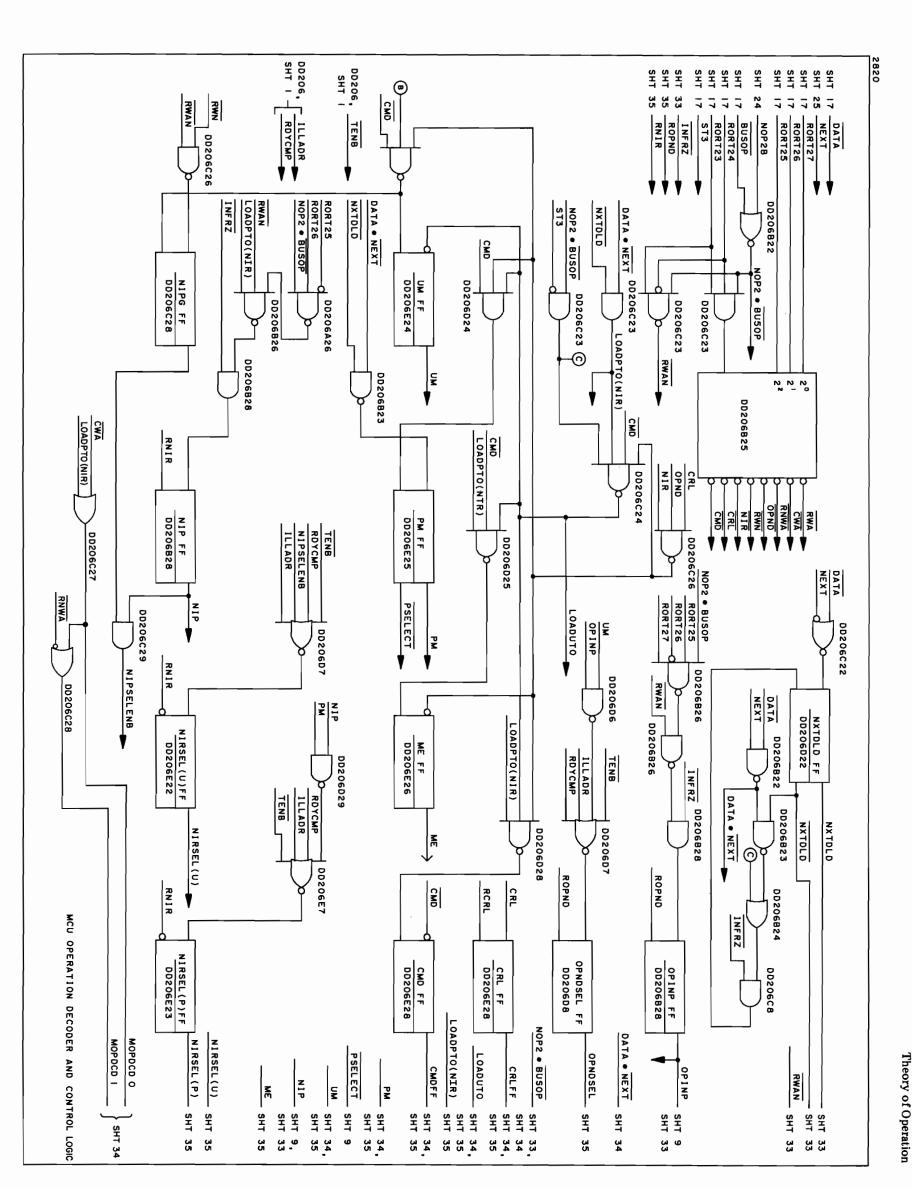

| 3-168.          | MCU Operation Decoder                                 | 3-38         |

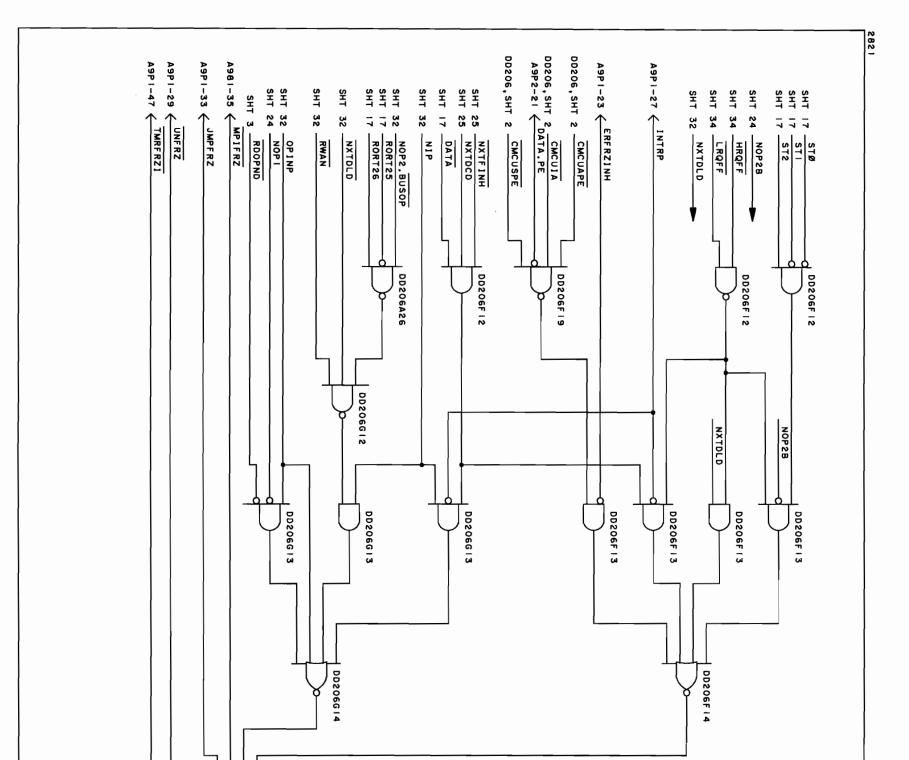

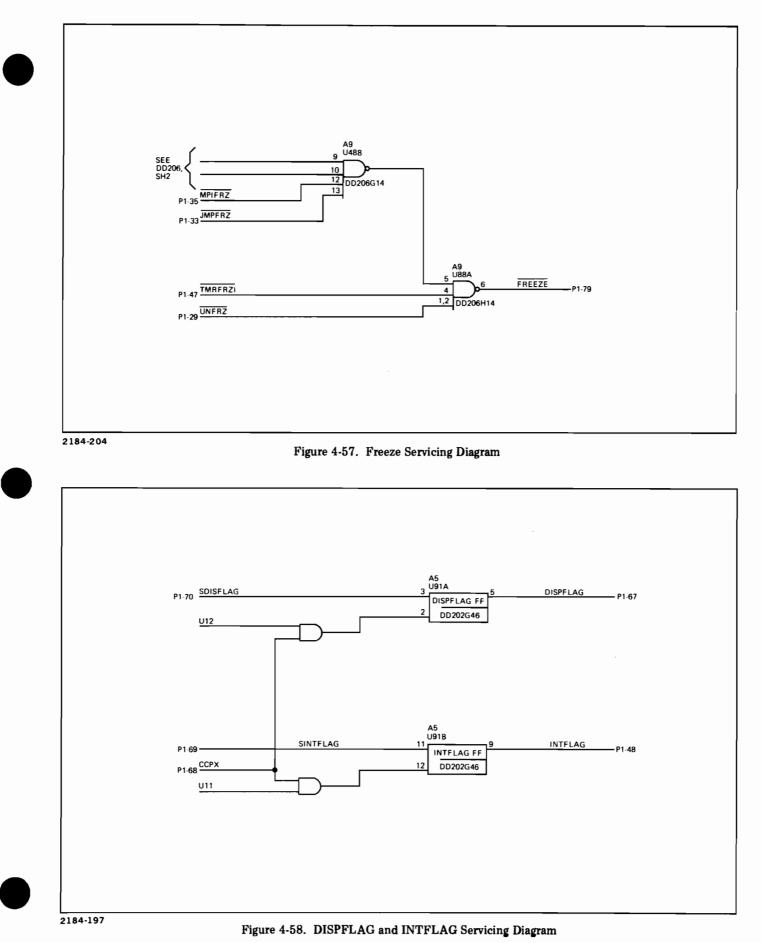

| 3-170.          | Freeze Logic                                          |              |

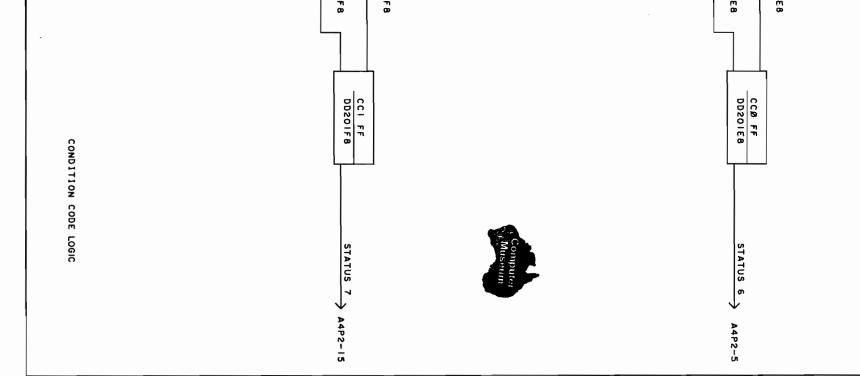

| 3-172.          | Overflow Flip-Flop                                    |              |

| 3-174.          | Carry Flip-Flop                                       |              |

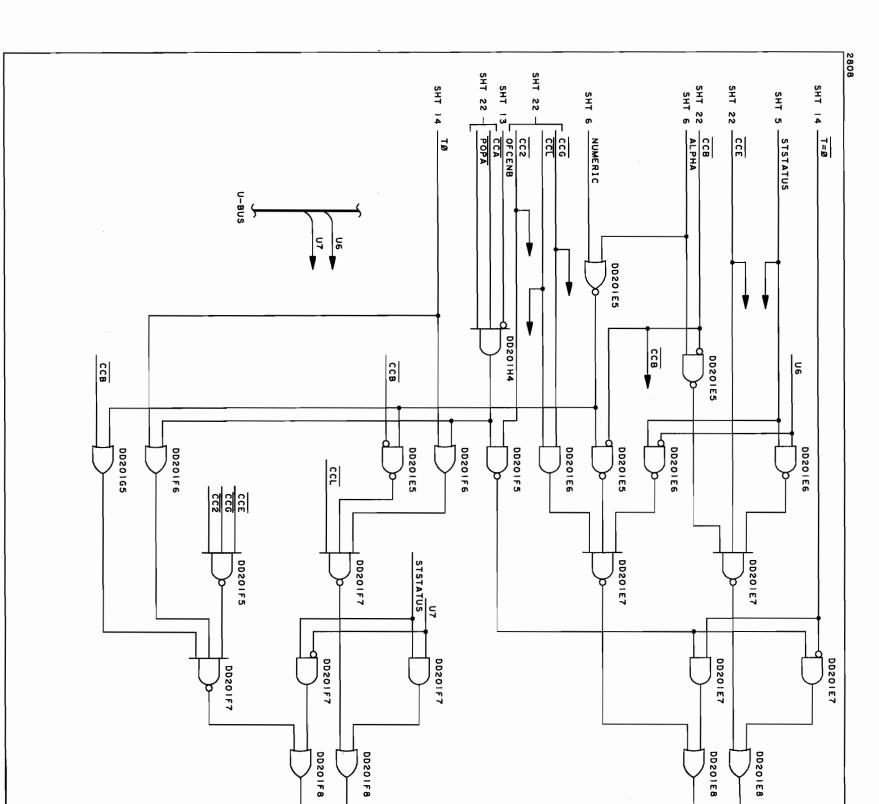

| 3-176.          | Condition Code Logic                                  |              |

| 3-181.          | Functional-Level Description                          |              |

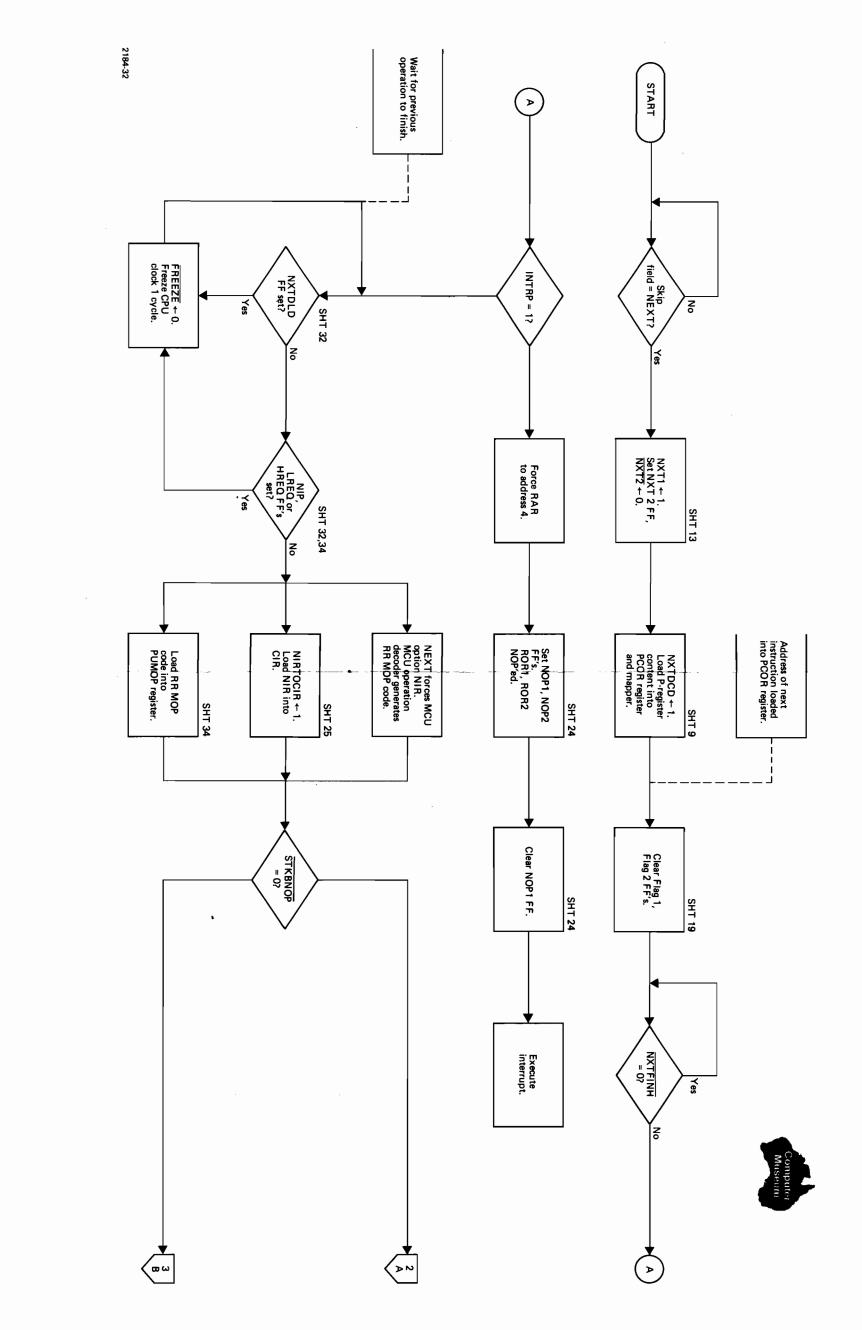

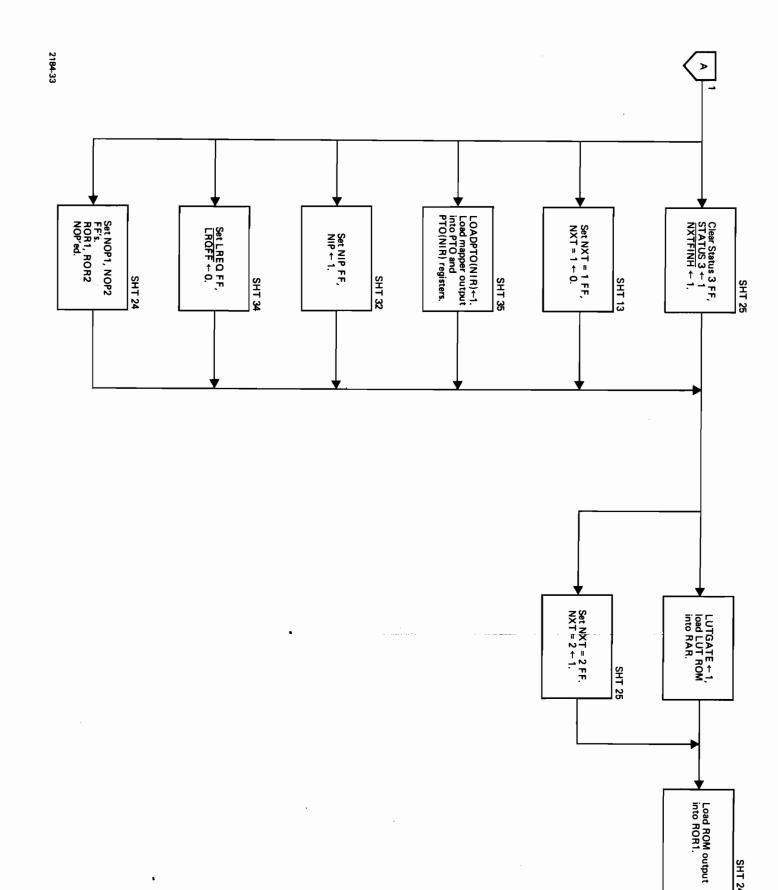

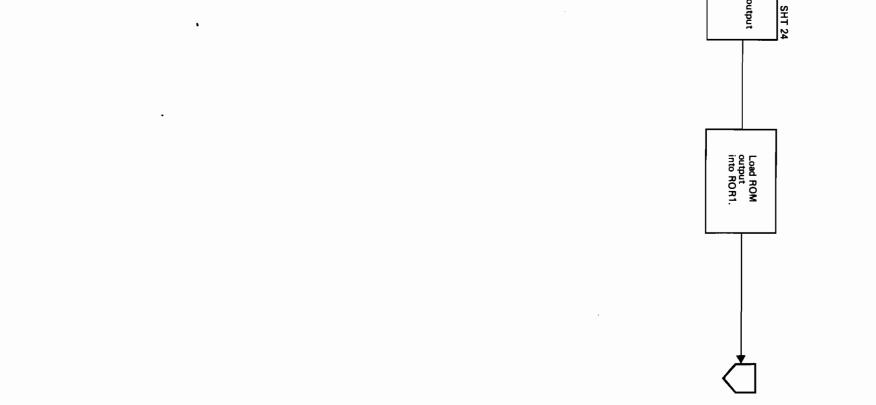

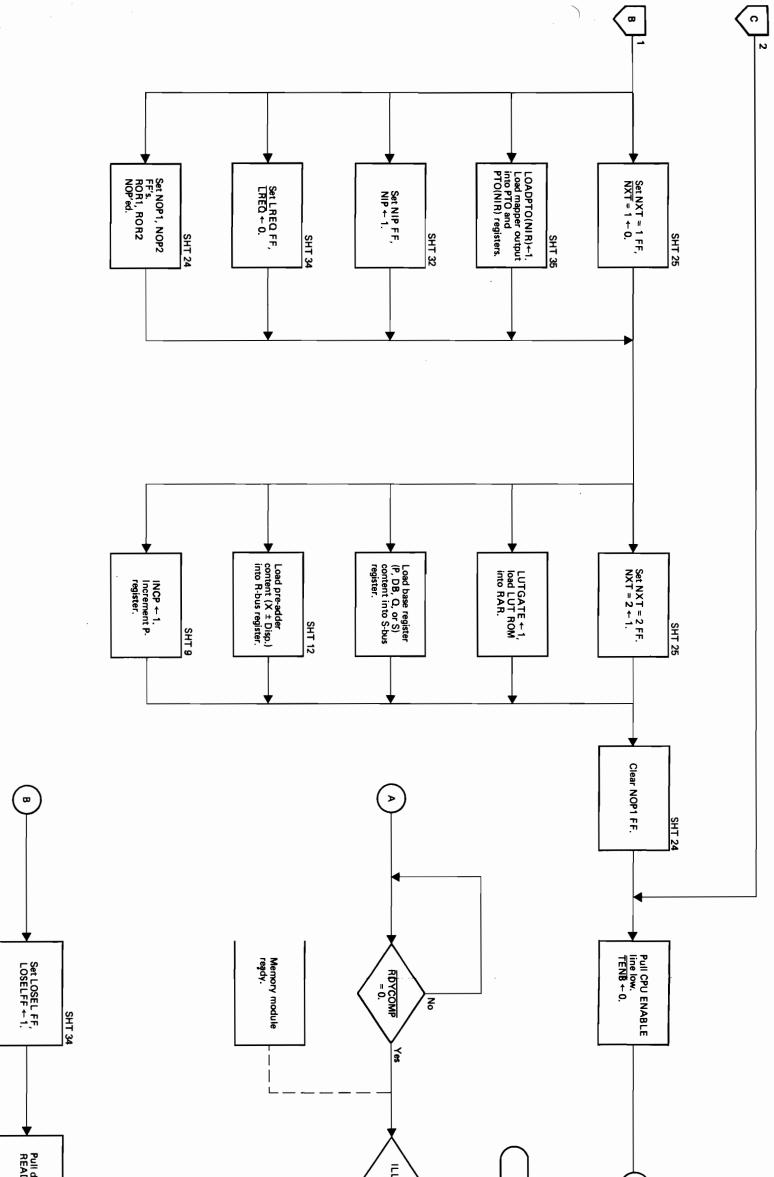

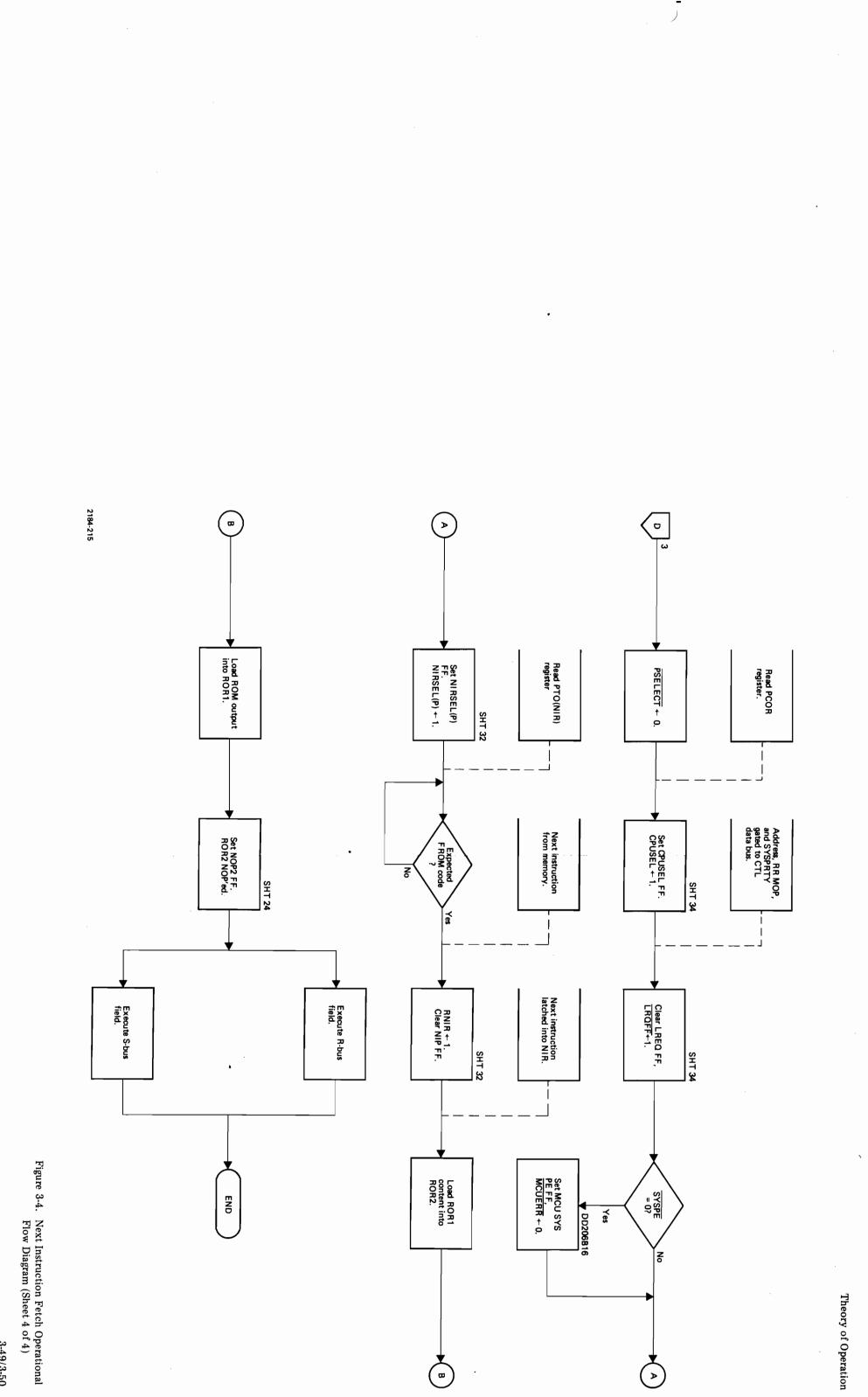

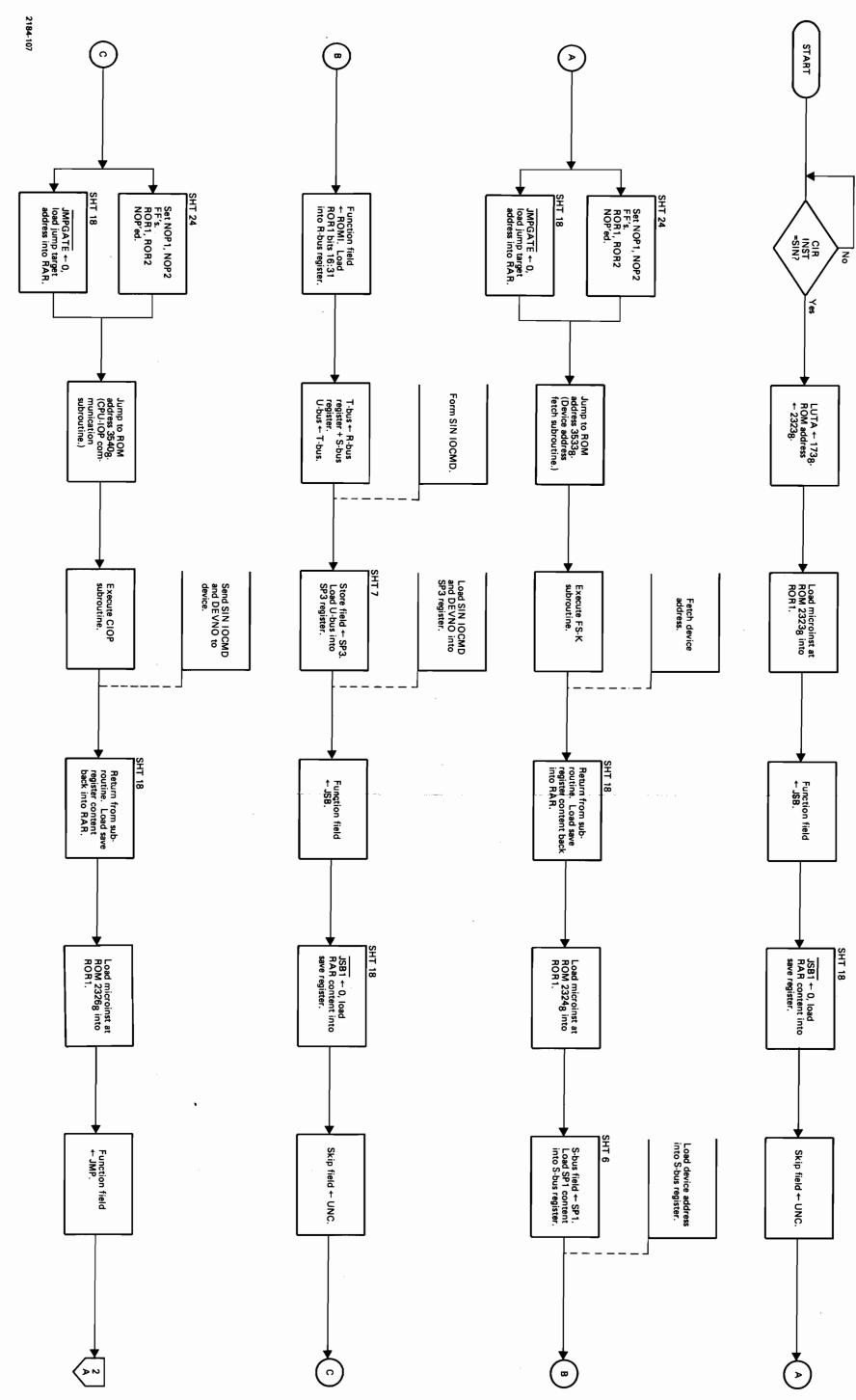

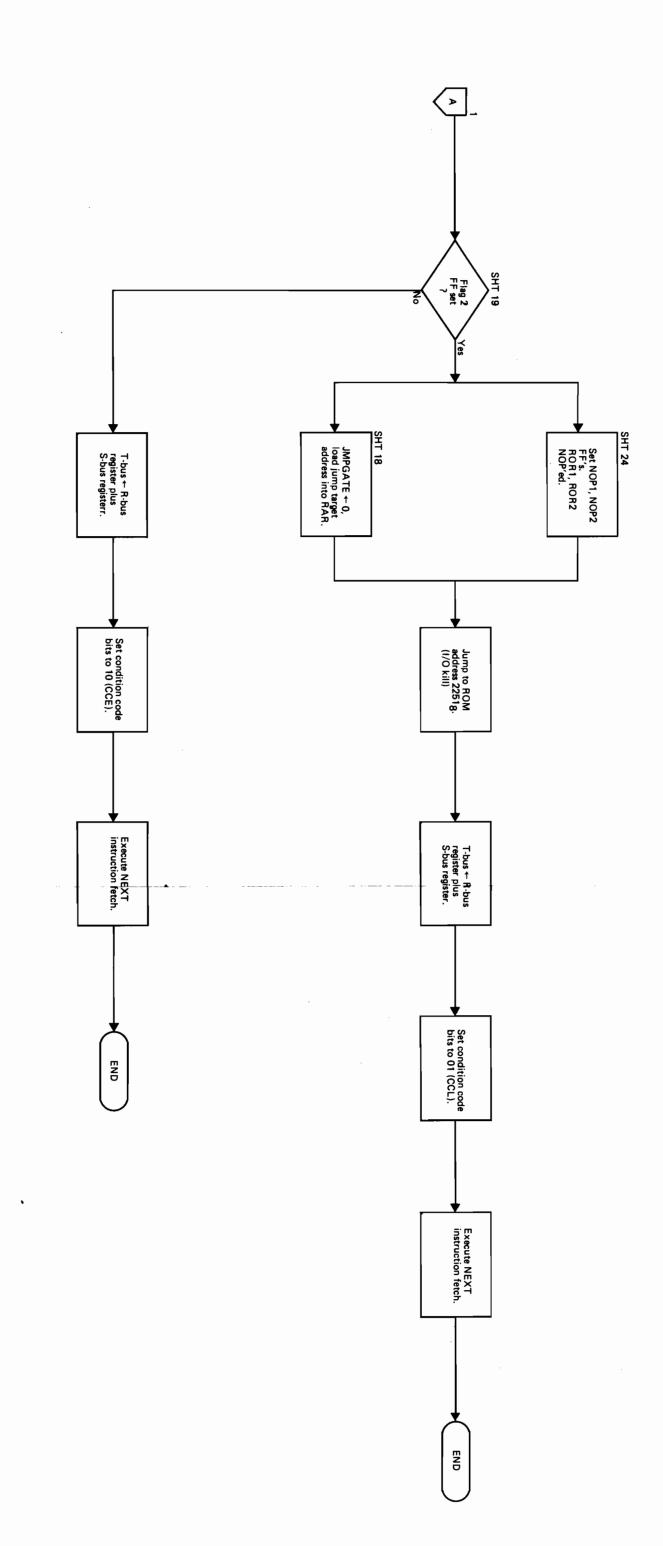

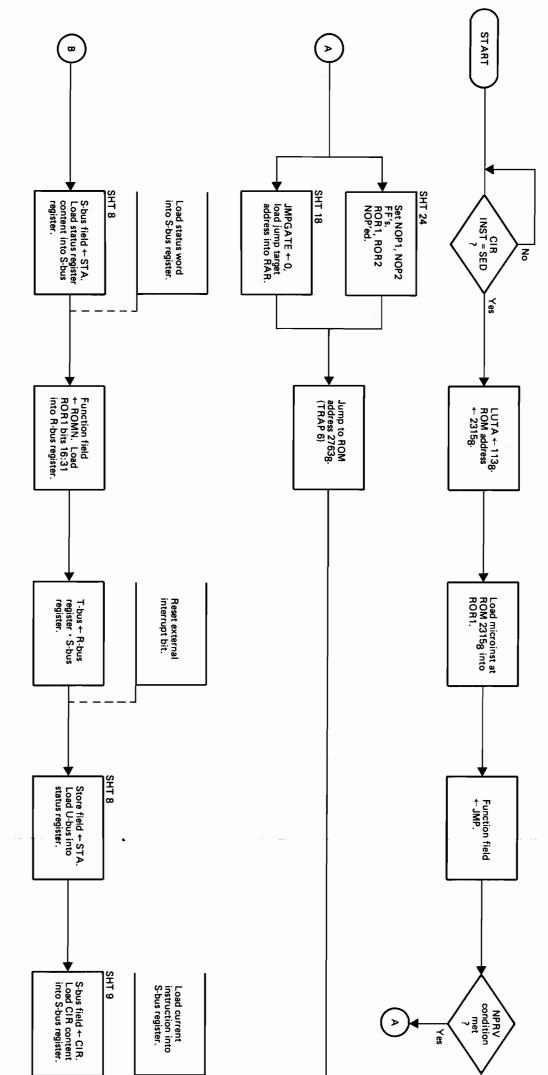

| 3-190.          | Next Instruction Fetch                                |              |

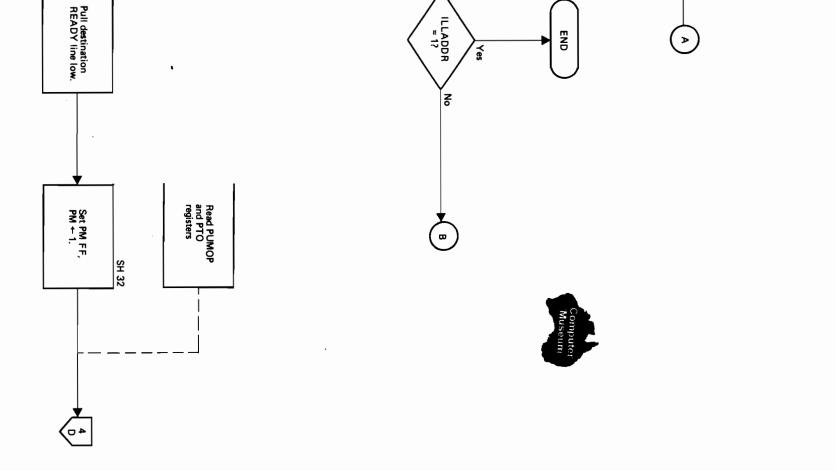

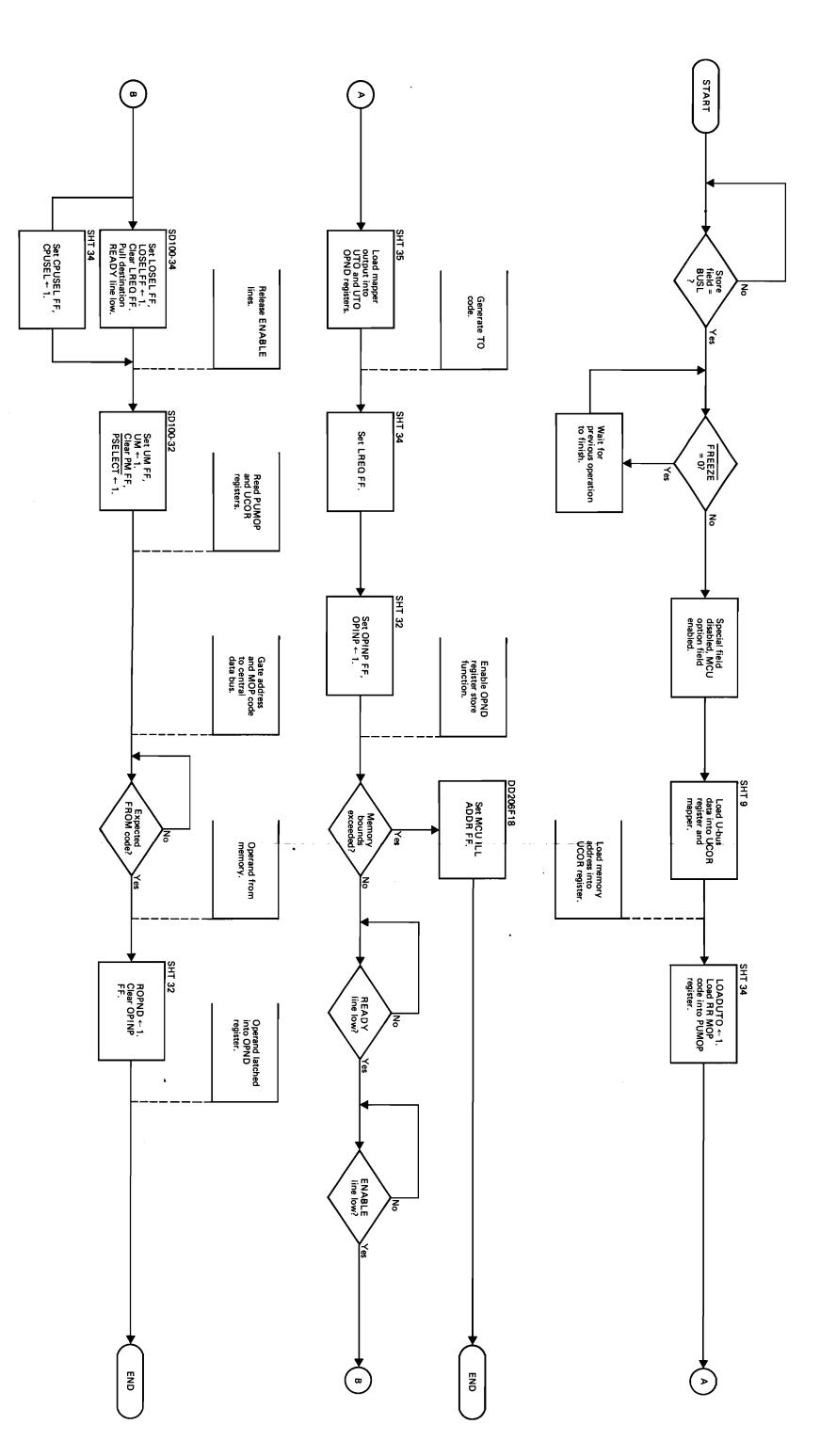

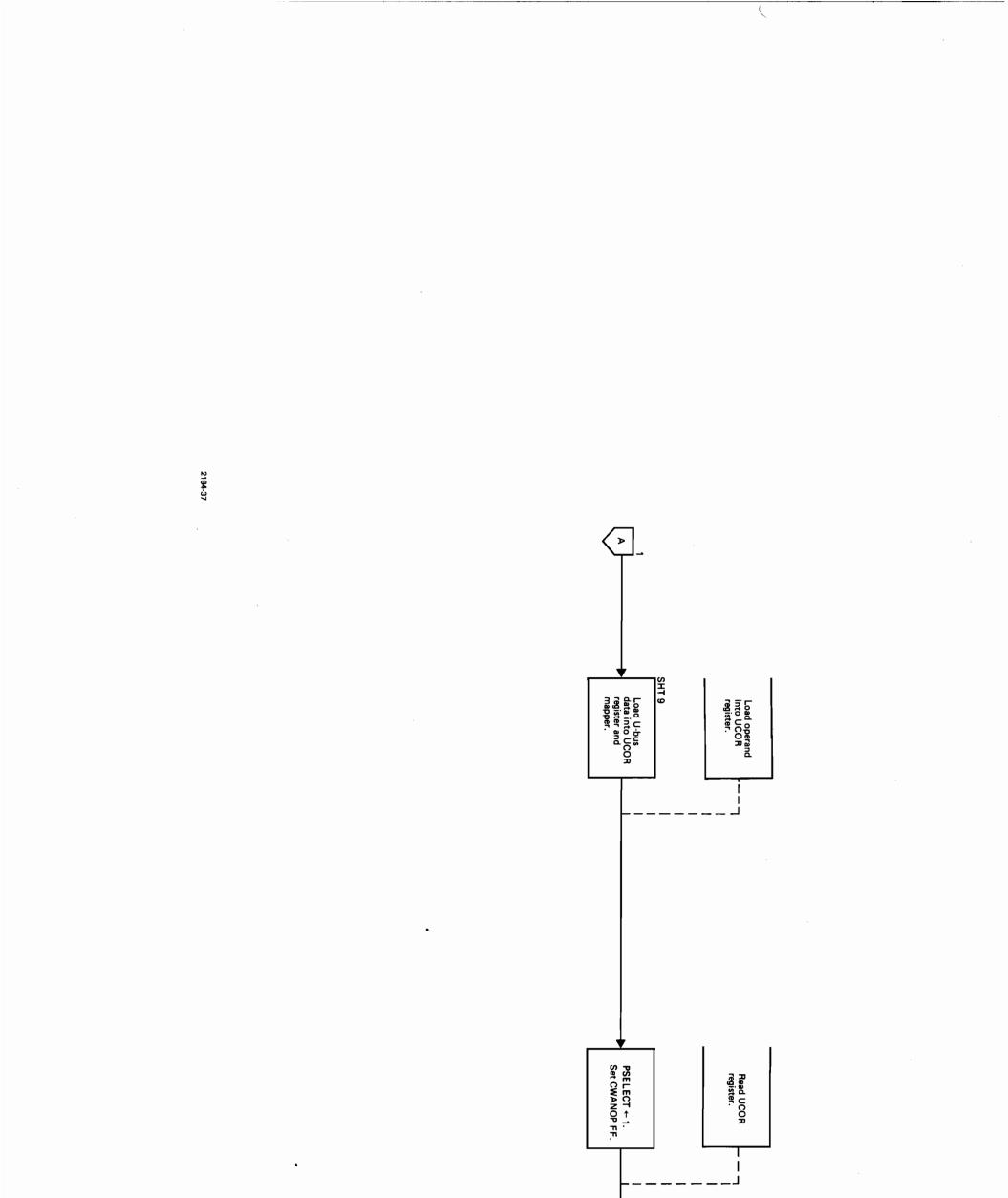

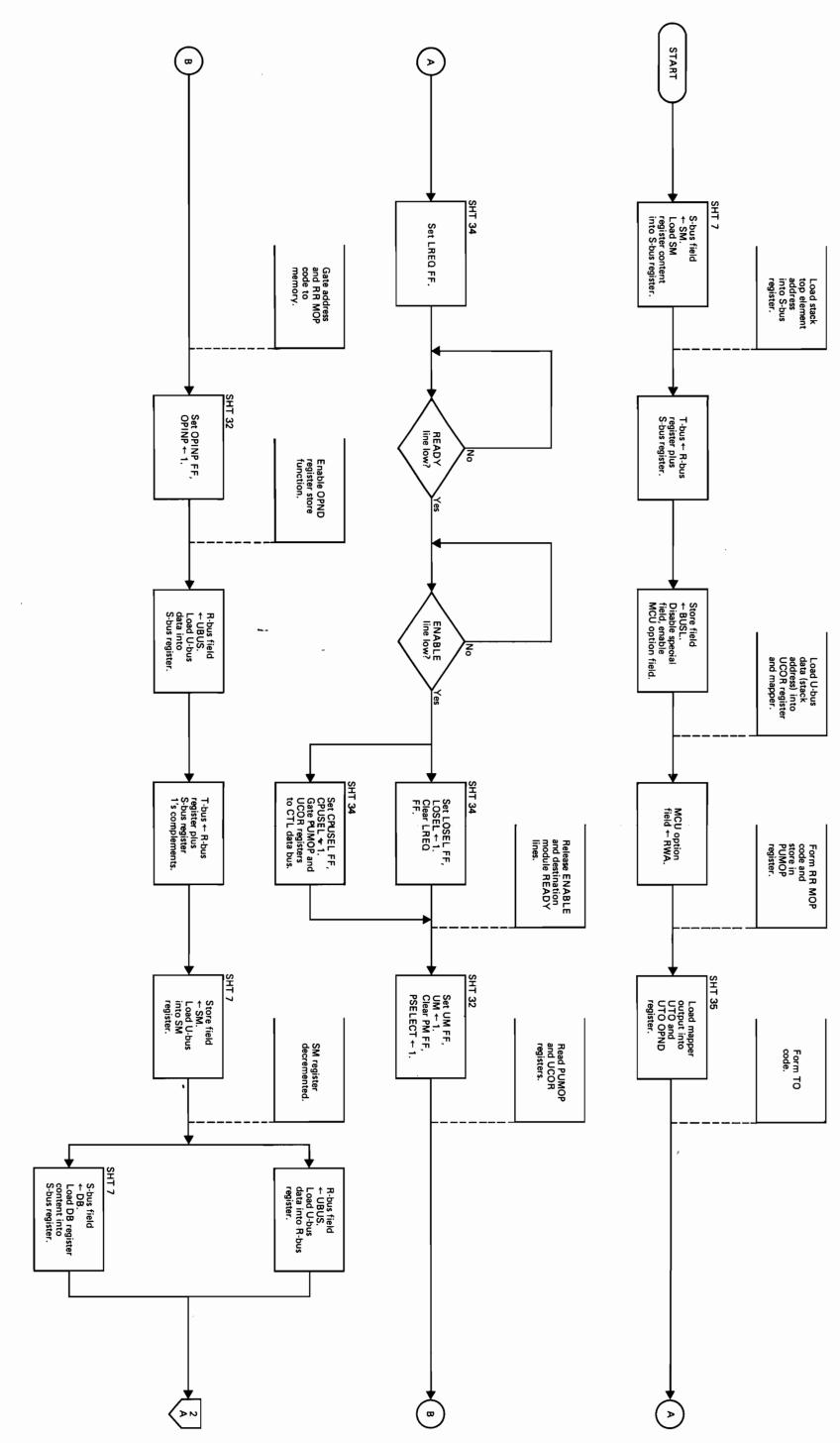

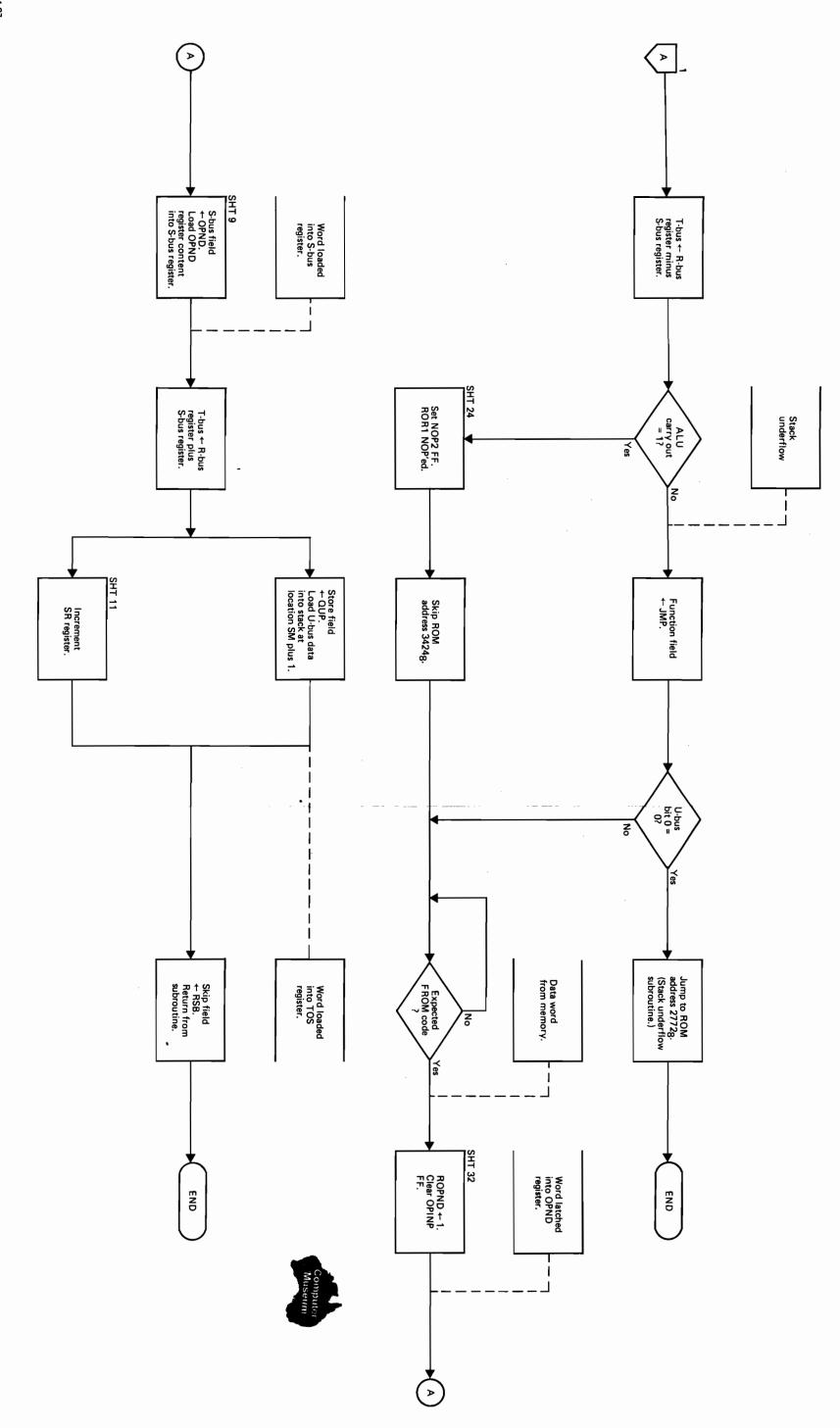

| 3-200.          | Operand Fetch                                         | 3-51         |

## CONTENTS (Continued)

## Section

IV

## Pages

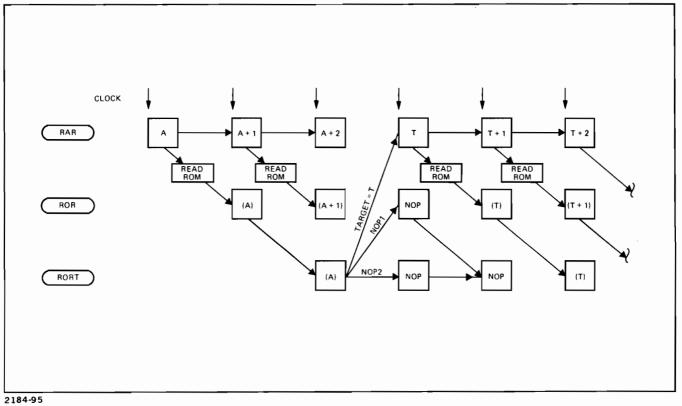

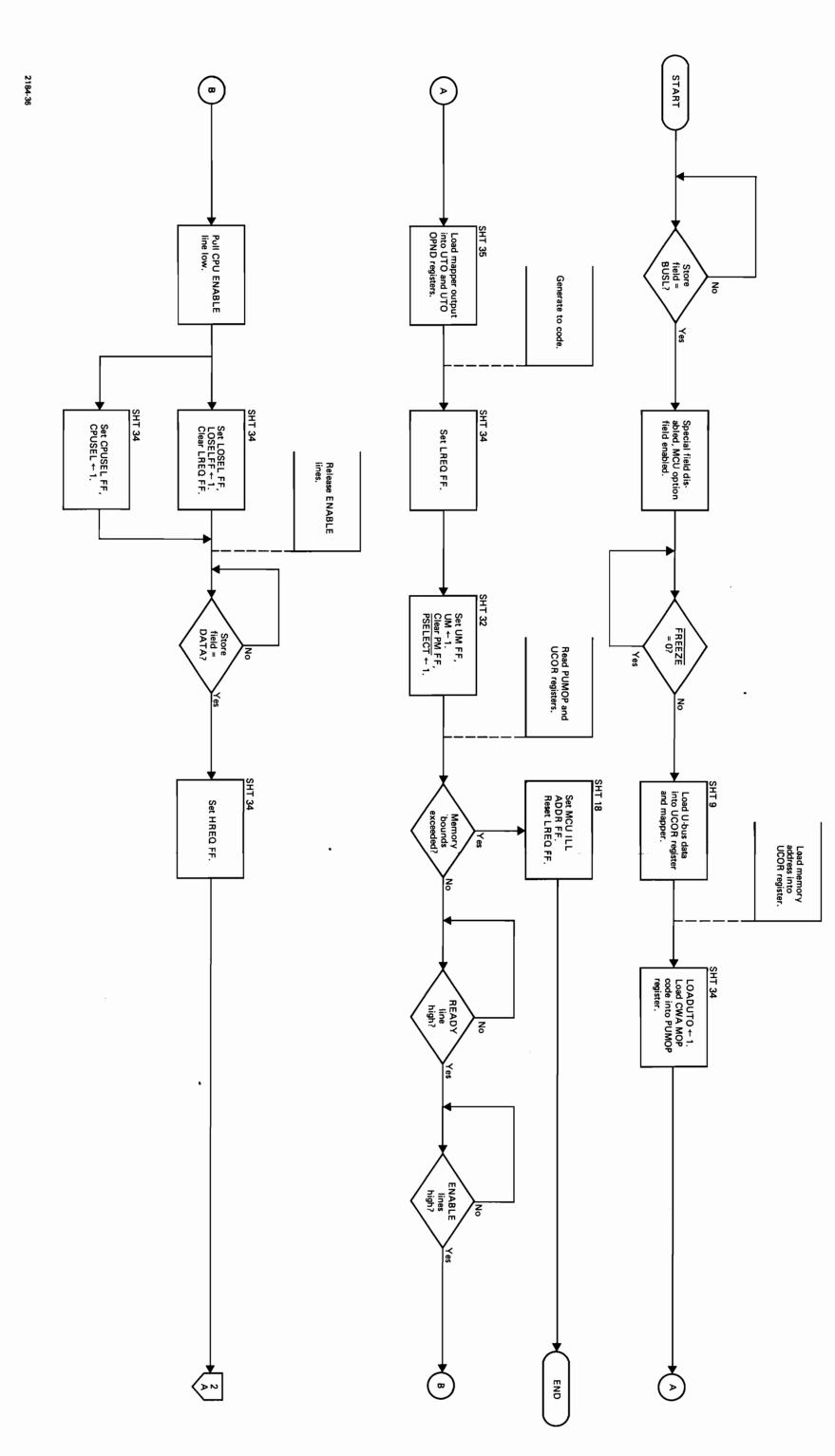

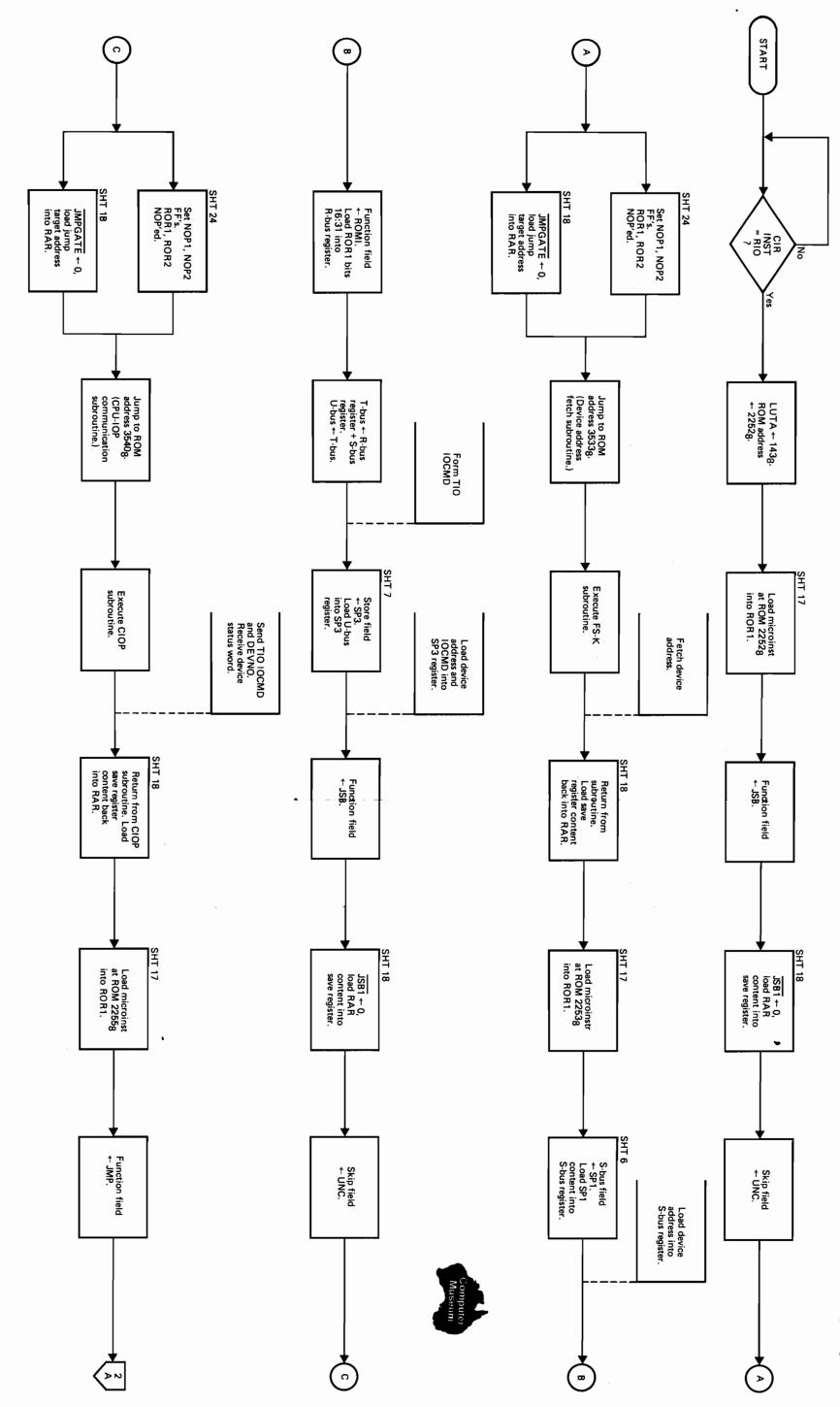

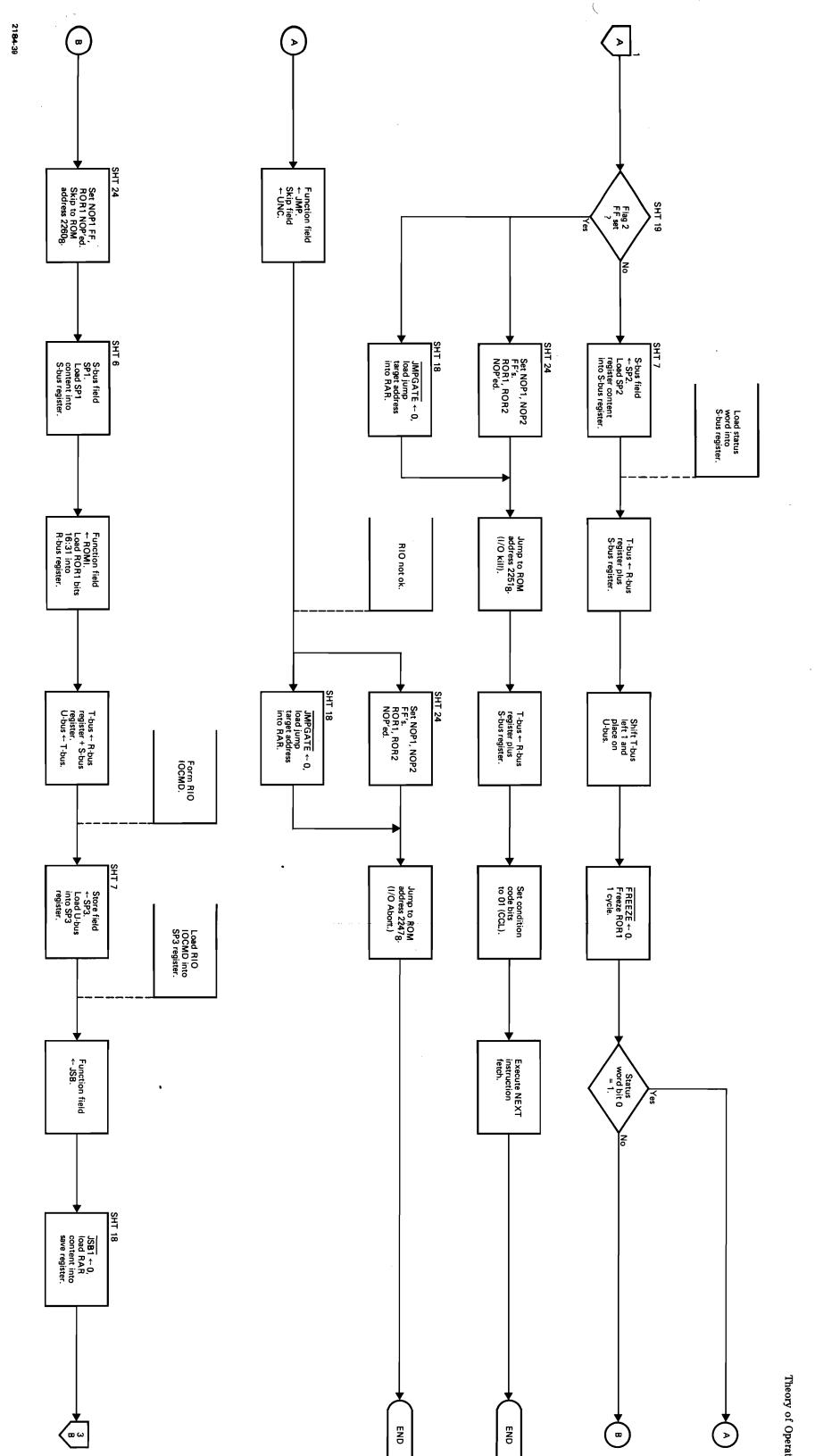

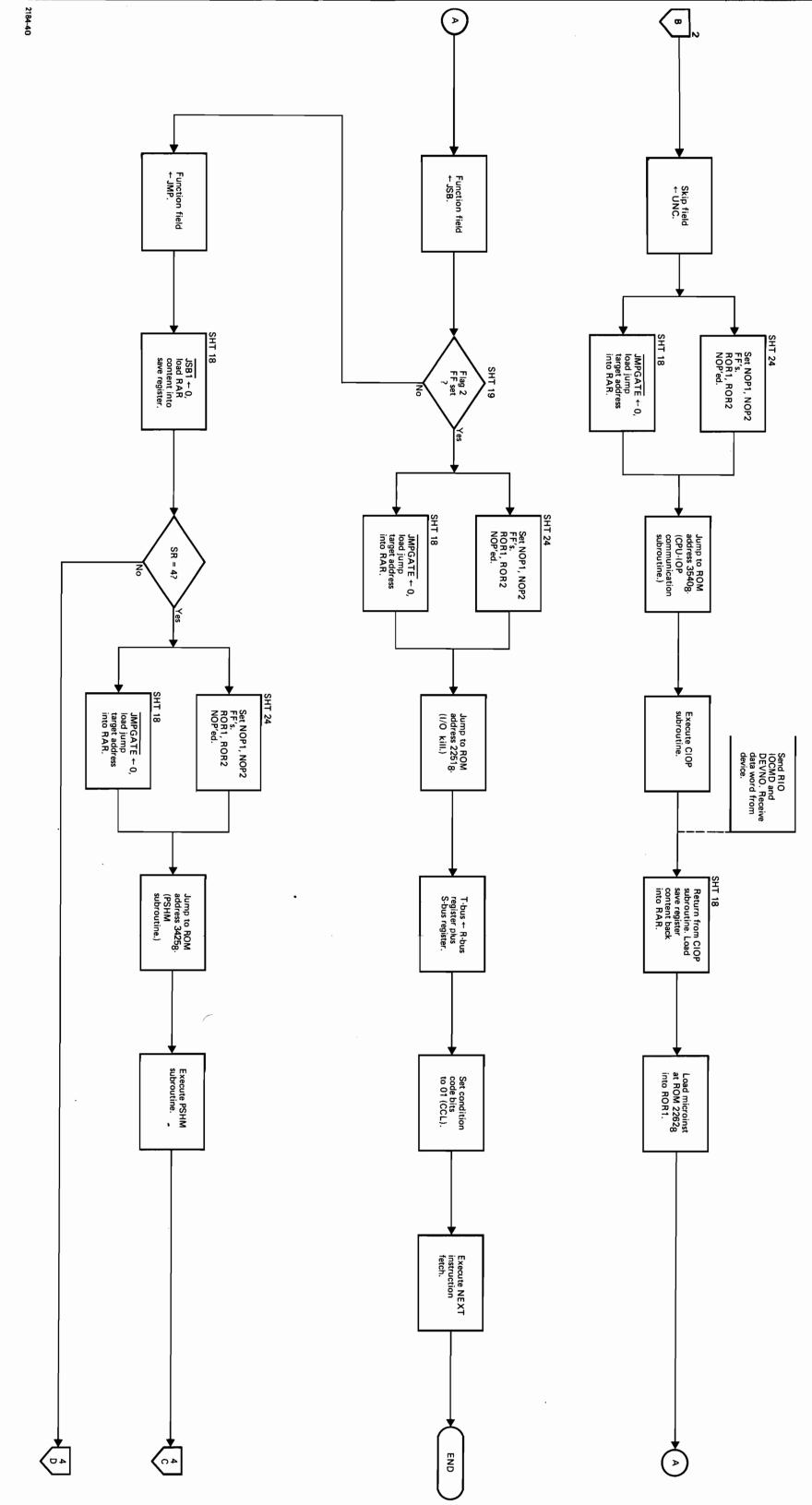

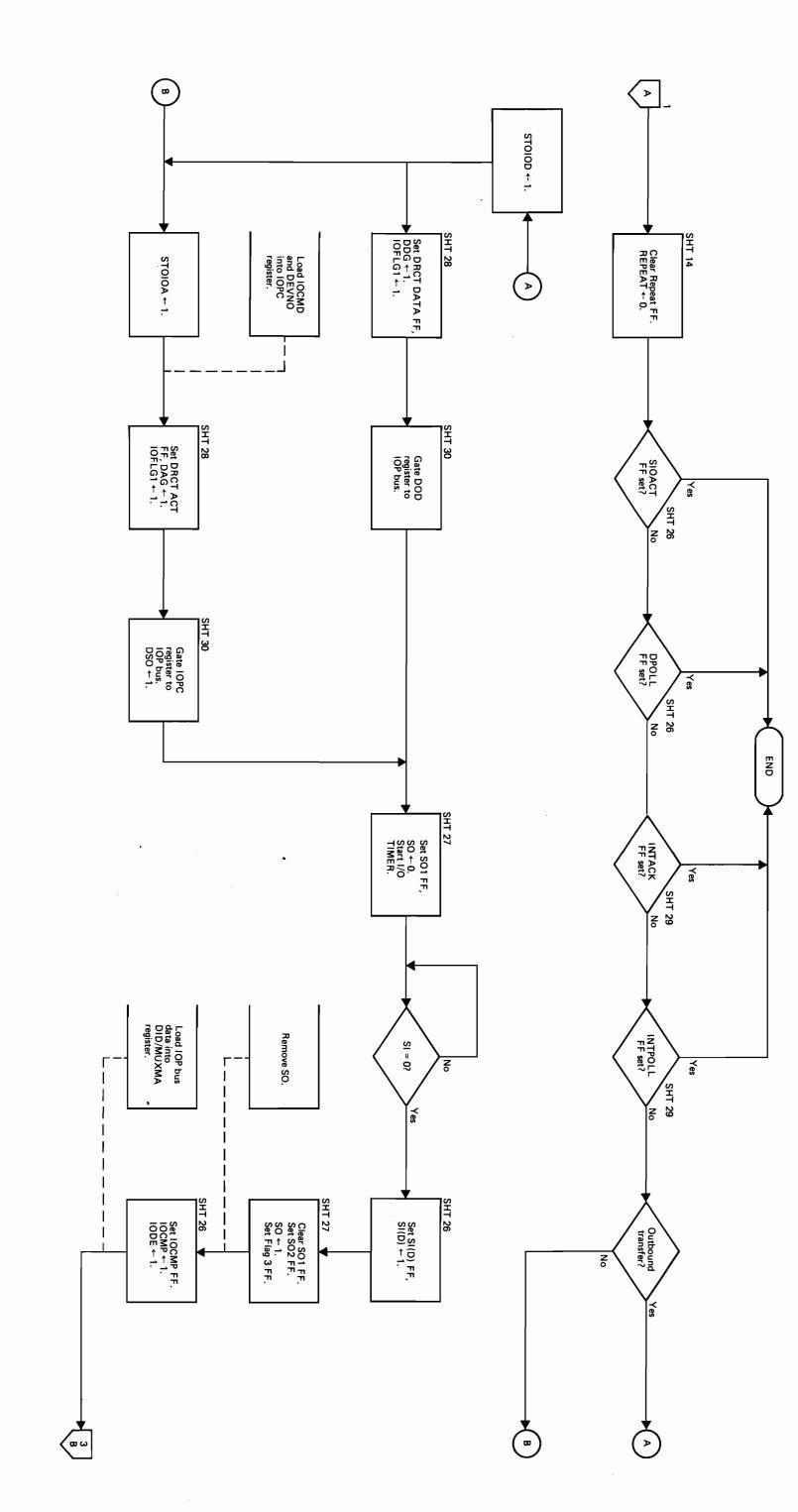

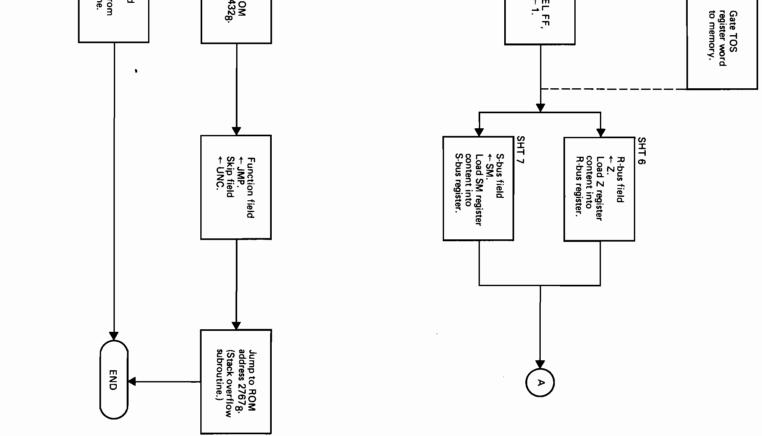

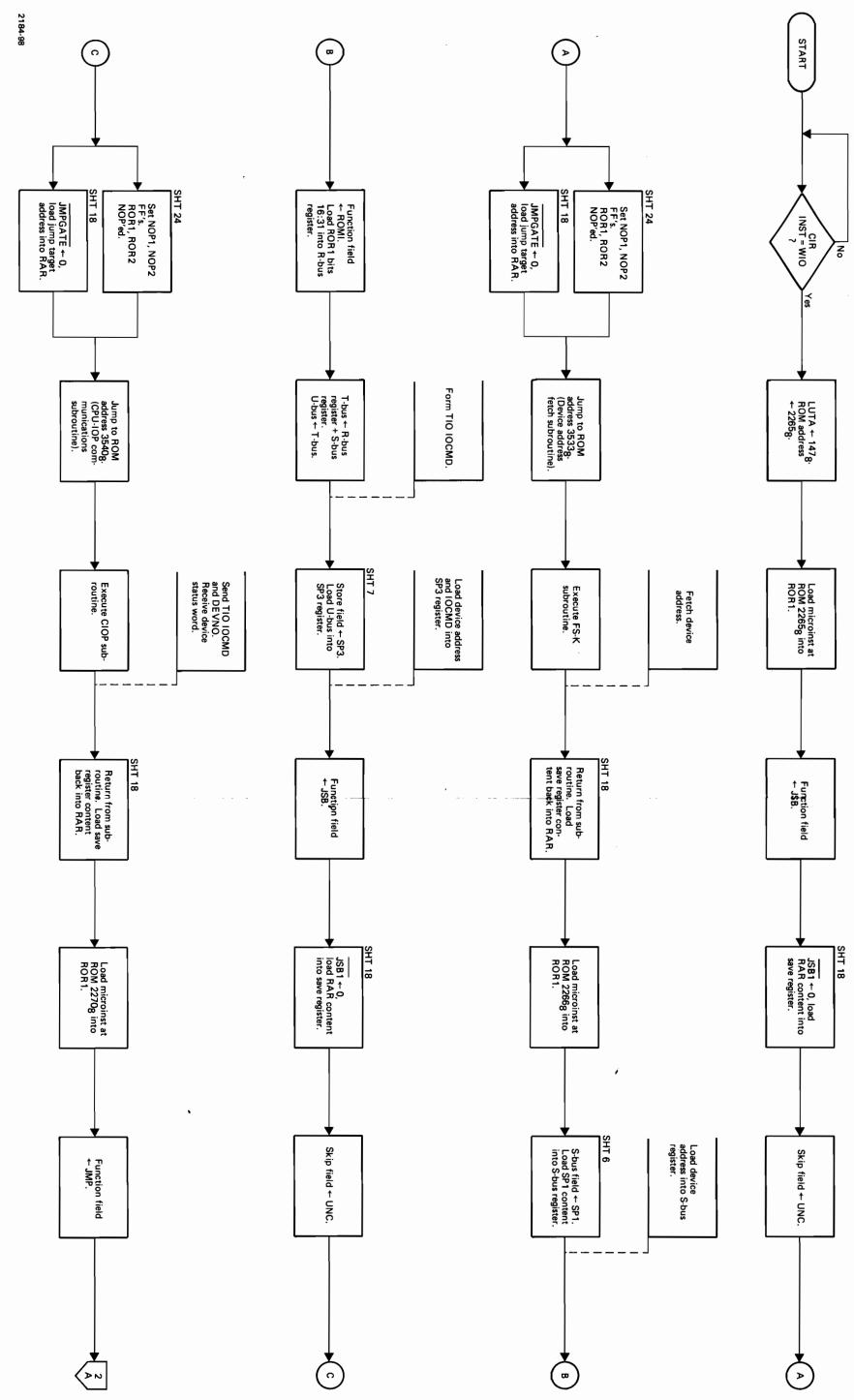

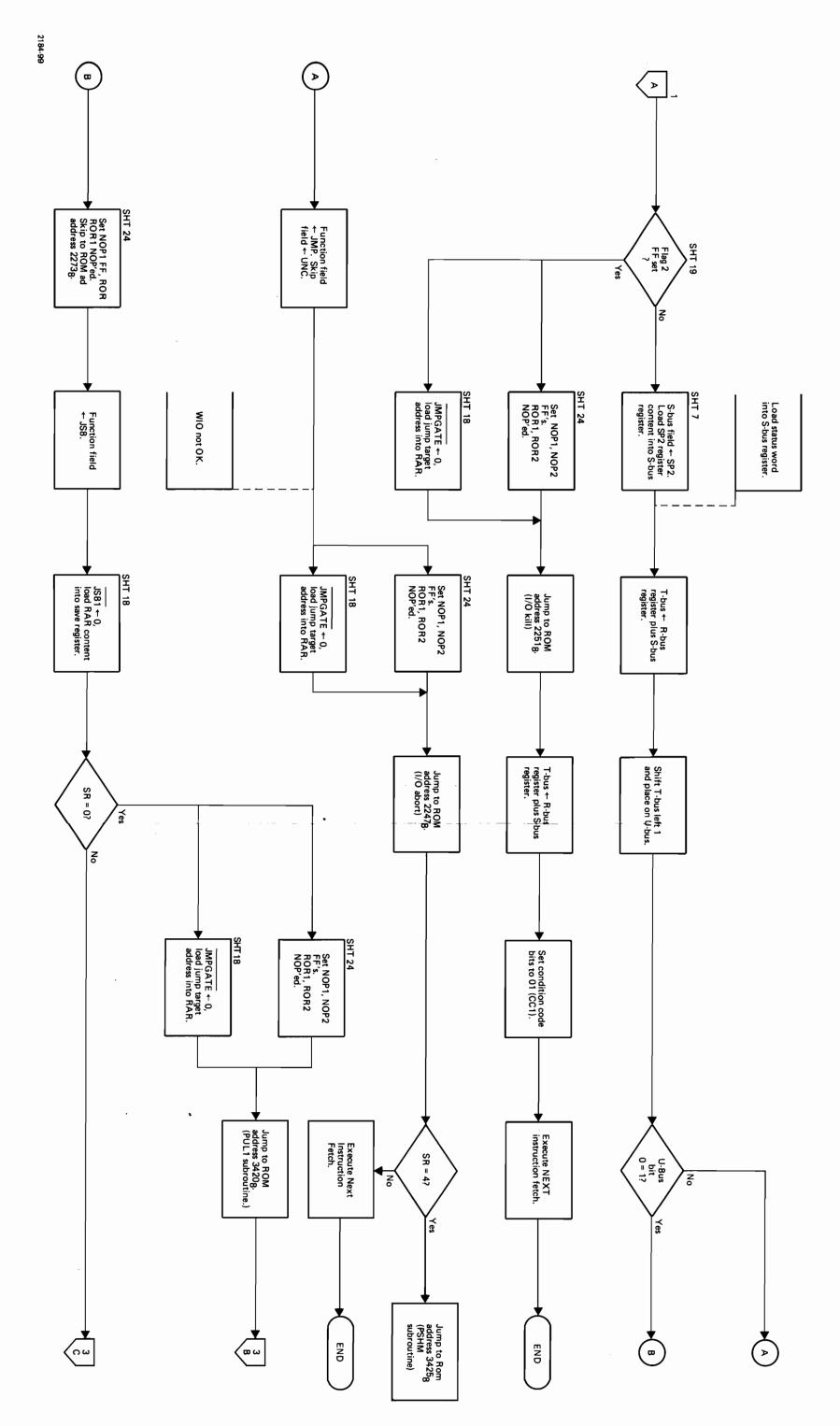

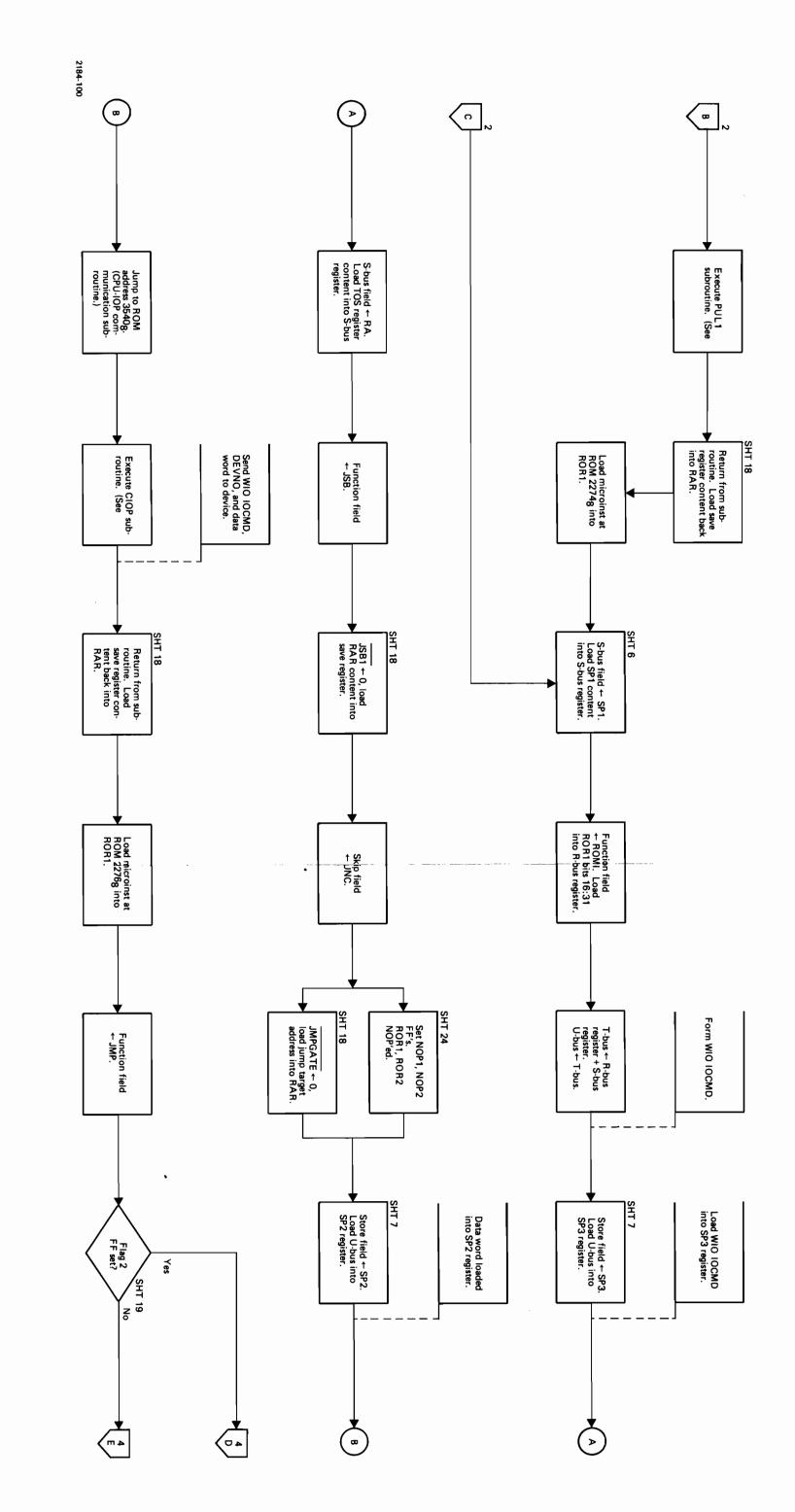

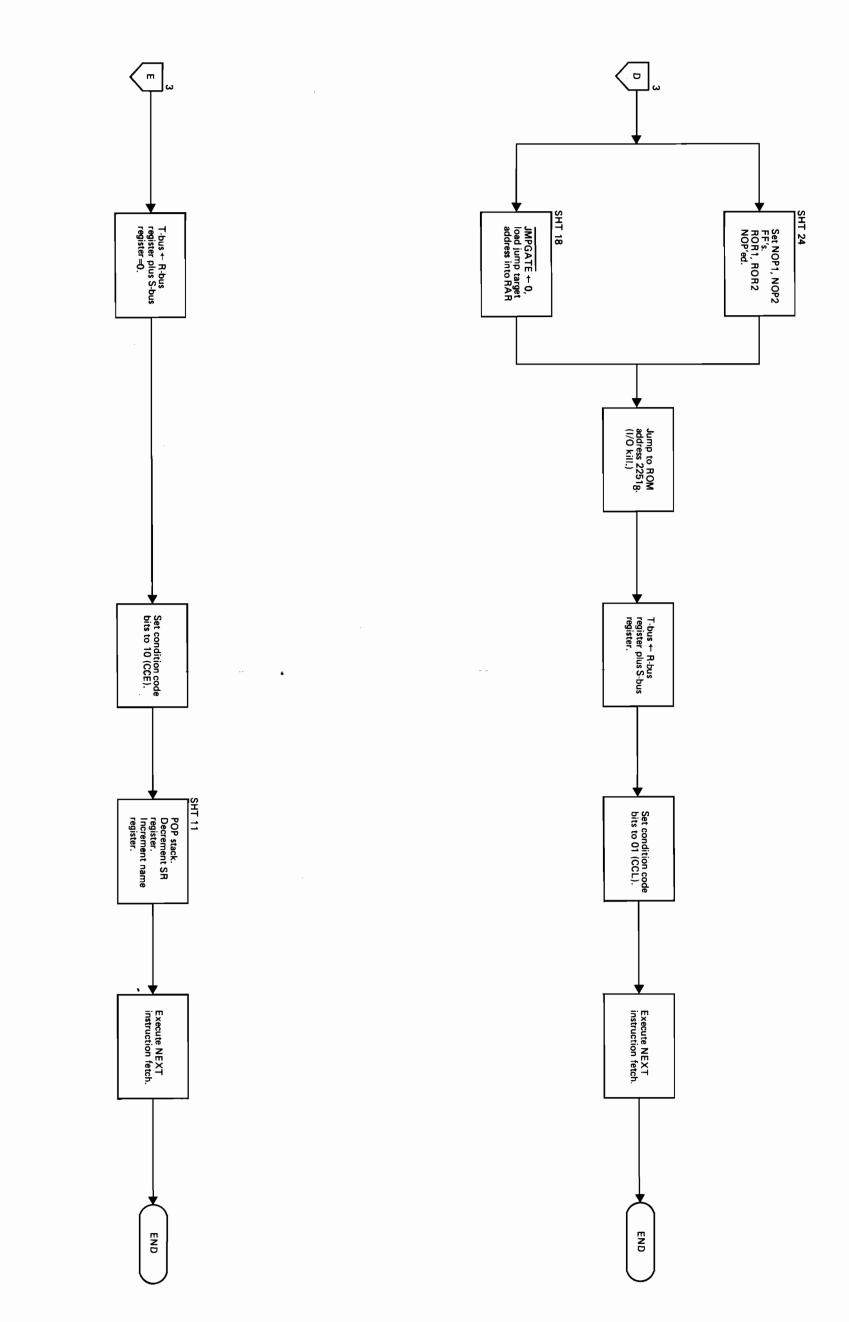

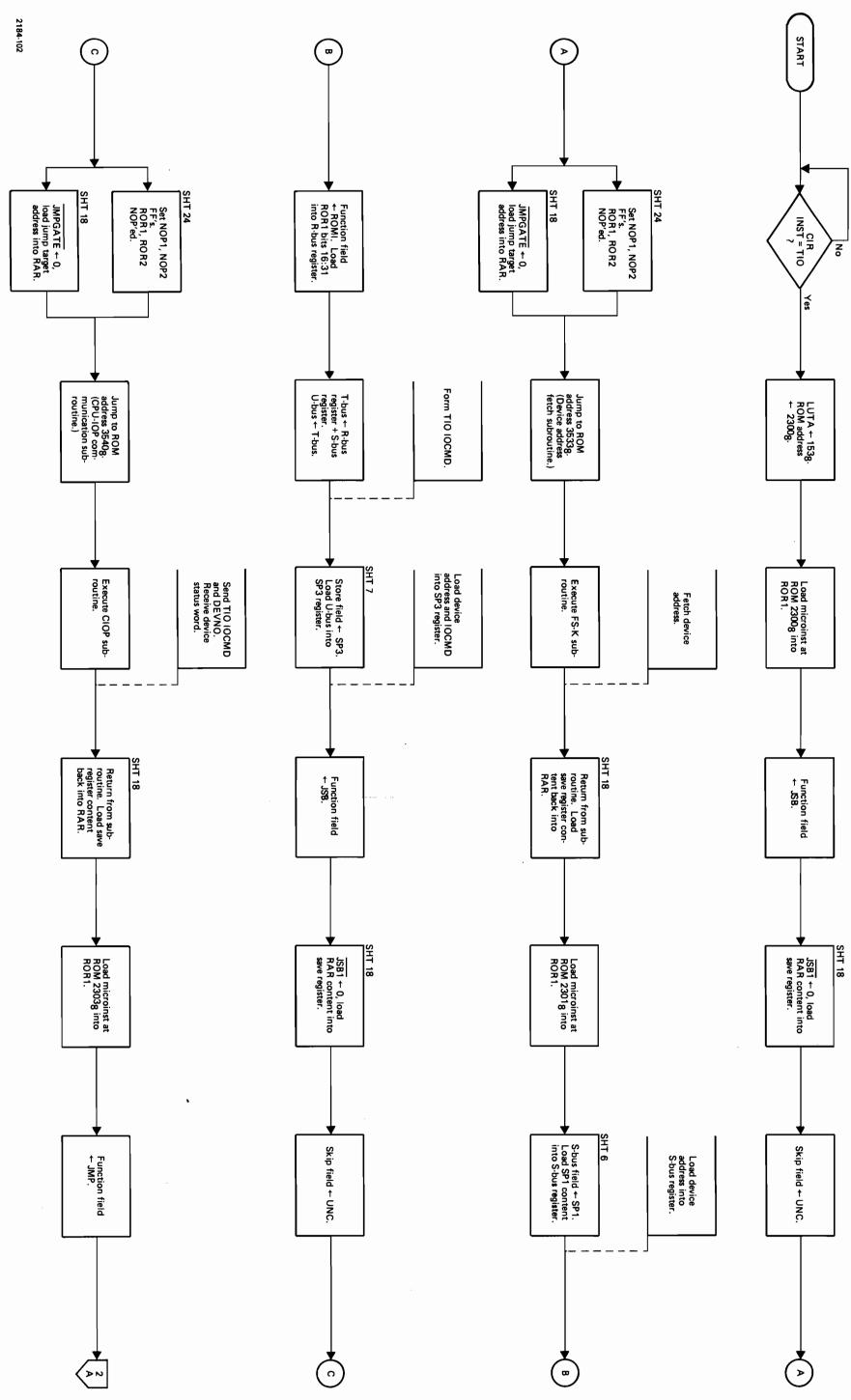

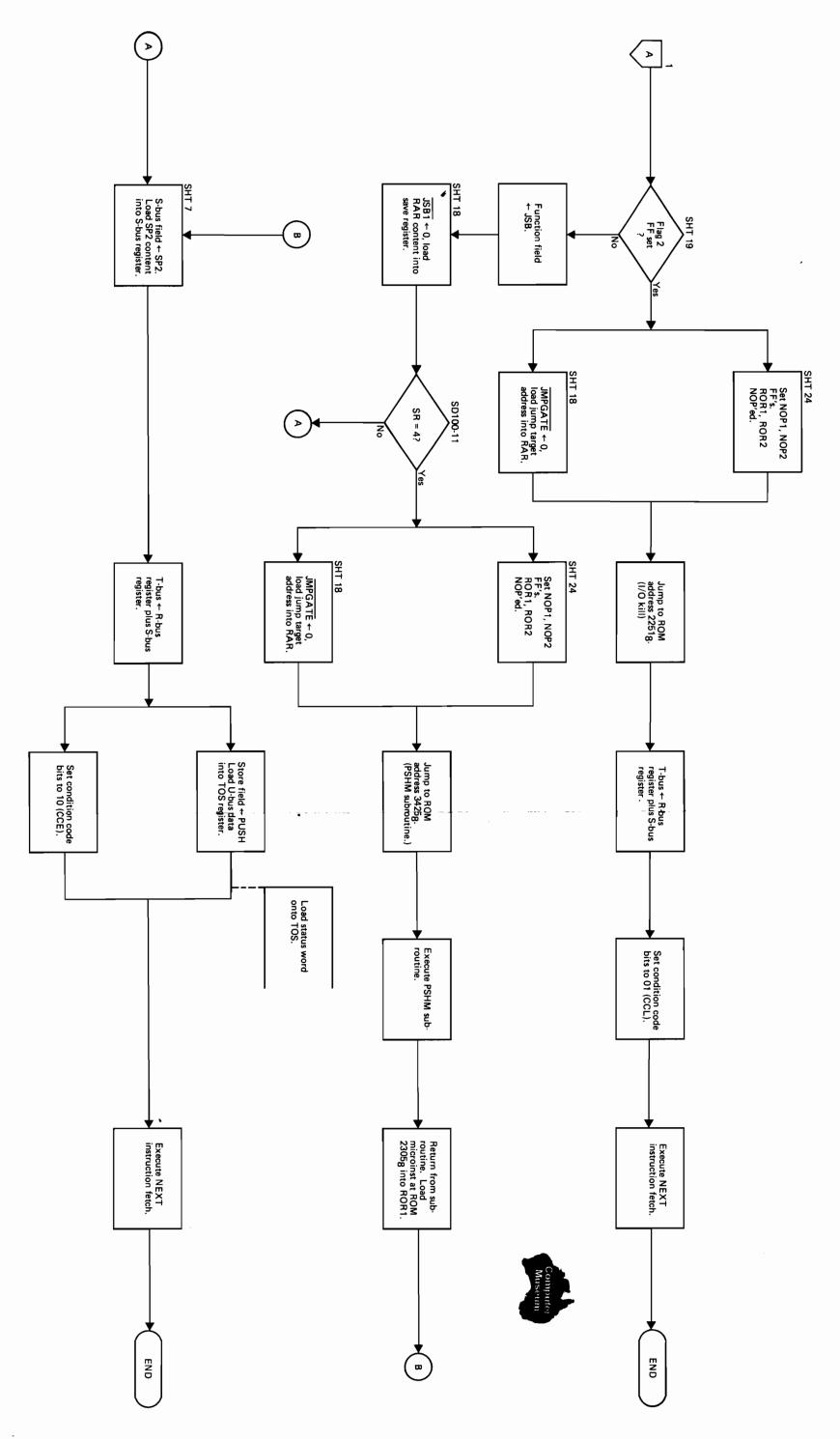

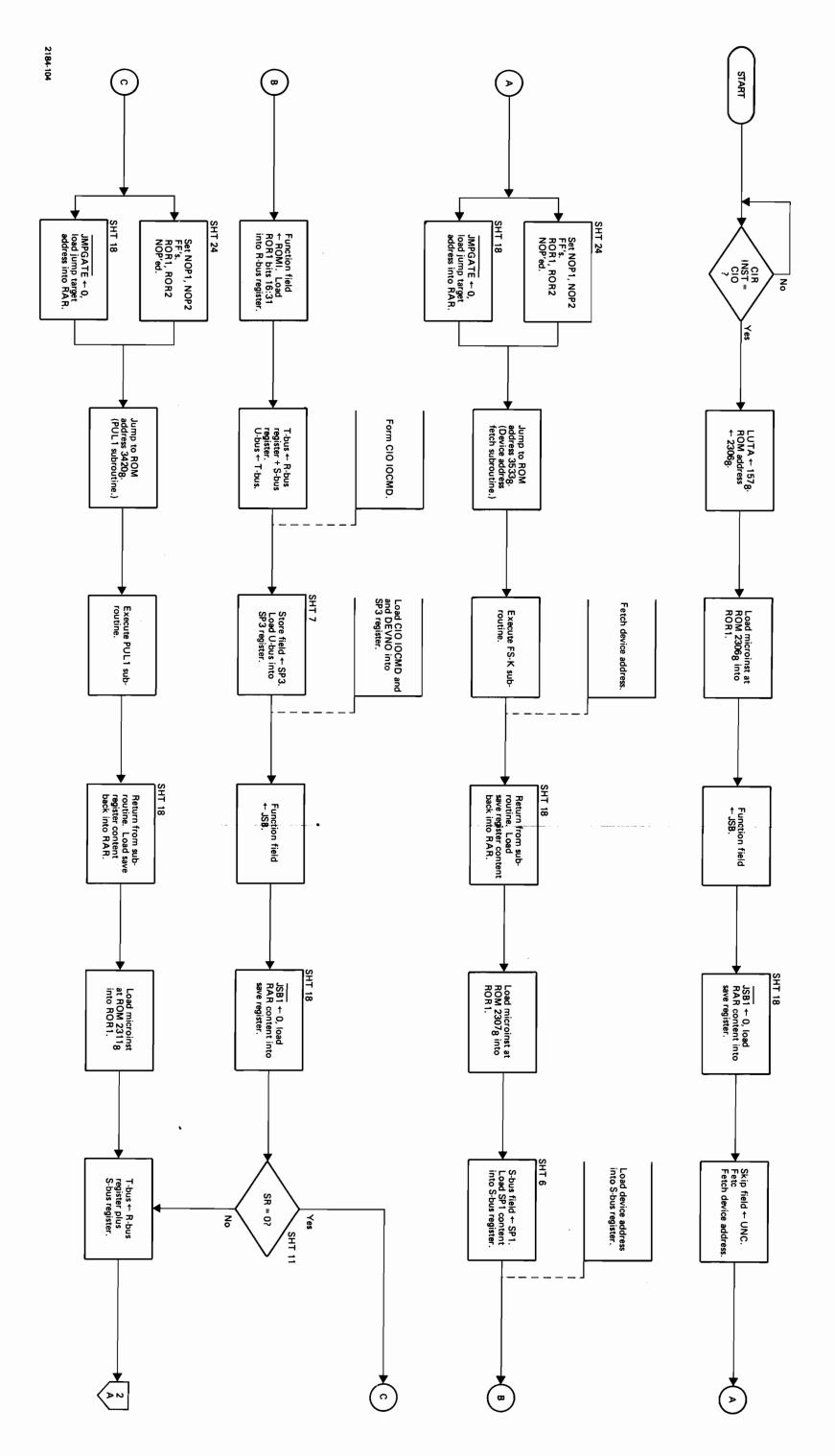

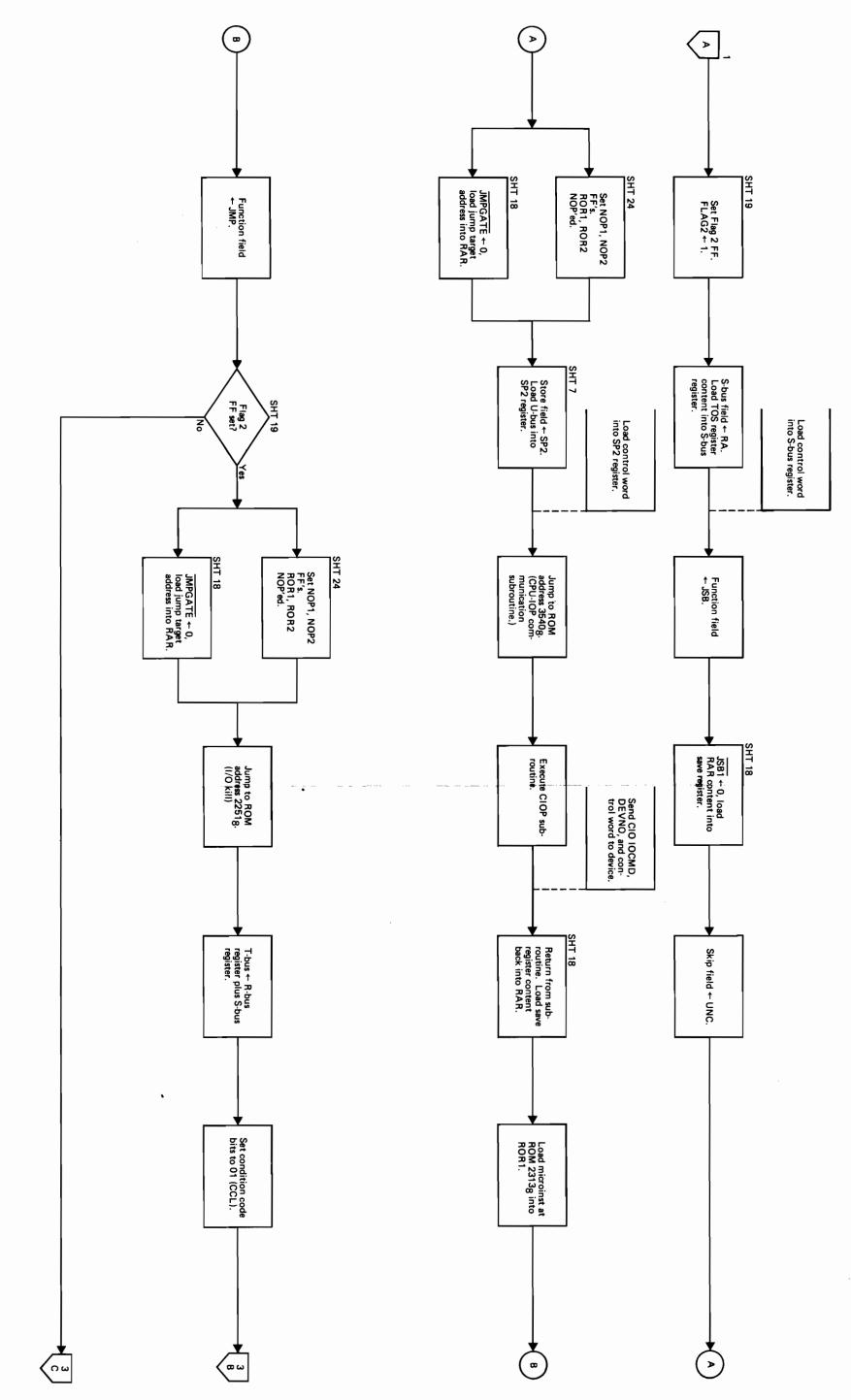

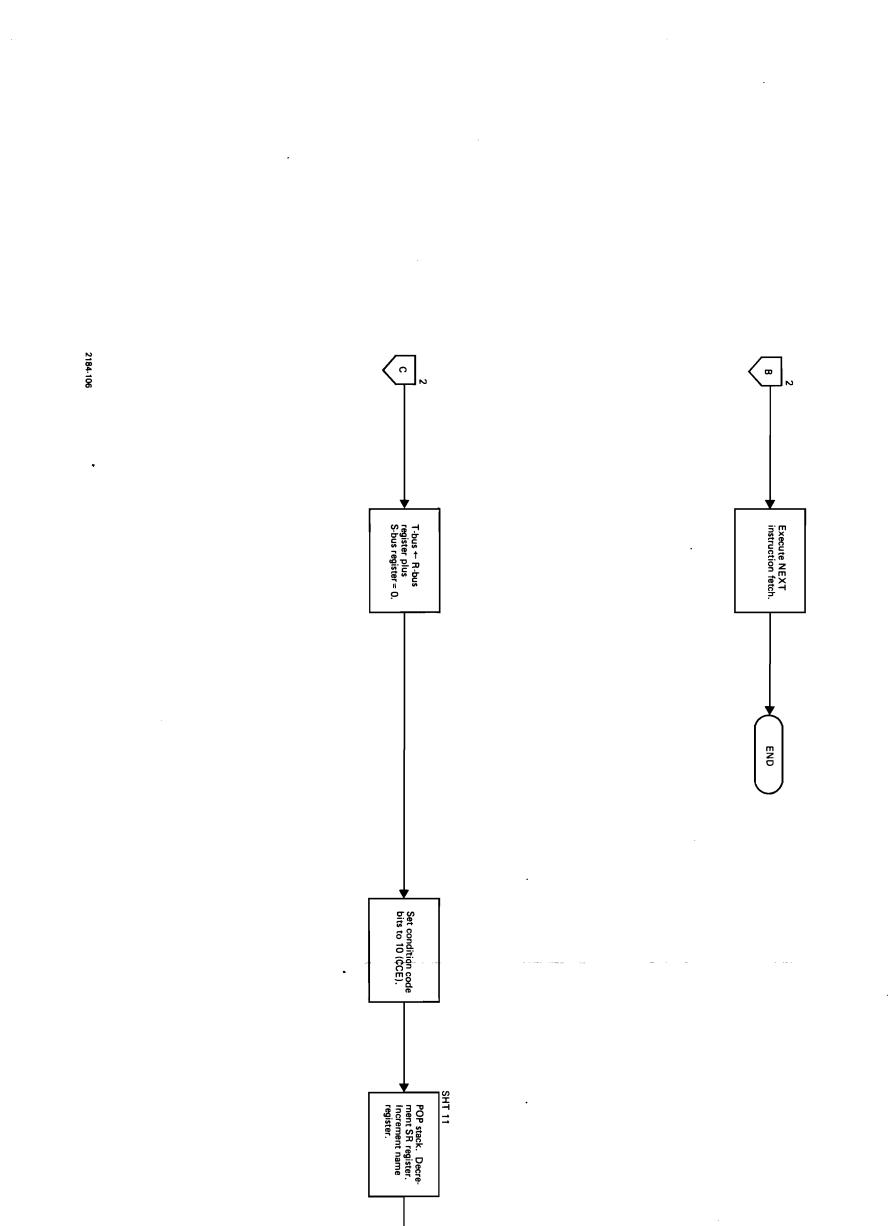

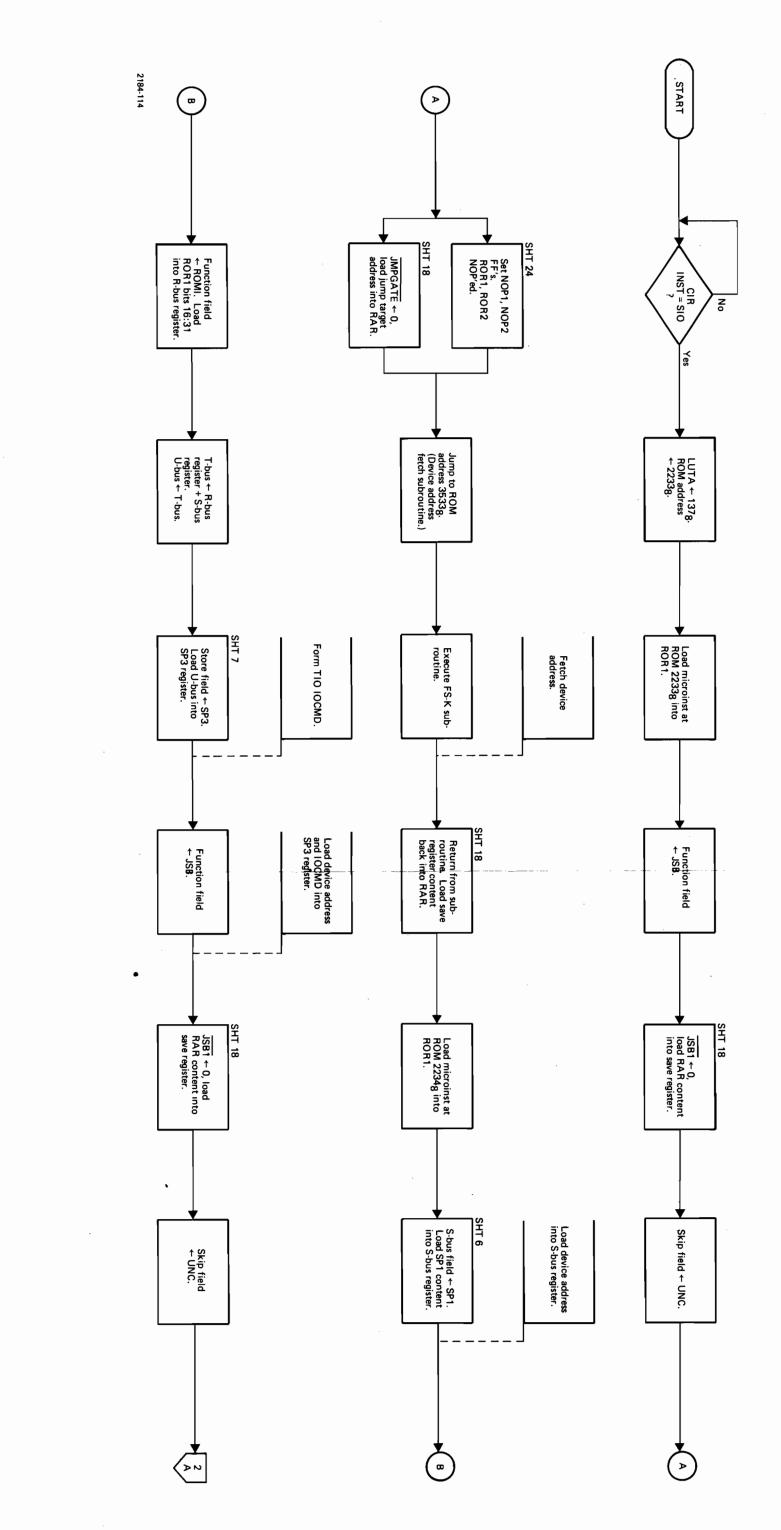

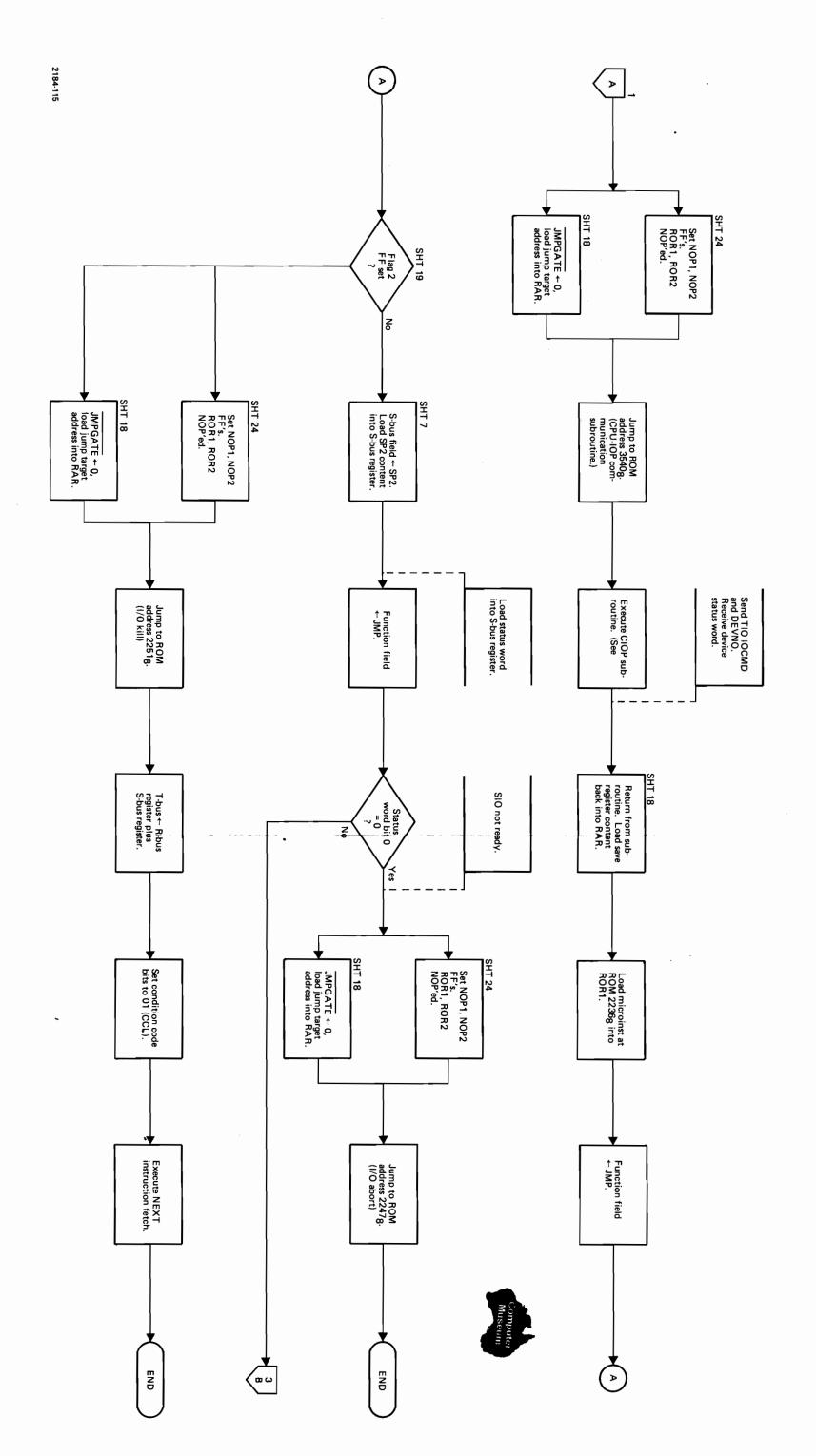

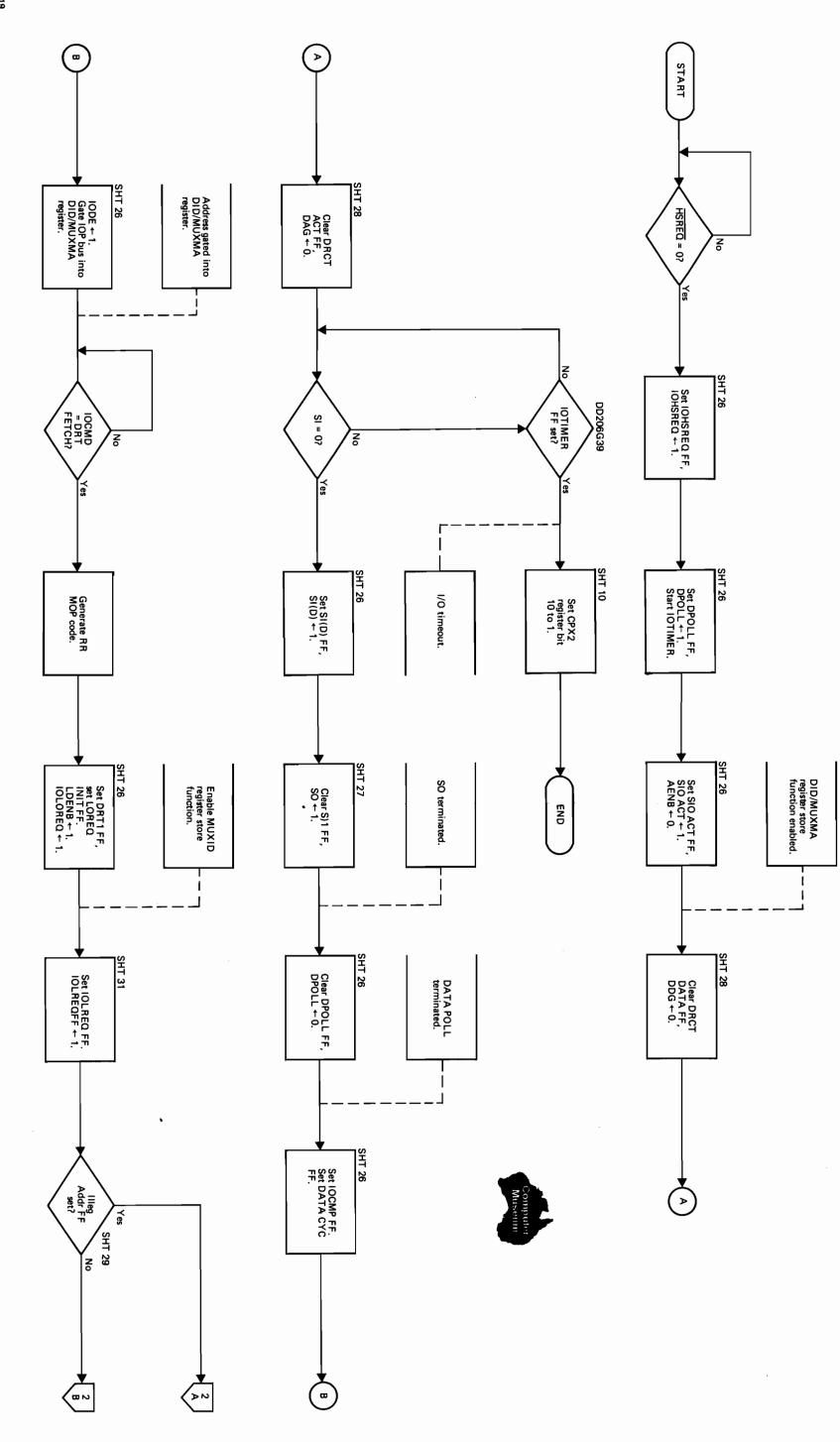

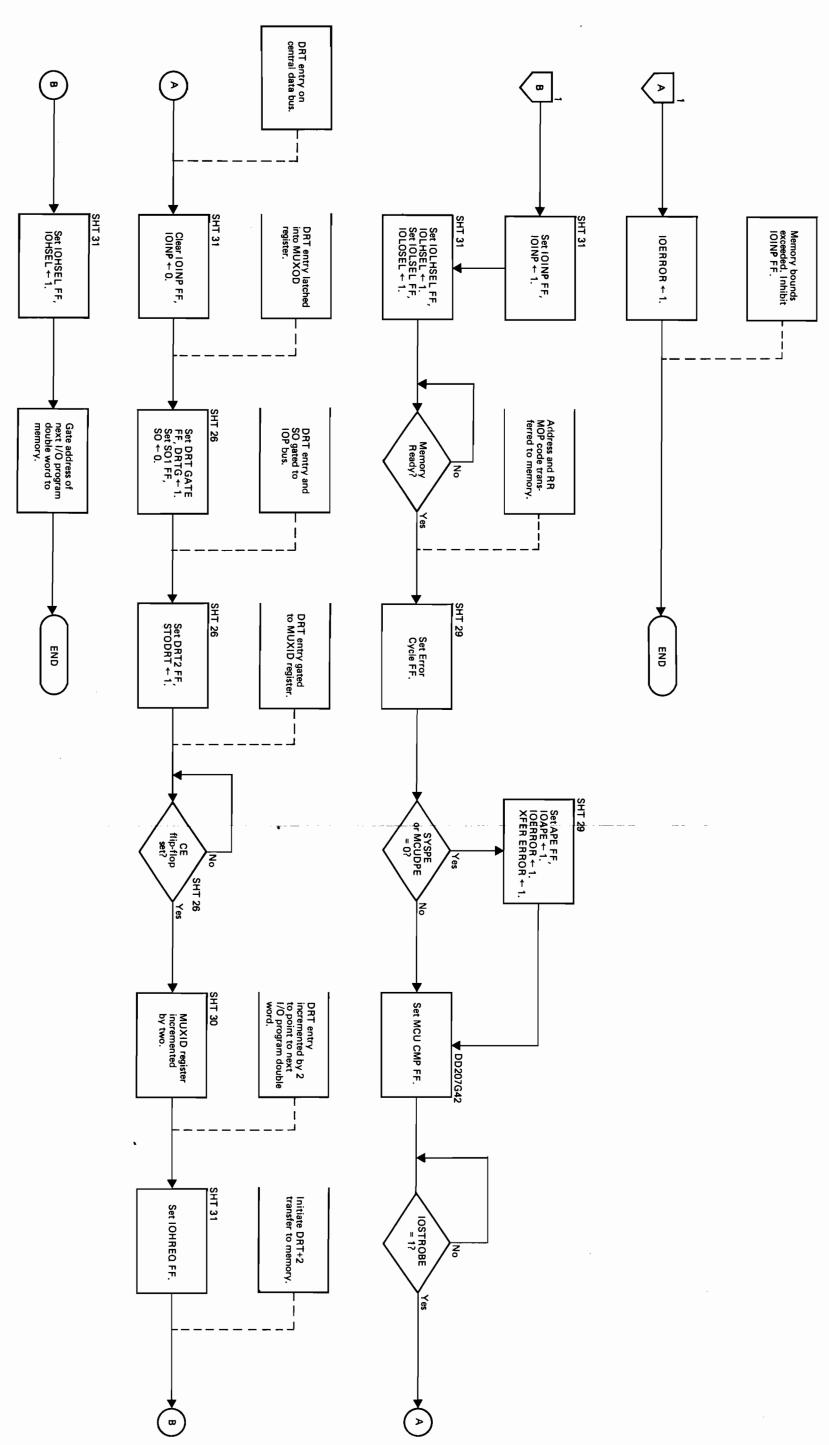

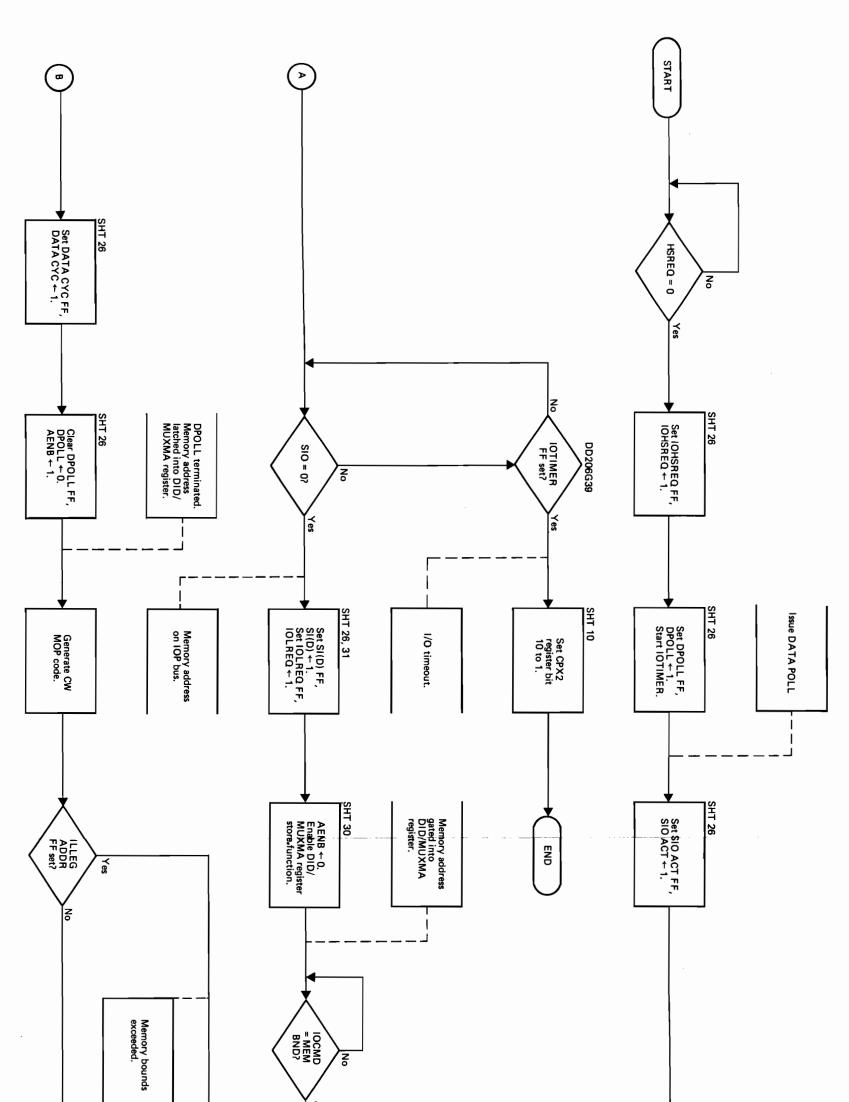

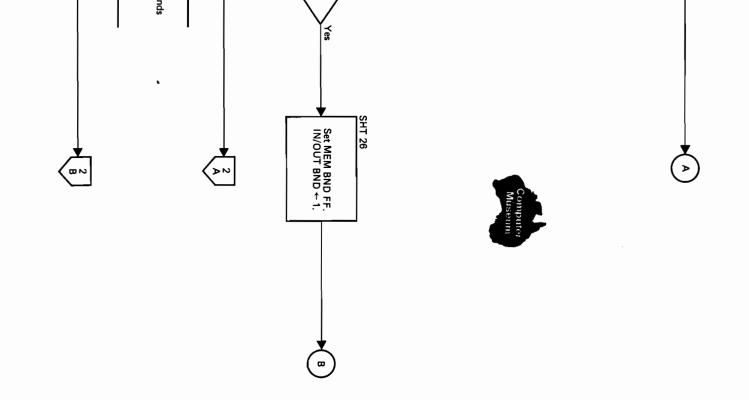

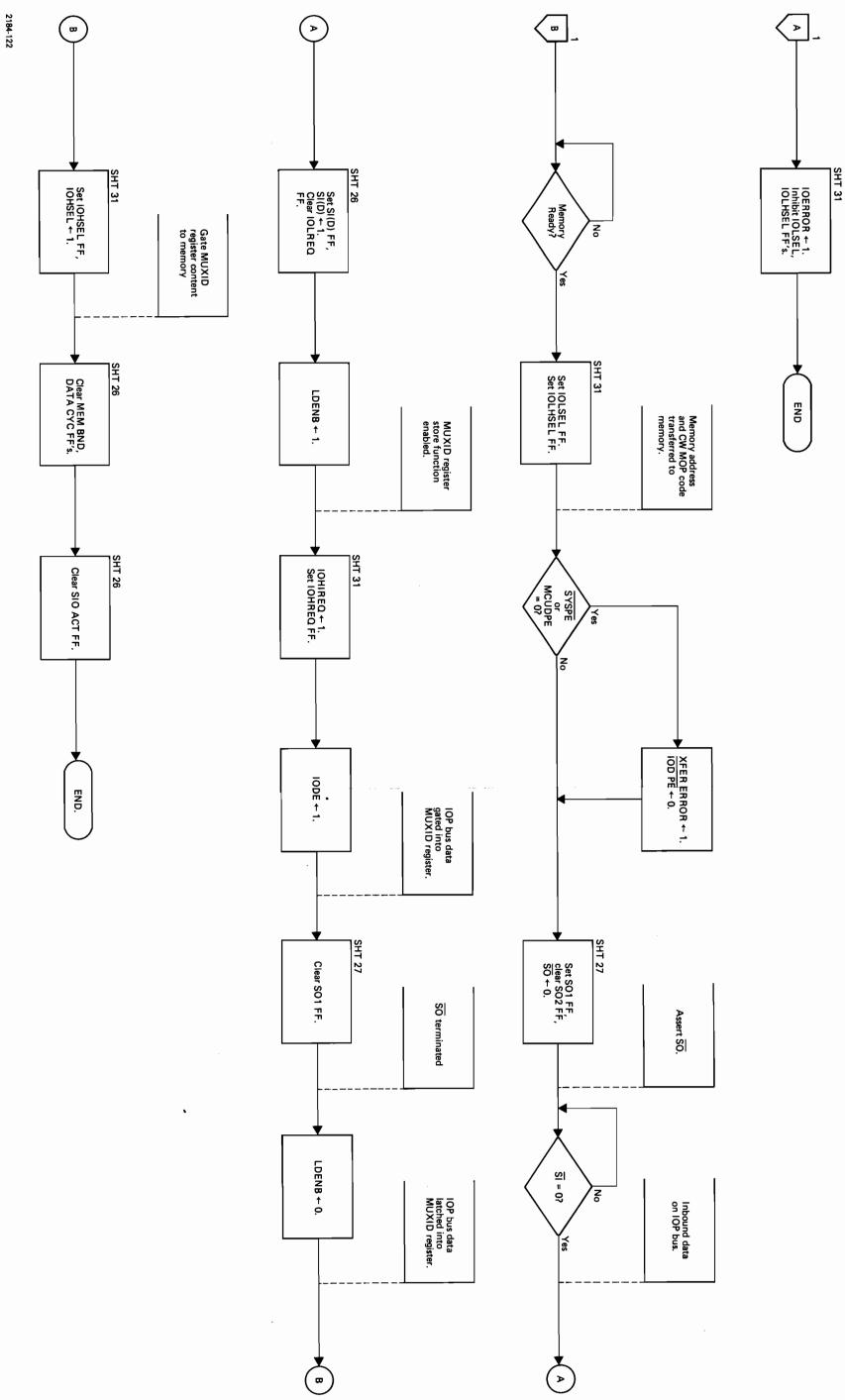

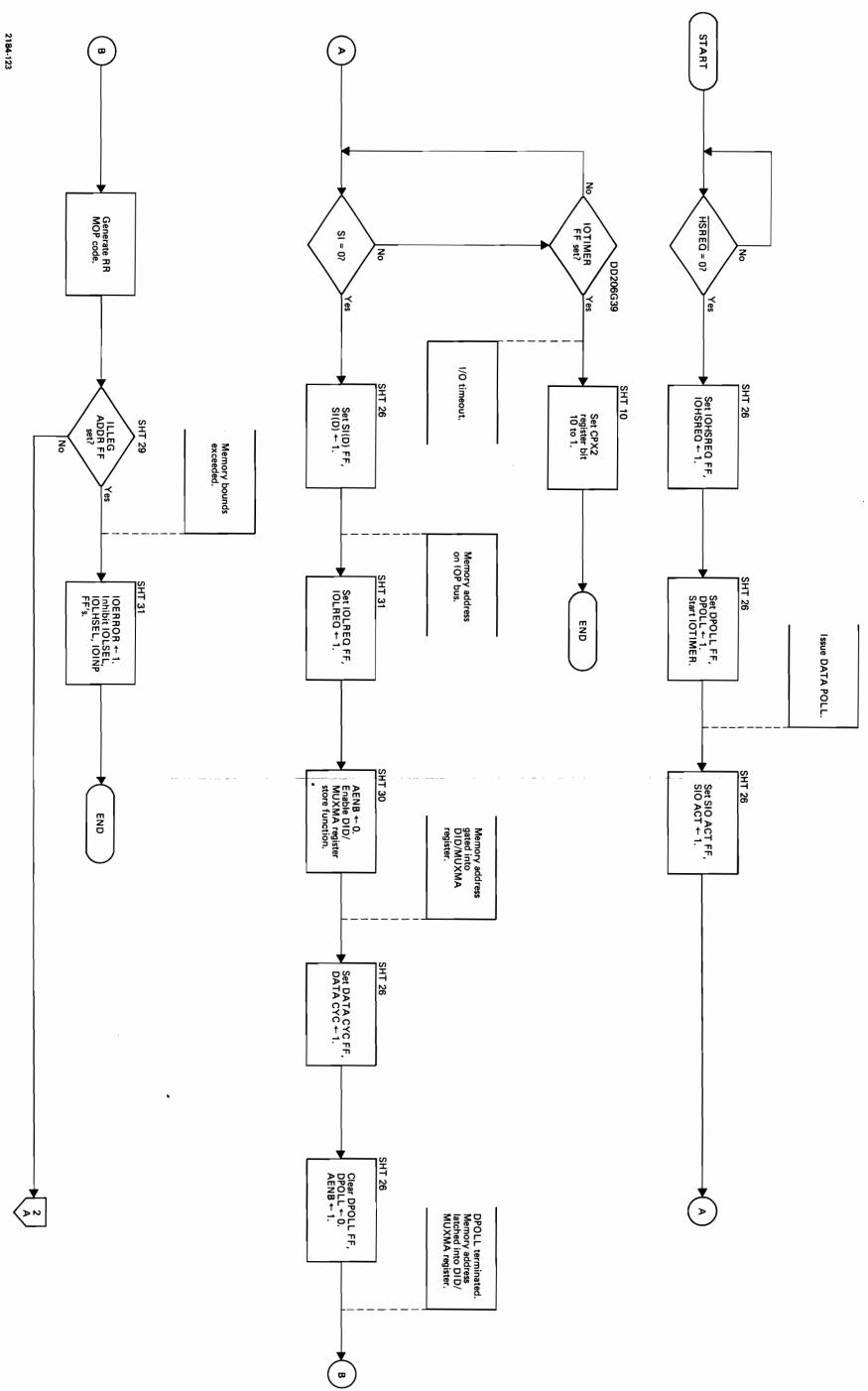

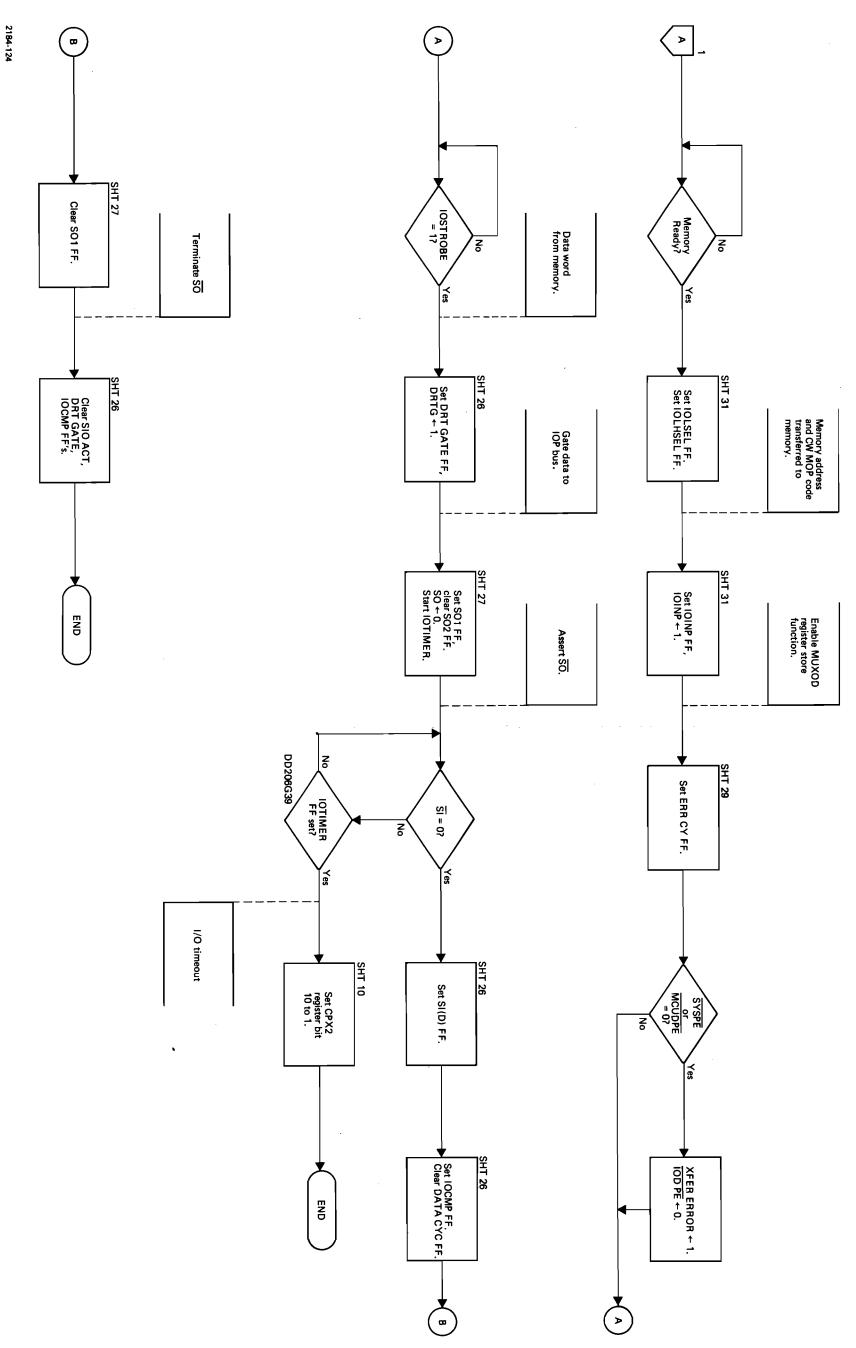

| 3-205.<br>3-207.<br>3-257. | Operand Store         3-51           Direct I/O         3-51           Programmed I/O         3-57 |

|----------------------------|----------------------------------------------------------------------------------------------------|

|                            |                                                                                                    |

|                            | TENANCE                                                                                            |

| 4-1.                       | Introduction                                                                                       |

| 4-4.                       | General Servicing Information                                                                      |

| <b>4-6</b> .               | Safety Precautions                                                                                 |

| 4-8.                       | Wiring Information                                                                                 |

| 4-10.                      | CPU/IOP Signals and Mnemonics                                                                      |

| 4-12.                      | Test Equipment and Data Required                                                                   |

| 4-14.                      | Preventive Maintenance                                                                             |

| 4-16.                      | Troubleshooting                                                                                    |

| 4-18.                      | On-Line Diagnostics                                                                                |

| 4-21.                      | Stand-Alone Diagnostic                                                                             |

| 4-23.                      | Microdiagnostics                                                                                   |

## **ILLUSTRATIONS**

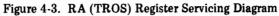

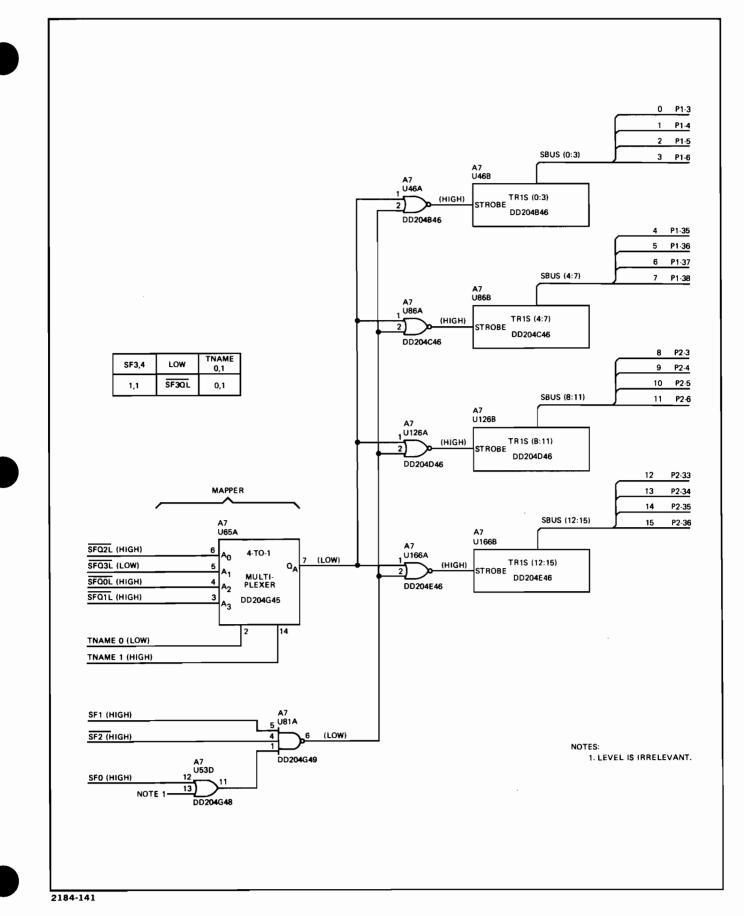

| Figure                                       | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                             |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

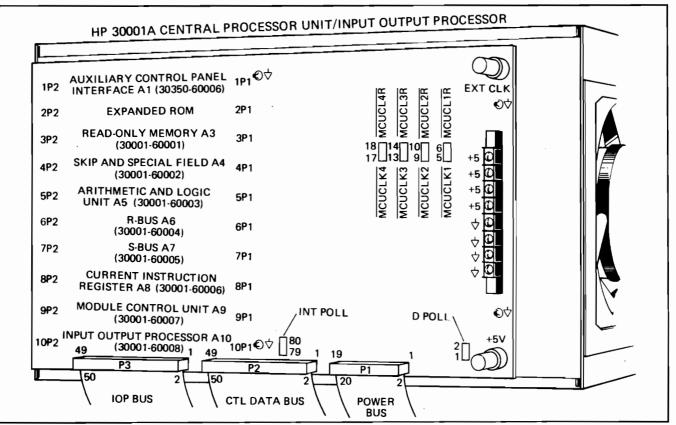

| 1-1.<br>1-2.<br>1-3.<br>1-4.<br>1-5.<br>1-6. | HP 30001A Central Processor Unit/Input Output Processor       Read-Only Memory Printed-Circuit Assembly A3, Part No. 30001-60001       Skip and Special Field Printed-Circuit Assembly A4, Part No. 30001-60002         Arithmetic and Logic Unit Printed-Circuit Assembly A5, Part No. 30001-60003       R-Bus Printed-Circuit Assembly A6, Part No. 30001-60004       Semultical Content of the semulti | . 1-3<br>. 1-4<br>. 1-5<br>. 1-6 |

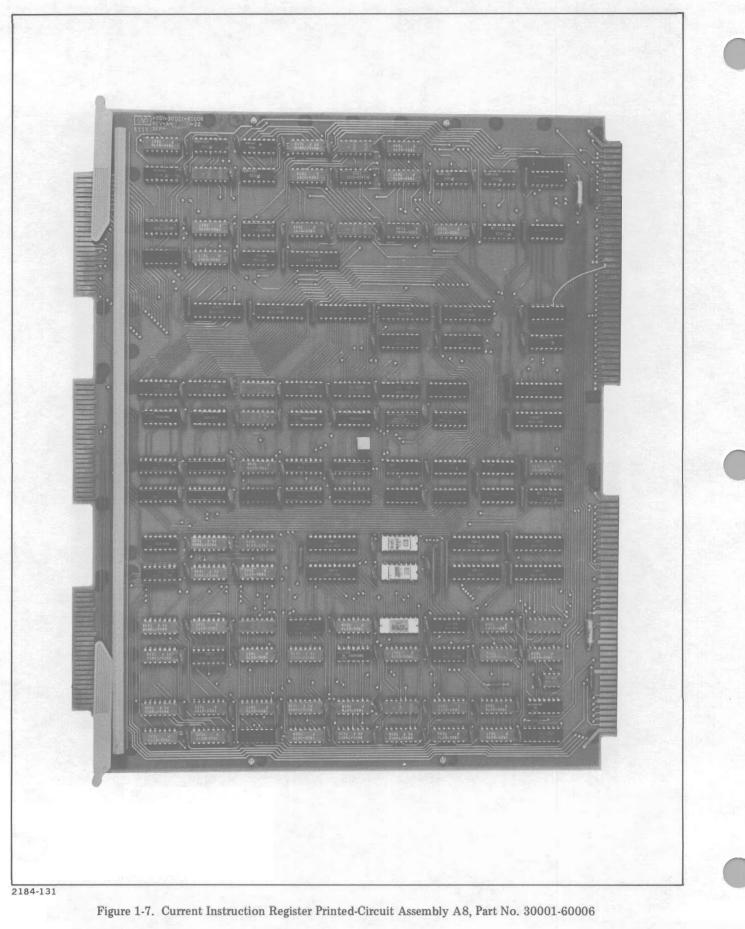

| 1-7.                                         | Current Instruction Register Printed-Circuit Assembly A8, Part No. 30001-60006                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |

| 1-8.                                         | Module Control Unit Printed-Circuit Assembly A9, Part No. 30001-60007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                  |

| 1-9.                                         | Input Output Processor Printed-Circuit Assembly A10, Part No. 30001-60008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-10                             |

| 1-10.                                        | Central Data Bus Terminator Printed-Circuit Assembly, Part No. 30001-60009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-11                             |

| 1-11.                                        | Input Output Processor Bus Terminator Printed-Circuit Assembly,<br>Part No. 30001-60016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-12                             |

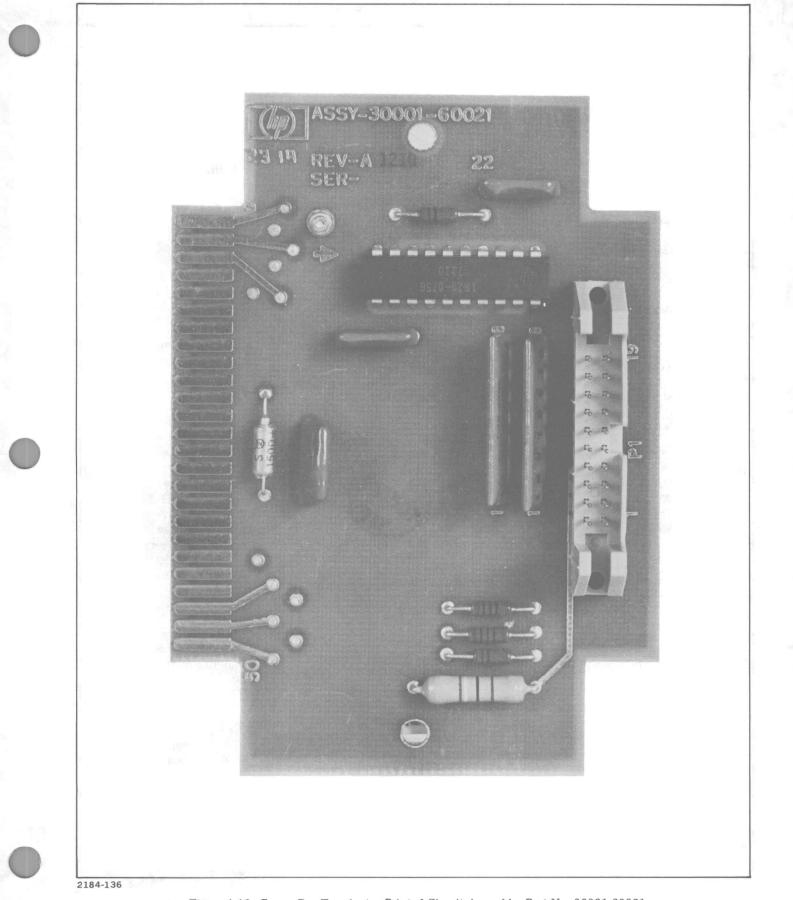

| 1-12.                                        | Power Bus Terminator Printed-Circuit Assembly, Part No. 30001-60021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |

| 2-1.                                         | Instruction Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |

| 2-2.                                         | Consolidated Microinstruction Coding Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                  |

| 2-3.                                         | Microinstruction Word Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

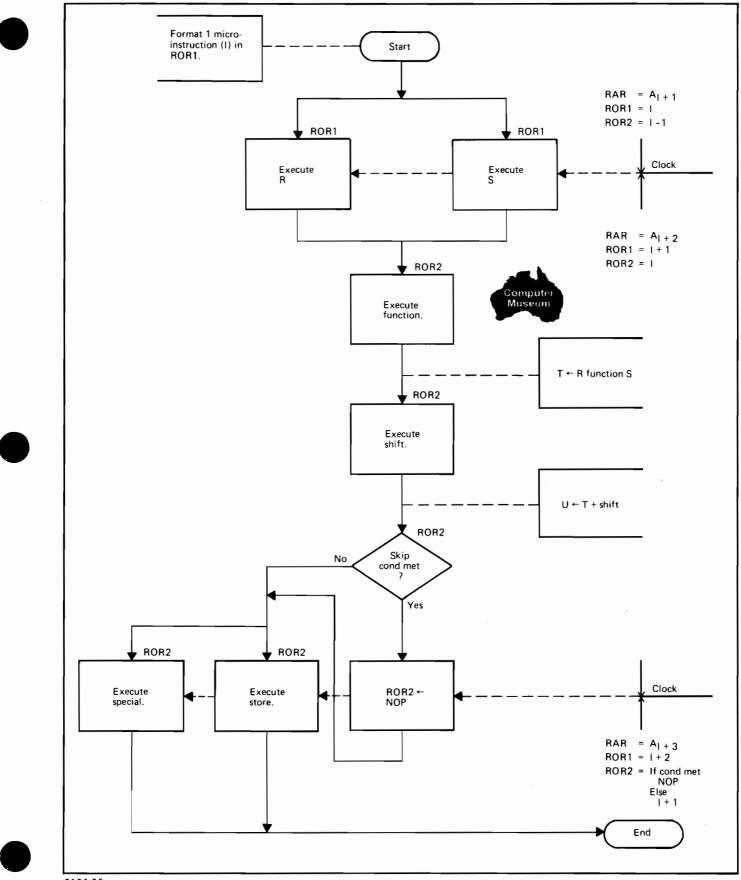

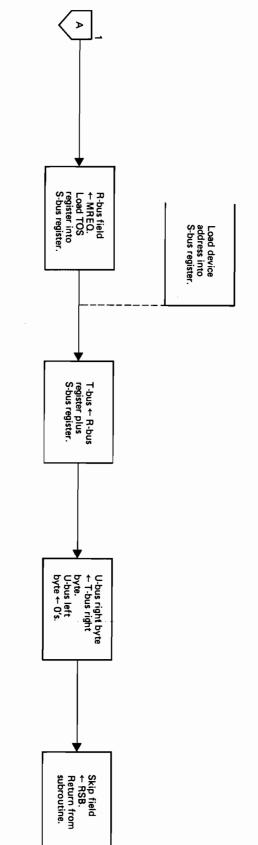

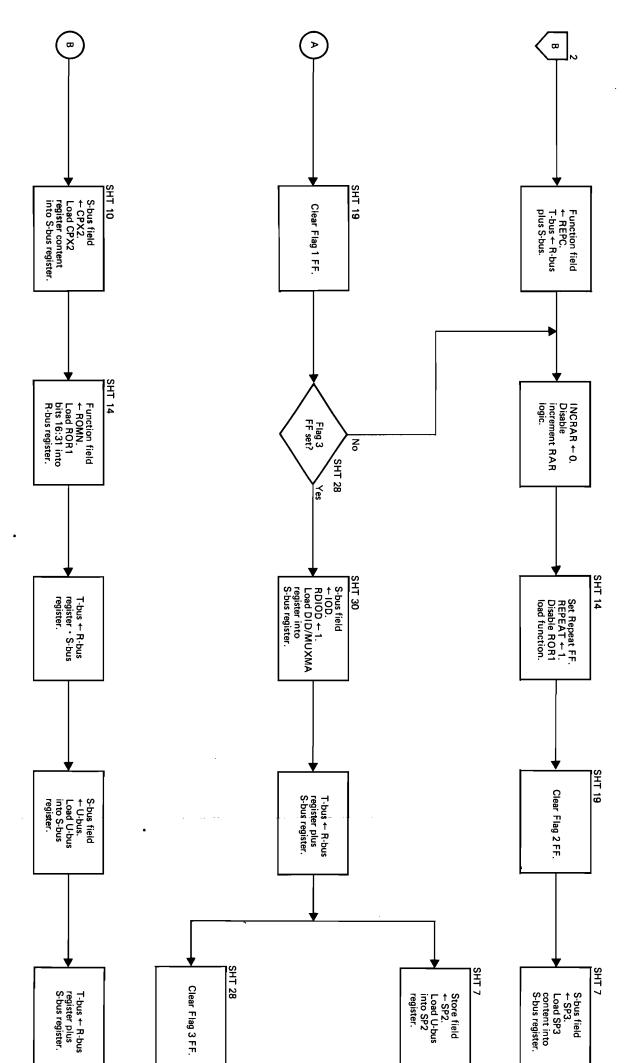

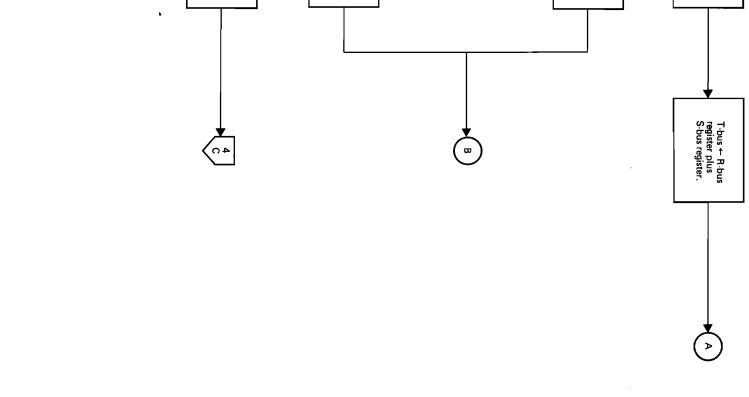

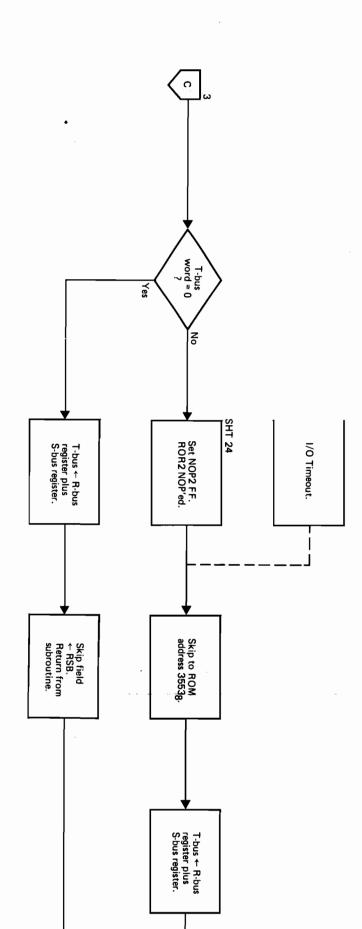

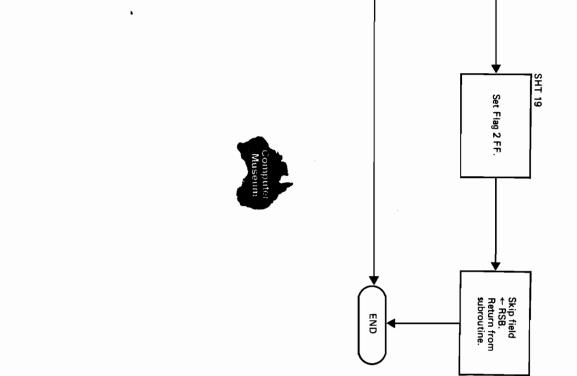

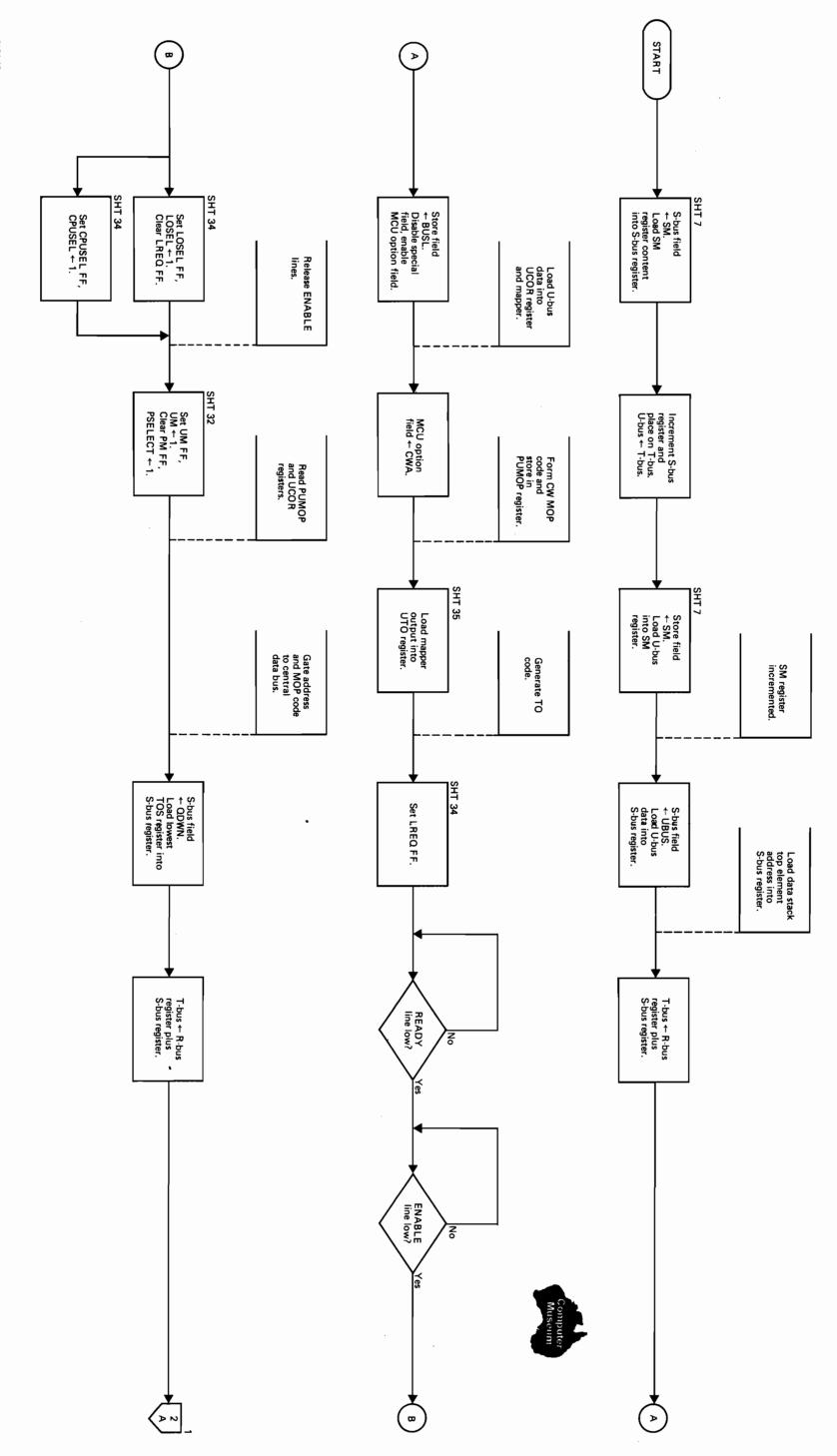

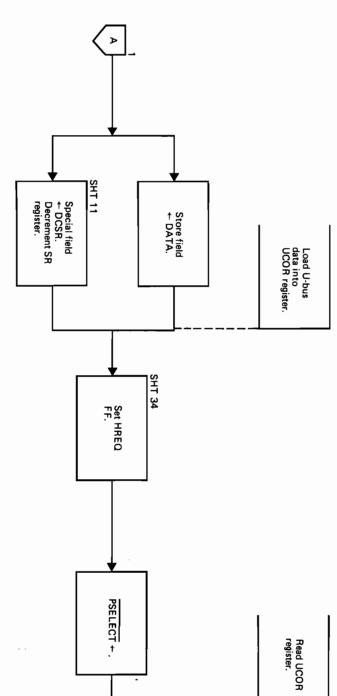

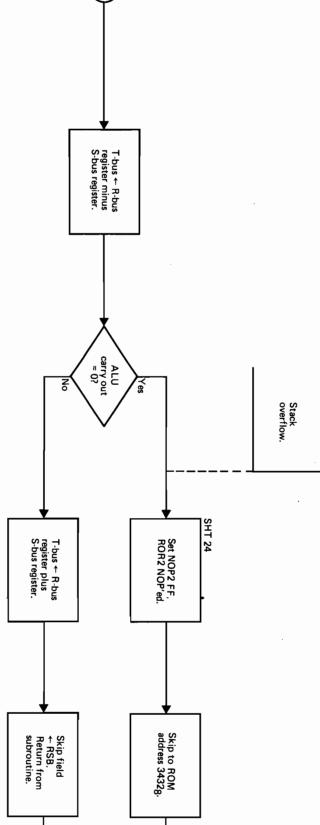

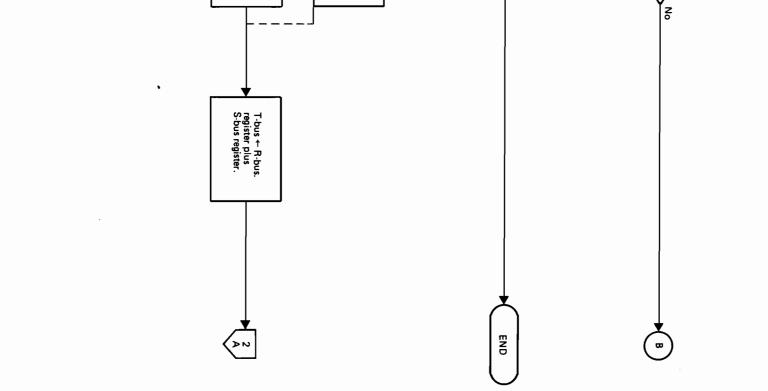

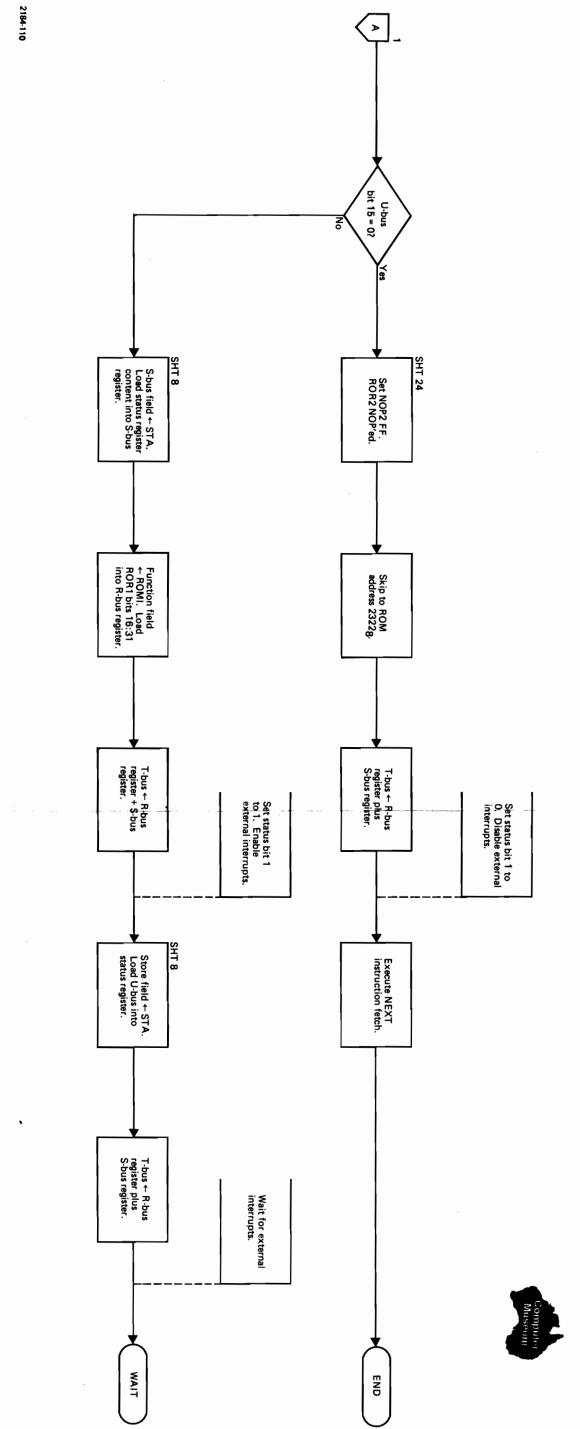

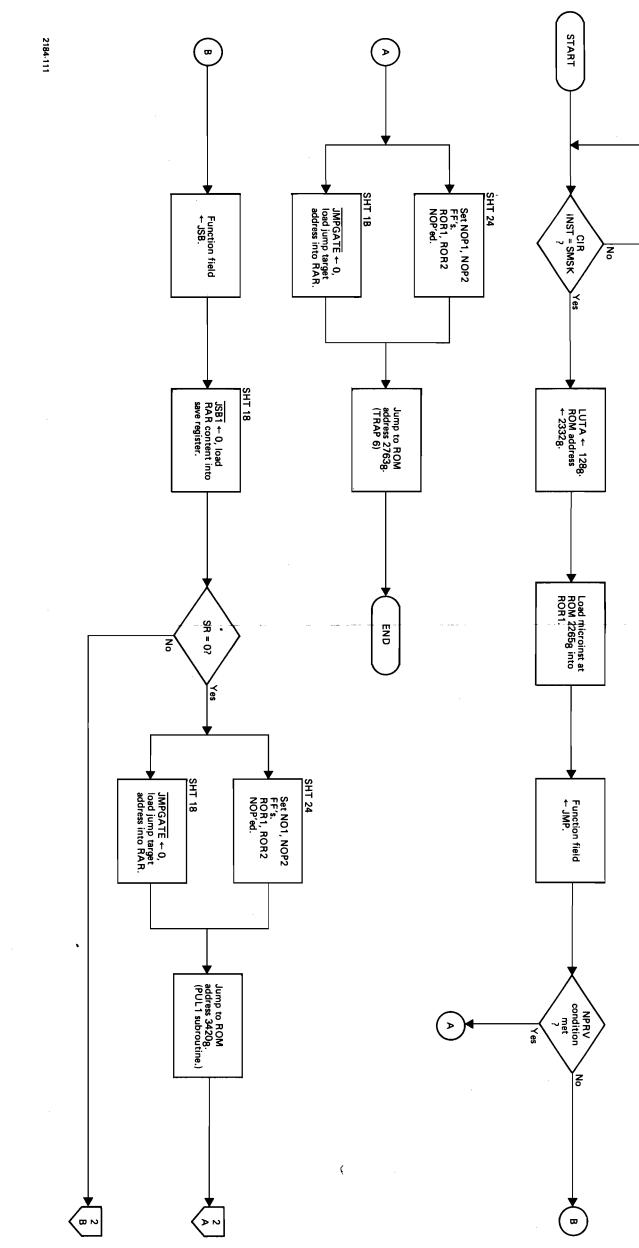

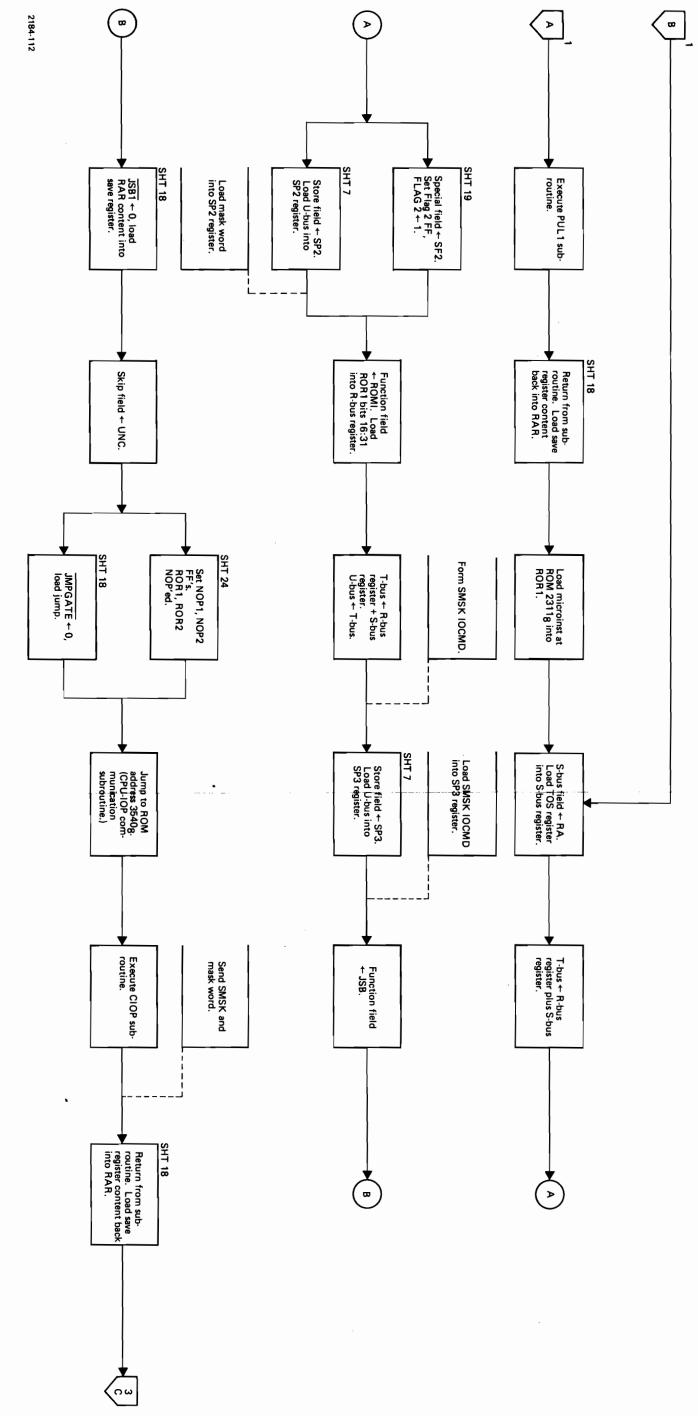

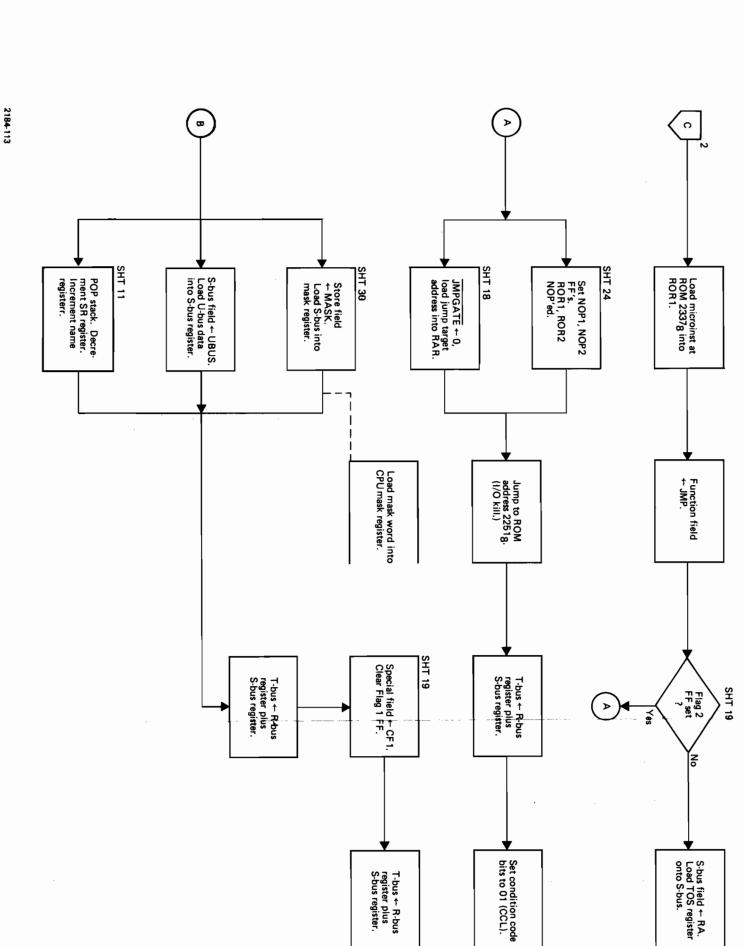

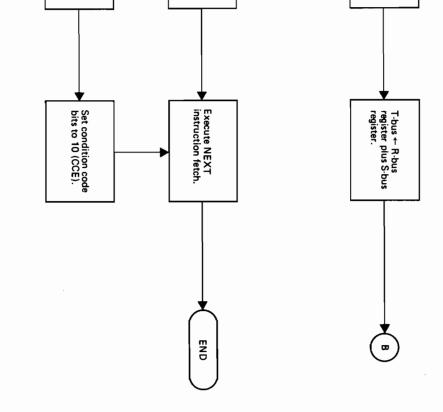

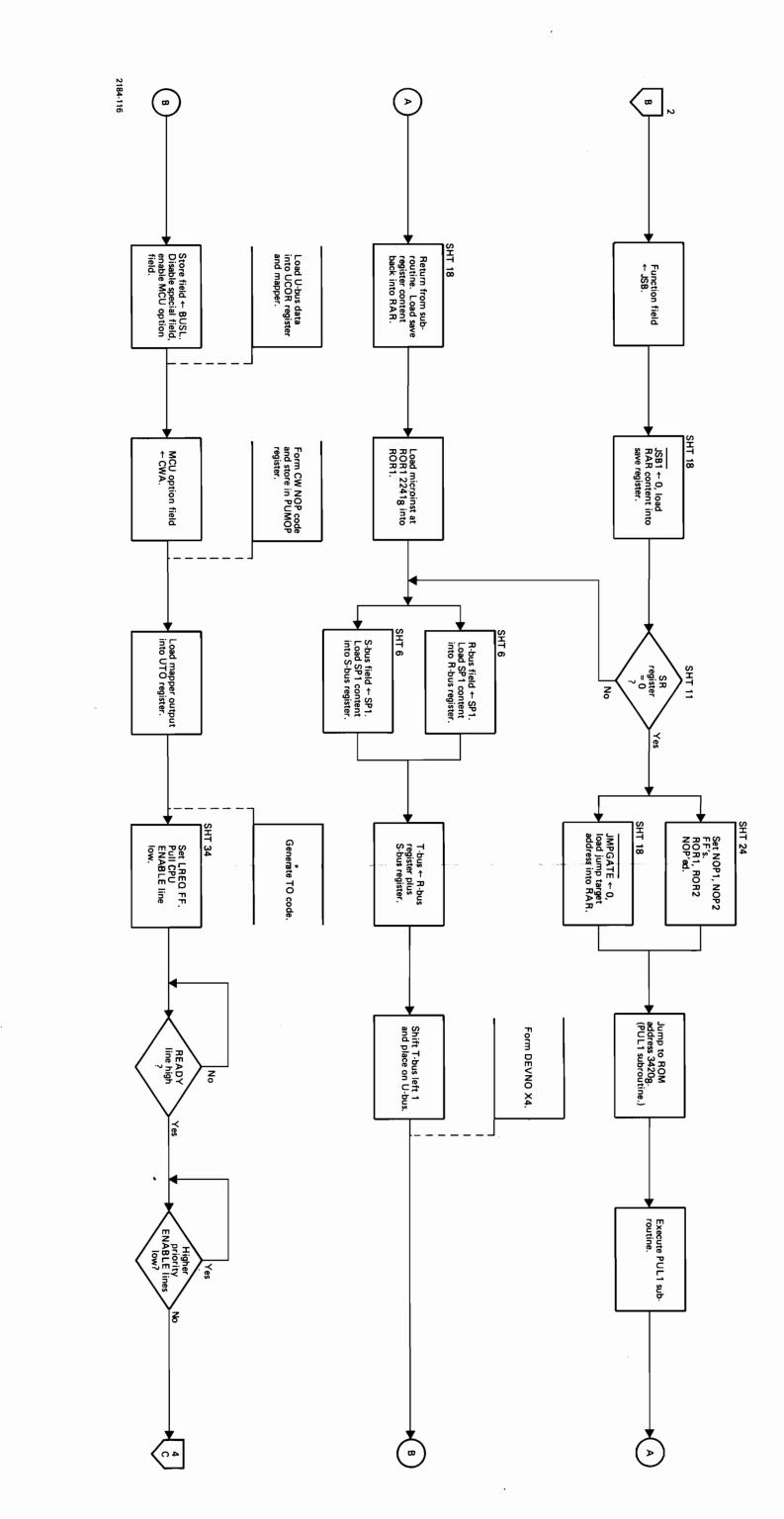

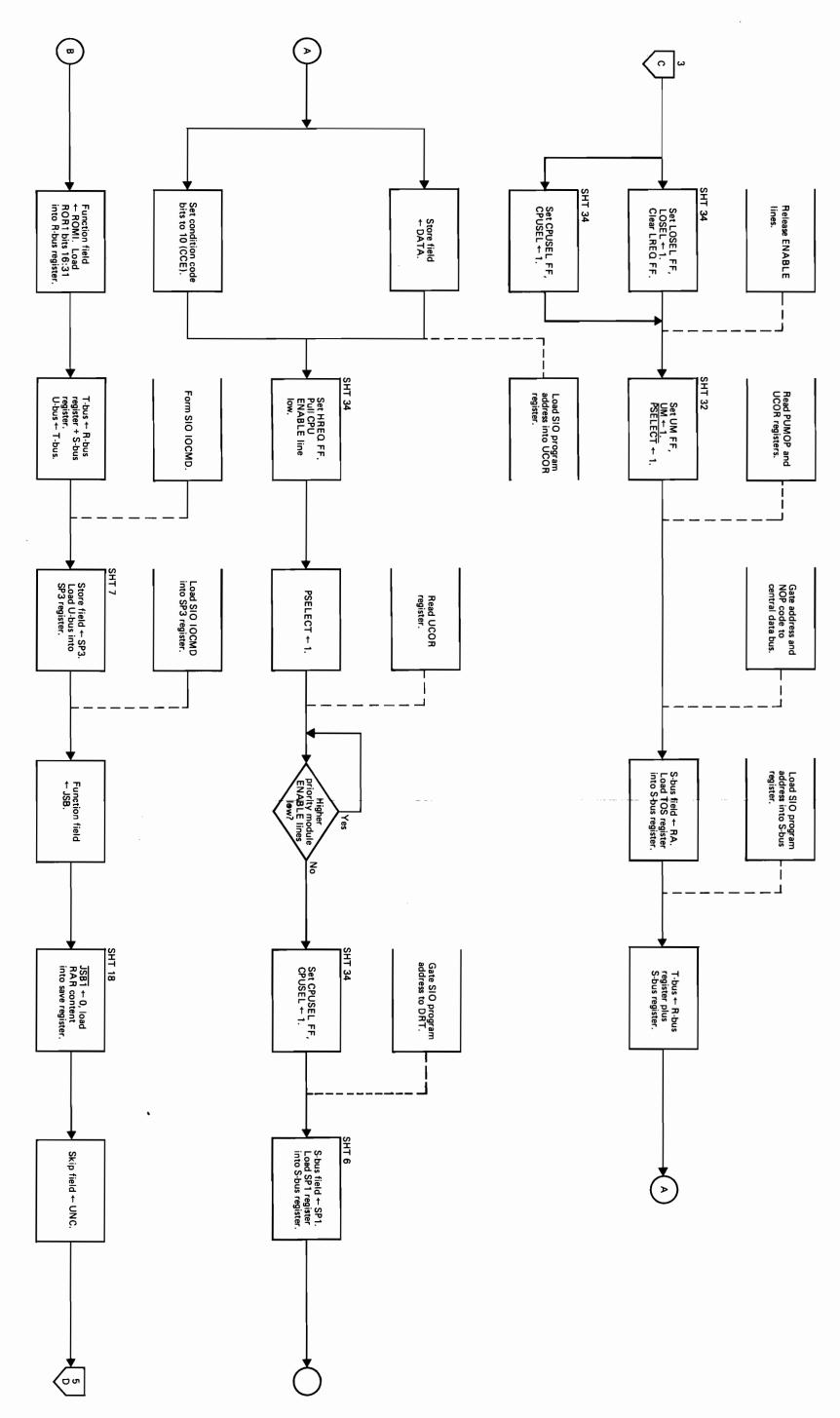

| <b>2-4</b> .                                 | Microinstruction Word Format 1 Flow Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-11                             |

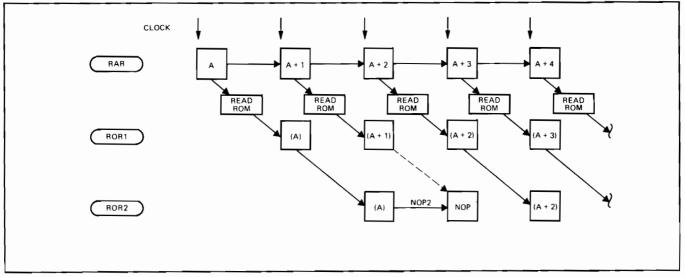

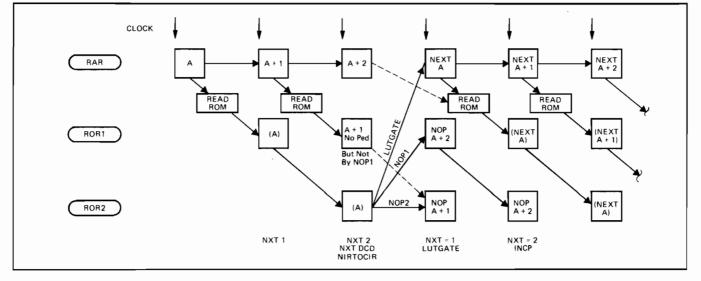

| 2-5.                                         | Execution of Microinstruction Containing Skip Condition (Condition Met)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-12                             |

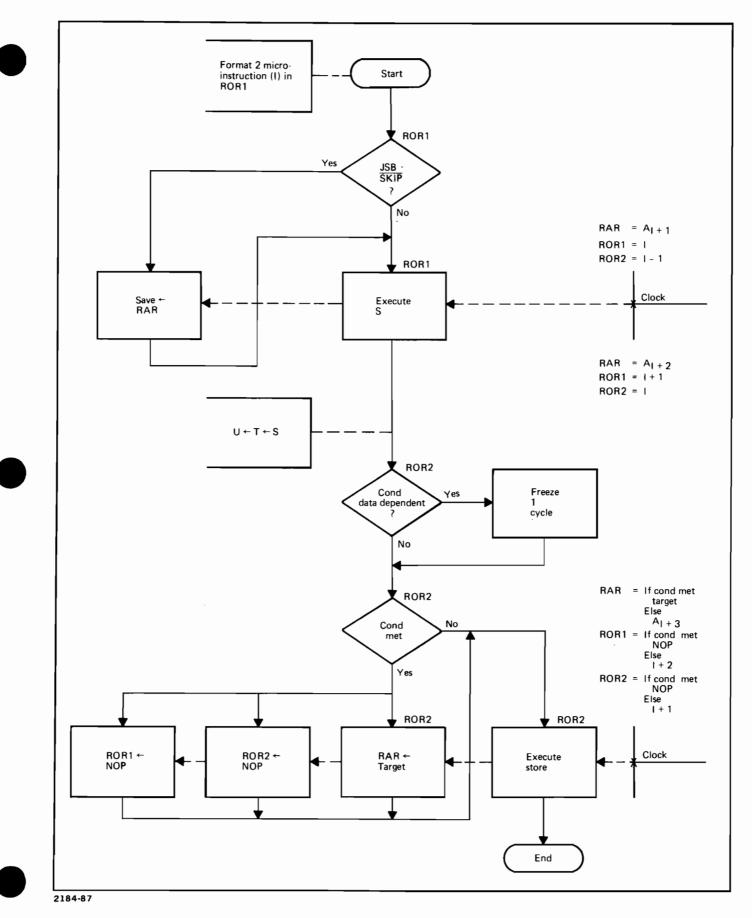

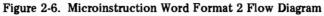

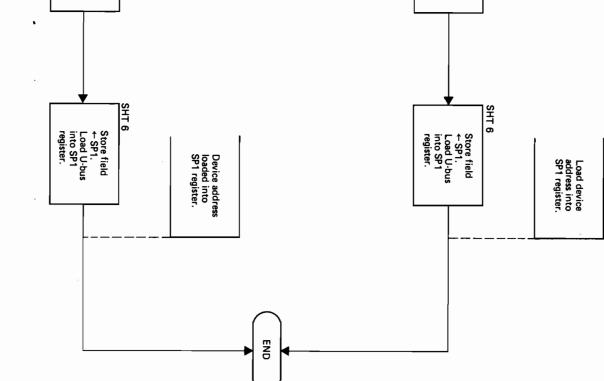

| 2-6.                                         | Microinstruction Word Format 2 Flow Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |

| 2-7.                                         | Execution of Microinstruction Containing Data Dependent JMP or JSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  |

|                                              | (Condition Met) to Target Address T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-14                             |

| 2-8.                                         | Execution of Microinstruction Containing JMP or JSB (Condition Met)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-14                             |

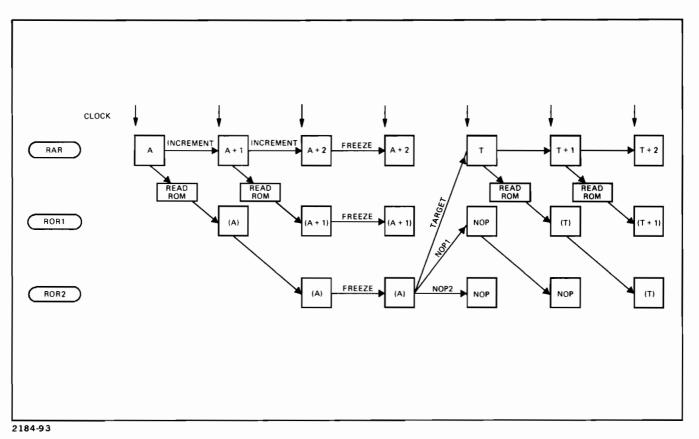

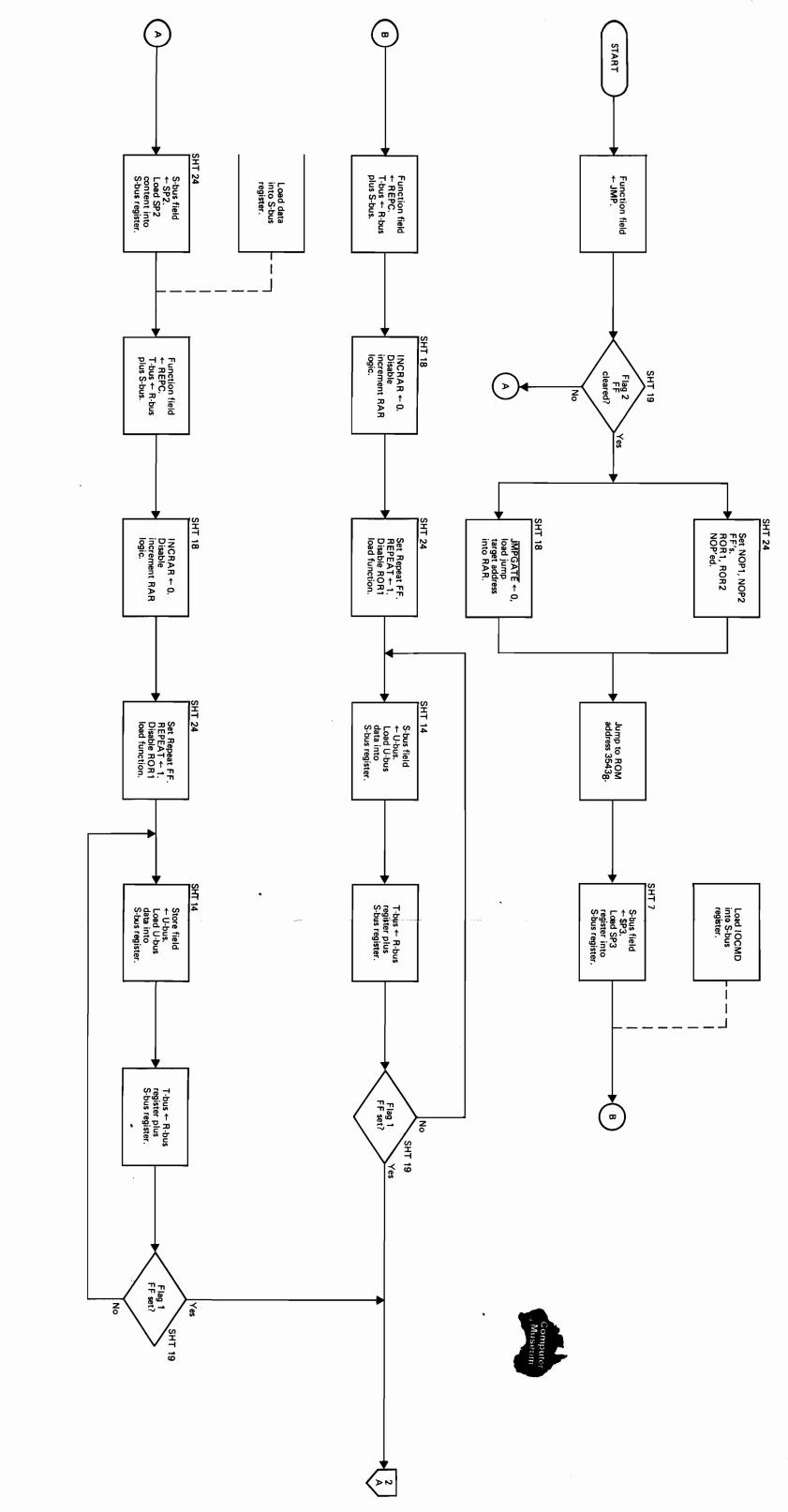

| 2-9.                                         | Microinstruction Word Format 3 Flow Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-15                             |

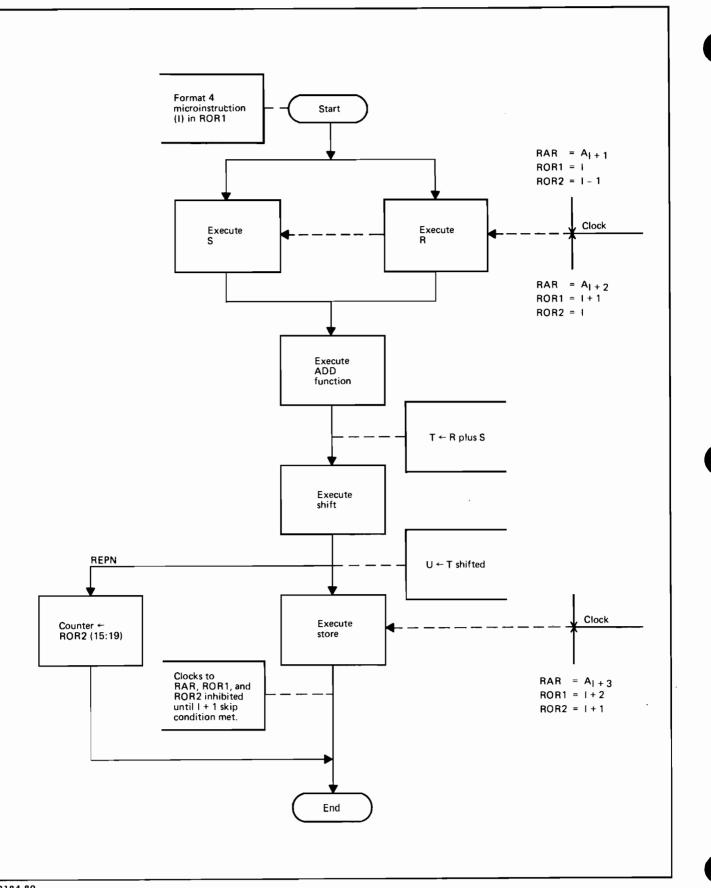

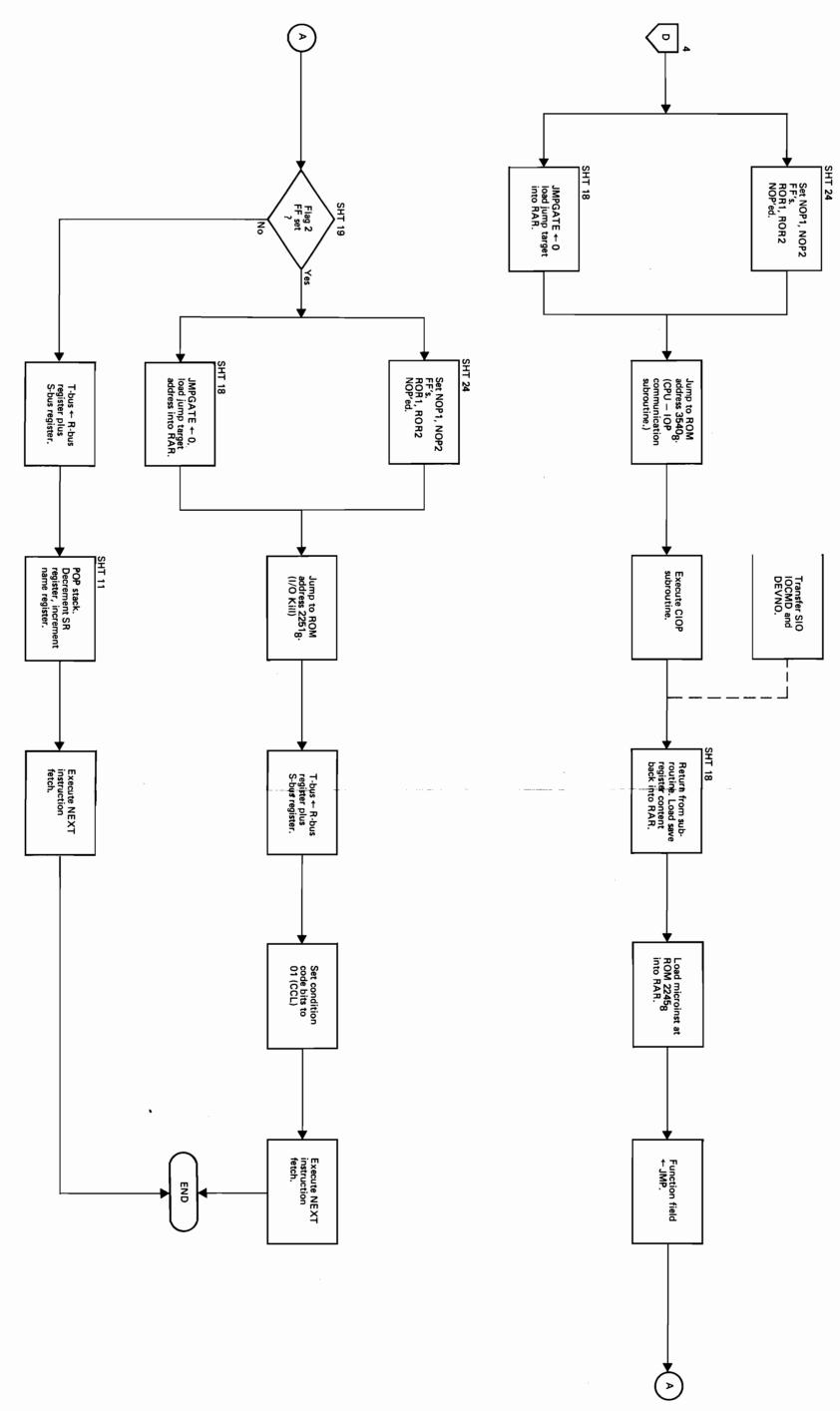

| 2-10.                                        | Microinstruction Word Format 4 Flow Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-16                             |

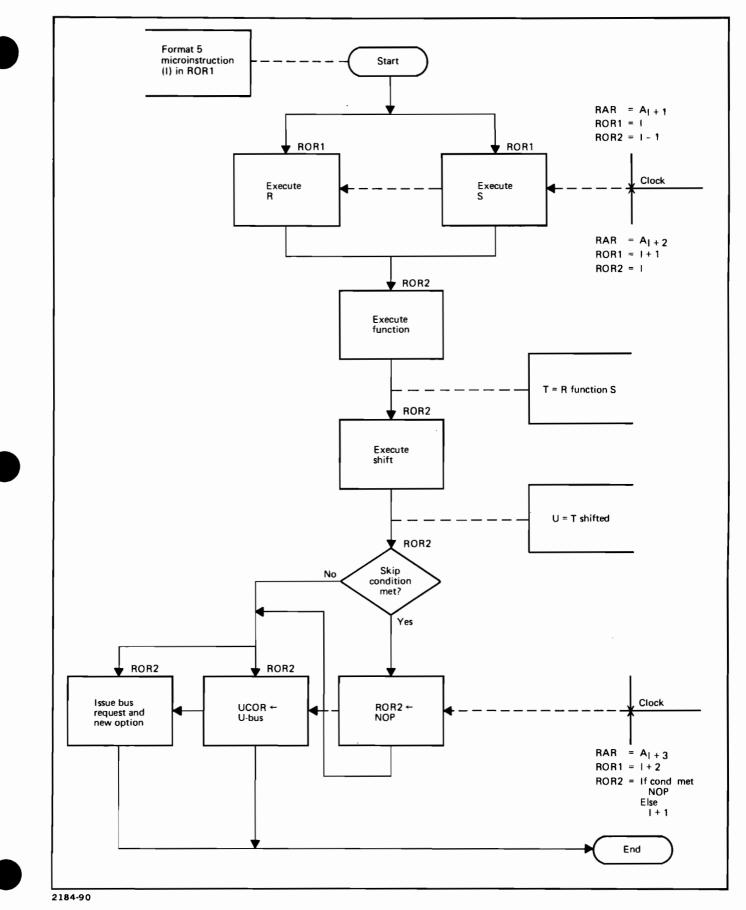

| <b>2-11</b> .                                | Microinstruction Word Format 5 Flow Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-17                             |

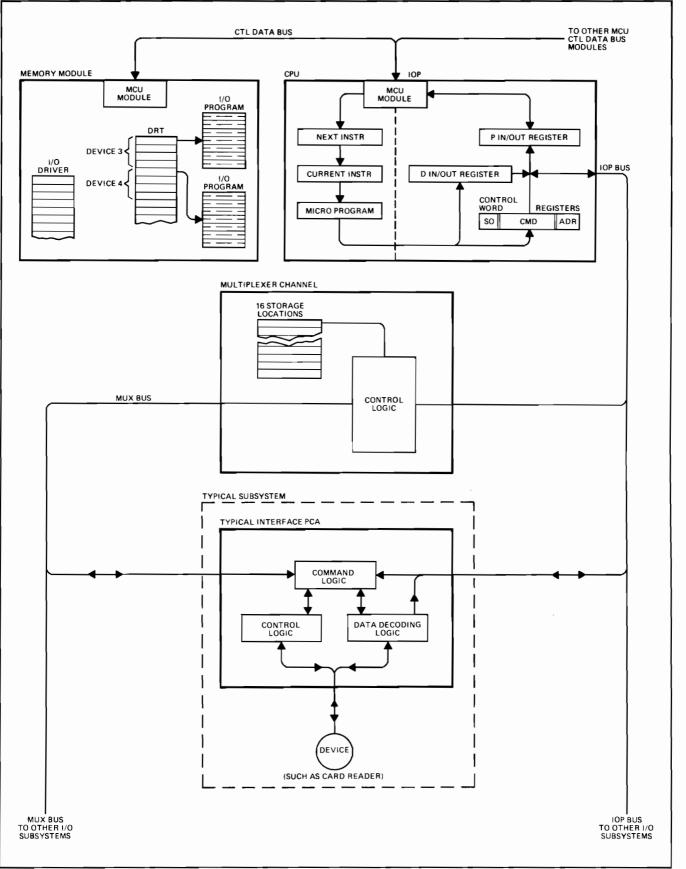

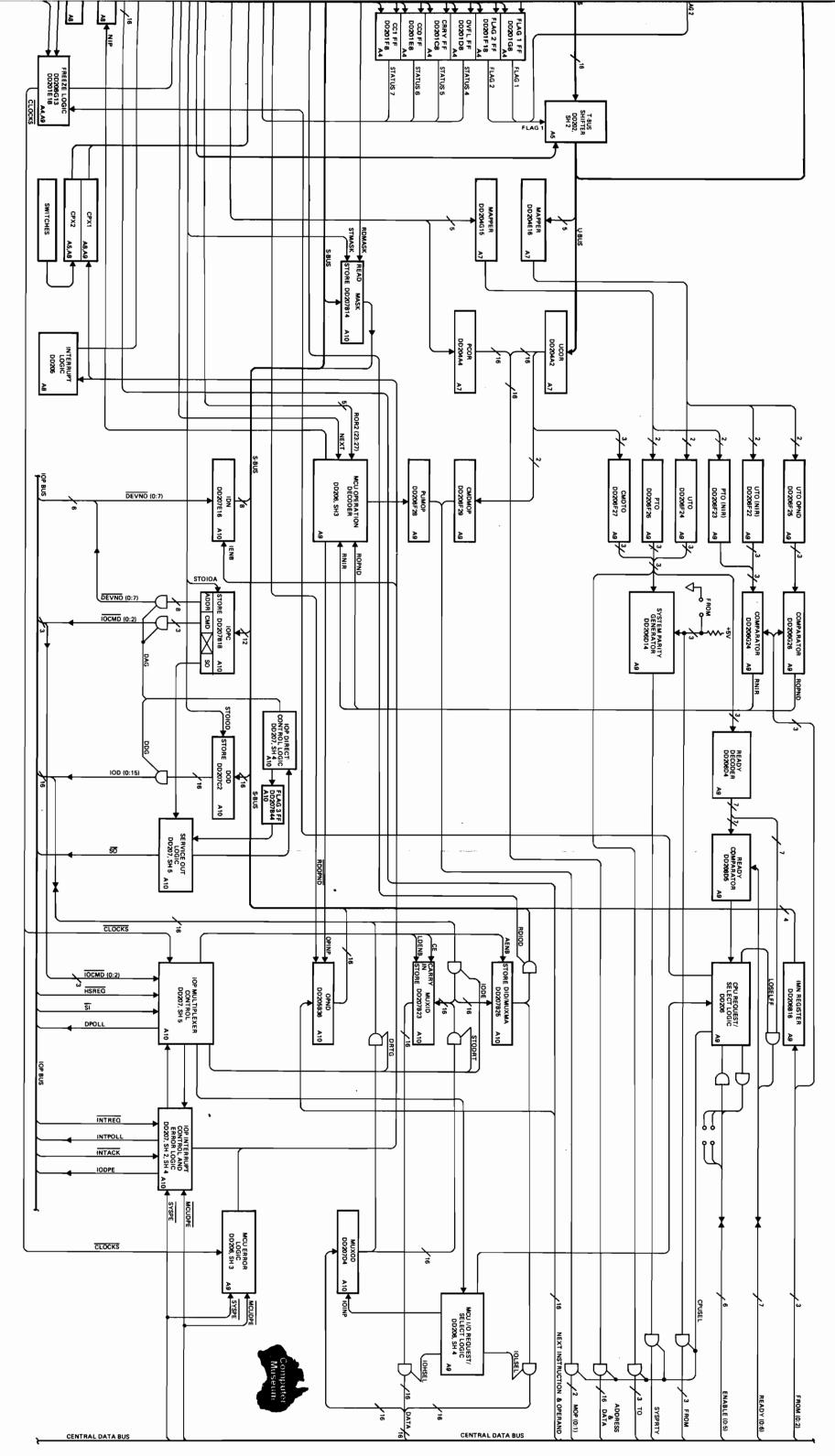

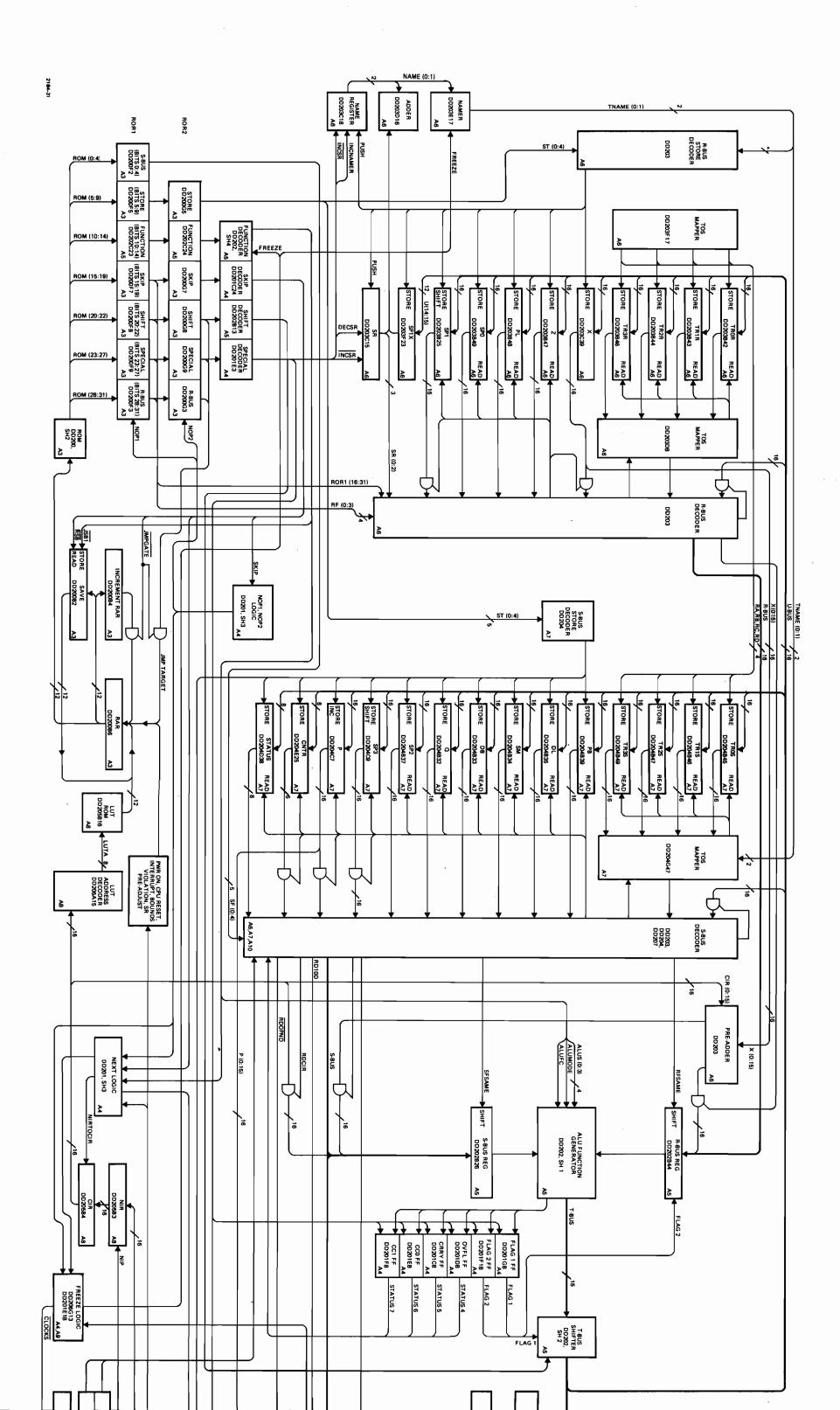

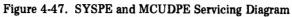

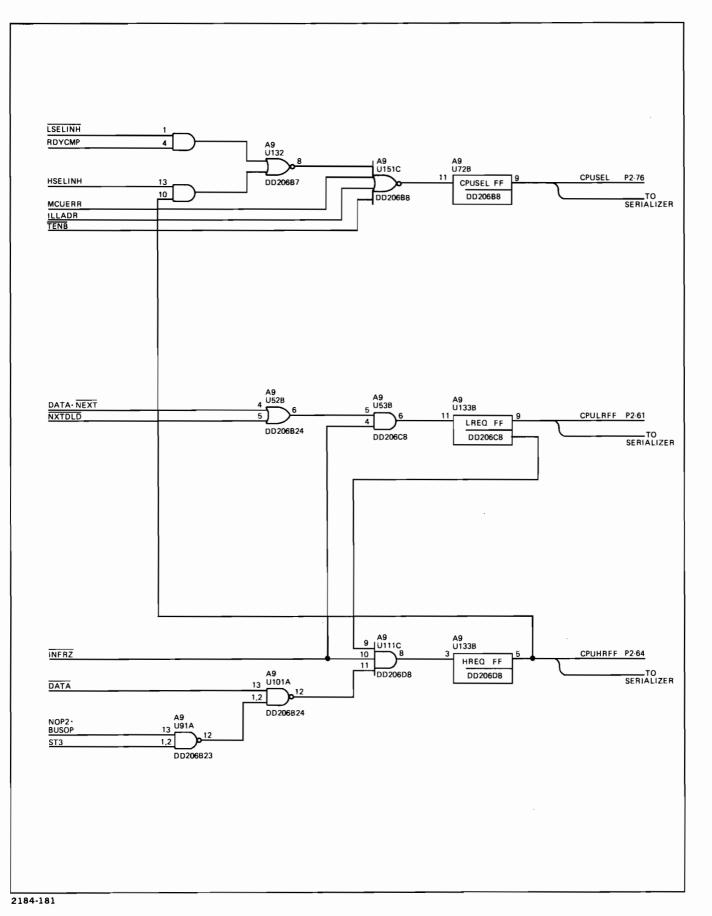

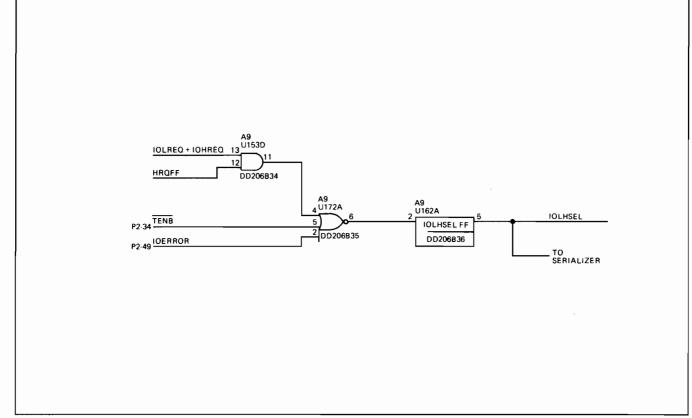

| 3-1.                                         | HP 3000 Computer System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                  |