### ENHANCED ASYNCHRONOUS DATACOM MODULE

Manual Part No. 13255-91239

**REVISED**

OCT-15-79

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

Copyright c 1980 by HEWLETT-PACKARD COMPANY

NOTE: This document is part of the 264XX DATA TERMINAL product series Technical Information Package (HP 13255).

## 1.0 INTRODUCTION.

The Enhanced Asynchronous Datacom PCA along with an interface cable assmebly comprise the Enhanced Asynchronous Datacom Module and provide a communication link between the terminal and an external computer.

## 2.0 OPERATING PARAMETERS.

A summary of operating parameters for the Enhanced Asynchronous Datacom Module is contained in tables 1.0 through 6.4.

Table 1.0 Physical Parameters

| : |                                         |                                      |                                         |          |  |  |  |

|---|-----------------------------------------|--------------------------------------|-----------------------------------------|----------|--|--|--|

|   | Part                                    |                                      | Size (L x W x D)                        | Weight   |  |  |  |

|   | Number                                  | Nomenclature                         | +/-0.100 Inches                         | (Pounds) |  |  |  |

| 1 | ===========                             |                                      |                                         | =======  |  |  |  |

|   | 02640-60239                             | Enhanced Asynchronous<br>Datacom PCA | 12.9 x 4.0 x 0.5                        | 0.38     |  |  |  |

|   | ======================================= |                                      | ======================================= | =======  |  |  |  |

|   | Number of Backplane Slots Required: 1   |                                      |                                         |          |  |  |  |

| = |                                         |                                      |                                         |          |  |  |  |

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

Table 2.0 Reliability and Environmental Information

| <br> <br>  Environmental | : (X)HP(       | Class B (       | ) Other:            |  |

|--------------------------|----------------|-----------------|---------------------|--|

| <br>  Restrictions:      | Type tested at | t product level | <b>1</b>            |  |

| <br> <br>                |                |                 |                     |  |

| 1                        | Failure Rate:  | 0.870 (perce    | ent per 1000 hours) |  |

Table 3.0 Power Supply and Clock Requirements - Measured (At +/-5% Unless Otherwise Specified)

| ======================================= |                  |                  |                 |

|-----------------------------------------|------------------|------------------|-----------------|

| +5 Volt Supply                          | +12 Volt Supply  | -12 Volt Supply  | -42 Volt Supply |

| a 100 mA                                | 8 40 mA          | a) 80 mA         | a mA            |

|                                         | <br> <br>        | <br>             | NOT APPLICABLE  |

| 115 vo                                  | Its ac           | 220 <b>v</b> o   | olts ac         |

| a A                                     |                  | · a              | · A             |

| NOT APPI                                | LICABLE          | NOT API          | PLICABLE        |

|                                         | Clock Frequency: | 4.915 MHz +/-0.1 | *               |

|                                         |                  |                  |                 |

Table 4.0 Switch Definitions

| ======================================= |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCA                                     | Function ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ======================================= |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| THE                                     | Transmit Handshake Enable Open - Enable Transmit Handshake Circuit Closed - Disable Transmit Handshake Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                         | SWITCHES 200, 600, EBE WORK ONLY WHEN KEYBOARD BAUD RATE SELECTION DIAL IS TURNED TO EXT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| EBE                                     | External Baud Rate Enable Open - Enable External Baud Rate Clock Closed - Disable External Baud Rate Clock and enable either 200 or 600 Baud                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 200                                     | 200 Baud Rate Enable Open - Enable 200 Baud Closed - Disable 200 Baud                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 600                                     | 600 Baud Rate Enable   1   Open - Enable 600 Baud   Closed - Disable 600 Baud   1   Closed - |

|                                         | ****NOTE**** Only 1 of switches  EBE, 200, 600 may be left open at any time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                         | <br>====================================                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 5.0 Connector Information

| _ ===================================== |         |                                         |  |

|-----------------------------------------|---------|-----------------------------------------|--|

| Connector                               | Signal  | Signal                                  |  |

| and Pin No.                             | Name [  | Description                             |  |

| P1 Pin 1                                | +5¥     | +5 Volt Power Supply                    |  |

| - 2                                     | еир     | Ground Common Return (Power and Signal) |  |

| - 3                                     | SYS CLK | 4.915 MHz System Clock                  |  |

| - 4                                     | -12V    | -12 Volt Power Supply                   |  |

| - 5                                     | ADDR 0  | Negative True, Address Bit 0            |  |

| j - 6                                   | ADDR1   | Negative True, Address Bit 1            |  |

| j7                                      | i<br>   | Not Used                                |  |

| - 8                                     | ADDR3   | Negative True, Address Bit 3            |  |

| - 9                                     | ADDR4   | Negative True, Address Bit 4            |  |

| -10                                     | ADDR5   | Negative True, Address Bit 5            |  |

| -11                                     | ADDR6   | Negative True, Address Bit 6            |  |

| <b>-12</b>                              | į       | }<br> } Not used                        |  |

| -13                                     | i       | j}                                      |  |

| -14                                     | ADDR9   | Negative True, Address Bit 9            |  |

| -15                                     | ADDR10  | Negative True, Address Bit 10           |  |

| -16                                     | ADDR11  | Negative True, Address Bit 11           |  |

| -17                                     | 1       | i)<br>i)                                |  |

| -18                                     | 1       | }<br> } Not used                        |  |

| -19                                     | 1       | []<br>[]                                |  |

| -20                                     | 1       | j) j                                    |  |

| -21                                     | 170     | Negative True, Input Output/Hemory      |  |

| -22                                     | GND     | Ground Common Return (Power and Signal) |  |

| 1                                       | 1       | 1                                       |  |

Table 5.0 Connector Information (Cont\*d.)

| 1 Connector | Signal    | Signal 1                                 |  |  |

|-------------|-----------|------------------------------------------|--|--|

| and Pin No. | Name      | Description                              |  |  |

| 1           | name      |                                          |  |  |

| Pl, Pin A   | GND       | Ground Common Return (Power and Signal)  |  |  |

|             |           |                                          |  |  |

| j -8        | i         | Not Used                                 |  |  |

| 1           | •         | 1                                        |  |  |

| 1 -c        | +12V      | +12 Volt Power Supply                    |  |  |

| 1           |           | • • • • • • • • • • • • • • • • • • •    |  |  |

| _D          | PUR ON    | System Power On                          |  |  |

| !           | 20166     | Nonether Tour Date Due Die 0             |  |  |

| -E          | BUS0      | Negative True, Data Bus Bit 0            |  |  |

| -F          | BUSI      | Negative True, Data Bus Bit 1            |  |  |

|             | 5031      | i negative rivey vata bus bit i          |  |  |

| i -н        | BUS2      | Negative True, Data Bus Bit 2            |  |  |

|             | 3002      | 1                                        |  |  |

| j -J        | BUS 3     | Negative True, Data Bus Bit 3            |  |  |

| į           | j         | i i                                      |  |  |

| ј -к        | BUS4      | Negative True, Data Bus Bit 4            |  |  |

| 1           |           | 1                                        |  |  |

| L           | BUS5      | Negative True, Data Bus Bit 5            |  |  |

| !           | 5110.5    |                                          |  |  |

| j -M        | BUS6      | Negative True, Data Bus Bit 6            |  |  |

| 1 -N        | 8US7      |                                          |  |  |

| , -n        | 1 8037    | i negative ilue, bata bus bit i          |  |  |

| -P          | WRITE     | Negative True, Write/Read Type Cycle     |  |  |

| i           | i         |                                          |  |  |

| j -R        | i         | i) Not                                   |  |  |

| <b>-</b> s  | İ         | j} Used j                                |  |  |

| 1           | 1         | 1                                        |  |  |

| 1           | 1         | 1                                        |  |  |

| j -T        | PRIOR IN  | Bus Controller Priority In               |  |  |

| ! :         |           | !                                        |  |  |

| i -u        | PRIOR OUT | Bus Controller Priority Out              |  |  |

| -v          | l<br>1    | <br> }                                   |  |  |

| 1 -4        | 1         | I <sup>r</sup><br> } Not Used            |  |  |

| -X          |           | 1)                                       |  |  |

| 1           | i         |                                          |  |  |

| -Y          | REO       | Negative True, Request (Bus Data         |  |  |

| Ì           | İ         | Currently Valid)                         |  |  |

| 1           | 1         | i                                        |  |  |

| -2          | ] ATN     | Negative True, Datacom Interrupt Request |  |  |

|             | !         |                                          |  |  |

| ]           |           | <u> </u>                                 |  |  |

Table 5.1 Connector Information

| Connector  <br>  and Pin No.            | Signal<br>Name | Signal Description                             |  |

|-----------------------------------------|----------------|------------------------------------------------|--|

| [====================================== |                |                                                |  |

| P2, Pin 1                               |                | Not Used                                       |  |

| Pin 2                                   |                | Not Used                                       |  |

| Pin 3                                   | -12V           | -12 Volt Power Supply                          |  |

| Pin 4                                   |                | )<br> }                                        |  |

| Pin 5                                   |                | Not Used                                       |  |

| Pin 6                                   | '              |                                                |  |

| Pin 7                                   | +12V           | +12¥ Power Supply                              |  |

| Pin 8                                   |                | <br> }<br> }                                   |  |

| through                                 |                | } Not Used                                     |  |

| Pin 12                                  |                | j)                                             |  |

| Pin 13                                  | +5V            | +5V Power Supply                               |  |

| Pin 14                                  |                | Not Used                                       |  |

| Pin 15                                  | TEST           | Special Test Point- Presets Baud Rate Counters |  |

| <br>                                    | <br>           |                                                |  |

Table 5.1 Connector Information (Cont\*d)

| ======================================= | ::::::::::::::::::::::::::::::::::::::: |                                                                                                                           |

|-----------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Connector                               | Signal<br>Name                          | Signal Description  *NOTE: Signals with an asterisk below are  TTL levels and should not be  connected to RS232C drivers. |

|                                         |                                         |                                                                                                                           |

| P2. Pin A                               | GND                                     | Terminal Logic Ground                                                                                                     |

| -в                                      | <b>9</b> A                              | Serial Data Out                                                                                                           |

| -с                                      | 88                                      | Serial Data In                                                                                                            |

| -D                                      | CA                                      | Request to Send                                                                                                           |

| -£                                      | СВ                                      | Clear to Send                                                                                                             |

| -F                                      | СС                                      | Data Set Ready                                                                                                            |

| -н                                      | AB                                      | Signal Ground                                                                                                             |

| -J                                      | CF                                      | Receiver Carrier                                                                                                          |

| -к                                      | X8 CLK                                  | External x8 Baud Rate Clock Out                                                                                           |

| . j<br>-L                               | * * * * * * * * * * * * * * * * * * *   | External x16 Baud Rate Clock Out                                                                                          |

| -н                                      | SA                                      | Secondary Channel Transmit                                                                                                |

| -N                                      | SB                                      | Secondary Channel Receive                                                                                                 |

| -P                                      | CD .                                    | Data Terminal Ready                                                                                                       |

| -R                                      | CH                                      | Rate Select                                                                                                               |

| -s                                      | X16 IN                                  | External x16 Baud Rate Clock In                                                                                           |

| <br>============                        |                                         |                                                                                                                           |

Table 6.0 Module Bus Pin Assignments

| function                                        | 1        | Bus          |

|-------------------------------------------------|----------|--------------|

| Performed: Output Control Register Bits         | Value    | Signal       |

| •                                               | ======   | ========     |

|                                                 | 1 X      | ADDR 15      |

| Poll Bit: Not Applicable                        | 1 X      | ADDR 14      |

|                                                 | į x      | ADDR 13      |

| Module Address: (ADDR 11,10,9,4) = (0001)       | i x      | ADDR 12      |

|                                                 | 1 0      | ADDR 11      |

|                                                 | 1 0      | ADDR 10      |

|                                                 | 1 0      | ADDR 9       |

| function Specifier: ADDR 5 = 0                  | 1 X      | ADDR 8       |

| ADDR 6 = 1                                      | X        | ADDR 7       |

|                                                 | 1        | ADDR 6       |

|                                                 | 0        | ADDR 5       |

|                                                 | 1        | ADDR 4       |

|                                                 | į x      | ADDR 3       |

|                                                 | j x      | ADDR 2       |

| Data Bus Bit Interpretation:                    | į x      | ADDR 1       |

|                                                 | i x      | ADDR 0       |

| B7 0=CH High                                    | ======   | ========     |

| 1=CH Low                                        | 1 87     | BUS 7        |

|                                                 | 1 B6     | BUS 6        |

|                                                 | B5       | BUS 5        |

| B6 0 = No Break                                 | B4       | BUS 4        |

| 1 = Break (SA is high, BA is low)               | B3       | BUS 3        |

|                                                 | B2       | 1 BUS 2      |

|                                                 | 1 B1     | BUS 1        |

| B5 0 = Parity Enable                            | 1 80     | BUS 0        |

| 1 = Parity Disable                              |          | =========    |

|                                                 |          | al 1=Bus Low |

|                                                 |          | al 0=Bus Hig |

| B4 0 = Odd Parity                               | X=Don*t  |              |

| 1 = Even Parity                                 | =======  | ========     |

|                                                 |          |              |

|                                                 |          |              |

| Transmit/Receive Baud Rate                      |          |              |

| 1 FVT 1 110. 1 150 1 200 1 1000 1 2400 1 4000 1 |          |              |

| EXT   110*   150   300   1200   2400   4800     |          |              |

| , , , , , , , , ,                               | 1        |              |

|                                                 | 1 1      |              |

|                                                 | <u> </u> |              |

| B1   0   0   0   0   1   1   1                  |          |              |

| *Selects two stop bits.                         |          |              |

| - delects the step ofts.                        |          |              |

|                                                 |          |              |

| DO 0 - 04 40 00                                 |          |              |

| BU U = LA 18 OR                                 |          |              |

| BO 0 = CA is on<br>1 = CA is off                |          |              |

| 1 = CA is off                                   |          |              |

Table 6.1 Module Bus Pin Assignments

| 1 Function                                 | 1        | Bus I                                   |  |  |  |

|--------------------------------------------|----------|-----------------------------------------|--|--|--|

| Performed: Input Received Data Character   | Value    | Signal                                  |  |  |  |

|                                            |          | ======================================= |  |  |  |

| i                                          | i x      | ADDR 15                                 |  |  |  |

| Poll Bit: Not Applicable                   | i x      | ADDR 14                                 |  |  |  |

| 1                                          | i x      | ADDR 13                                 |  |  |  |

| Module Address: (ADDR 11,10,9,4) = (0001)  | . x      | ADDR 12                                 |  |  |  |

|                                            | Ô        | ADDR 11                                 |  |  |  |

| i                                          | i        | ADDR 10                                 |  |  |  |

| <u>;</u>                                   | 0        | ADDR 9                                  |  |  |  |

| Function Specifier: ADDR 5 = 0             | i x      | ADDR 8 1                                |  |  |  |

| ADDR 6 = 0                                 | Î        | ADDR 7                                  |  |  |  |

|                                            | Ô        | ADDR 6                                  |  |  |  |

|                                            | . 0      | ADDR 5 1                                |  |  |  |

|                                            | iii      | ADDR 4 I                                |  |  |  |

|                                            | i x      | ADDR 3                                  |  |  |  |

|                                            | î        | ADDR 2                                  |  |  |  |

| Data Bus Bit Interpretation:               | i x      | ADDR 1                                  |  |  |  |

| 1                                          | i x      | ADDR 0                                  |  |  |  |

| B7 Receive Data Bit 7                      |          |                                         |  |  |  |

| (Equals 0 if parity is selected, otherwise | 87       | BUS 7                                   |  |  |  |

| is equal to most significant data bit)     | 86       | BUS 6                                   |  |  |  |

| 1                                          | 1 B5 1   | BUS 5                                   |  |  |  |

| 1 B6 Receive Data Bit 6                    | 1 B4     | BUS 4                                   |  |  |  |

|                                            | i 83     | BUS 3                                   |  |  |  |

| j                                          | B2       | BUS 2                                   |  |  |  |

| B5 Receive Data Bit 5                      | B1       | BUS 1                                   |  |  |  |

|                                            | 1 80     | BUS 0                                   |  |  |  |

|                                            |          | ======================================= |  |  |  |

| 1 84 Receive Data Bit 4                    | •        | 1 1=Bus Low                             |  |  |  |

|                                            |          | 1 0=Bus High                            |  |  |  |

|                                            | IX=Don't |                                         |  |  |  |

| •                                          |          | :::::::::::::::                         |  |  |  |

|                                            |          |                                         |  |  |  |

| i                                          |          | į                                       |  |  |  |

| B2 Receive Data Bit 2                      |          | i                                       |  |  |  |

|                                            |          | i                                       |  |  |  |

|                                            |          | i                                       |  |  |  |

| B1 Receive Data Bit 1                      |          | ì                                       |  |  |  |

|                                            |          | i                                       |  |  |  |

| i ·                                        |          | i                                       |  |  |  |

| BO Receive Data Bit O                      |          | i                                       |  |  |  |

|                                            |          | i                                       |  |  |  |

|                                            |          | i                                       |  |  |  |

|                                            | =======  |                                         |  |  |  |

Table 6.2 Module Bus Pin Assignments

| Function                                      | 1            | ) Bus        |

|-----------------------------------------------|--------------|--------------|

| Performed: Output data character for transmis | sion   Value | Signal       |

|                                               | ======       |              |

| •                                             | į x          | ADDR 15      |

| Poll Bit: Not Applicable                      | i x          | ADDR 14      |

|                                               | į x          | ADDR 13      |

| Module Address: (ADDR 11,10,9,4) = (0001)     | i x          | ADDR 12      |

|                                               | jo           | ADDR 11      |

|                                               | j O          | ADDR 10      |

|                                               | 1 0          | ADDR 9       |

| Function Specifier: ADDR 5 = 1                | j x          | ADDR 8       |

| ADDR 6 = 1                                    | į x          | ADDR 7       |

|                                               | 1 1          | ADDR 6       |

|                                               | 1            | ADDR 5       |

|                                               | 1            | ADDR 4       |

|                                               | j x          | ADDR 3       |

|                                               | į x          | ADDR 2       |

| Data Bus Bit Interpretation:                  | į x          | ADDR 1       |

|                                               | j x          | ADDR 0       |

| } If Parity is Enabl                          |              | =========    |

| 37 Transmit Data Bit 7  Bit 7 is replaced     | by 1 B7      | BUS 7        |

| } proper parity.                              | B6           | BUS 6        |

|                                               | 85           | BUS 5        |

| B6 Transmit Data Bit 6                        | <b>j 84</b>  | BUS 4        |

|                                               | B3           | BUS 3        |

|                                               | B2           | BUS 2        |

| B5 Transmit Data Bit 5                        | B1           | BUS 1        |

|                                               | B0           | BUS 0        |

|                                               | 1======      |              |

| B4 Transmit Data Bit 4                        |              | al 1=Bus Low |

|                                               |              | al 0=Bus Hig |

|                                               | X=Don* t     |              |

| B3 Transmit Data Bit 3                        | =======      | ========     |

|                                               |              |              |

| DO Terresia Data (144 O                       |              |              |

| B2 Transmit Data Bit 2                        |              |              |

|                                               |              |              |

| B1 Transmit Data Bit 1                        |              |              |

| DI TRANSMIC DATA DIT I                        |              |              |

|                                               |              |              |

|                                               |              |              |

Table 6.3 Module Bus Pin Assignments

| =======     |                                                 | =======     |                                         |

|-------------|-------------------------------------------------|-------------|-----------------------------------------|

| Funct       |                                                 | }           | Bus 1                                   |

| l Perfoi    | med: Input Datacom Status                       | Value       | ,                                       |

| !<br>!      |                                                 | •           | ======================================= |

| ;<br>! 0511 | Bit: Not Applicable                             | X           | ADDR 15                                 |

| 1 -011      | Bit: Not Applicable                             | 1 X         | ADDR 14                                 |

| !           | · · · · · · · · · · · · · · · · · · ·           | 1 X         | ADDR 13                                 |

| j modul     | e Address: $(ADDR 11,10,9,4) = (0001)$          | l x         | ADDR 12                                 |

| ļ           |                                                 | J 0         | ADDR 11                                 |

| 1           |                                                 | 0           | ADDR 10                                 |

| 1           |                                                 | 0           | ADDR 9                                  |

| Funct       | ion Specifier: ADDR 5 = 1                       | X           | ADDR 8                                  |

| Ì           | ADDR 6 = 0                                      | i x         | ADDR 7 1                                |

| Ì           | •                                               | 0           | ADDR 6 1                                |

| i           |                                                 | 1           | ADDR 5                                  |

| i           |                                                 | ī           | ADDR 4                                  |

| i           |                                                 | i x         | ADDR 3 1                                |

| 1           | Data Bus Bit Interpretation:                    | X           | ADDR 3 1                                |

| ;           | was bus bit interpretations                     | 1 ^<br>1 X  | •                                       |

| 97          | Times Independed ALTERNATE STATUS (ACCES        |             | ,                                       |

| В7          | Timer Interrupt   ALTERNATE STATUS (A0=1)       | į x         | ADDR 0 1                                |

| !           | }                                               | 1           | =======                                 |

| ļ           | } Data Set Ready (CC)                           | B7          | BUS 7                                   |

| 1           |                                                 | <b>B6</b>   | BUS 6                                   |

| •           |                                                 | <b> </b> 85 | BUS 5                                   |

| 86          | Secondary Channel Receive (SB)                  | B4          | BUS 4                                   |

| •           |                                                 | B3          | BUS 3 1                                 |

| 1           |                                                 | B2          | 1 BUS 2 1                               |

| i           |                                                 | i B1        | i BUS 1 i                               |

| i 85        | Clear to Send (CB)                              | i 80        | BUS 0                                   |

| i           |                                                 | •           | ======================================= |

| i           |                                                 | 1=Logic     | al 1=Bus Low                            |

| i           |                                                 |             | al 0=Bus High                           |

| i 84        | Carrier (CF)                                    | X=Don t     |                                         |

| 1           |                                                 | •           | ======================================= |

| ;           |                                                 |             |                                         |

| B3          | 0 = No Parity Error}                            |             | 1                                       |

| 1 53        |                                                 |             | !                                       |

|             | •                                               |             | !                                       |

| !           | ) Overrun and parity errors                     |             | reset                                   |

|             | } after each character is re                    | celved.     | I                                       |

| 82          | 0 = No Overrun }                                |             |                                         |

| ļ           | 1 = Overrun Error }                             |             |                                         |

| ı           |                                                 |             | 1                                       |

| 1           |                                                 |             | 1                                       |

| B1          | 0 = Transmit Holding Register Full } ALTERNATE  |             |                                         |

| 1           | 1 = Transmit Holding Register Empty} 0= Transmi |             |                                         |

| ŧ           | } 1= Transmi                                    | ssion Co    | mplete                                  |

| 1           |                                                 |             | i                                       |

| ĺ           |                                                 |             | 1                                       |

| j 80        | O = No Data Received Data received is made "O"  | by inpu     | tting a i                               |

| i           | 1 = Data Received } received data character (   | see tabl    | e 5.1).                                 |

| i           |                                                 |             | i                                       |

| ========    |                                                 | =======     |                                         |

|             |                                                 |             | •                                       |

Table 6-4 Module Bus Pin

| Performed: Input instruction to Set/Reset Data | Value   | Signal        |

|------------------------------------------------|---------|---------------|

| Terminal Ready (CD) and Enable/Disable         | ======  | ========      |

| Timer                                          | i X     | ADDR 15       |

|                                                | j x     | ADDR 14       |

| Poll Bit: Not Applicable                       | i x     | ADDR 13       |

|                                                | į X     | ADDR 12       |

| Module Address: (ADDR 11,10,9,4) = (0001)      | A11     | ADDR 11       |

|                                                | A10     | ADDR 10       |

| ·                                              | 1 A9    | ADDR 9        |

|                                                | į x     | ADDR 8        |

| Function Specifier: ADDR 5 = 0                 | 1 X     | ADDR 7        |

| ADDR 6 = 0                                     | 1 1     | ADDR 6        |

|                                                | 1 1     | ADDR 5        |

|                                                | 1 A4    | ADDR 4        |

|                                                | 1 A3    | ADDR 3        |

| A3 = 0, CD On                                  | A2      | ADDR 2        |

| A3 = 1, C) Off                                 | l X     | ADDR 1        |

|                                                | j x     | ADDR 0        |

|                                                | ]====== | =========     |

|                                                | 1 B7    | BUS 7         |

|                                                | 1 B6    | BUS 6         |

| AO = 1 Enable Timer                            | 85      | BUS 5         |

| AO = O Disable Timer                           | B 4     | BUS 4         |

|                                                | 1 83    | BUS 3         |

| A1 = 1 Not Used                                | B2      | BUS 2         |

| A1 = 0 Clear Timer Interrupt                   | 1 81    | BUS 1         |

|                                                | 1 BO    | 1 BUS 0       |

|                                                |         | ==========    |

|                                                |         | al 1=Bus Low  |

|                                                |         | al O=Bus High |

|                                                | ======  |               |

|                                                |         |               |

|                                                |         |               |

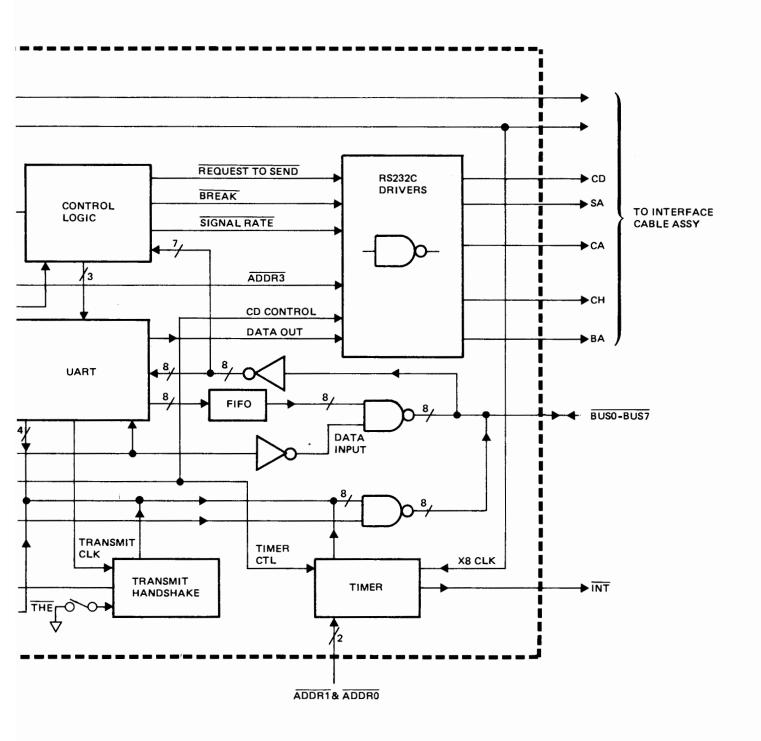

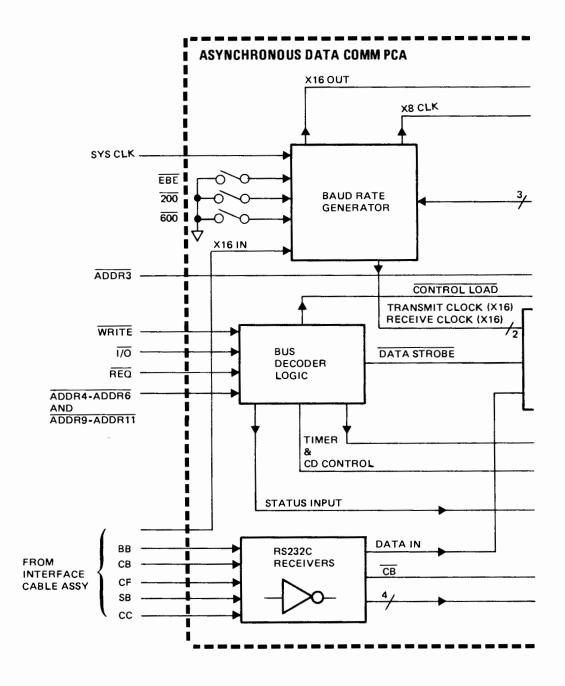

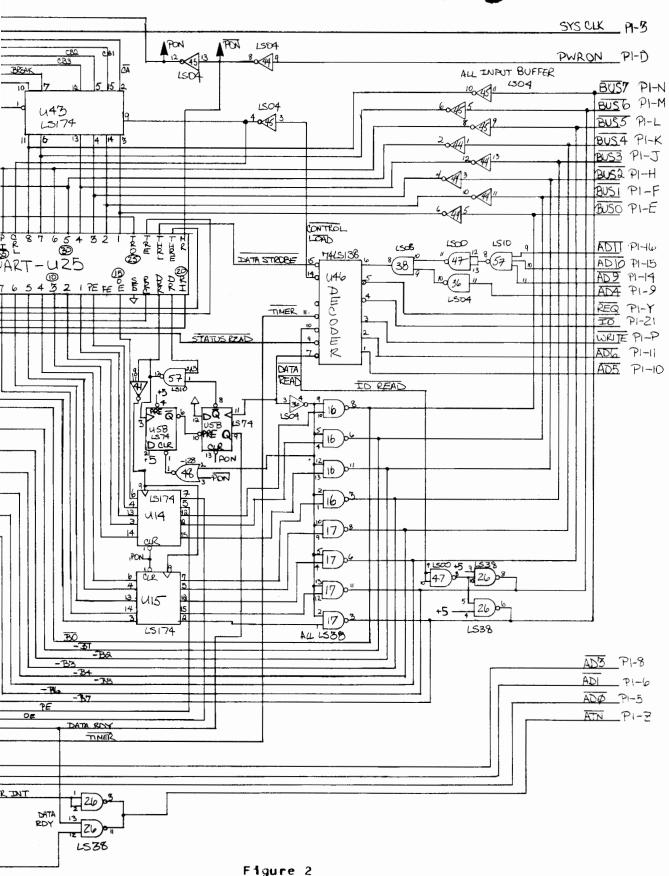

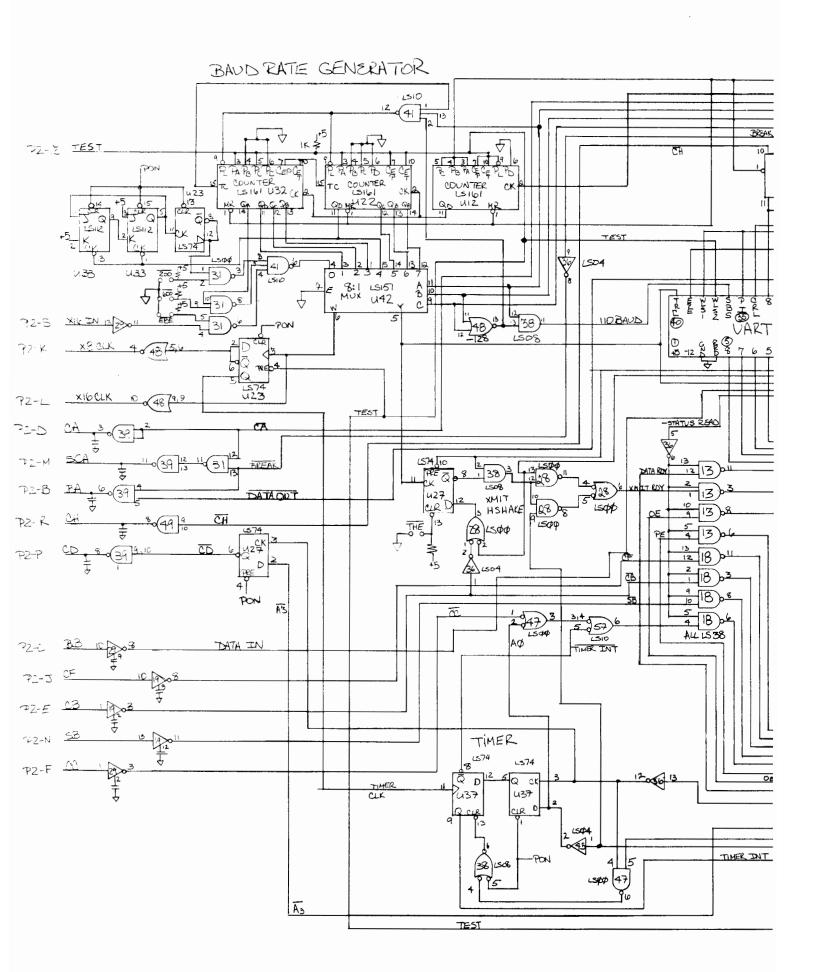

3.0 FUNCTIONAL DESCRIPTION. Refer to the block diagram (figure 1), schematic diagram (figure 2), component location diagram (figure 3), and parts list (02640-60239) located in the appendix.

The Enhanced Asynchronous Datacom Module is the primary interface between the terminal and external data processing equipment. It provides characterter parallel data, status, and control information to the terminal microprocessor by way of firmware control. Individual characters are sent and received bit-serial and character-serial using an EIA RS232C electrical interface. The PCA can be connected to external data processing equipment directly or by modem depending on the on the interface cable assembly used. The module functional groups consist of the universal asynchronous receiver/transmitter (UART), bus decoder logic, control logic, baud rate generator, RS232C drivers, Hardware Timer Logic, Transmit Handshake and Fifo buffer.

- 3-1 UART.

- The UART is Western Digital's TR1602B and is the key element of the module. It accepts a parallel character from the terminal data bus, appends the necessary asynchronous character formatting and parity bits, and transmits the information serially at a rate determined by ar input clock. The UART has a master reset input for power on initialization, control inputs and status outputs for firmware control of the interface, and clock inputs for determining the serial data bit rate. The UART receives serial data, deletes the start and stop framing bits, optionally checks incoming parity, and outputs a parallel character.

- The UART (U25), provides all control logic and data storage necessary to implement an asynchronous parallel-to-serial (transmit) and serial-to-parallel (receive) converter. It has control inputs to determine character size and formatting, including an optional parity bit (generated on output and checked on input). The UART has status outputs for determining when the UART can accept another parallel character for transmission or for indicating that a character has been received and is ready for input. The UART has transmit and receive clock inputs which are clocked at 16 times the desired baud rate.

- 3.1.2.1 There are five control inputs (Pins 35, 39, 36, 37, and 38) for the UART which define character format and parity. The character size is always eight bits with the optional even or odd parity being placed in the most significant bit of the character when selected. If 110 baud is the bit rate used, an extra stop bit is added to the asynchronous character formatting. When transmitted, each character will consist of a start bit, eight data bits (optional parity) least significant bit first, and one or two (110 baud) stop bits.

- 3.1.2.2 Characters to be transmitted are loaded into the UART by DATA STROBE. This output command from the bus decoder circuit strobes data into the UART using input THRL (Transmit Holding Register Load) at Pin 23. This causes the THRE (Transmit Holding Register Empty) at Pin 22 output to go low and remain false until the character in the buffer is transferred into the UART's serial output shifter. The character in the buffer is transferred to the shifter when the shifter is empty or has completed the previous character and the THRE output goes true again. Data bits and format bits (start, stop, and parity) are shifted out of the UART at TRO (Transmitter Register Output) at Pin 25 according to the inputs from the control logic. Each individual bit takes 16 transmit clocks to be shifted out.

- 3.1.2.3 The UART uses the RRC (Receiver Clock) signal at Pin 17 to sample the RI input (Receive Serial In) at Pin 20 for an asynchronous start bit. When it detects a valid start bit, the UART begins shifting data (16 clocks per bit) into the receive serial shifter. When the character is completed, the UART removes the asynchronous format bits (start and stop) transfers the character in parallel to UART outputs Pins 5 through 12 and sets DR (Data Received) at Pin 19 high. When one character is received, the UART updates two status bits, PE (Parity Error) at Pin 13 and OE (Overrun Error) at Pin 15. PE is set high only when odd or even parity is selected by the control logic and the input character had the incorrect parity. OE is set high when the UART has already received a character, DR (Pin 19) is high and a new character is loaded into it. When Data Input (U36, Pin 4) is decoded, the UART data outputs are gated onto the terminal bus and DRR (Data Received Reset) at Pin 18 is pulse, setting DR (Pin 19) low. The UART is then ready for another character.

- 3.2 BUS DECODER LOGIC.

- 3.2.1 The bus decoder logic provides the interface for the module and includes module address decoding and input and output enable signals.

Hodule address and data bus control signals determine when the PCA will input (Processor Read) data or control and when it will output (Processor Write) data or status.

- The address of the Enhanced Asynchronous Datacom PCA is determined by two logic gates, (U57, Pin 8 and U36, Pin 10). These connect to the terminal address lines (ADDRII, ADDRIO, ADDR9 and ADDR4). The module is further addressed by inputs from the terminal bus to a 1-of-8 decoder (U46), which samples WRITE, ADDR6, and ADDR5 with REQ and I/O enabling the decoder.

- 3.2.2.1 The normal bus addressing sequence is for all of the module address information to be placed on the terminal data bus and allowed to become stable. Then REQ which is the final enabling signal (execute or strobe command) is set true (low). This creates one of the following output strobes from the 1-of-8 decoder (U42): DATA STROBE (U46, Pin 15), CONTROL LOAD (U46, Pin 14), STATUS INPUT (U36, Pin 6), DATA INPUT (U36, Pin 4), Timer Function (U36, Pin 12) and Firmware Control Read (U47, Pin 5).

- 3.2.2.2 Data output from the UART and interface status are available to the terminal data bus through buffers (U13, U14, U15, and U16). The three input commands (STATUS INPUT, DATA INPUT, and FIRMWARE READ) enable status or data to be gated onto the terminal data bus. During a data input, OR at U25, Pin 19 is set while the data is gated to the terminal bus.

- 3.2.2.3 The occurance of a FIRMWARE READ gates a (CO) hex on to the data bus. This differentiates this Datacom board from the General Purpose (02640-60143) Datacom board.

- 3.3 CONTROL LOGIC.

- 3.3.1 The control logic circuit is loaded from the terminal data bus by a microprocessor output command. There are seven bit positions which control interface signals, define UART controls, and select the data in/out bit rate (baud rate).

- 3.3.2 The control register is program loaded into hex register U43. The inputs to the control register are BUSO through BUS7. The control The control information is loaded into the register by CONTROL LOAD (U46, Pin 14). (Refer to table 5.0 for definition of conrol register bits.)

- 3.3.2.1 The three baud rate select bits (CB3, CB2, and CB1) go to the multiplexer and determine which part of the divider chain or if the X16 IN clock is to be used as the bit rate clock. The baud rate select code for 110 baud is detected by two gates (U48, Pin 13 and U38, Pin 11) indicating two stop bits to the UART control and enabling the preset function of the divider chain to obtain 110 baud.

- 3.3.2.2 The Break flip-flop controls DATA OUT by making it high without regard to data being transmitted from the UART. BREAK is used by the terminal for remote interrupt to data processing equipment. If the Break flip-flop is not set, data is treated normally by the RS232C driver.

- 3.4 BAUD RATE GENERATOR.

- 3.4.1 The baud rate generator defines bit timing during transmit and receive operations. It consists of a 12-bit counter chain and a multiplexer which selects one of eight possible baud rates. The counter chain divides the terminal data bus System Clock (SYS CLK) down into useable baud rate frequencies.

- 3.4.2 Three counters (U32, U22, and U12) and an eight-input multiplexer (U42) comprise the baud rate generator. Seven of the baud rates are generated from the terminal System Clock and the eighth is an external input. As outputs, the PCA generates external signals equal to the baud rate times sixteen and times eight (TTL level signals).

- 3.4.2.1 The three counters generate six baud rates directly by dividing System Clock by factors of two. The other baud rate (110 baud) is not directly derived by dividing by two. The select code for 110 baud is detected (U48, Pin 13 and U38, Pin 11) and a preset function is enabled when the counter chain overflows (U32, Pin 15). A constant is parallel-loaded into the last two counters (U32 and U22), which perform a divide by 175 instead of 256. This gives the transmit and receive clocks (X16) necessary for that baud rate (the frequency is exactly 1755 +/-1 Hz).

### Baud Rate Summary

| Baud Rate<br>Select Bits<br>Control Register |       |       |                                     |                | System Clock                            |

|----------------------------------------------|-------|-------|-------------------------------------|----------------|-----------------------------------------|

| 3                                            | 2     | 1     | Baud Rate                           | Frequency (Hz) | (Divide by)                             |

| =====                                        | ===== | ===== | =========                           | ***********    | ======================================= |

| 1                                            | 1     | 1     | 9600                                | 153,600        | 32                                      |

| 1                                            | 1     | 0     | 4800                                | 76,800         | 64                                      |

| 1                                            | 0     | 1     | 2400                                | 38,400         | 128                                     |

| 1                                            | 0     | 0     | 1200                                | 19,200         | 256                                     |

| 0                                            | 1     | 1     | 300                                 | 4,800          | 1024                                    |

| 0                                            | 1     | 0     | 150                                 | 2,400          | 2048                                    |

| .0                                           | 0     | 1     | 110                                 | 1,755          | 2800                                    |

| 0                                            | 0     | 0     | External<br>Clock In<br>(max 10000) | (max 160 kHz)  | -                                       |

3.4.2.2 The three baud rate select bits from the control logic go to a multiplexer (U42) in the baud rate generator. Seven of the baud rates are

generated by the counter chain, the eighth is the X16 IN clock (P2-S) which can be no greater than 160 kHz (10,000 baud) and TTL specification levels. One output of the multiplexer goes to the UART clocks and the other to a buffer which provides a TTL level X16 baud rate clock (X16 OUT) at P2, Pin L. Flip-flop (U23, Pin 6) divides the baud rate clock to provide an external TTL level X8 Clock (X8 CLK) at P2, Pin K.

3.4.2.3 In addition to the above baud raes, 200 and 600 Baud may be selected. By disabling the external baud rate generater

(close switch  $\overline{\text{EBE}}$ ), setting baud rate to EXT, and enabling either 200 or 600 Baud (by opening appropriate switch), the user can select either 200 or 600 Baud.

- 3.5 RS232C DRIVERS.

- 3.5.1 The interface between the Enhanced Asynchronous Datacom Module and external devices conforms to the EIA RS232C standard, which specifies electrical and logical operation, interface limitation, and defines the signal functions. The RS232C interface allows the PCA and thus the terminal to be connected locally to data processing equipment or to modems for remote operation using the telephone network. The RS232C drivers provide serial data out and three control outputs.

3.5.2 The interface signals are available at the PCA rear connector (P2) for connection to a cable assembly. The RS232C voltage outputs are signals converted from TTL levels (+5 volts and ground) by integrated circuit drivers (U39 and U49).

The REQUEST TO SEND output comes directly from the control logic at U22. Pin 7 and is used in modem applications to begin a transmit operation. The DATA TERMINAL READY output is always high (except in auto dial timer mode) the terminal power is on. Secondary Channel Transmit (SA) is used on Bell 202 or equivalent data sets and is high unless the

Break flip-flop (U43, Pin 7) is low or REQUEST TO SEND is low. Capacitors C6 are used for slew rate control.

- 3.6 RS232C RECEIVERS. The RS232C receivers also meet the EIA standard and provide DATA IN and three control inputs. The RS232C inputs are converted to TTL levels by integrated circuit receivers (U19,U29). Capactions C7, C8, C9, and C10 on the input receivers are used for noise suppression. DATA IN (BB), is converted to TIL levels by the receiver and goes directly to the UART. Four inputs (CF, CB, CC, SB) are provided for modem status monitoring by the terminal processor.

- 3.7 TIMER ROUTINES Several Critical timing functions must be performed to implement the auto dial feature. By programming (in firmware) the Baud Rate Generator to 110 Baud, and using the X8 clock, we have a timer of 1.12 ms duration. By counting these timer interrupts, critical times of longer duration be achieved with a high accuracy. Specific timer firmware controls are shown in Table 6.4.

- 3.8 TRANSMIT HANDSHAKE

- 3.8.1 The transmit handshake circuit provides the capability of handshaking transmitted data with an RS232C control line. When the transmit

handshake circuit is enabled (THE Switch open), the terminal responds to the CB control line temporarily stopping data transmission. Transmisssion is halted by turning off the Transmit Ready Status bit.

- 3.8.2 This circuit is a 2-state, syschronous machine that is clocked at 16 times the transmit baud rate. CB must be stable at the middle of the last sixteenth of the last stop bit of a character with at least 150 nanoseconds of setup time. The Off state of CB signals a "busy" condition. If a "busy" signal appears at CB, then the transmission will be held off temporarily.

- 3.9 FIFO BUFFER

- 3.9.1 In order to give the main processor enough time to receive and process incoming characters from the datacom interface card, an extra layer of buffering (U14 and U15) is added to the existing one character buffer available within the UART. Serial data flow therefore is from the RS232C signal interface to the UART, the resulting parallel data is routed to the buffer and then finally is gated onto the backplane when the proper signal (from the processor) is received.

Figure 1 Enhanced Asynchronous Datacom Block Diagram OCT-15-79 13255-91239

Enhanced Asynchronous Datacom PCA Schematic Diagram OCT-15-79 13255-91239

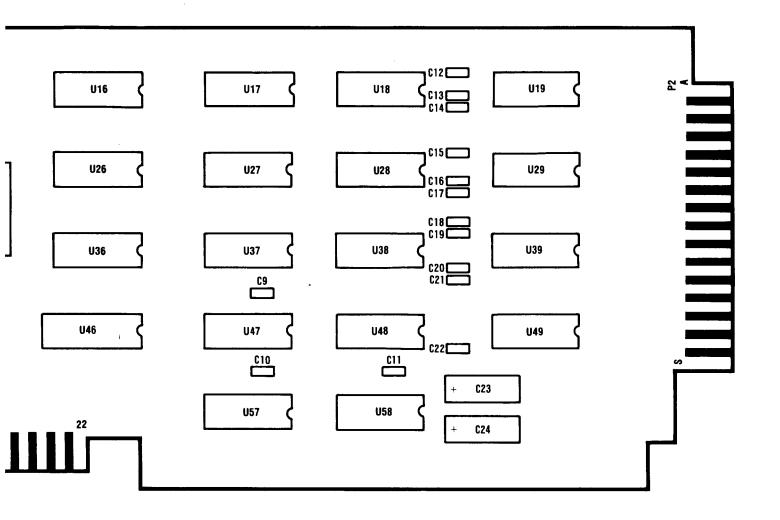

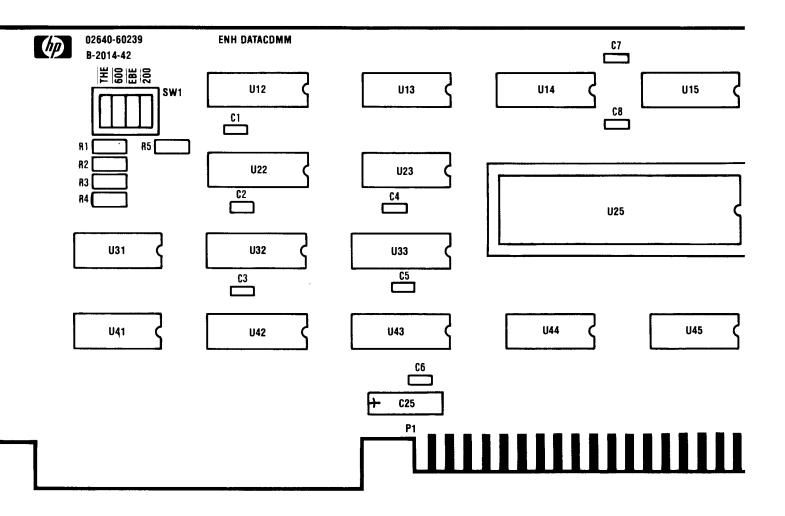

Figure 3

Enhanced Asynchronous Datacom PCA Component Location

Diagram

OCT-15-79

13255-91239

# Replaceable Parts

| Reference<br>Designation         | HP Part<br>Number                                             | C<br>D                | Qty              | Description                                                                                                                                                                                             | Mfr<br>Code                                        | Mfr Part Number                                                |

|----------------------------------|---------------------------------------------------------------|-----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|

|                                  | 02640-60239                                                   | 7                     | 1                | ENHANCED ASYNCH DATACOHM-PCA<br>DATA CODE:B-2014-42                                                                                                                                                     | 28480                                              | 02640-60239                                                    |

| C1<br>C2<br>C3<br>C4<br>C5       | 0160-4554<br>0160-4554<br>0160-4554<br>0160-4554<br>0160-4554 | 77777                 | 11               | CAPACITOR-FXD .01UF +-20% 50VDC CER CAPACITOR-FXD .01UF +-20% 50VDC CER CAPACITOR-FXD .01UF +-20% 50VDC CER CAPACITOR-FXD .01UF +-20% 50VDC CER CAPACITOR-FXD .01UF +-20% 50VDC CER                     | 28480<br>28480<br>28480<br>28480<br>28480          | 0160-4554<br>0160-4554<br>0160-4554<br>0160-4554<br>0160-4554  |

| C6<br>C7<br>C8<br>C9<br>C10      | 0160-4554<br>0160-4554<br>0160-4554<br>0160-4554<br>0160-4554 | 7<br>7<br>7<br>7<br>7 |                  | CAPACITOR-FXD .01UF +-20% 50VDC CER CAPACITOR-FXD .01UF +-20% 50VDC CER CAPACITOR-FXD .01UF +-20% 50VDC CER CAPACITOR-FXD .01UF +-20% 50VDC CER CAPACITOR-FXD .01UF +-20% 50VDC CER                     | 28480<br>28480<br>28480<br>28480<br>28480          | 0160-4554<br>0160-4554<br>0160-4554<br>0160-4554<br>0160-4554  |