#### INSTALLATION AND MAINTENANCE MANUAL

### MODEL 2100S MICROPROGRAMMABLE SYSTEMS COMPUTER

#### **SERIAL NUMBERS COVERED**

This manual applies directly to Model 2100S Computers having serial numbers prefixed 1314, 1320, 1322, 1330, 1333, 1345, 1402, 1410, 1420, 1435, and 1449. Computers with higher prefix numbers will be covered in manual updating supplements.

#### **OPTIONS COVERED**

This manual covers options 015, 024, and 032 as well as the basic computer.

#### **ACCESSORIES COVERED**

This manual covers the following accessory kits:

12885A-003 and 12885A-004 Memory (8K Increments) Accessory Kits

Field installation of the above accessory kits is covered in separate manuals.

### **CONTENTS**

| Secti | on             |                                                               | Page  |

|-------|----------------|---------------------------------------------------------------|-------|

| I     | GENER          | AL INFORMATION                                                |       |

|       | 1-1.           | Introduction                                                  | 1-1   |

|       | 1-3.           | Scope                                                         | 1-2   |

|       | 1-7.           | General Description                                           | 1-3   |

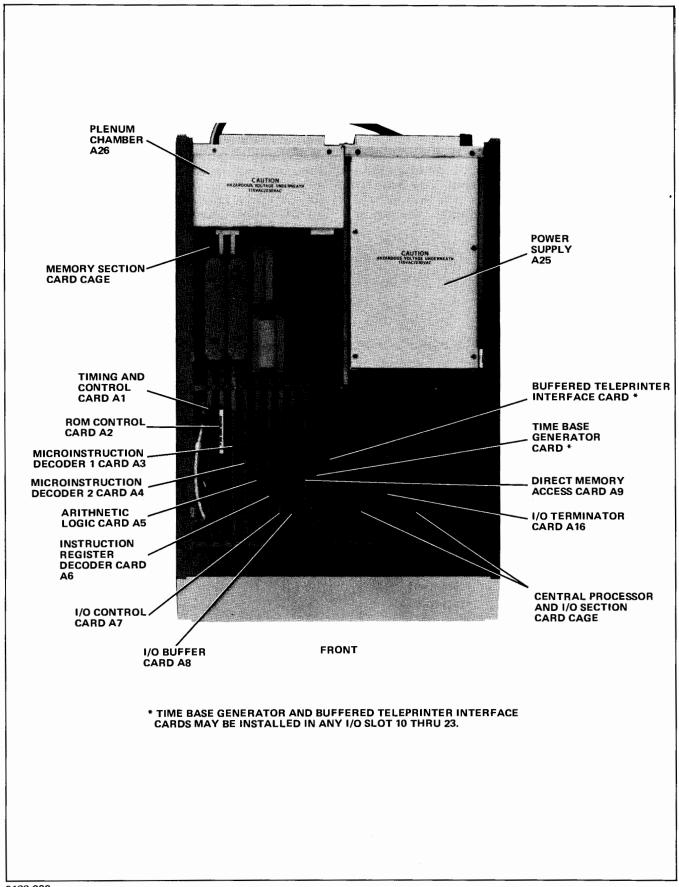

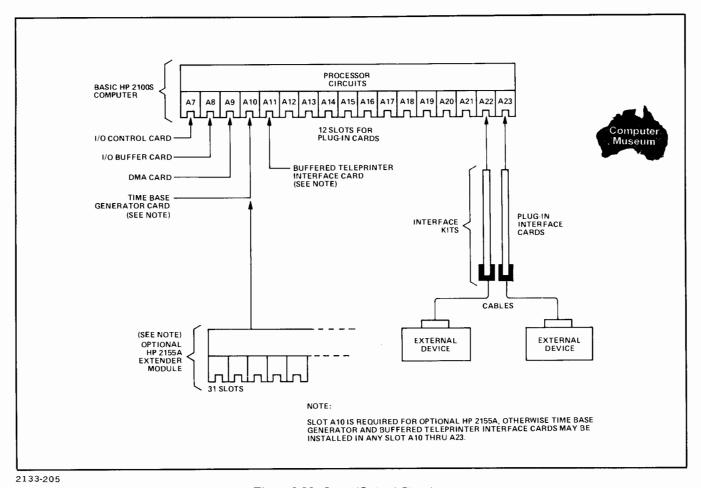

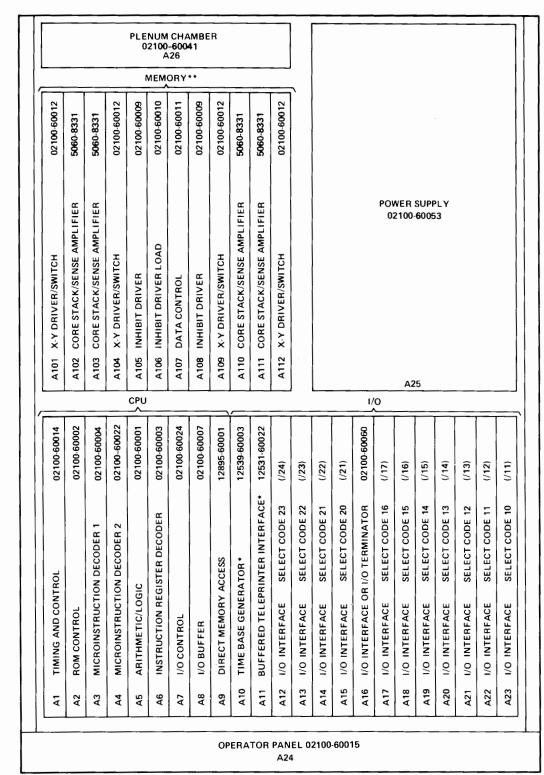

|       | 1-8.           | Computer Assemblies                                           | 1-3   |

|       | 1-10.          | Circuit Cards                                                 | 1-3   |

|       | 1-14.          | Operator Panel                                                | 1-6   |

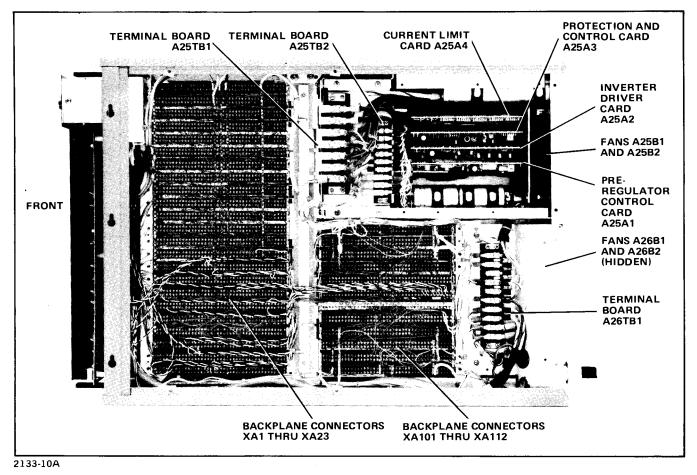

|       | 1-15.          | Power Supply Section                                          | 1.6   |

|       | 1-17.          | Backplane Assembly                                            |       |

|       | 1-17.          |                                                               | 1-6   |

|       | 1-10.<br>1-19. | Processor Options                                             |       |

|       |                | - ' - '                                                       |       |

|       | 1-20.          | Memory Sizes                                                  |       |

|       | 1-23.          | Input/Output Accessories                                      |       |

|       | 1-24.          | Panel Controls and Indicators                                 |       |

|       | 1-26.          | Specifications                                                |       |

|       | 1-28.          | Identification                                                |       |

|       | 1-29.          | Computer Model Number                                         | 1-8   |

|       | 1-31.          | Computer Serial Number                                        | 1-8   |

|       | 1-33.          | Option Numbers                                                | 1-10  |

|       | 1-36.          | Assembly Part Numbers                                         | 1-10  |

|       | 1-39.          | Circuit-Card Revision Codes                                   | 1-10  |

|       | 1-41.          | Power Supply Date Code                                        | 1-13  |

|       | 1-43.          | Documentation of Equipment Improvements                       |       |

|       | 1-45.          | Maintenance Accessories and Service Items                     |       |

|       | 1.47.          | Maintenance Accessory Kit                                     |       |

|       | 1-49.          | Card Extenders                                                |       |

|       | 1.49.          | Extension Cables                                              |       |

|       | 1-50.<br>1-51. | Memory Current Sense Cable                                    |       |

| ,     |                |                                                               |       |

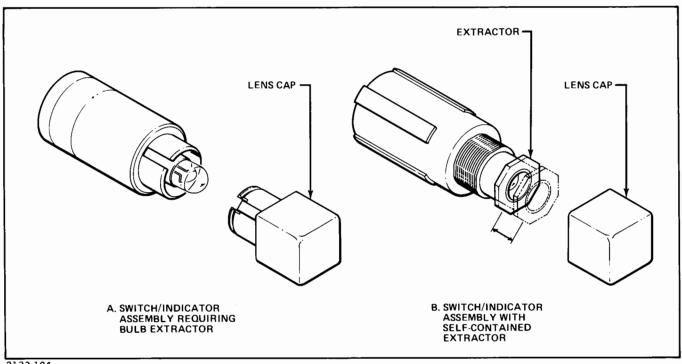

|       | 1-52.          | Light Bulb Extractor                                          |       |

|       | 1-53.          | Rack Mounting Kit                                             |       |

|       | 1-55.          | Manuals                                                       |       |

|       | 1-57.          | Maintenance Features                                          |       |

|       | 1-59.          | Recommended Maintenance Tools, Parts, Materials and Equipment |       |

|       | 1-60.          | Tools                                                         | 1-13  |

|       | 1-65.          | Parts and Materials                                           | 1-16  |

|       | 1-68.          | Servicing Equipment                                           | 1-16  |

|       | 1-70.          | Field Office Assistance                                       | 1-16  |

|       |                |                                                               |       |

| II    | INSTA          | LLATION                                                       |       |

|       | 2-1.           | Introduction                                                  | . 2-1 |

|       | 2-4.           | Inspection of Shipment                                        |       |

|       | 2-11.          | Physical Inventory                                            |       |

|       | 2-12.          | Manuals                                                       |       |

|       | 2-14.          | Equipment                                                     |       |

|       | 2.18.          | Program Tapes                                                 |       |

|       | 2-10.          | Installation Procedure                                        |       |

|       | 2-20.<br>2-21. |                                                               |       |

|       |                | Manual Updating                                               |       |

|       | 2-23.          | Environmental Requirements                                    |       |

|       | 2-26.          | Power Requirements                                            |       |

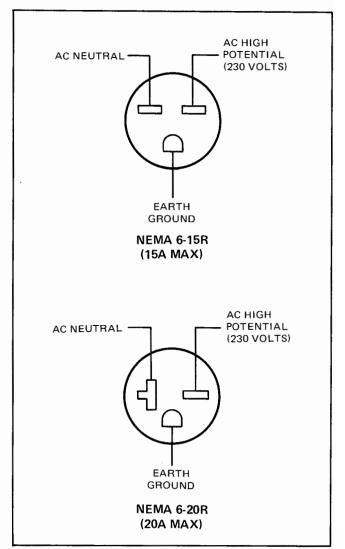

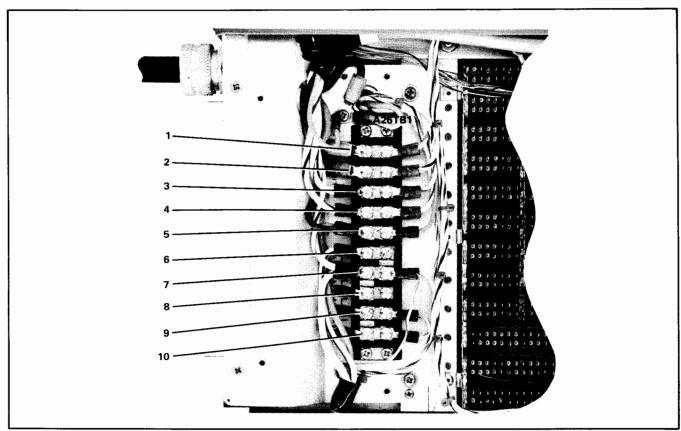

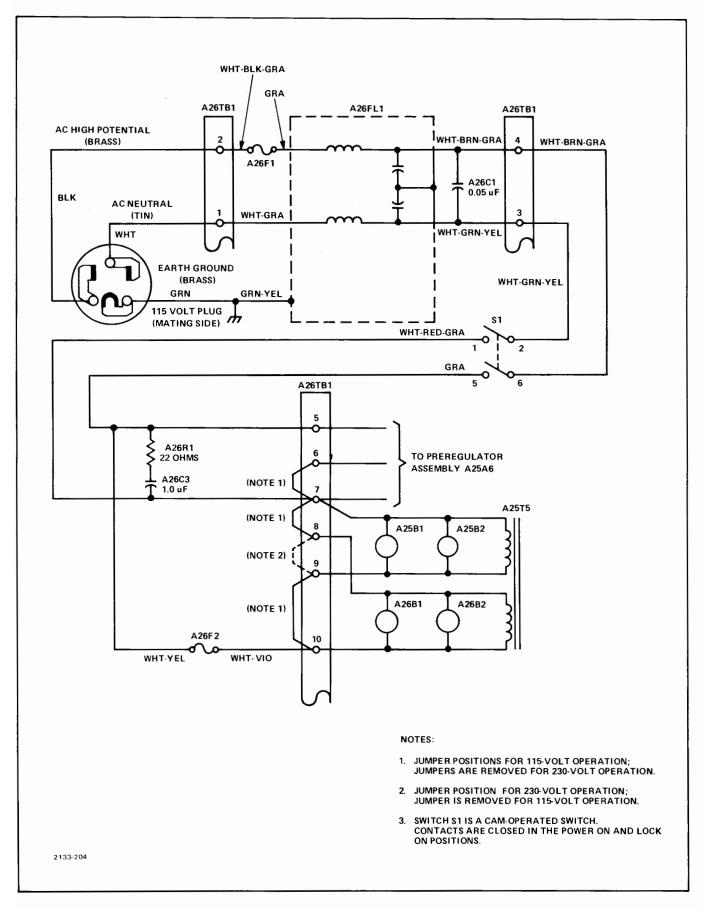

|       | 2-29.          | AC Power Outlet and External Ground                           |       |

|       | 2-36.          | AC Power Cable                                                |       |

|       | 2-39.          | Power Supply Checkout                                         |       |

|       | 2-41.          | Mounting                                                      |       |

|       | 2-45.          | Performance Check                                             |       |

|       | 2 47           | Claims                                                        | 2.7   |

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

| Secti | on                      | Page                                                                                                                                            |

|-------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 2-49.<br>2-50.<br>2-52. | Repackaging for Shipment         2-7           Shipment Using Original Packaging         2-7           Shipment Using New Packaging         2-7 |

|       |                         |                                                                                                                                                 |

| III   | THEOR                   | LY OF OPERATION                                                                                                                                 |

|       | 3-1.                    | Introduction                                                                                                                                    |

|       | 3-3.                    | Reference Information                                                                                                                           |

|       | 3-5.                    | Binary Signal Levels                                                                                                                            |

|       | 3-7.                    | Logic Circuits                                                                                                                                  |

|       | 3-10.                   | Signal Names                                                                                                                                    |

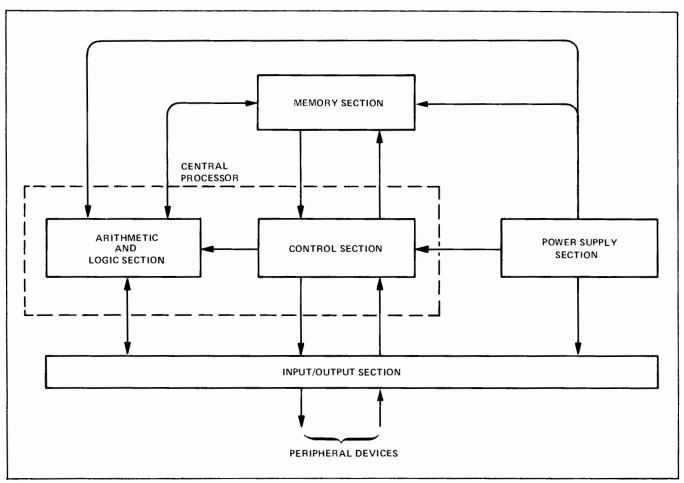

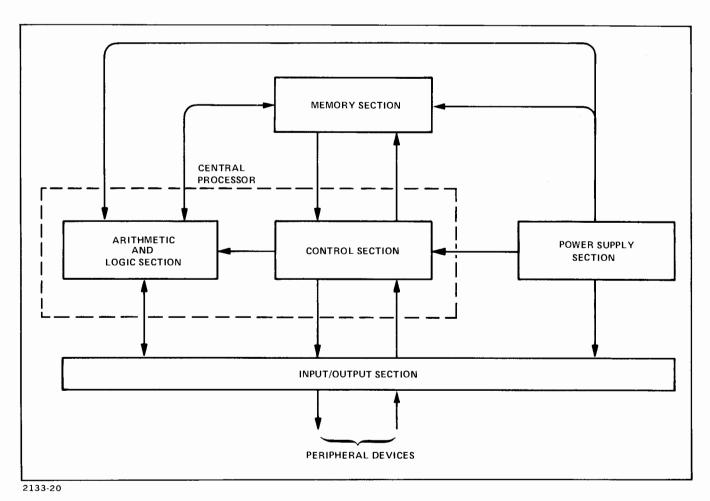

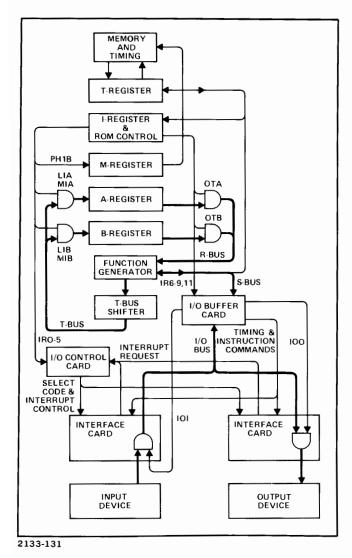

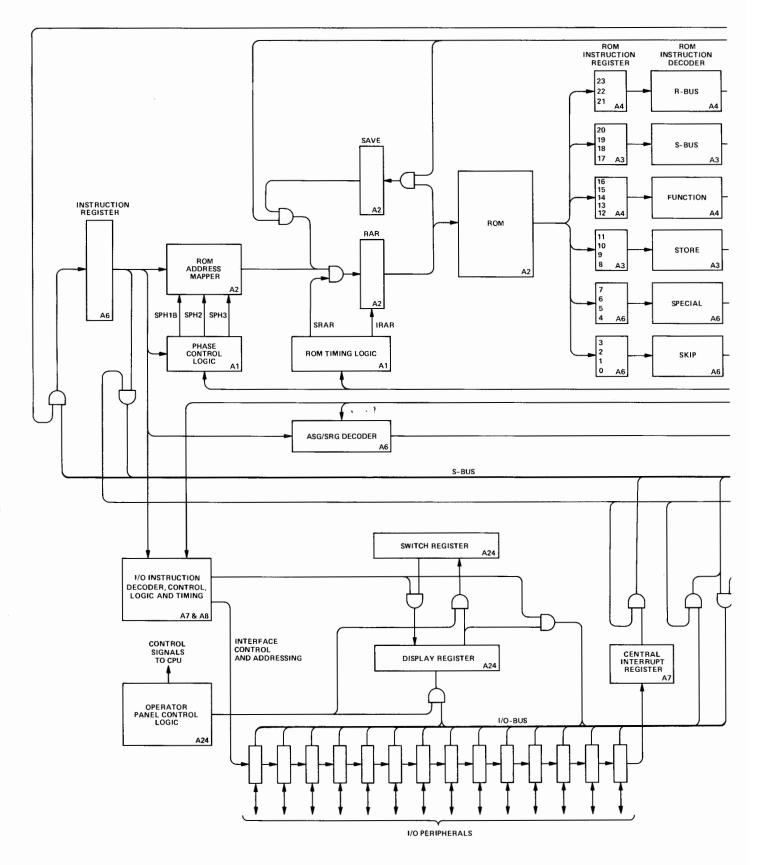

|       | 3-19.                   | Computer Functional Sections                                                                                                                    |

|       | 3-21.                   | Memory                                                                                                                                          |

|       | 3-23.                   | Arithmetic and Logic                                                                                                                            |

|       | 3-25.                   | Input/Output 3-2                                                                                                                                |

|       | 3-27.                   | Control                                                                                                                                         |

|       | 3-29.                   | Power Supply                                                                                                                                    |

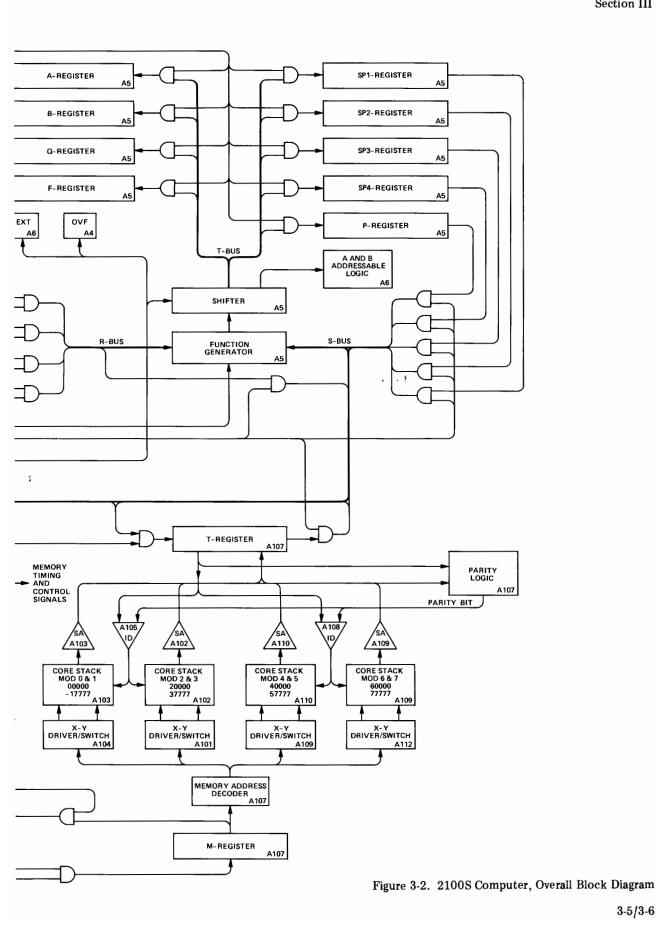

|       | 3-32.                   | Overall Block Diagram Discussion                                                                                                                |

|       | 3-34.                   | Bus System                                                                                                                                      |

|       | 3-36.                   | Memory Section                                                                                                                                  |

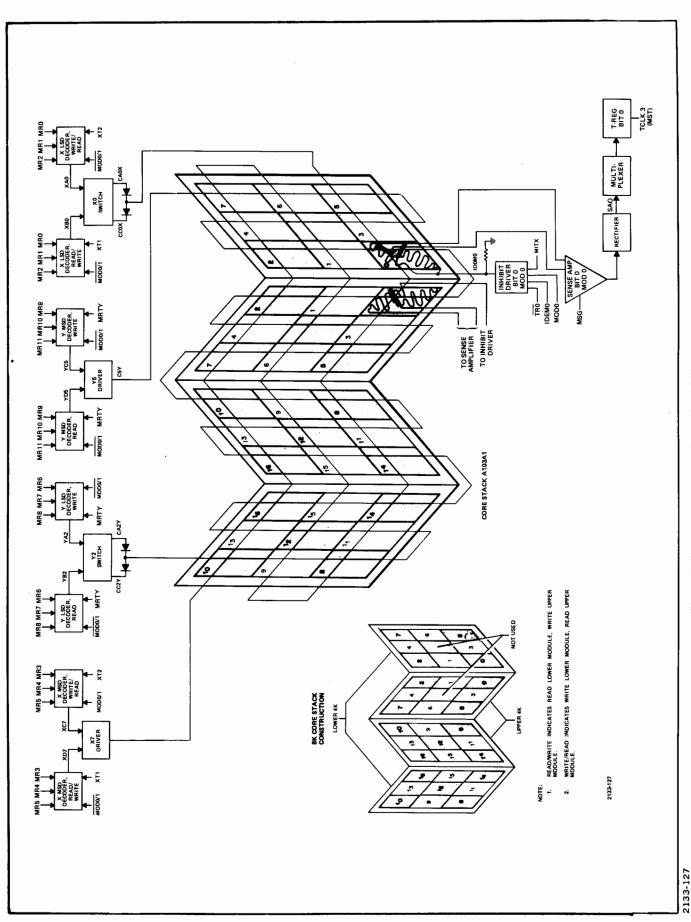

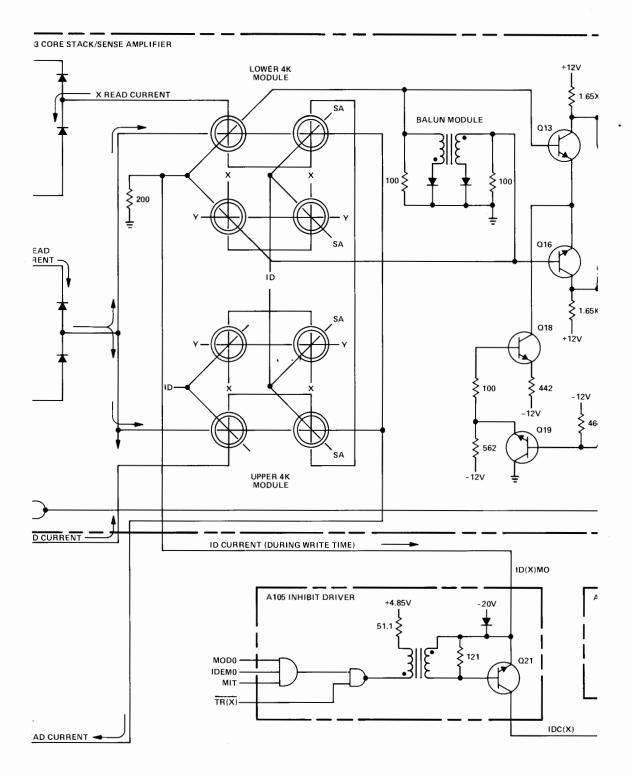

|       | 3-38.                   | Core Stack                                                                                                                                      |

|       | 3-40.                   | Memory Timing and Control                                                                                                                       |

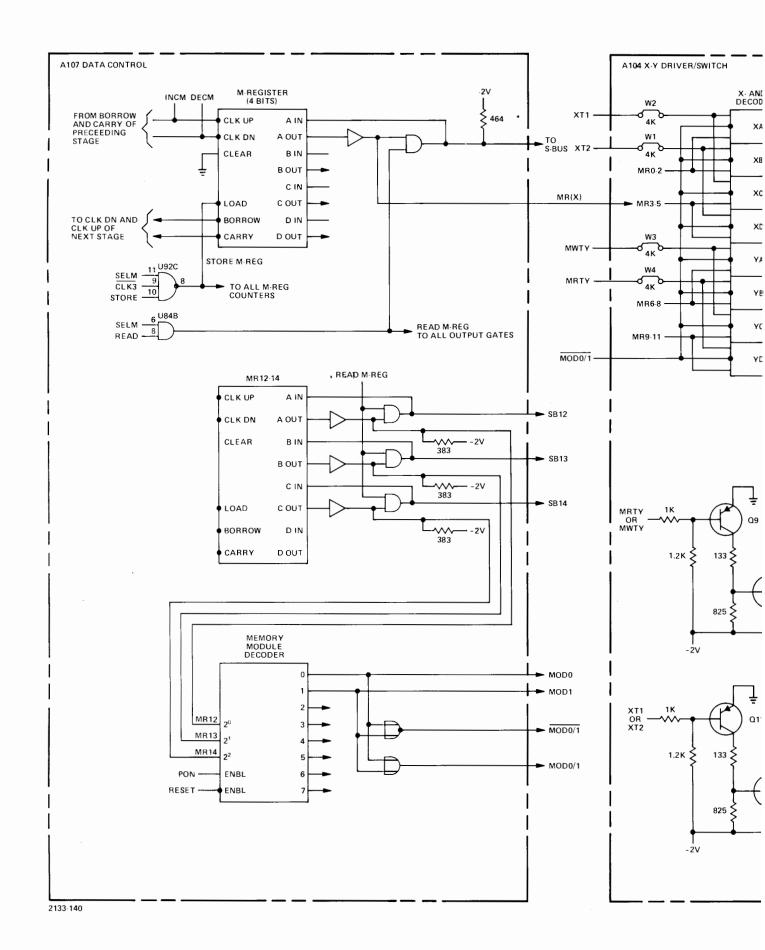

|       | 3-41.                   | Memory Section Registers                                                                                                                        |

|       | 3-42.                   | Memory Address Decoder                                                                                                                          |

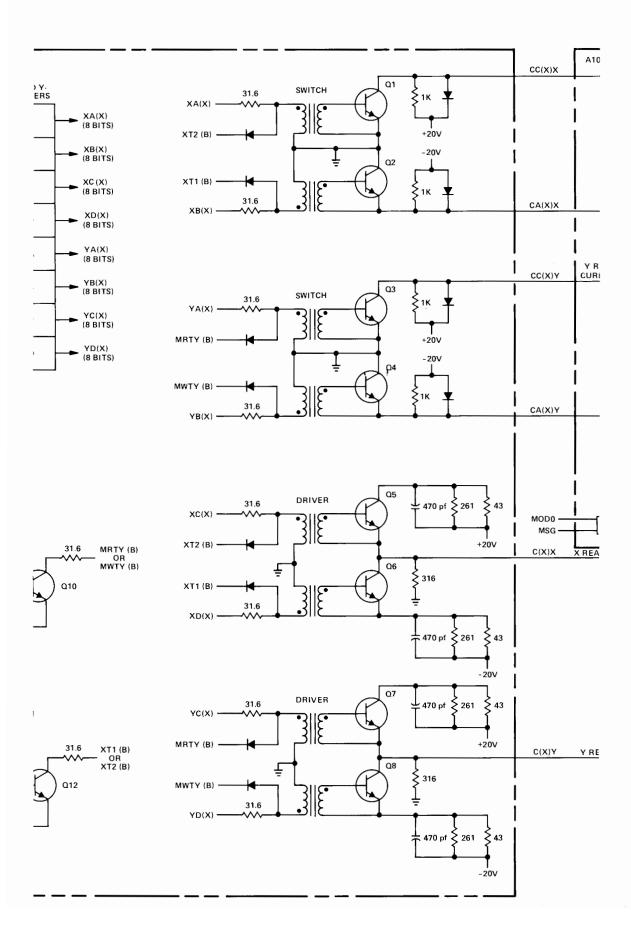

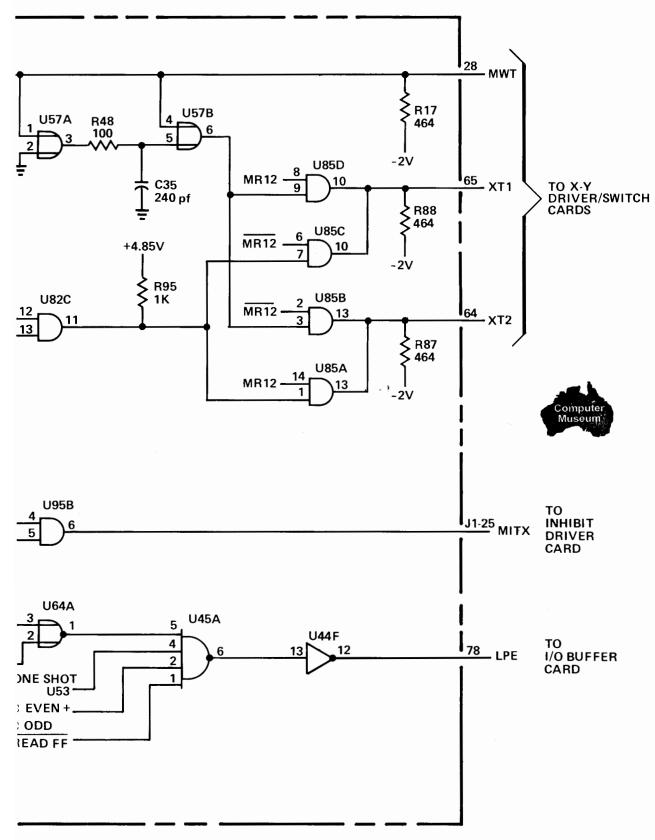

|       | 3-43.                   | X/Y Driver/Switches                                                                                                                             |

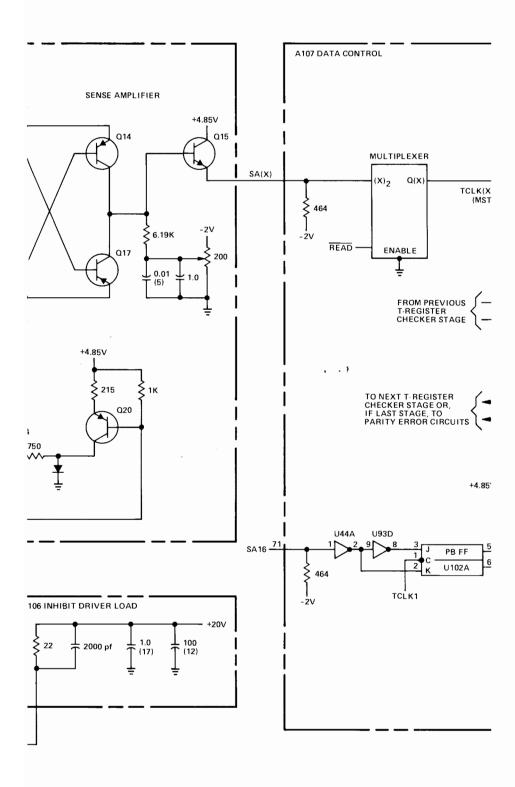

|       | 3-44.                   | Sense Amplifiers                                                                                                                                |

|       | 3-45.                   | Inhibit Drivers                                                                                                                                 |

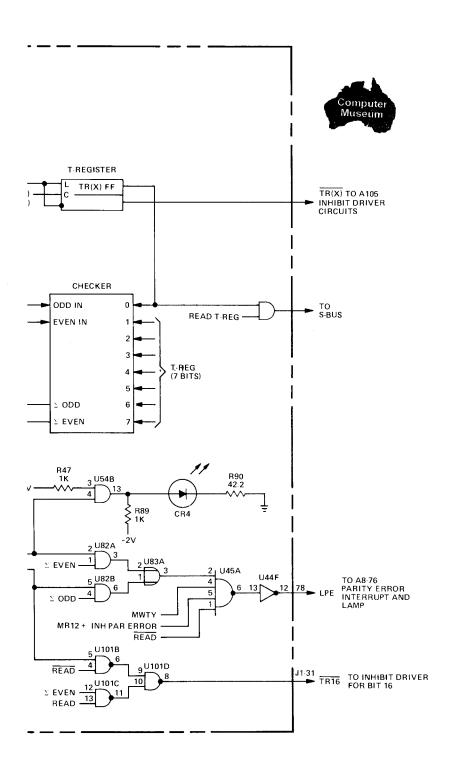

|       | 3-46.                   | Parity Logic                                                                                                                                    |

|       | 3-47.                   | Arithmetic and Logic Section                                                                                                                    |

|       | 3-47.<br>3-49.          |                                                                                                                                                 |

|       | 3-49.<br>3-50.          |                                                                                                                                                 |

|       | 3-50.<br>3-51.          |                                                                                                                                                 |

|       | 3-51.<br>3-52.          |                                                                                                                                                 |

|       | 3-52.<br>3-53.          |                                                                                                                                                 |

|       | 3-54.                   |                                                                                                                                                 |

|       | 3-54.<br>3-55.          | Function Generator                                                                                                                              |

|       | 3-56.                   | Shifter                                                                                                                                         |

|       | 3-50.<br>3-57.          | A- and B-Addressable Logic FFs                                                                                                                  |

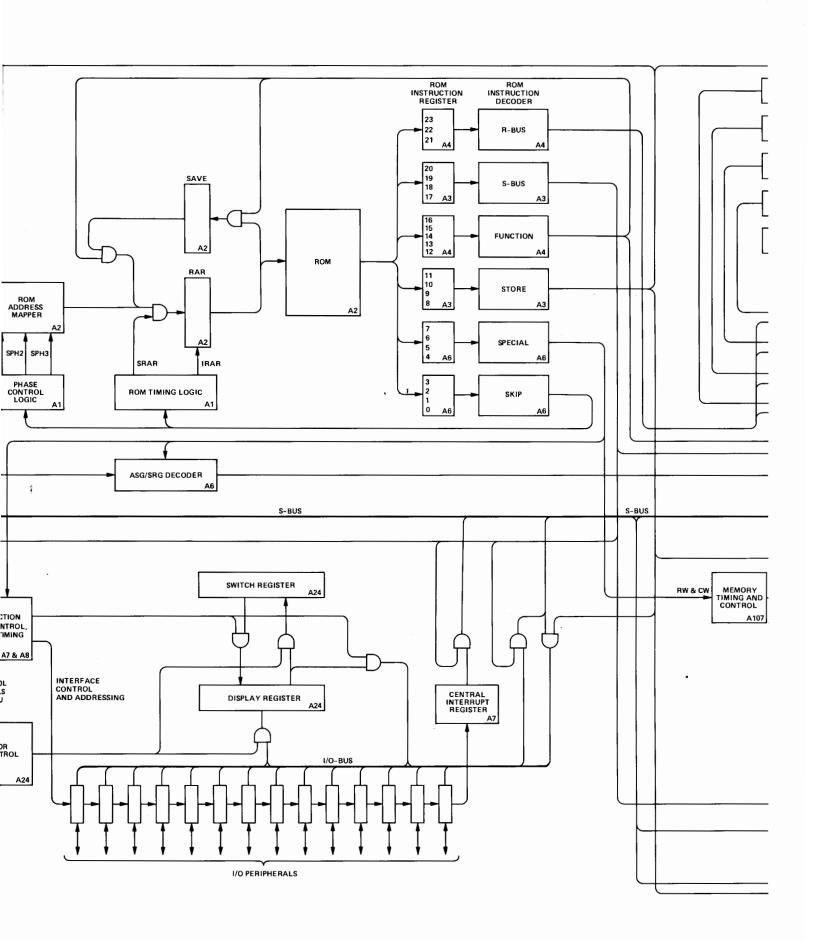

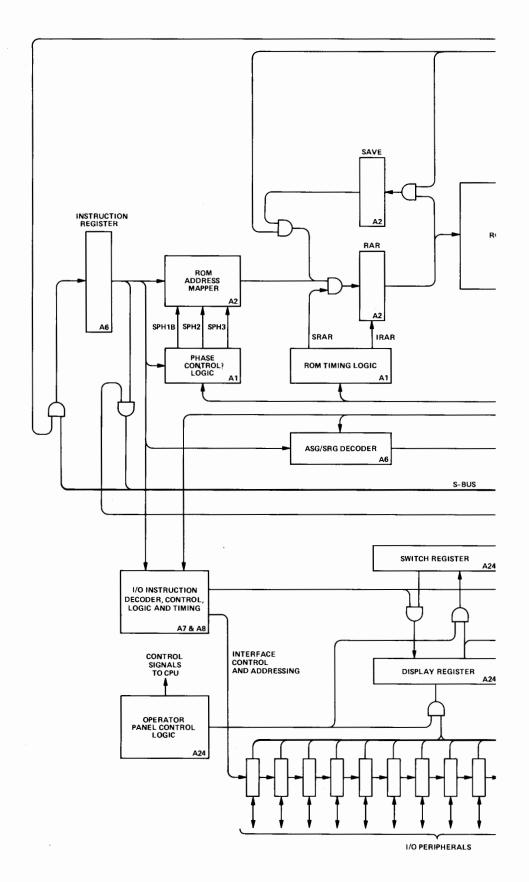

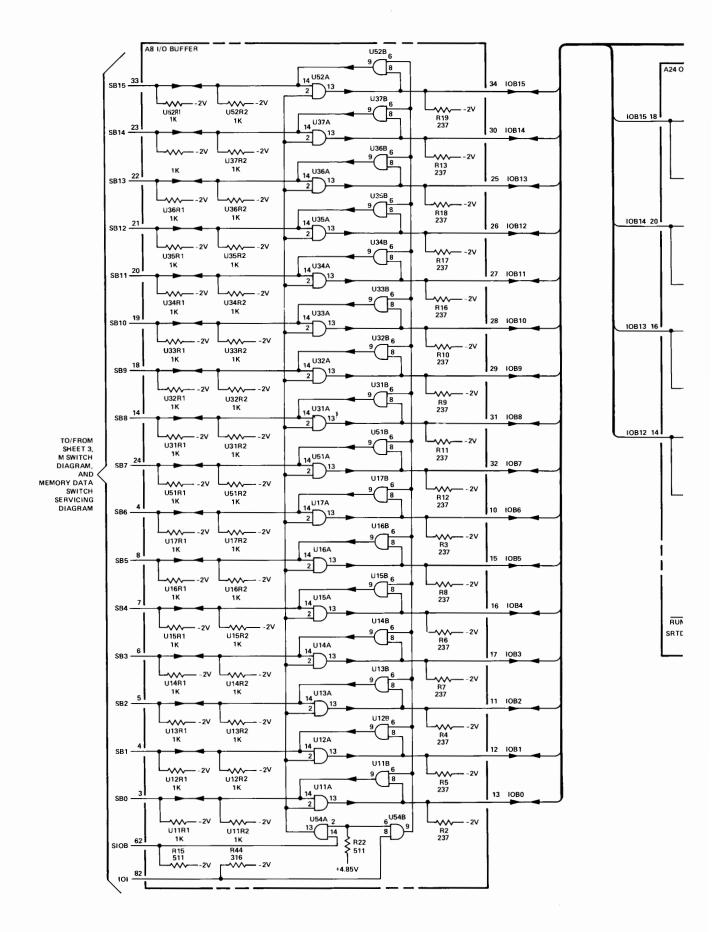

|       | 3-57.<br>3-59.          | Input/Output Section                                                                                                                            |

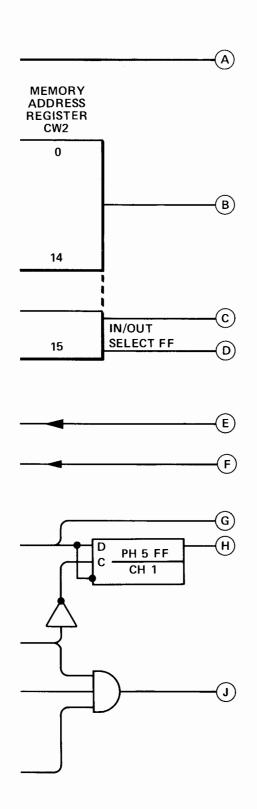

|       | 3-60.                   | I/O Section Registers                                                                                                                           |

|       | 3-60.<br>3-61.          | Central Interrupt Register                                                                                                                      |

|       | 3-61.<br>3-62.          | S-Register                                                                                                                                      |

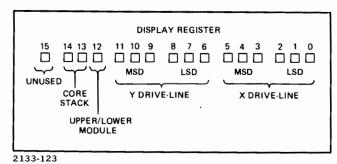

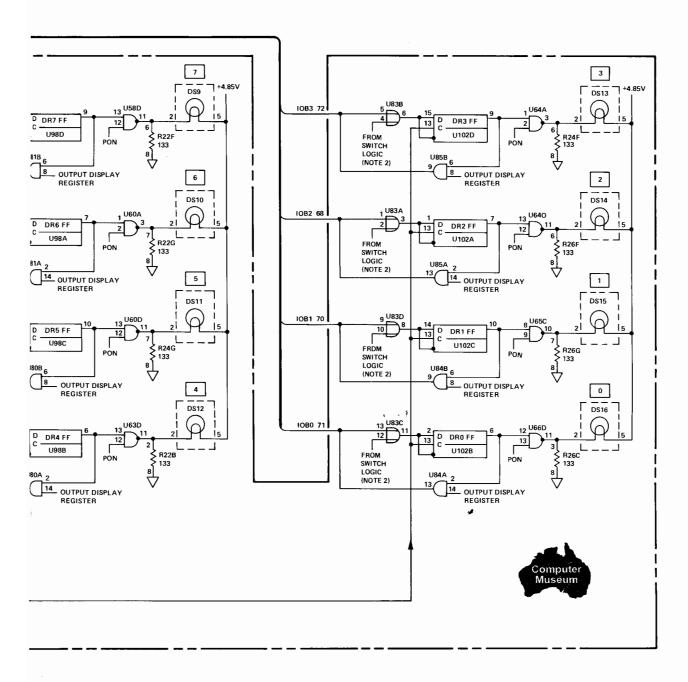

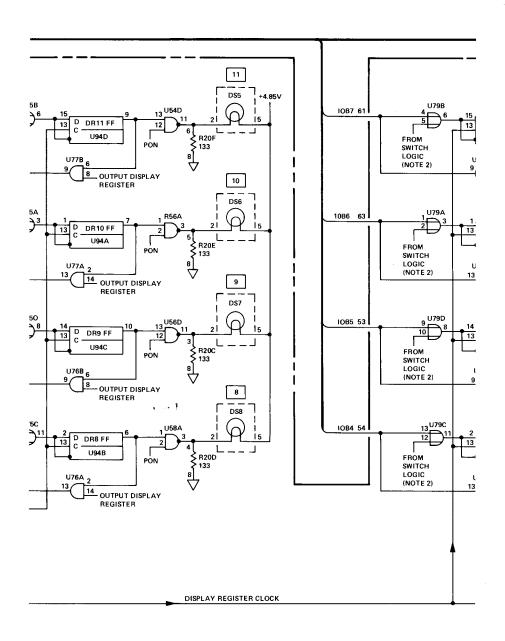

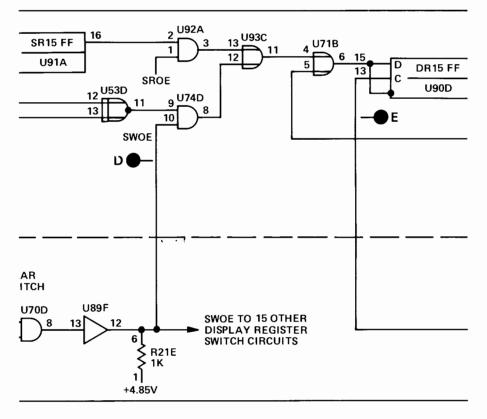

|       | 3-62.<br>3-63.          | Display Register                                                                                                                                |

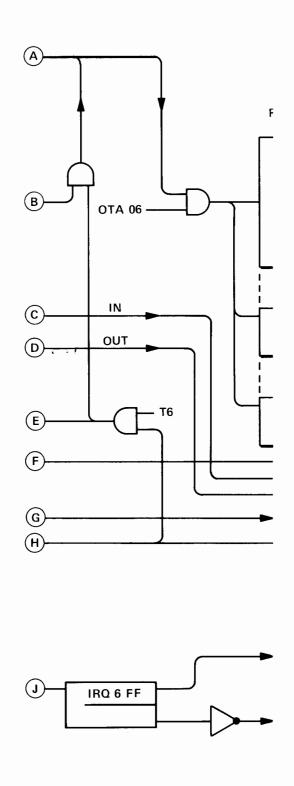

|       | 3-65.                   | I/O Instruction Decoder, Control Logic, and Timing                                                                                              |

|       | 3-68.                   | Interface Cards                                                                                                                                 |

|       | 3-08.<br>3-73.          |                                                                                                                                                 |

|       |                         | Instruction Register                                                                                                                            |

|       | 3-74.                   | Phase Control Logic                                                                                                                             |

|       | 3-75.                   | ROM Address Mapper                                                                                                                              |

|       | 3-76.                   | ROM Address Register                                                                                                                            |

|       | 3-77.                   | Save Register                                                                                                                                   |

|       | 3-78.                   | ROM                                                                                                                                             |

|       | 3-79.                   | ROM Instruction Register                                                                                                                        |

|       | 3-80.                   | ROM Instruction Decoder                                                                                                                         |

|       | 3-81.                   | SRG/ASG Decoder                                                                                                                                 |

|       | 3-82.                   | Computer Functional Operation                                                                                                                   |

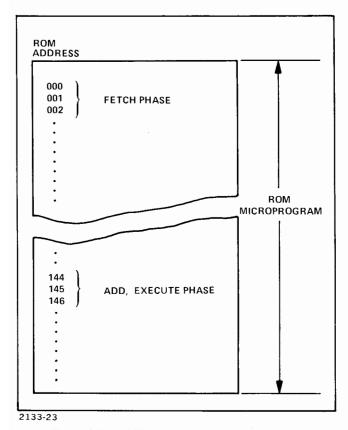

|       | 3-84                    | ROM Microprogram Control                                                                                                                        |

| Section          |                                      | Page   |

|------------------|--------------------------------------|--------|

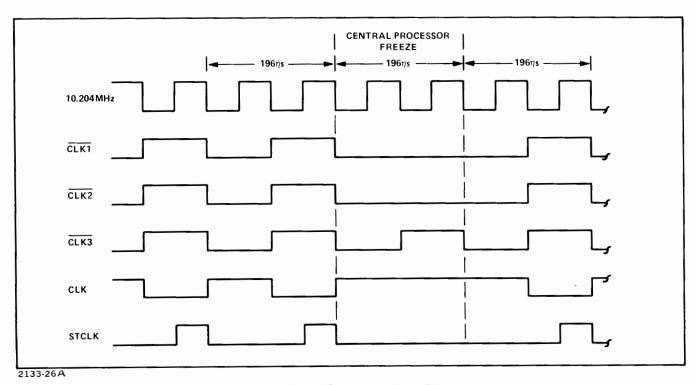

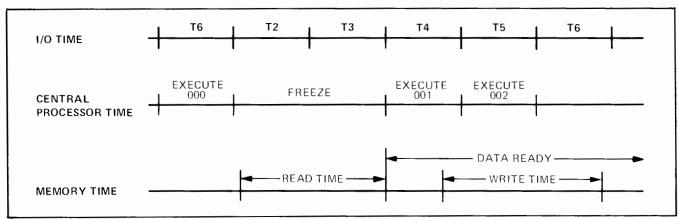

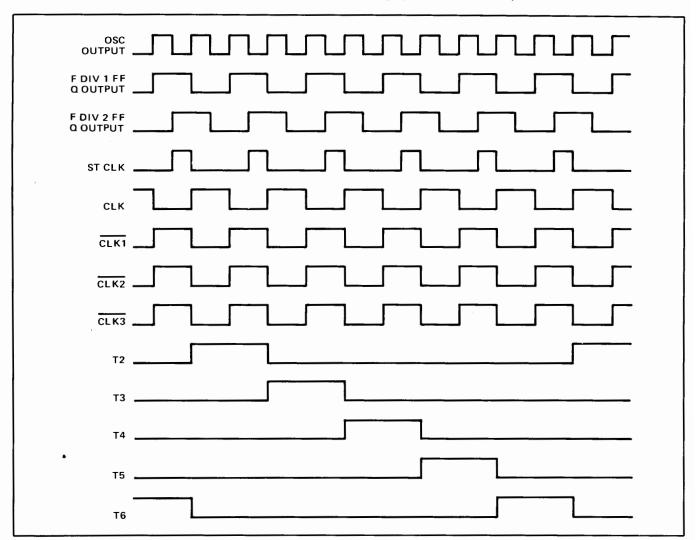

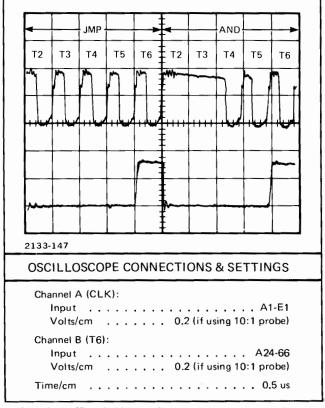

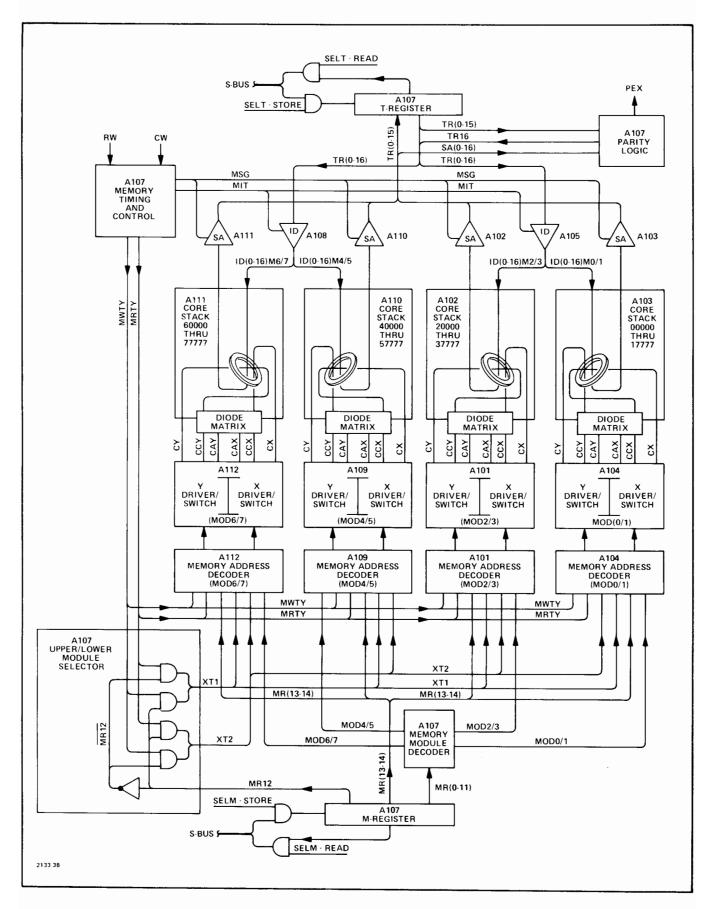

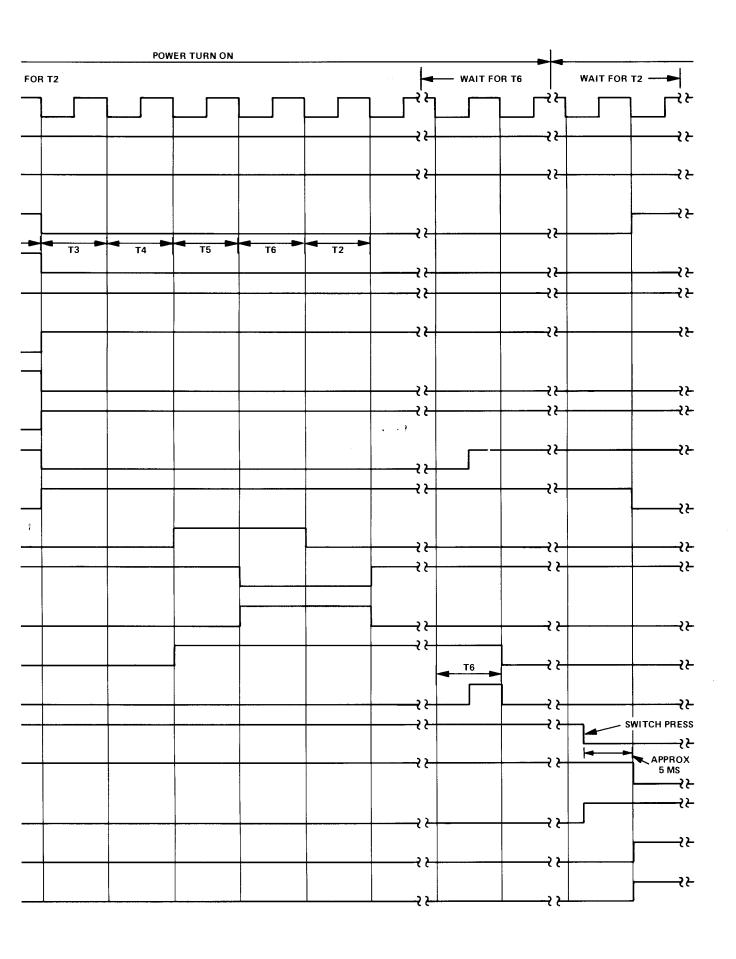

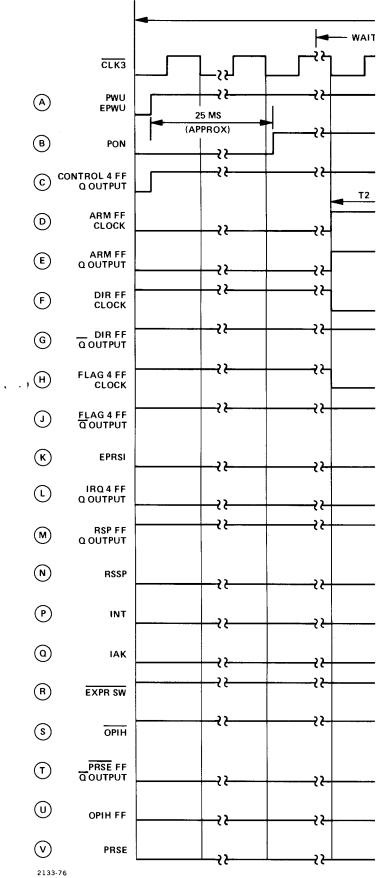

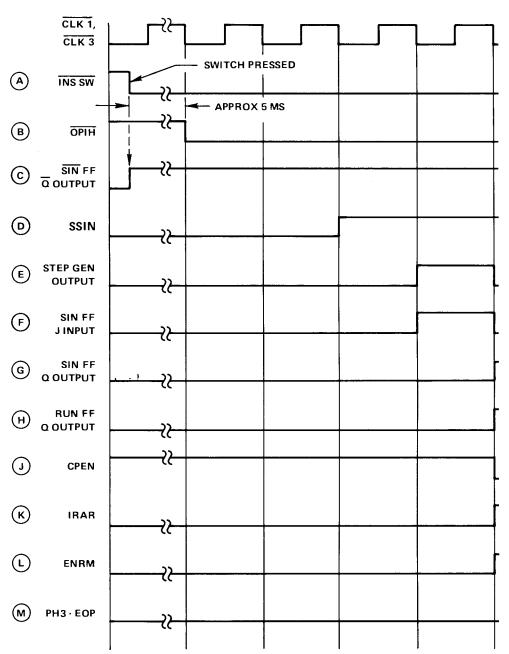

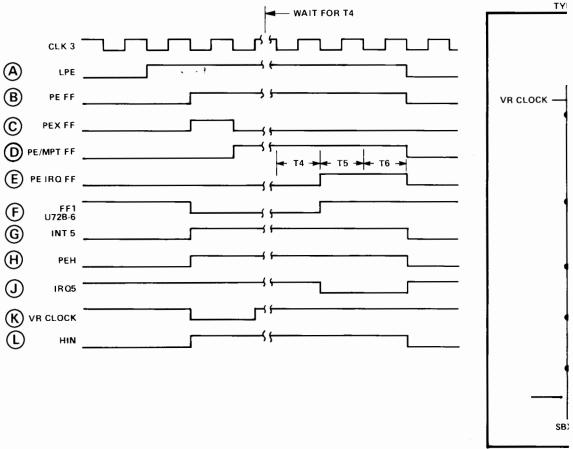

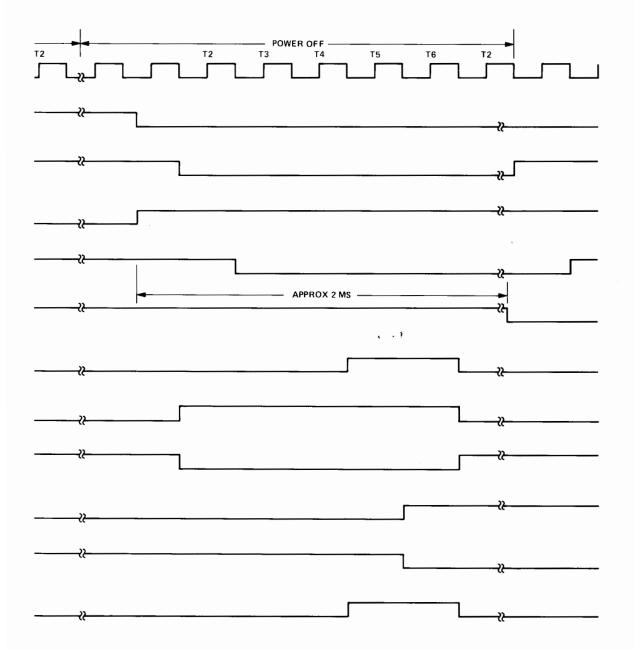

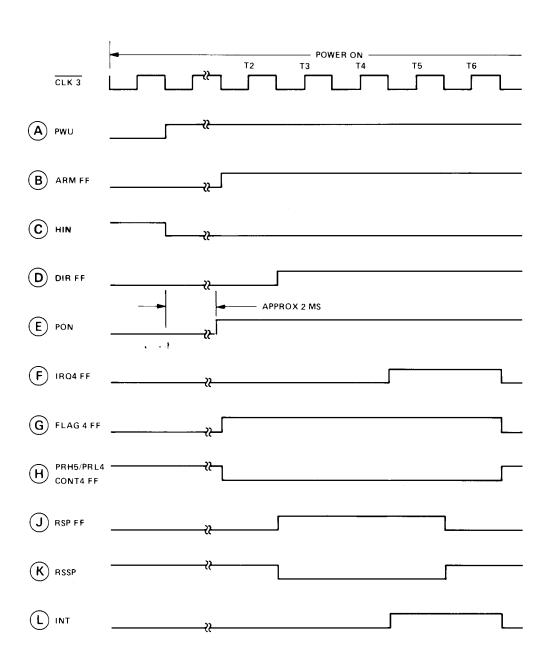

| 3-96.            | Computer Timing                      | 3-10   |

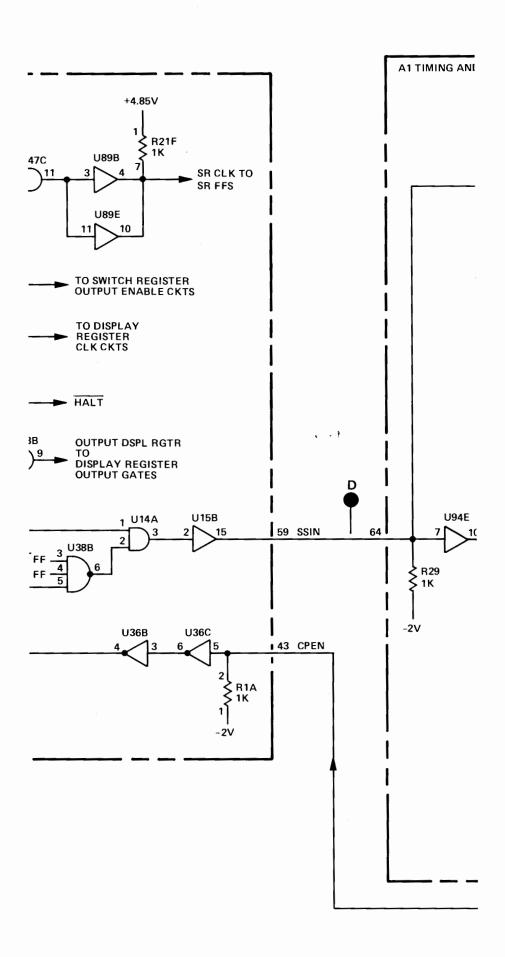

| 3-99.            | I/O Section Timing                   | 3-10   |

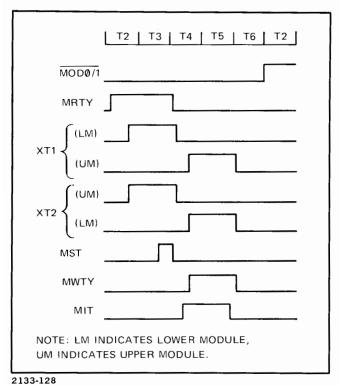

| 3-101.           | Memory Section Timing                |        |

| 3-102.           | Memory Read Time                     |        |

| 3-103.           | Memory Write Time                    |        |

| 3-105.           | Central Processor Timing             |        |

| 3-117.           | Phases of Operation                  |        |

| 3-119.           | Fetch Phase                          |        |

| 3-120.           | Indirect Phase                       |        |

| 3-121.           | Execute Phase                        |        |

| 3-122.           | Phase 5                              |        |

| 3-123.           | Set Phase Logic                      |        |

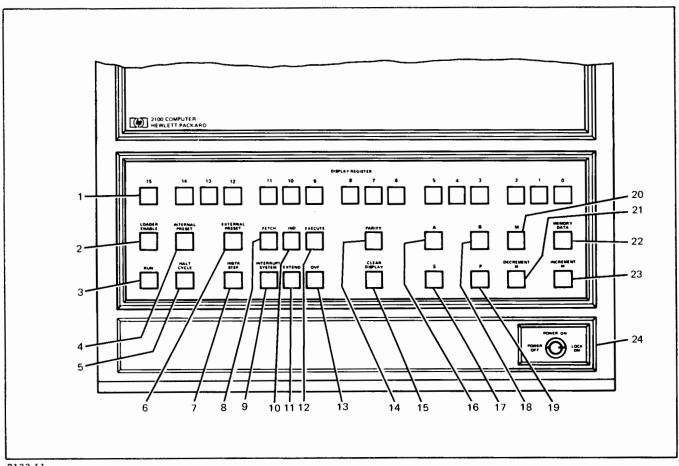

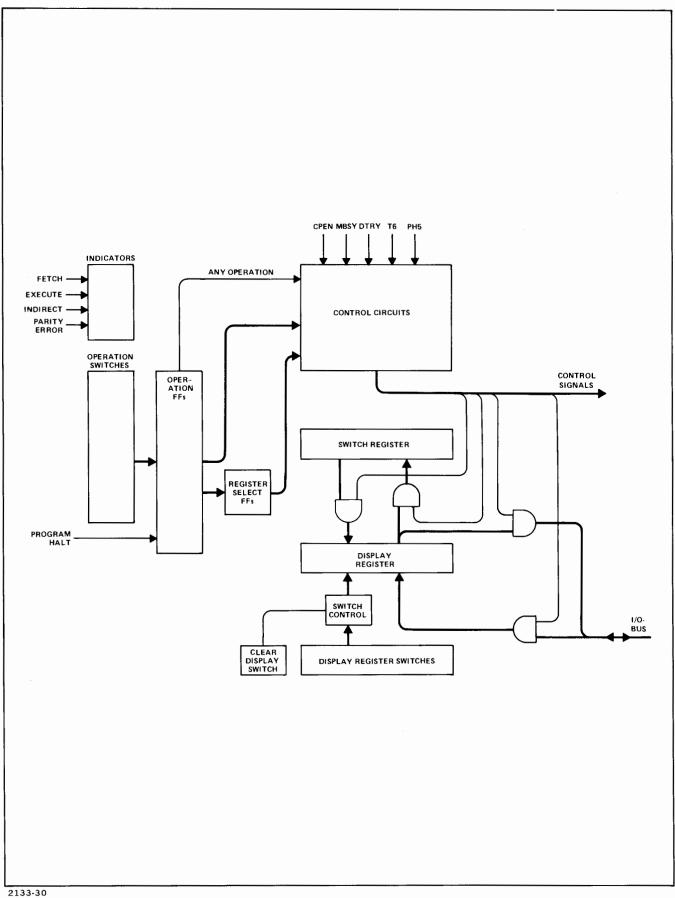

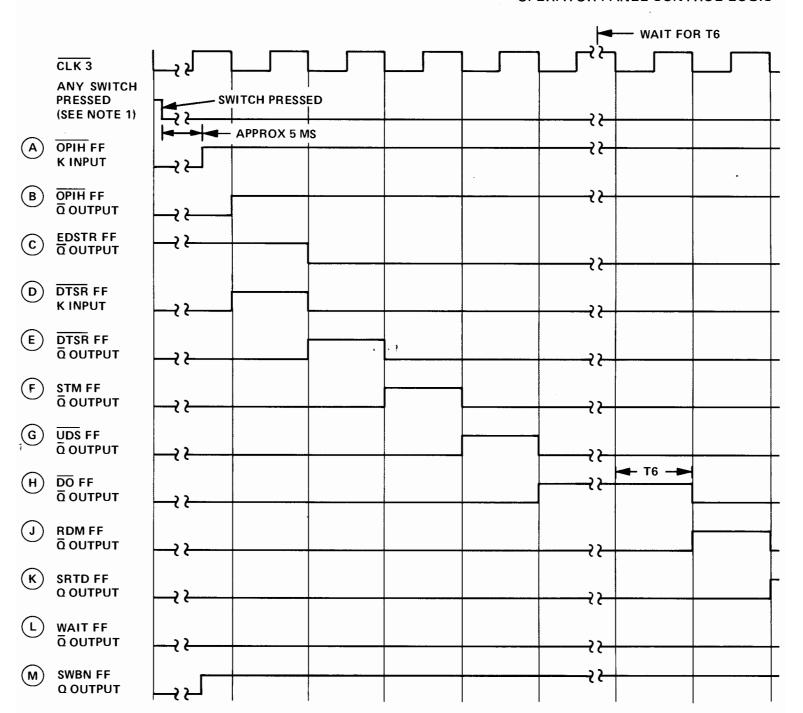

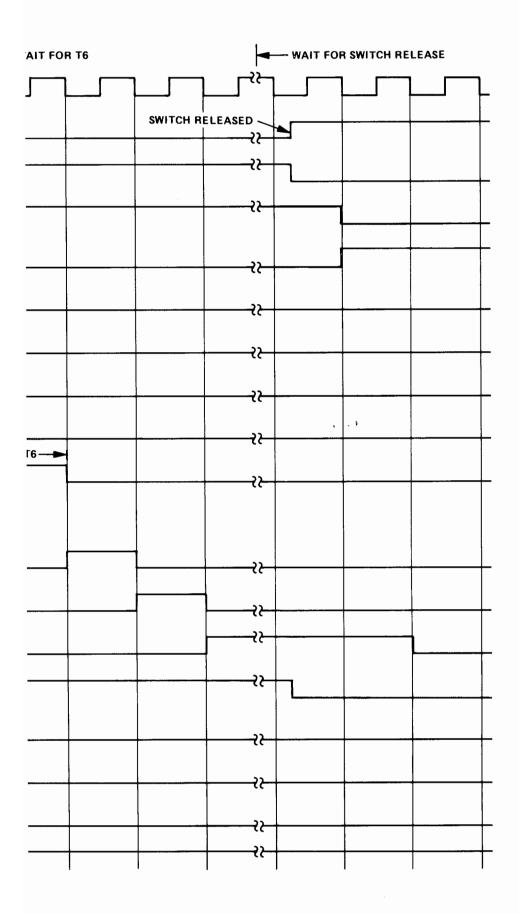

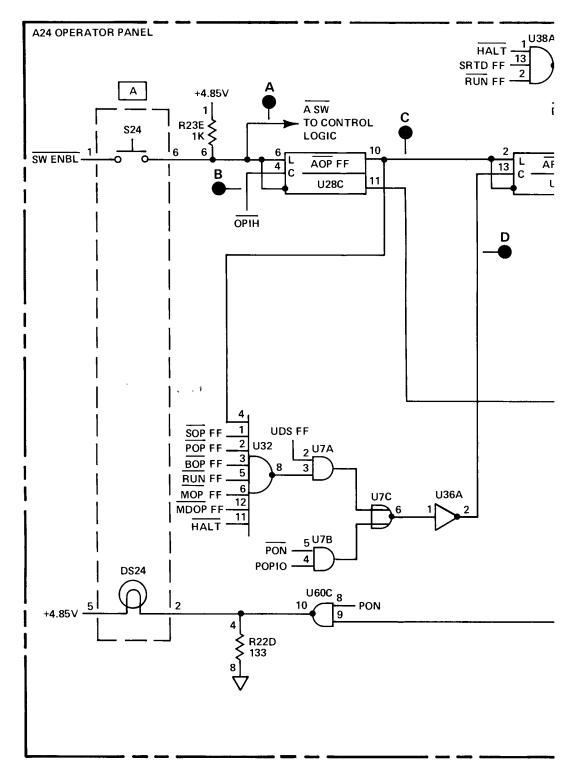

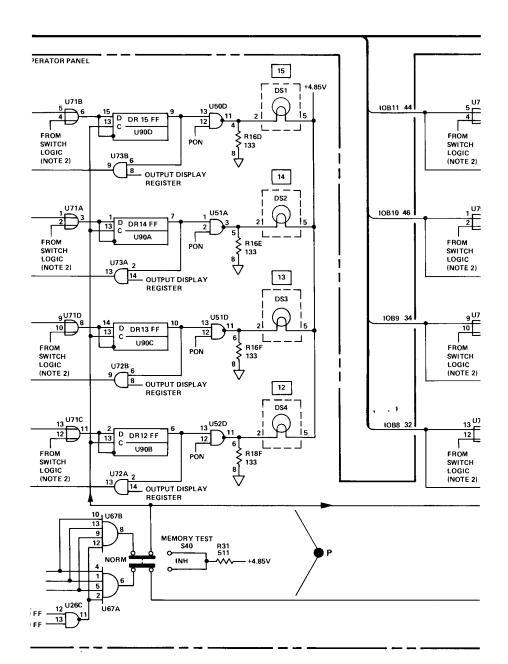

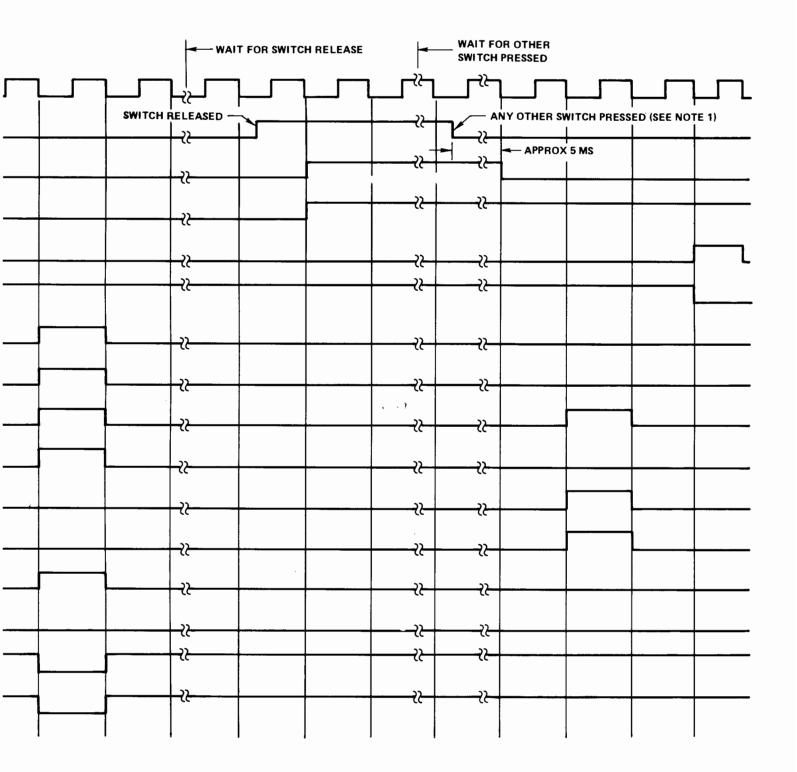

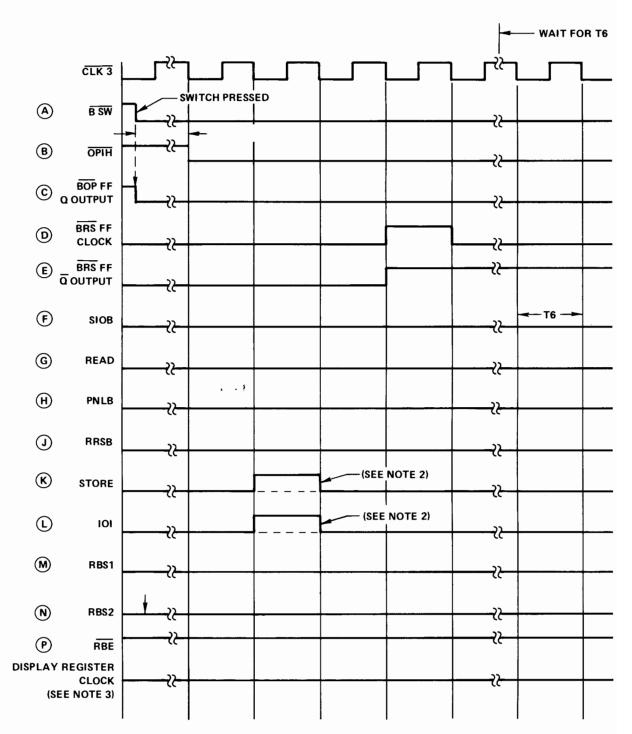

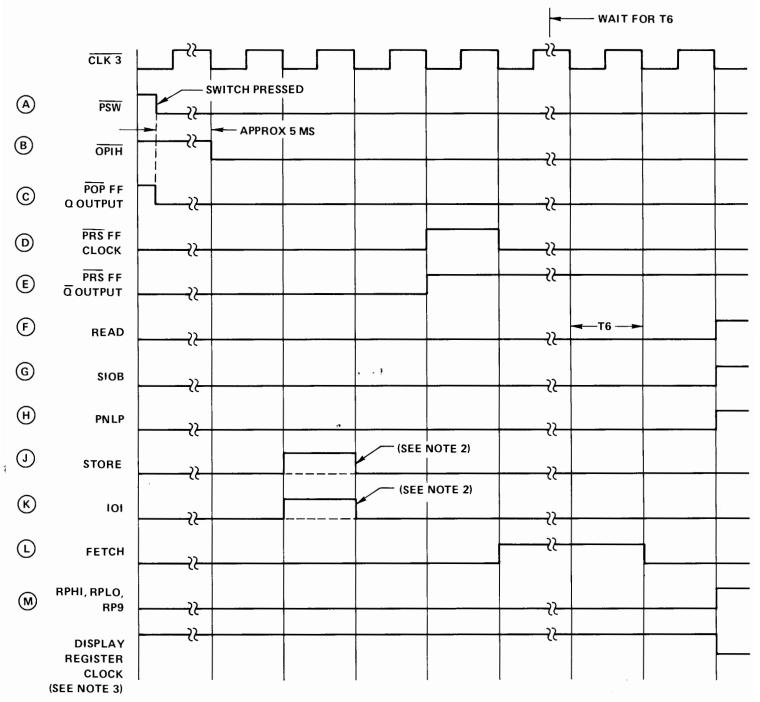

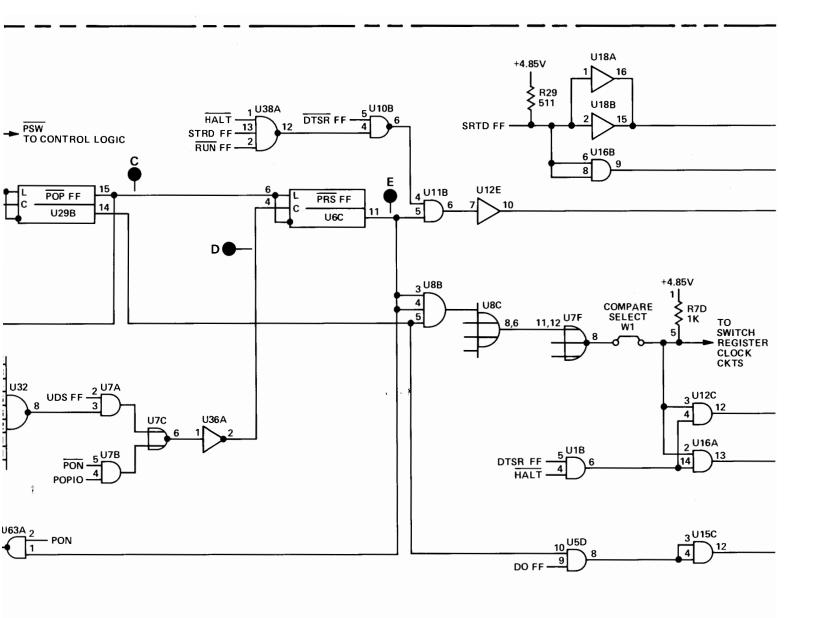

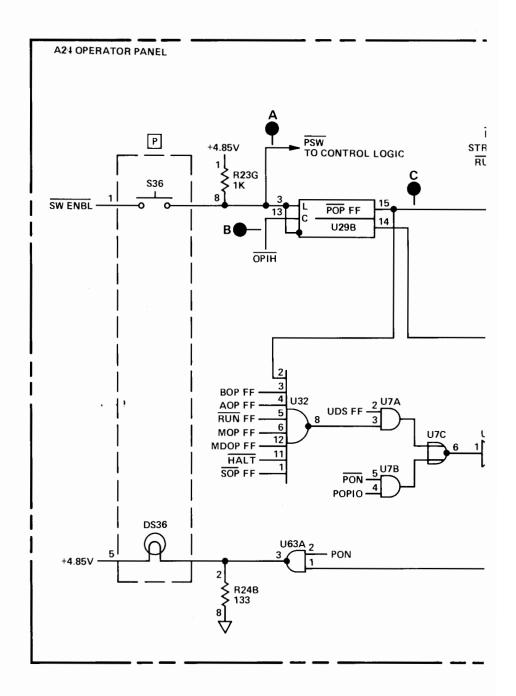

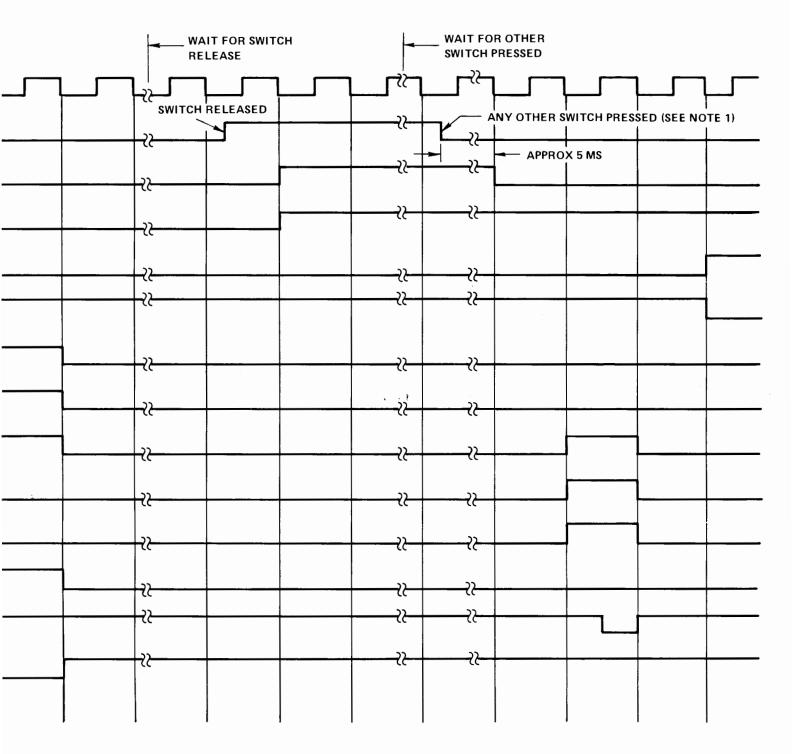

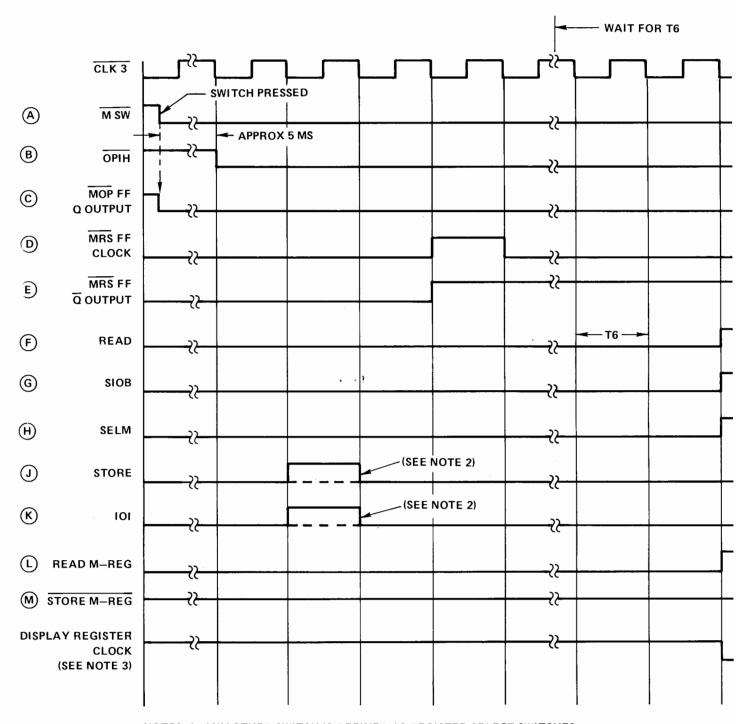

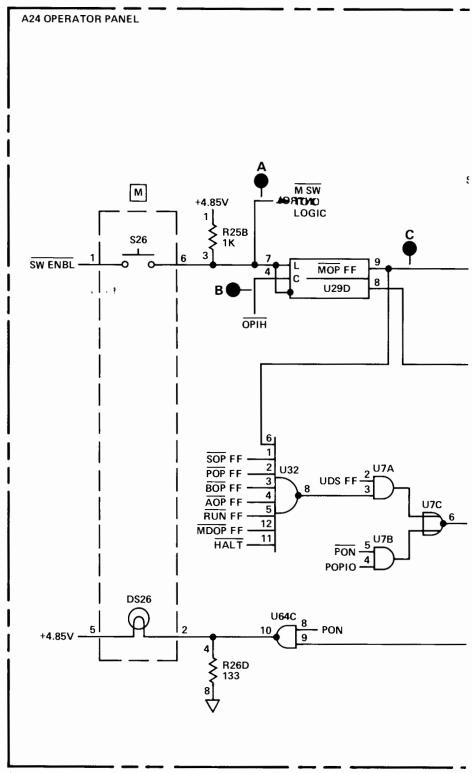

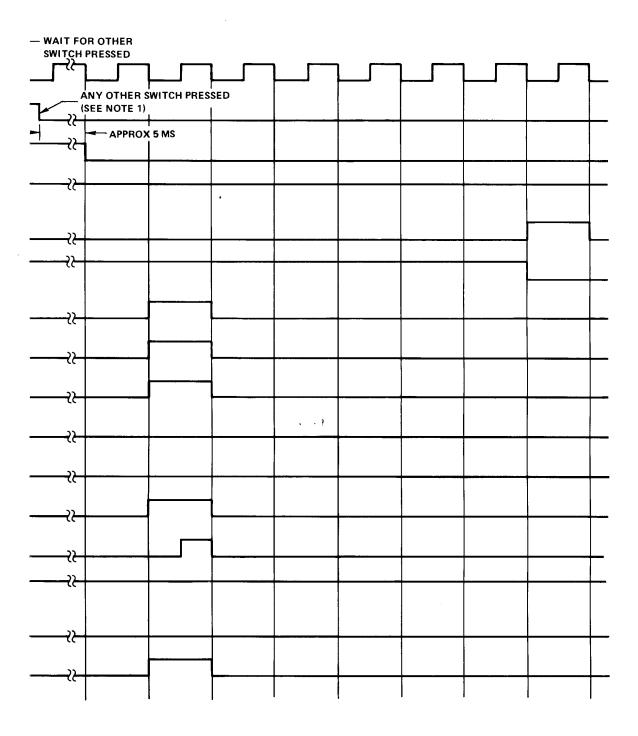

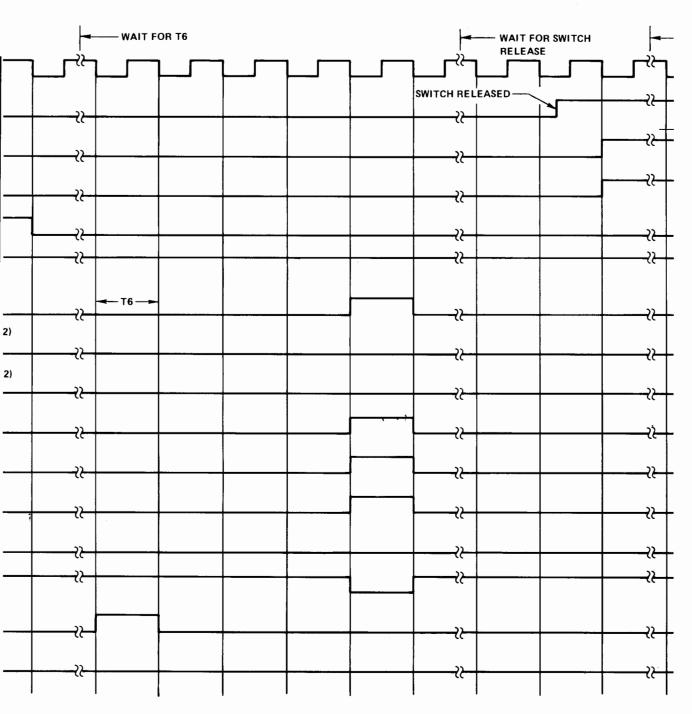

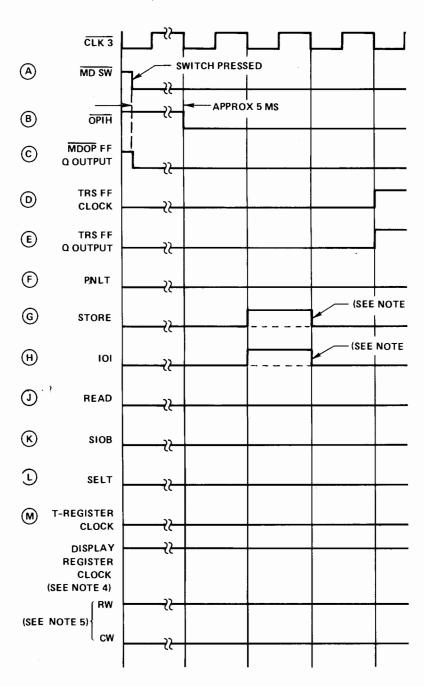

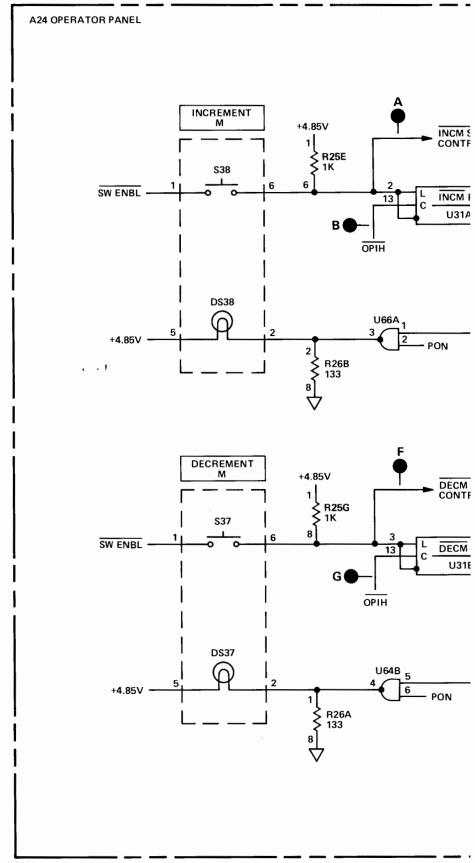

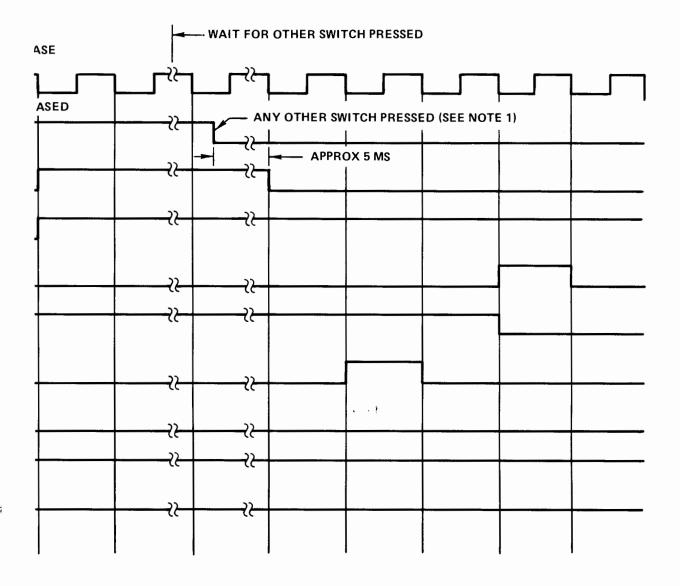

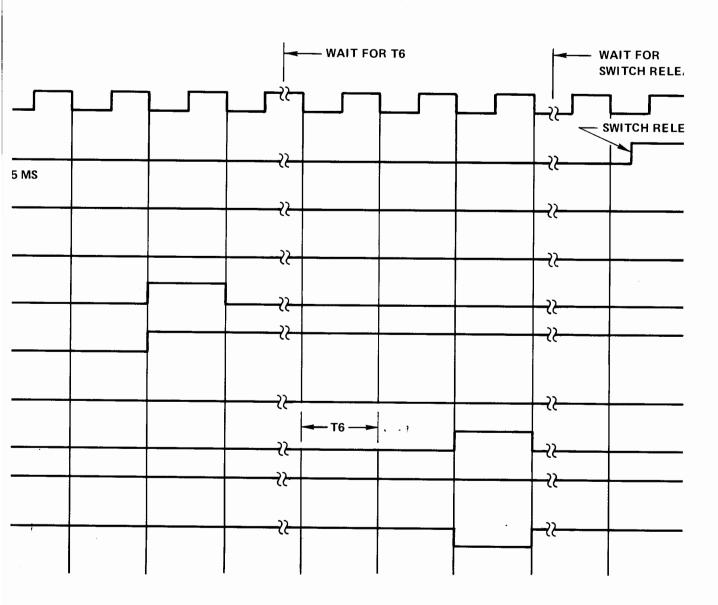

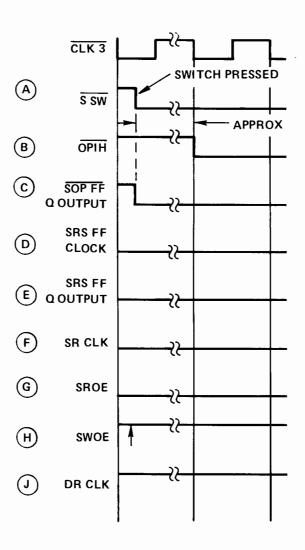

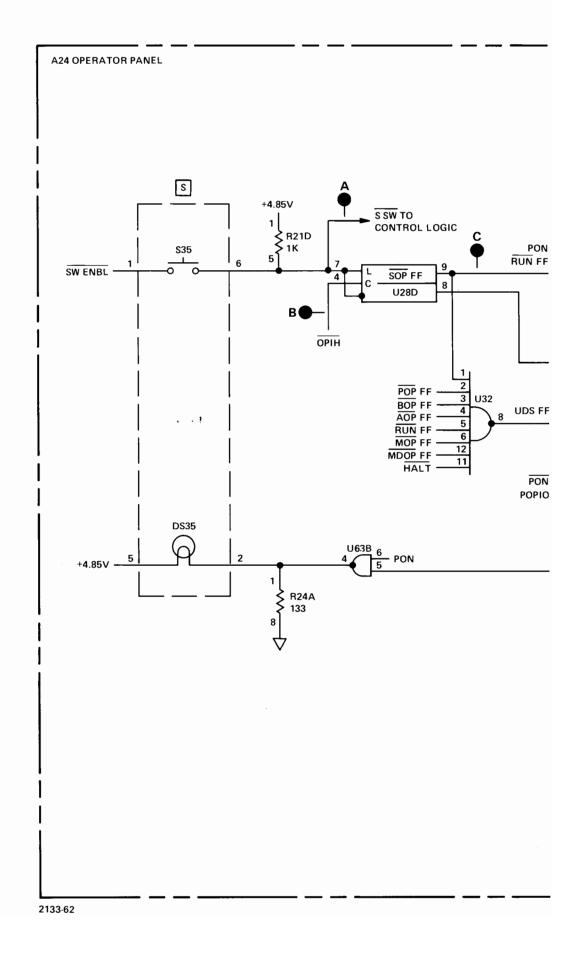

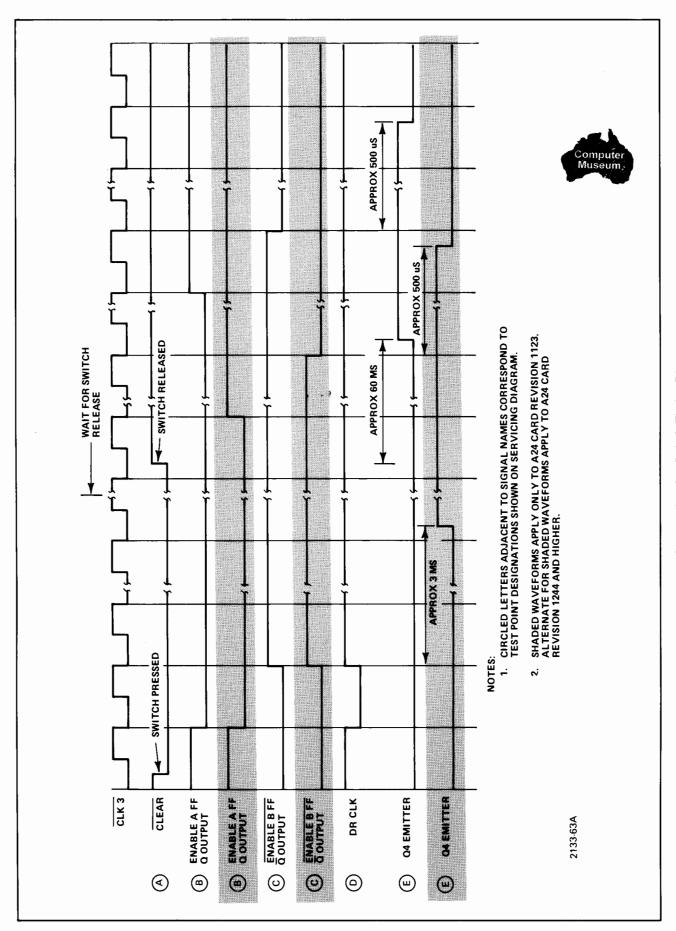

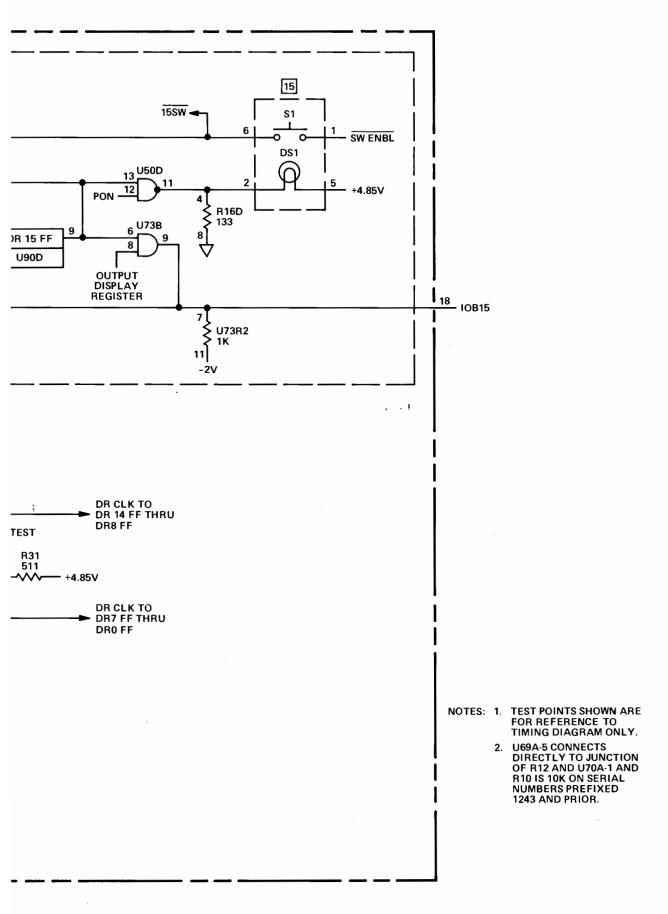

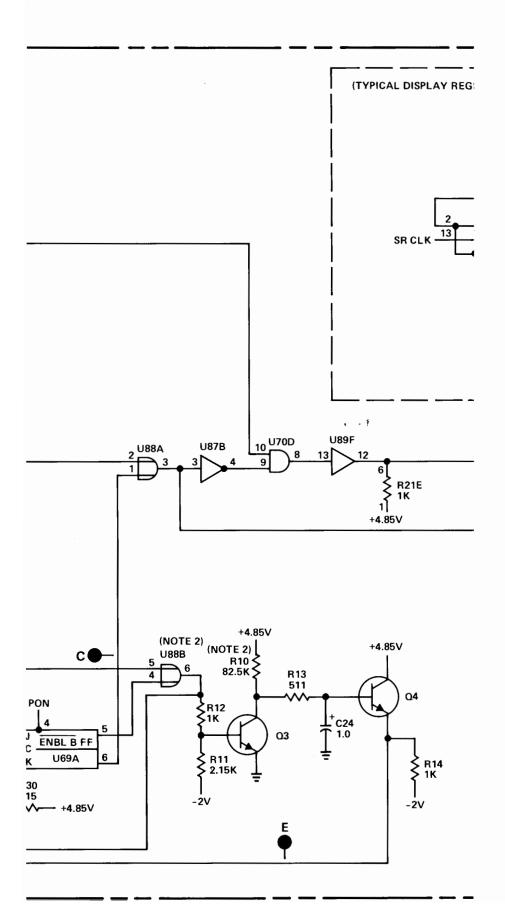

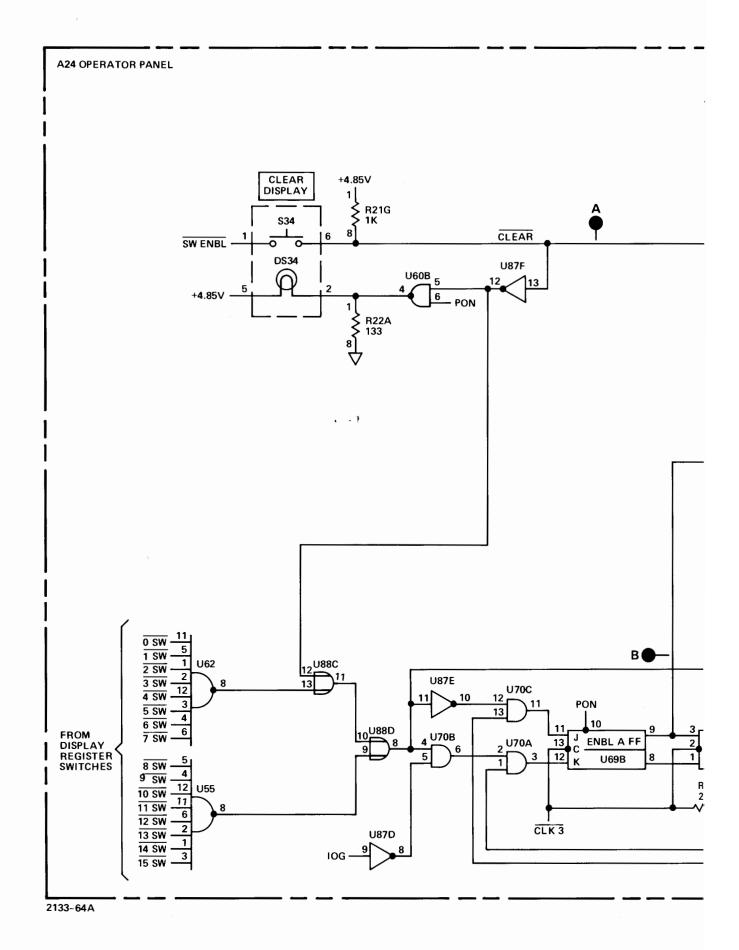

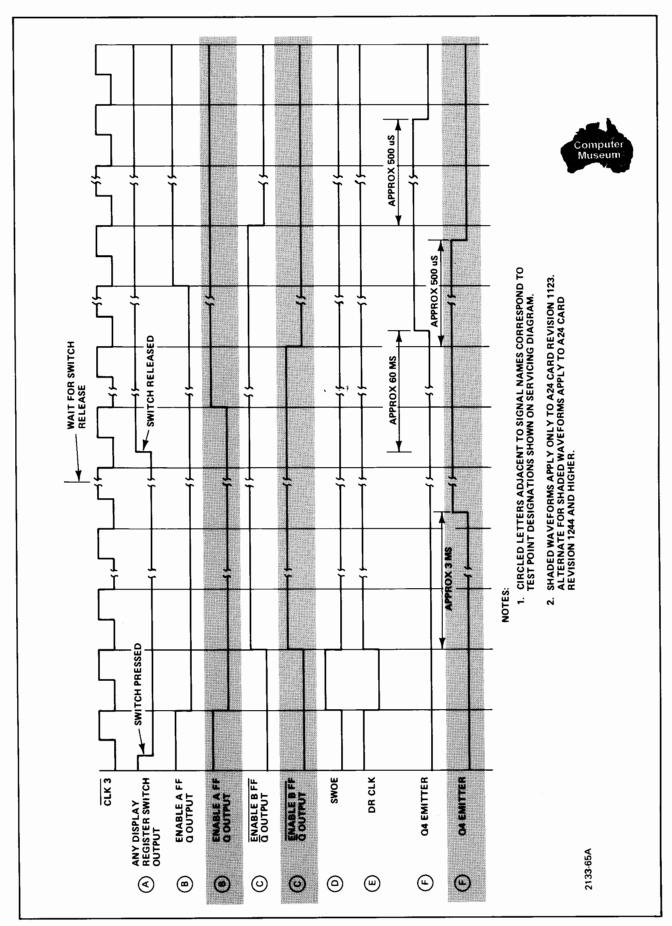

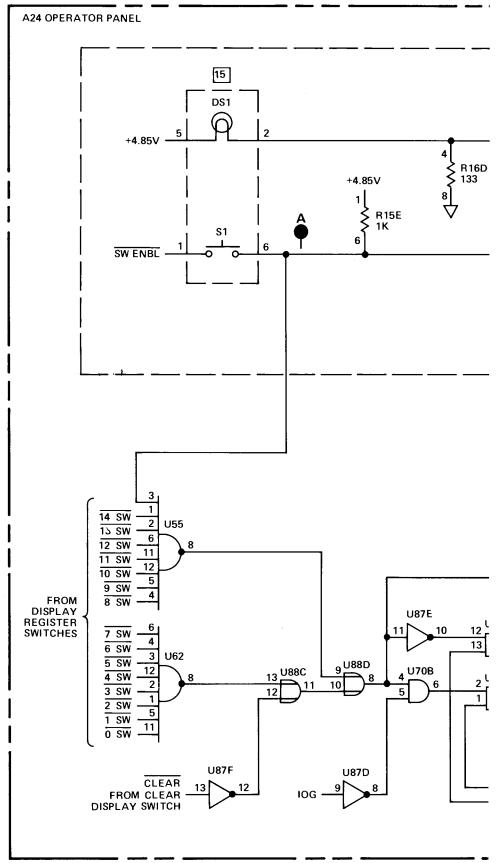

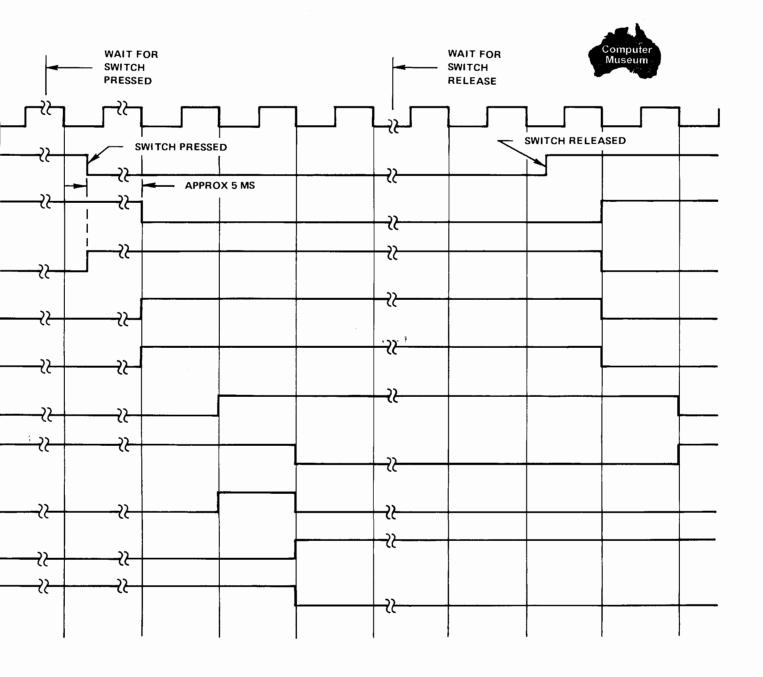

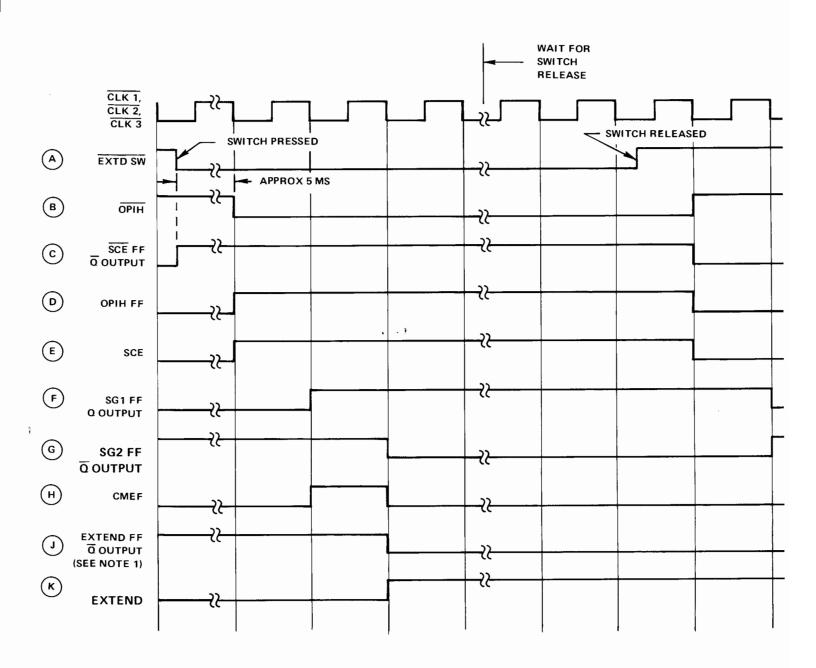

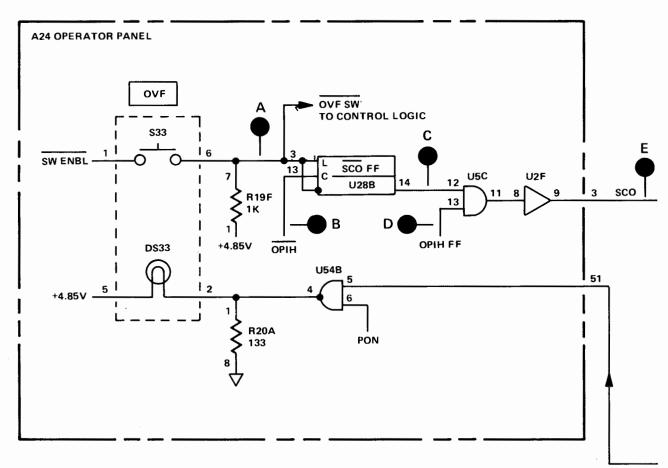

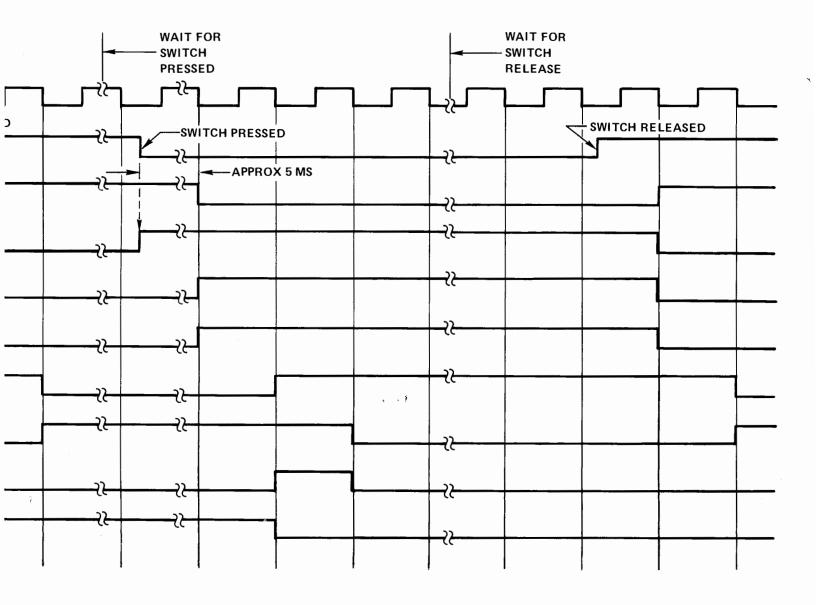

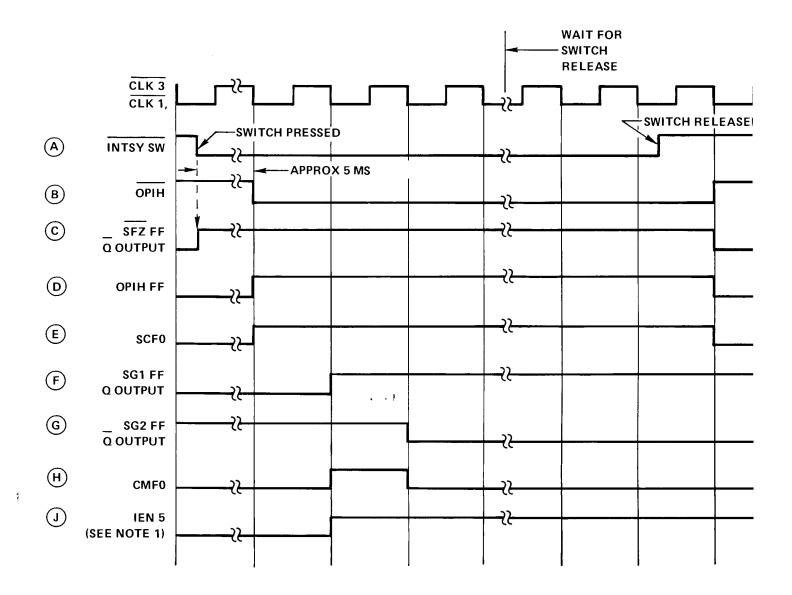

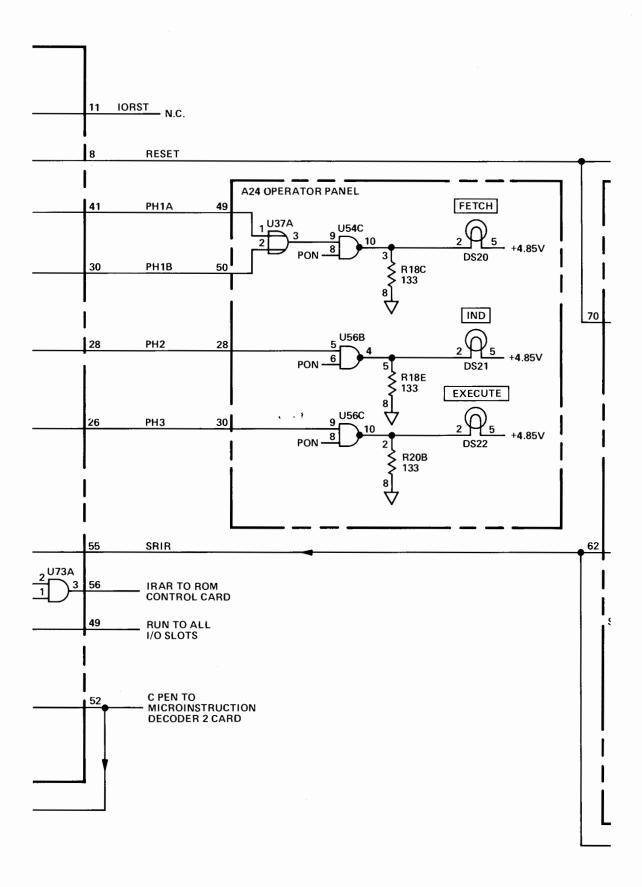

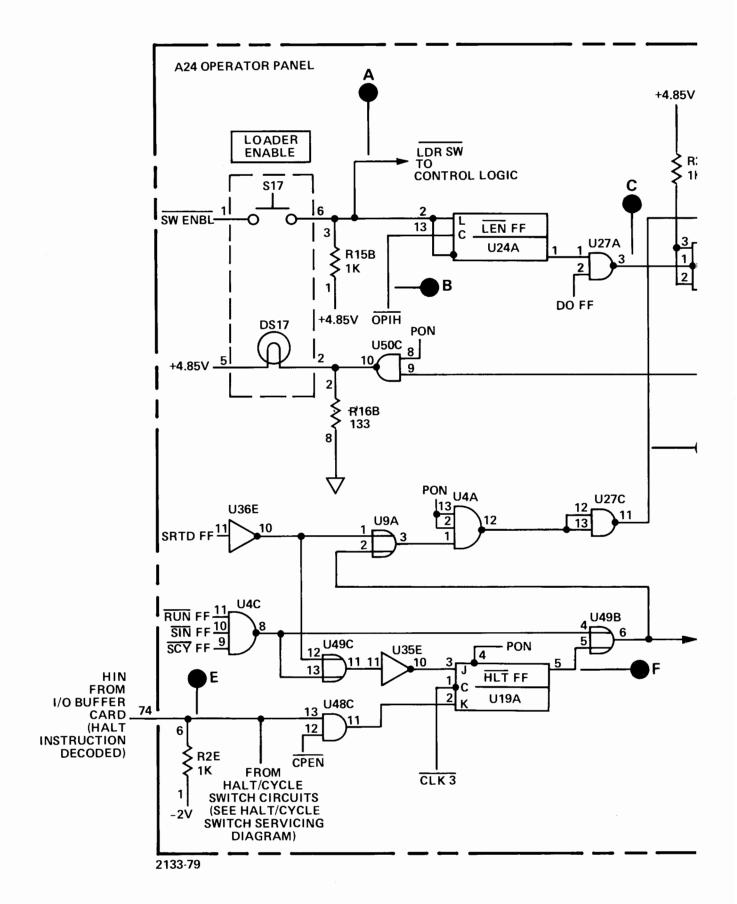

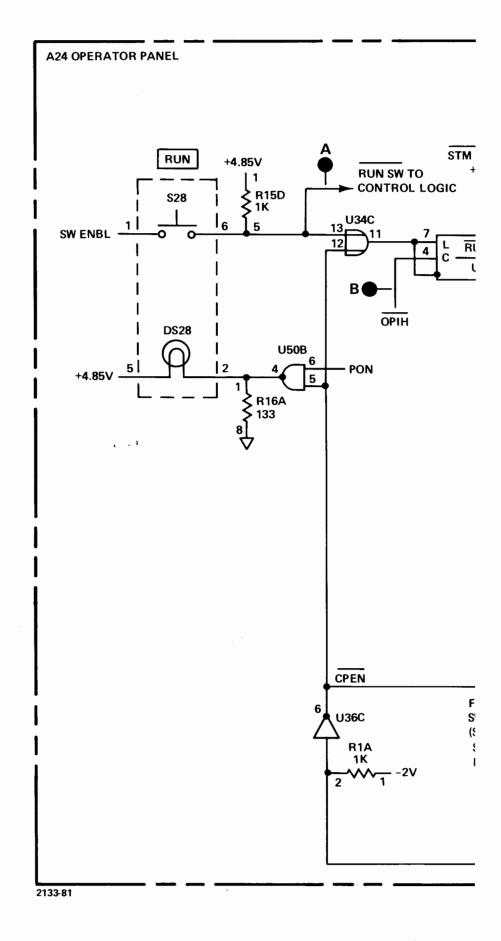

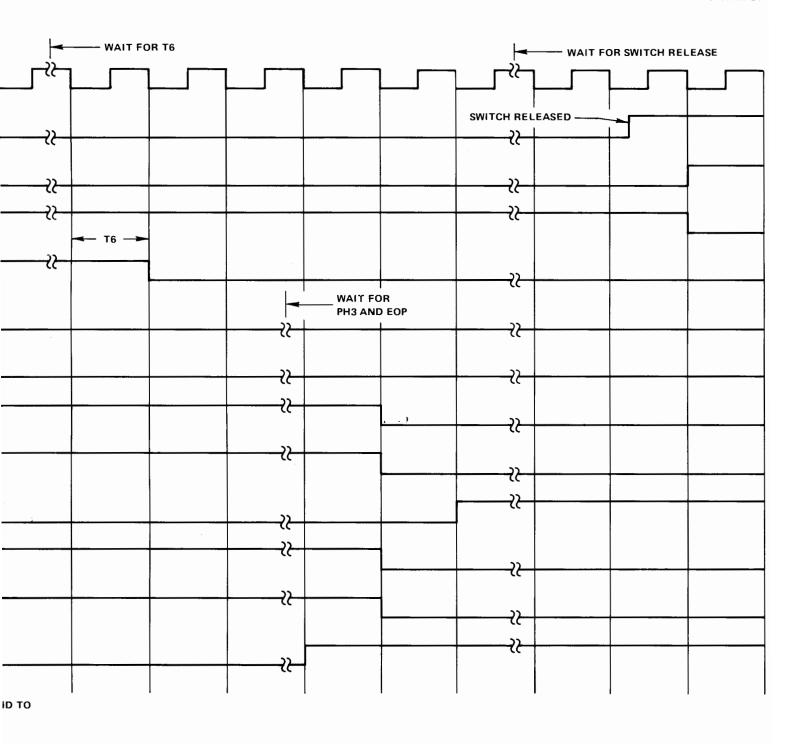

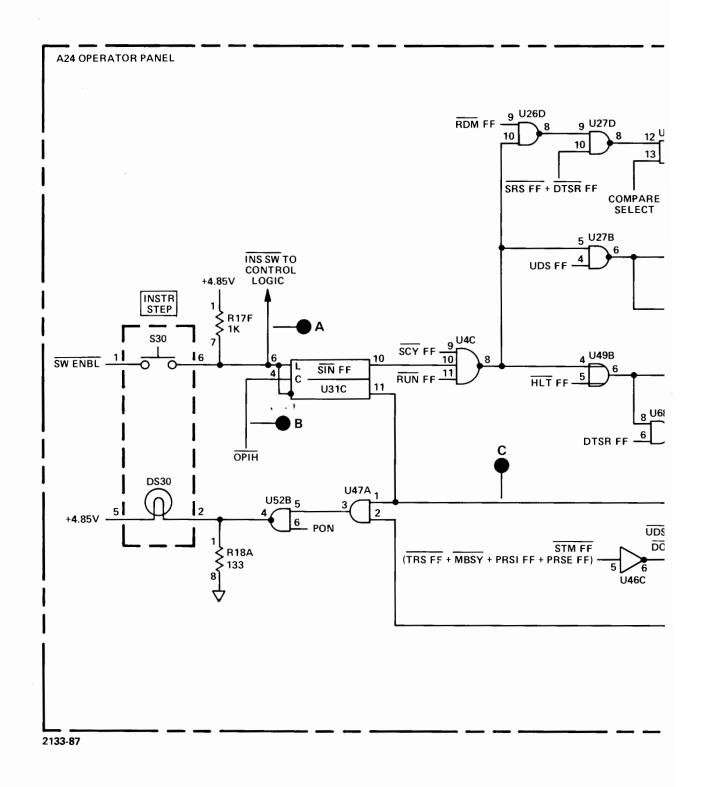

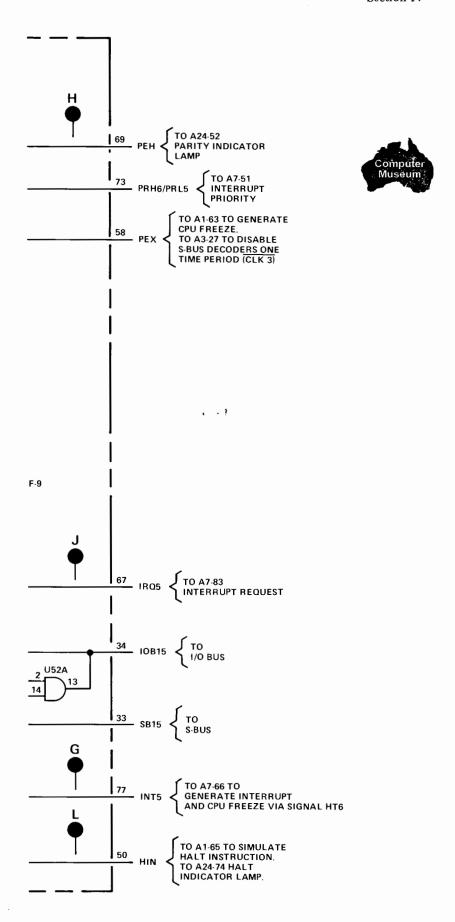

| 3-125.<br>3-125. | Operator Panel                       |        |

| 3-123.<br>3-128. | Panel Switches and Indicators        |        |

| 3-128.<br>3-130. | Computer Power Switch                |        |

| 3-130.<br>3-131. |                                      |        |

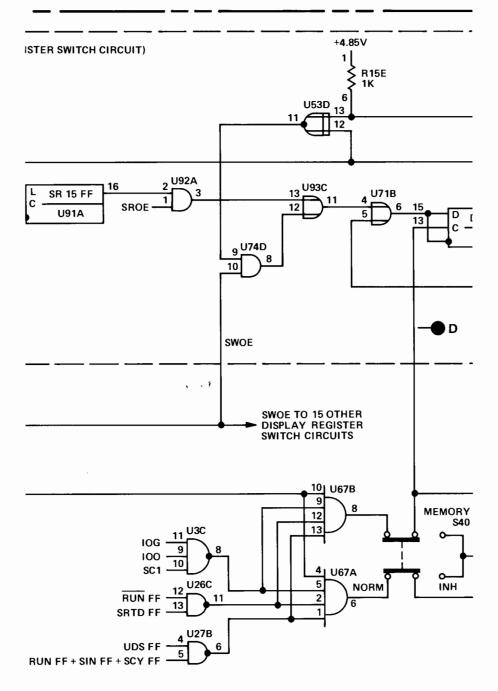

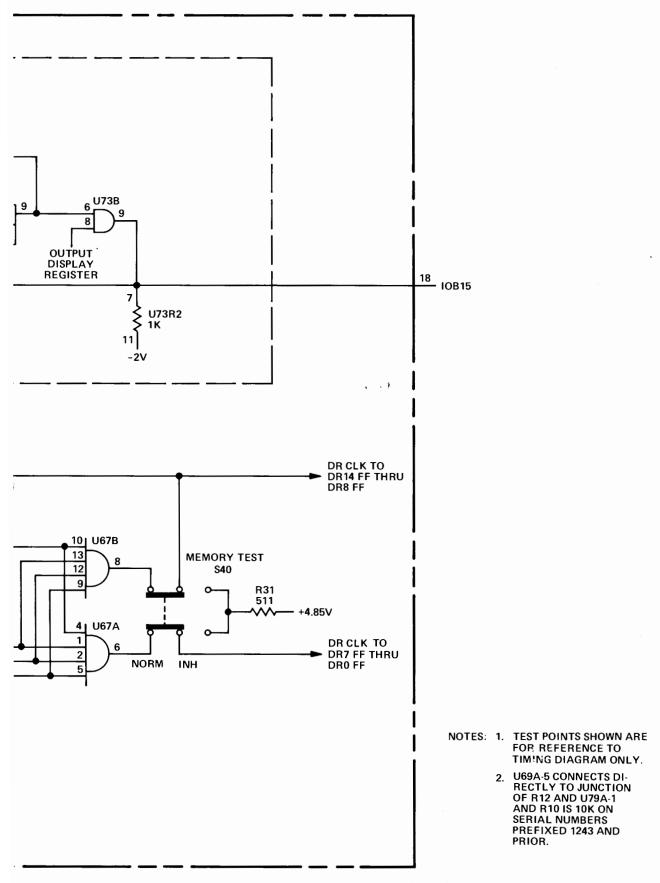

|                  | Display Register Switches            |        |

| 3-133.           | Operation Switches                   |        |

| 3-136.           | Special Maintenance Switches         |        |

| 3-139.           | Indicators                           |        |

| 3-140.           | Operator Panel Functional Operation  |        |

| 3-141.           | General                              |        |

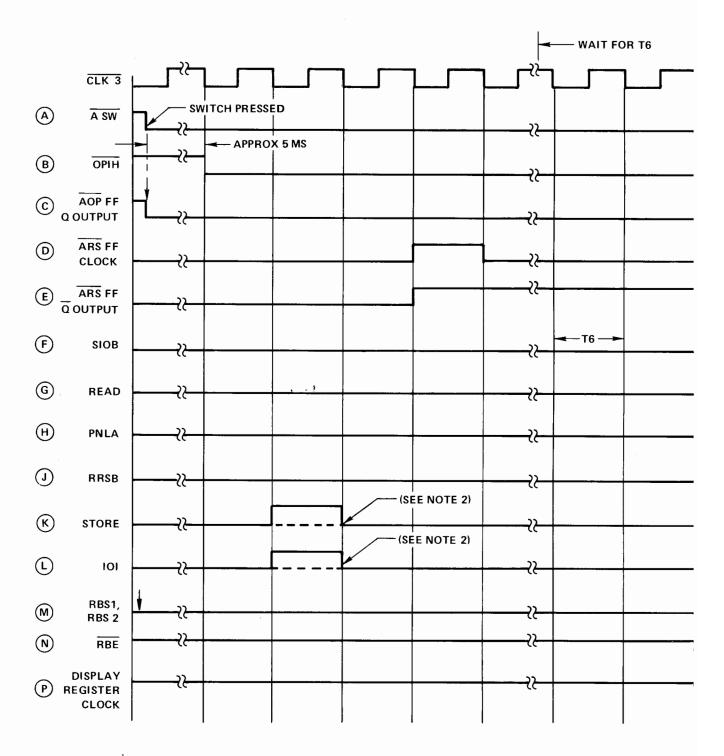

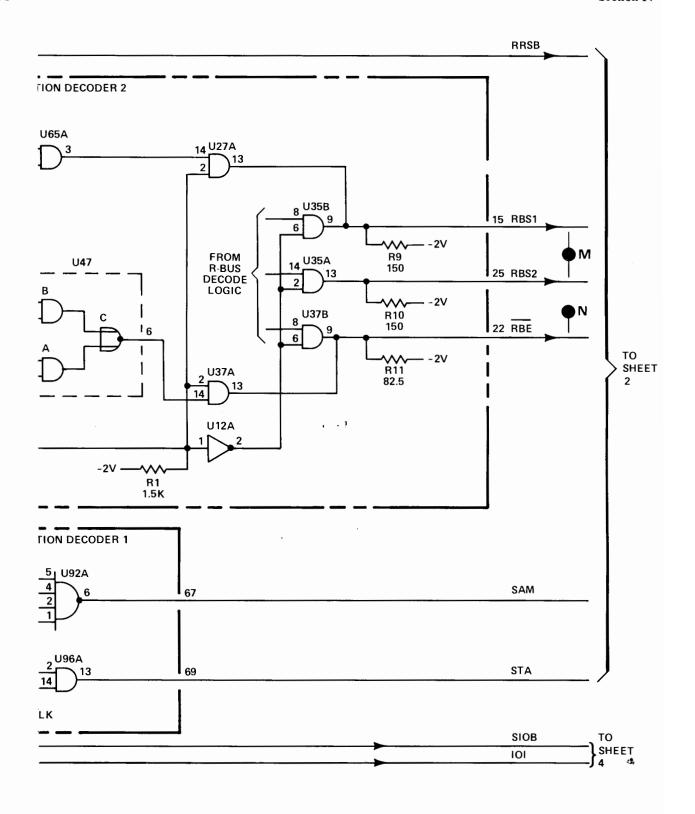

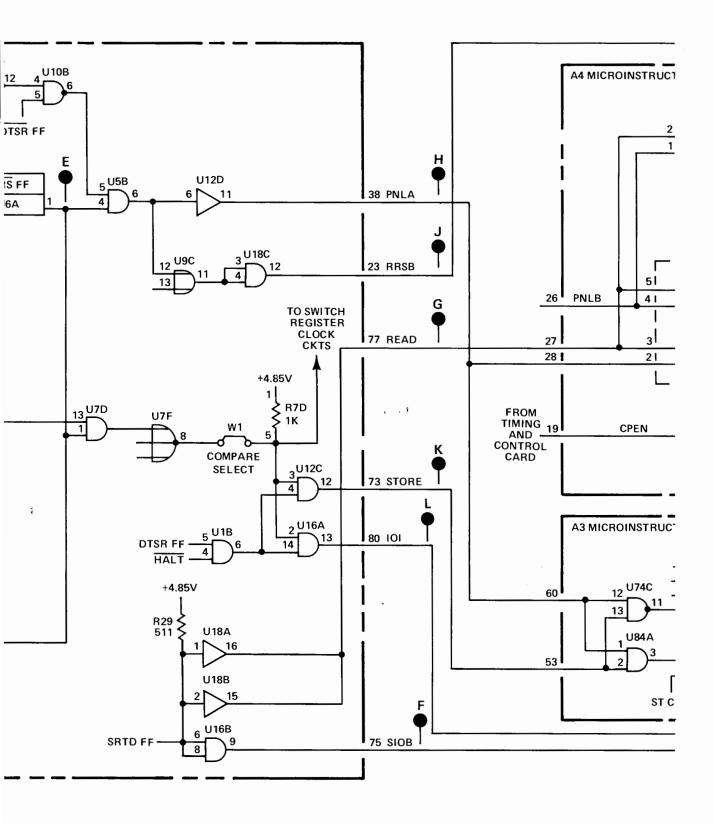

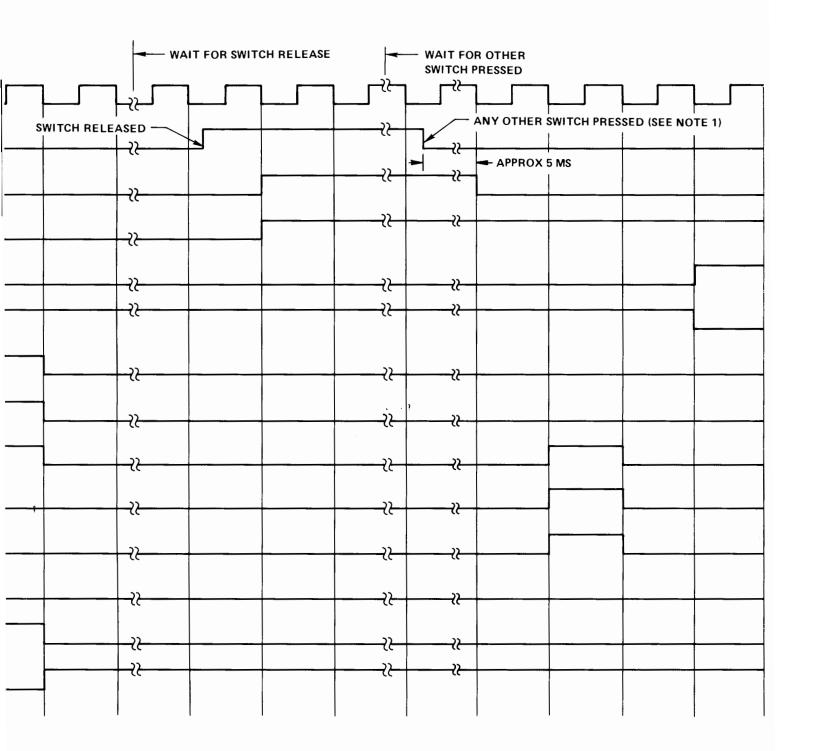

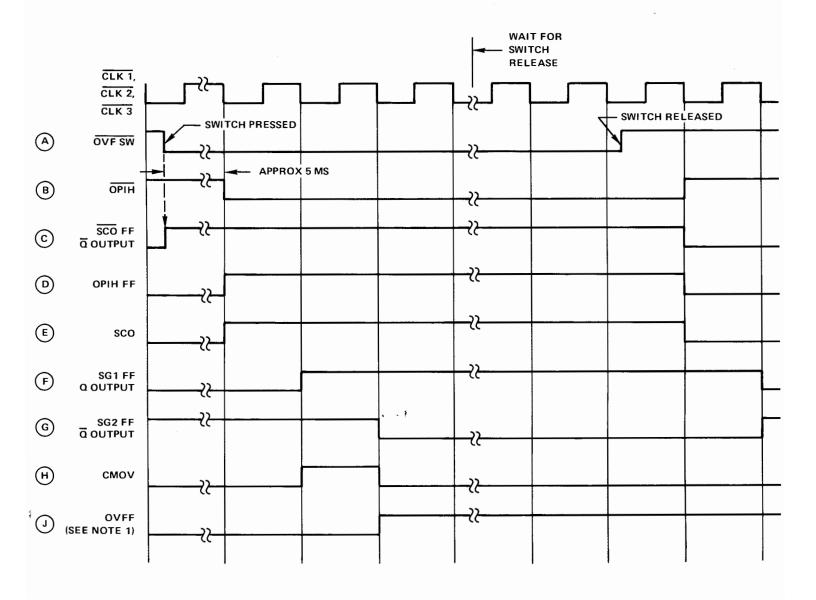

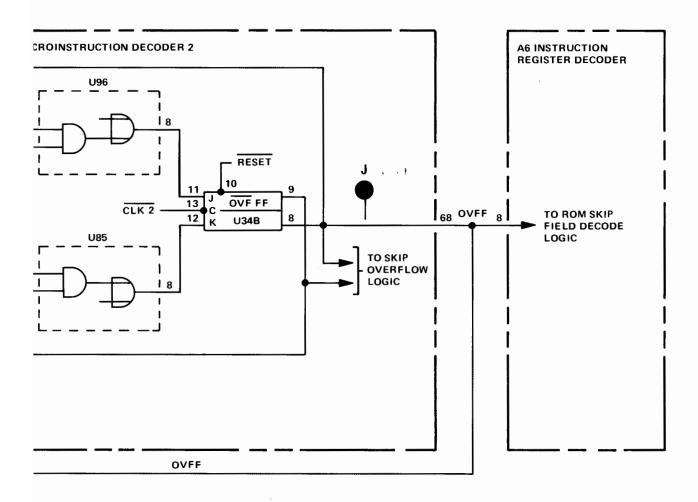

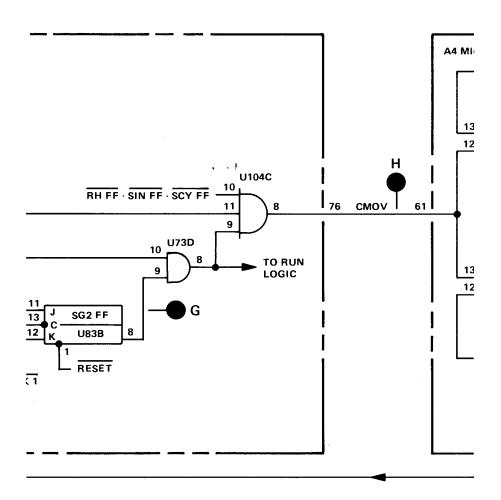

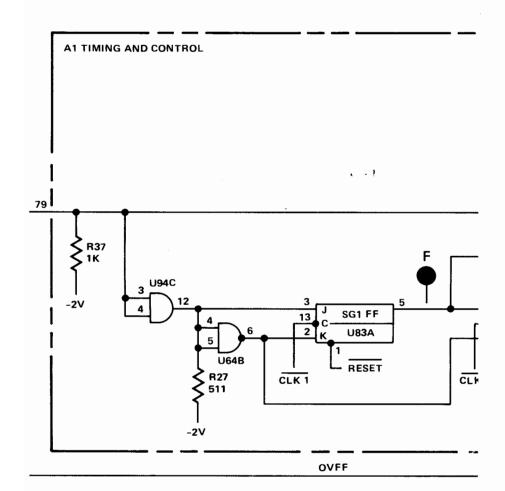

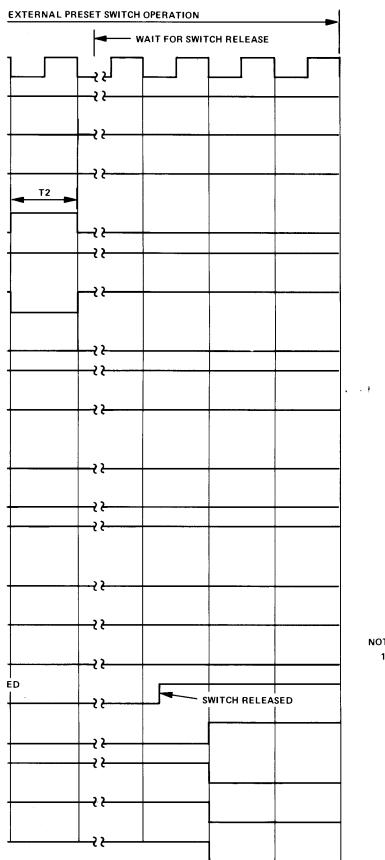

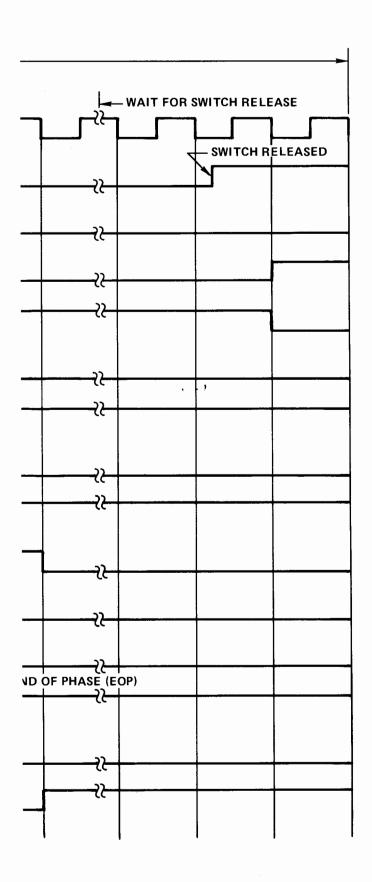

| 3-143.           | Operator Panel Cycle                 |        |

| 3-145.           | Special Computer Functions           |        |

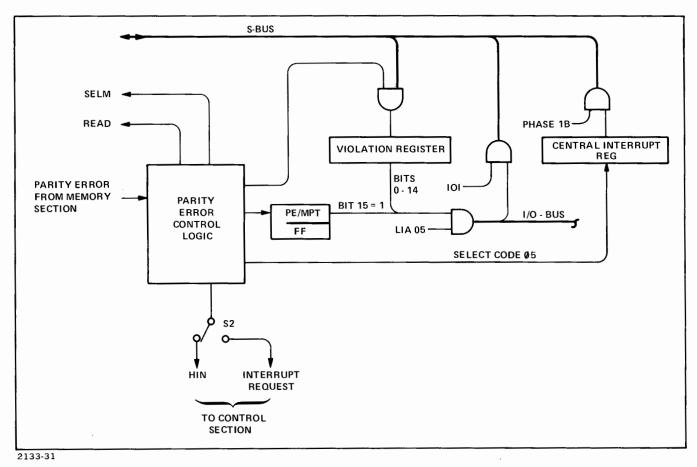

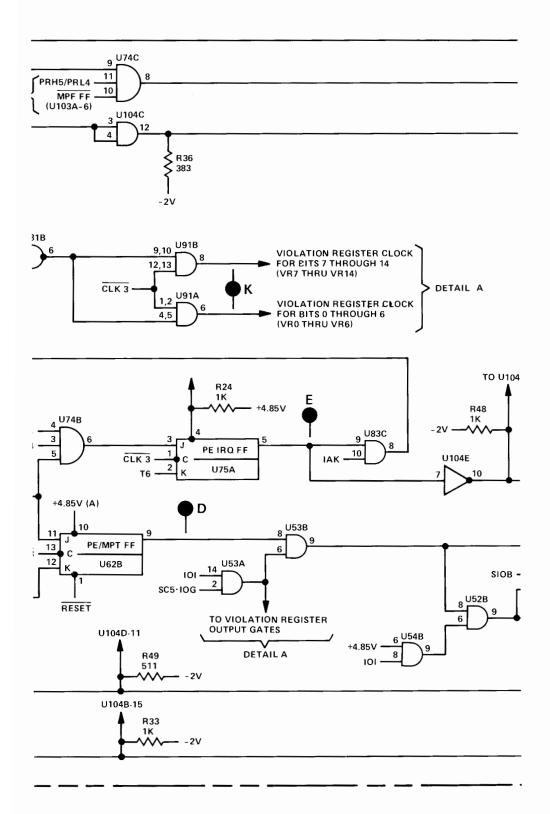

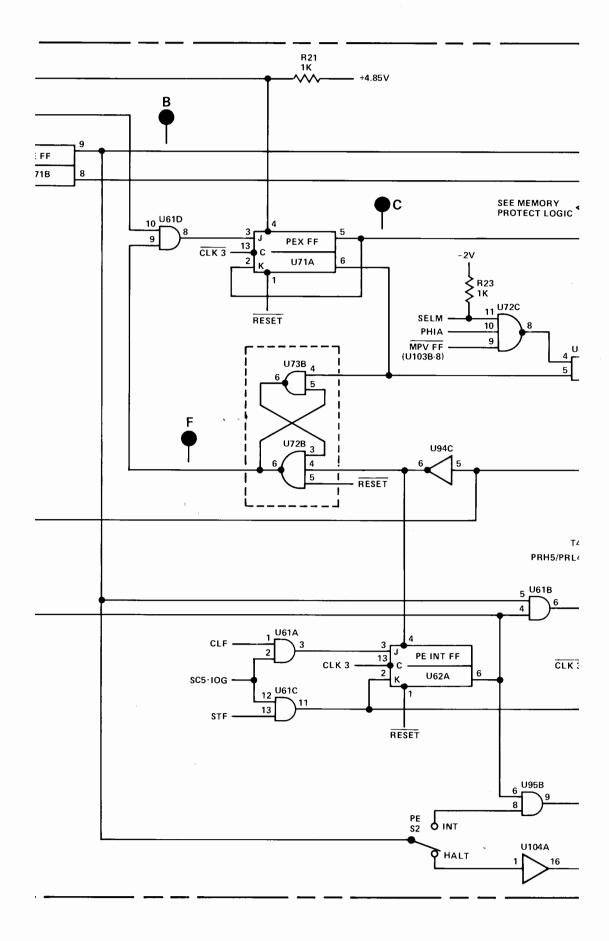

| 3-148.           | Parity Error                         |        |

| 3-149.           | General                              |        |

| 3-151.           | Parity Error Halt                    |        |

| 3-152.           | Parity Error Interrupt               |        |

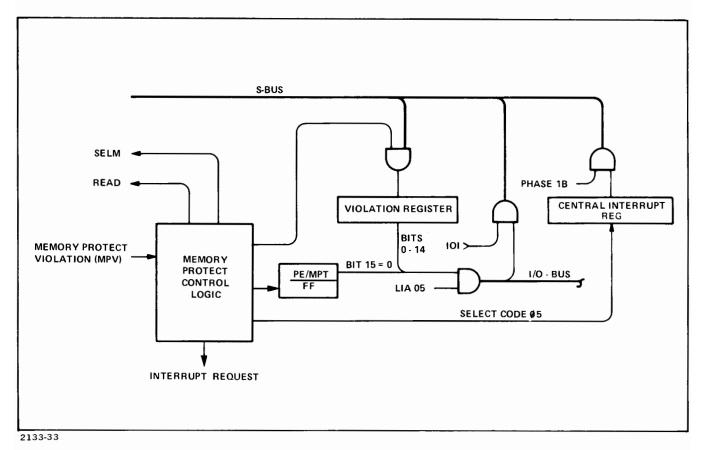

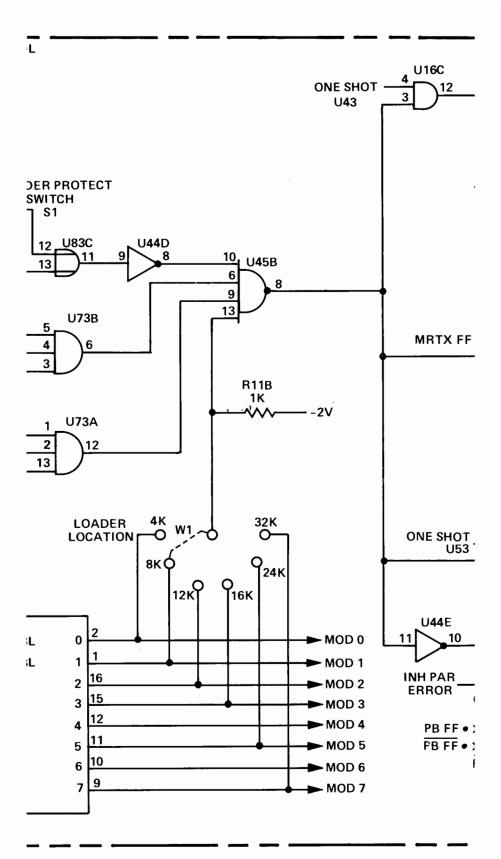

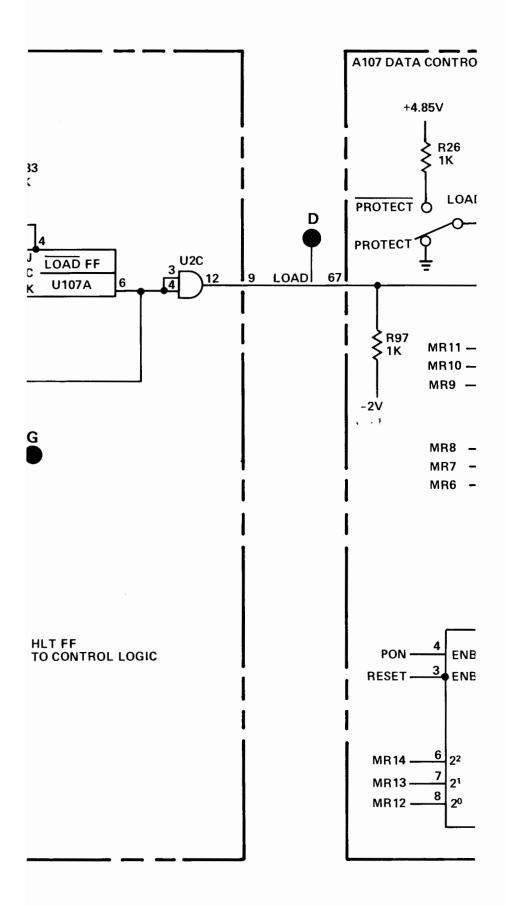

| 3-154.           | Memory Protect                       | . 3-21 |

| 3-155.           | General                              |        |

| 3-157.           | Detecting a Memory Protect Violation | . 3-21 |

| 3-159.           | Memory Protect Interrupt             | . 3-21 |

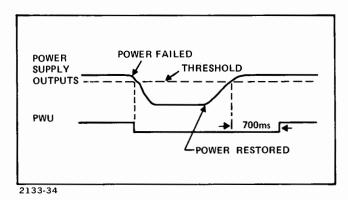

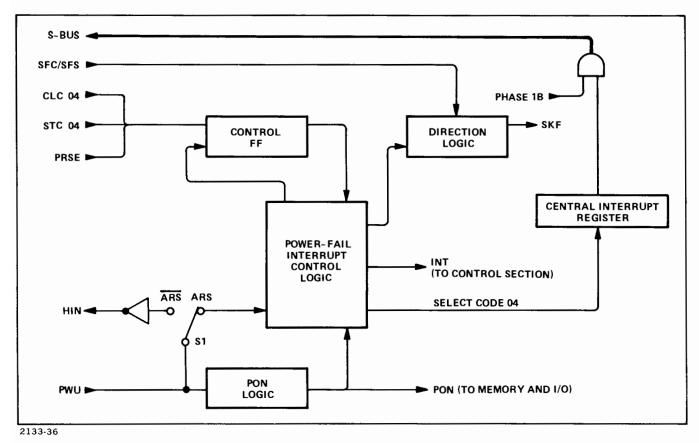

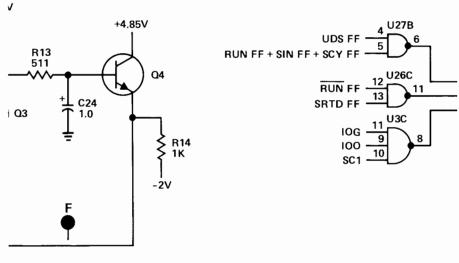

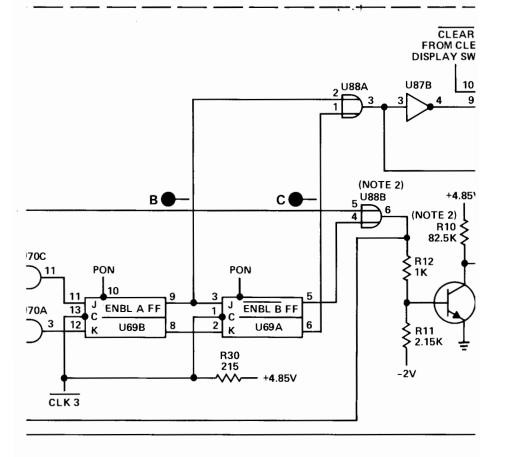

| 3-161.           | Power-Fail                           | . 3-22 |

| 3-162.           | General                              | . 3-22 |

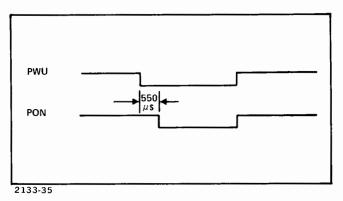

| 3-167.           | PWU Signal                           | . 3-22 |

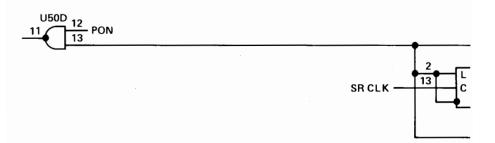

| 3-168.           | PON Signal                           | . 3-22 |

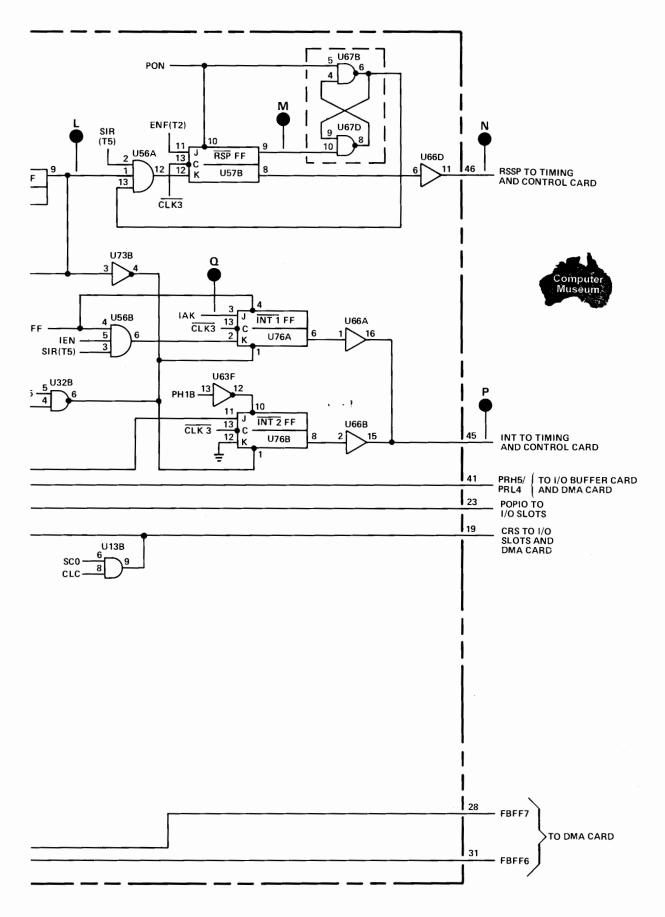

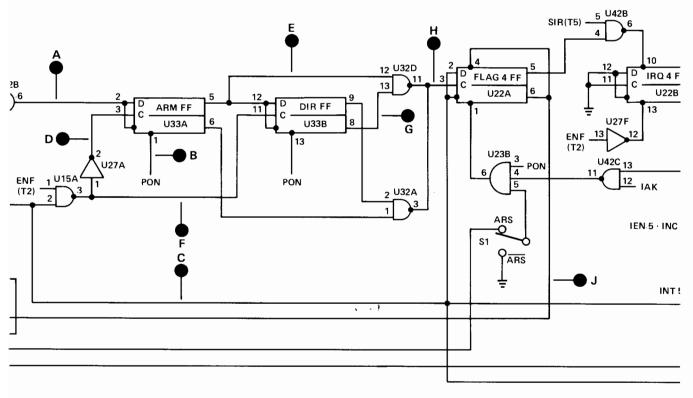

| 3-169.           | Interrupt Operation                  | . 3-23 |

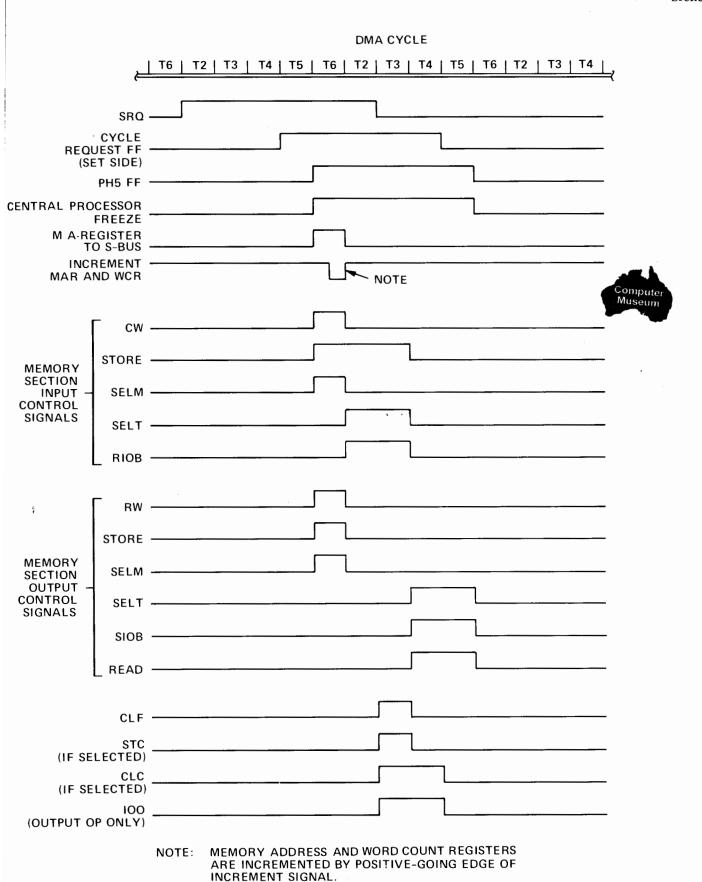

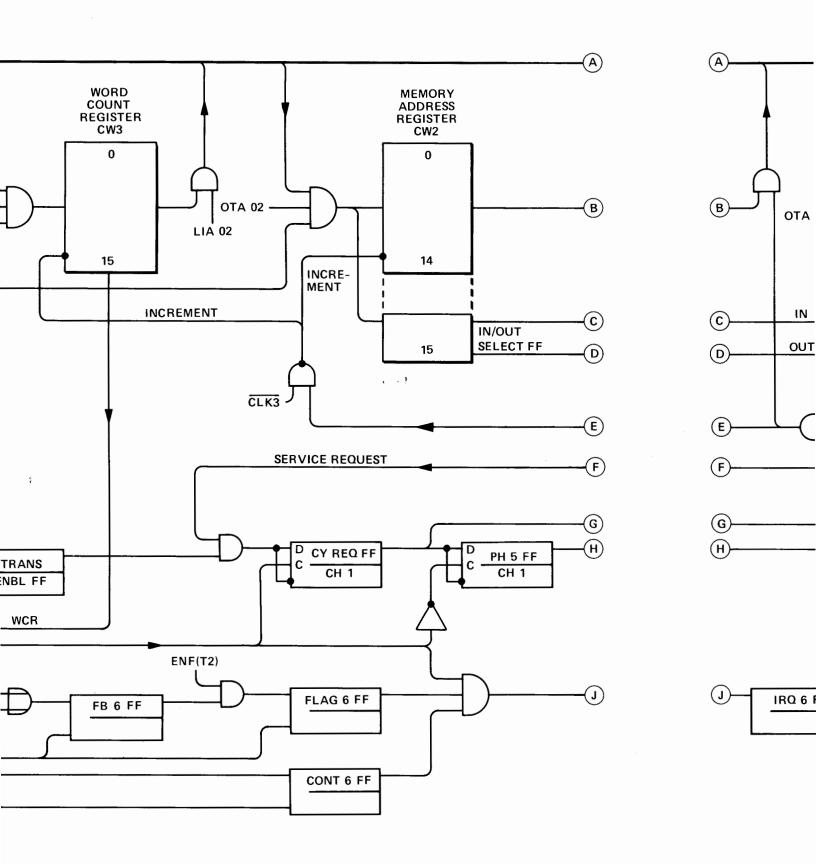

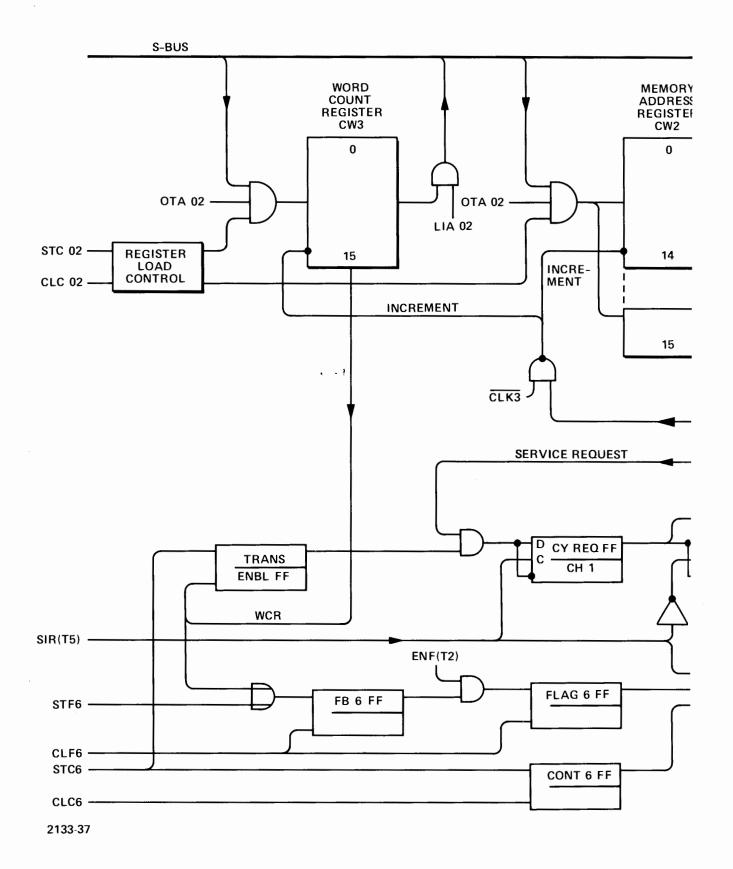

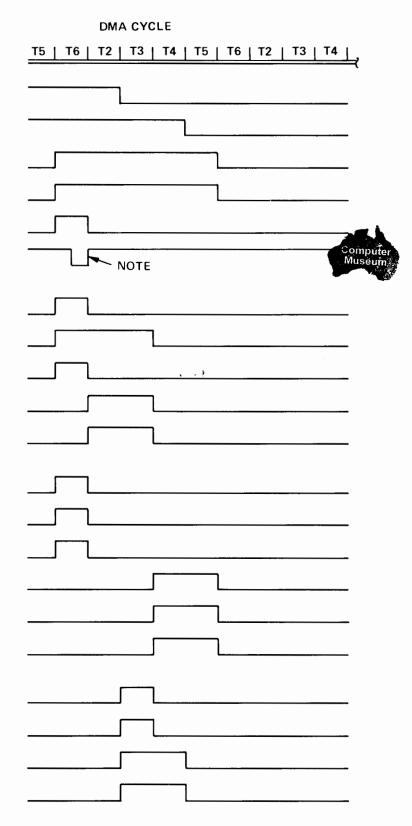

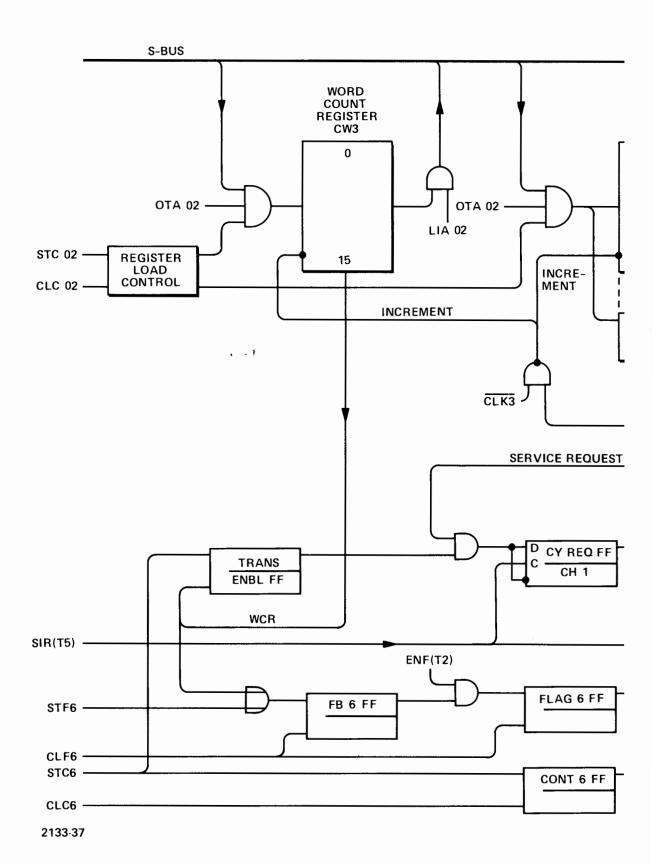

| 3-172.           | Direct Memory Access                 |        |

| 3-173.           | General                              |        |

| 3-175.           | DMA Initialization                   |        |

| 3-180.           | DMA Cycle                            |        |

| 3-183.           | Input Operation                      |        |

| 3-185.           | Output Operation                     |        |

| 3-186.           | End Data Transfer                    |        |

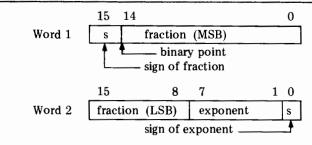

| 3-188.           | Floating Poing                       |        |

| 3-189.           | General                              |        |

| 3-190.           | Floating-Point Operation             |        |

| 3-190.<br>3-192. | Floating-Point Instructions          |        |

| 3-192.<br>3-194. | Detailed Theory Introduction         |        |

| 3-194.<br>3-196. |                                      |        |

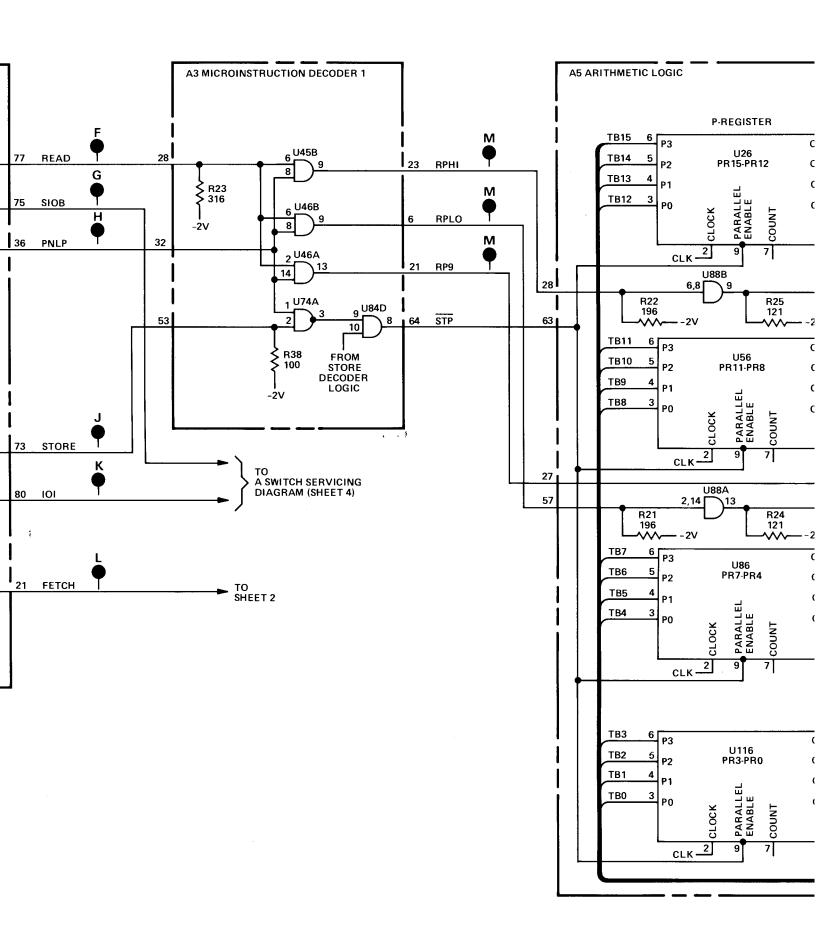

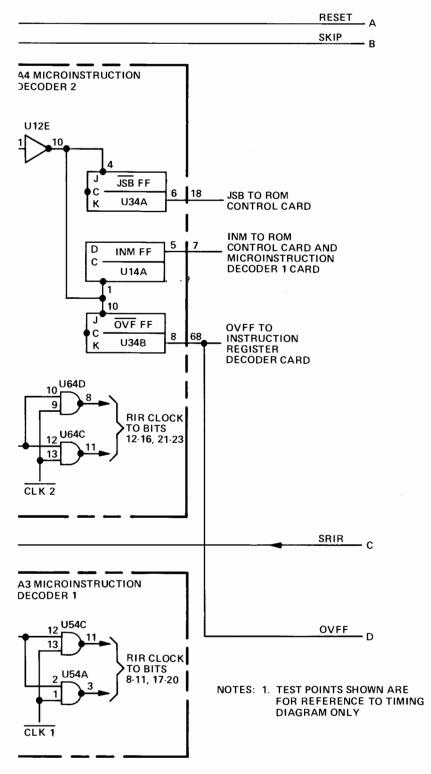

| 3-196.<br>3-197. | Control Section Detailed Theory      |        |

|                  |                                      |        |

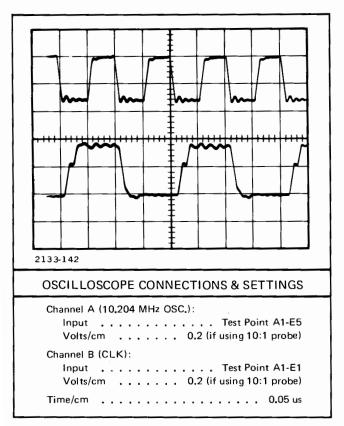

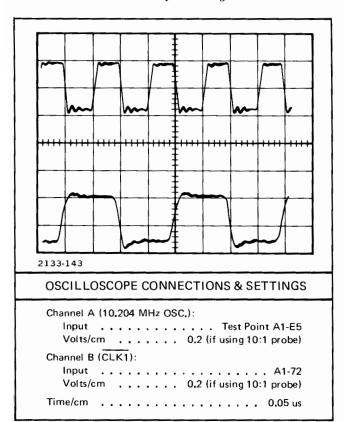

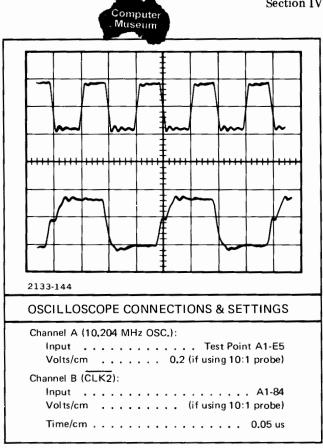

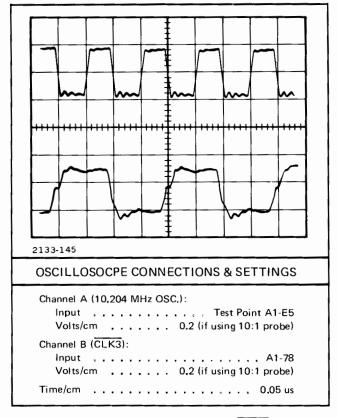

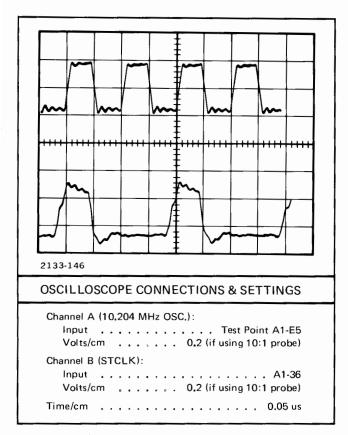

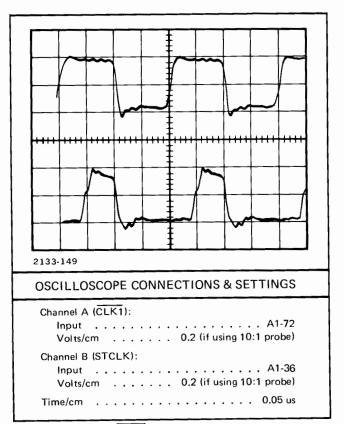

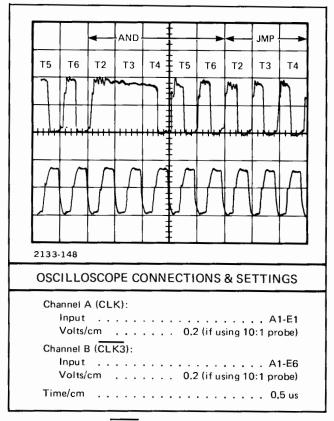

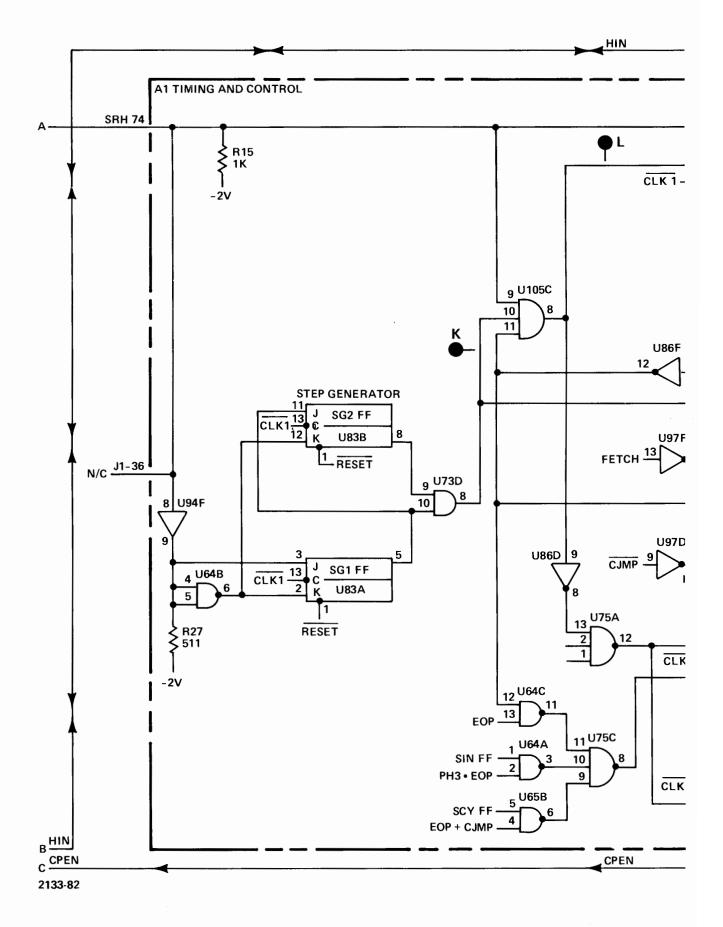

| 3-199.           | Oscillator                           |        |

| 3-200.           | Frequency Divider                    |        |

| 3-201.           | Clock Gating Circuits                |        |

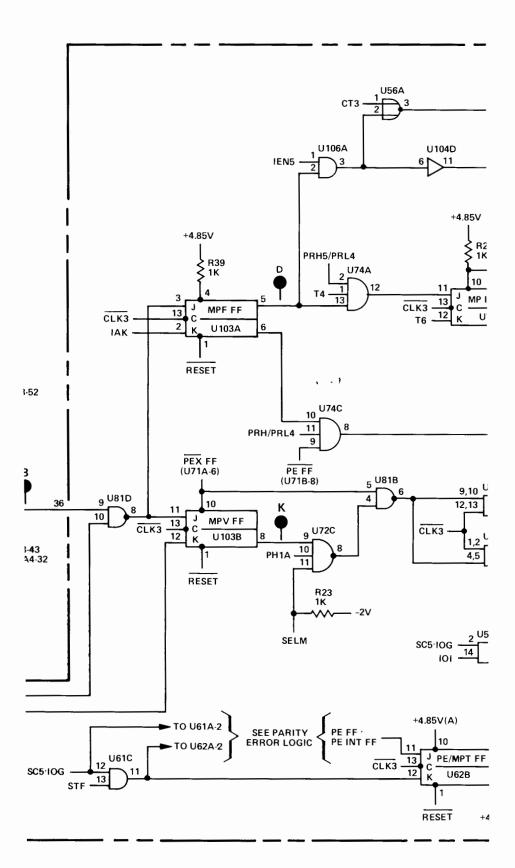

| 3-204.           | Parity Error Freeze                  |        |

| 3-205.           | I/O Freeze                           |        |

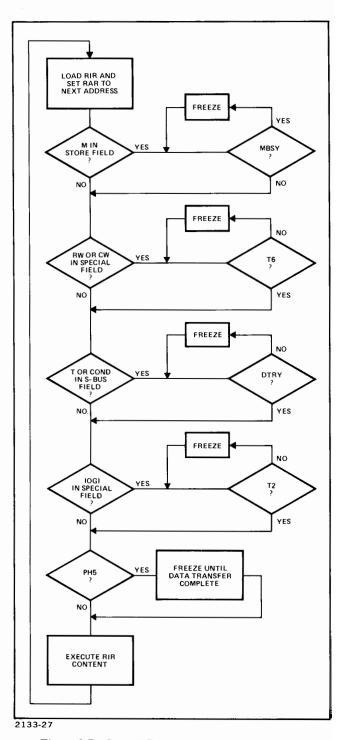

| 3-206            | Freeze Logic                         | 3-30   |

| Section | Page                                     |

|---------|------------------------------------------|

| 3-211.  | Memory Protect or Parity Error Interrupt |

| 3-212.  | DMA Cycle                                |

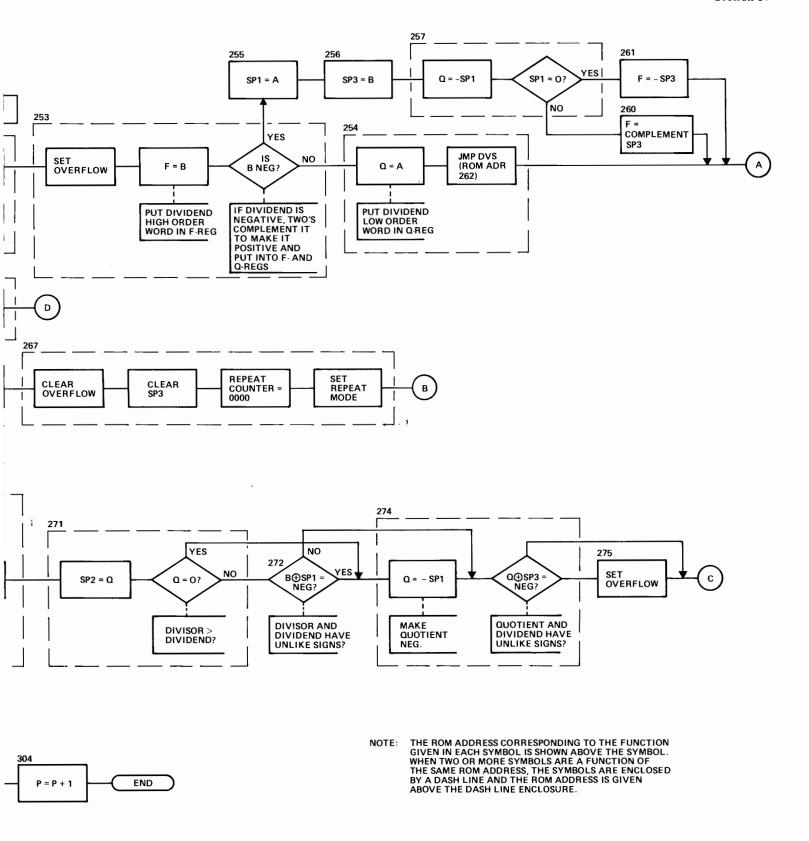

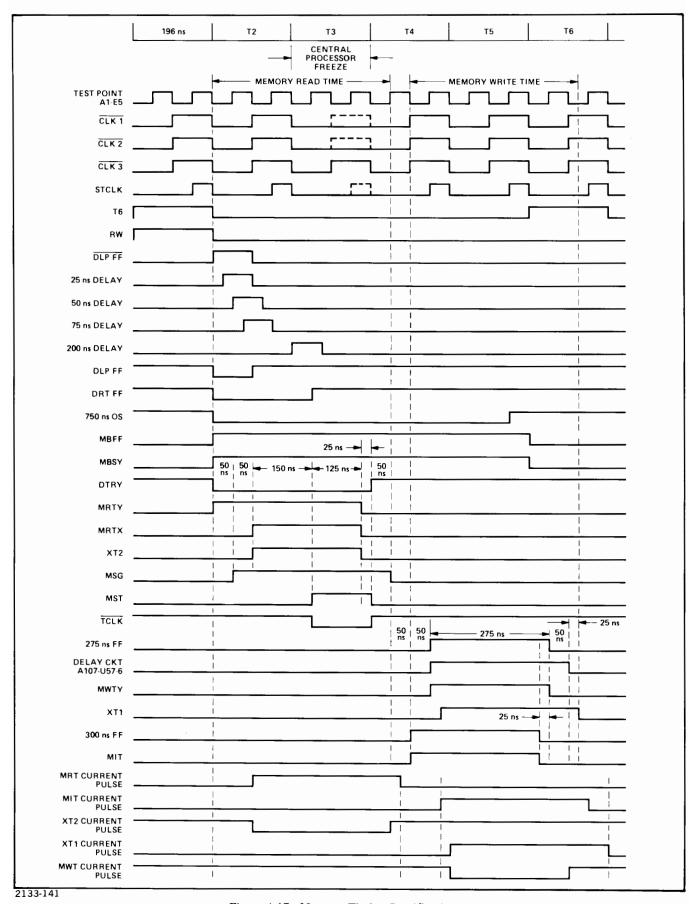

| 3-213.  | Divide Operation                         |

| 3-215.  | Memory Read/Write and Clear/Write        |

| 3-217.  | Read T-Register                          |

| 3-219.  | Store M-Register                         |

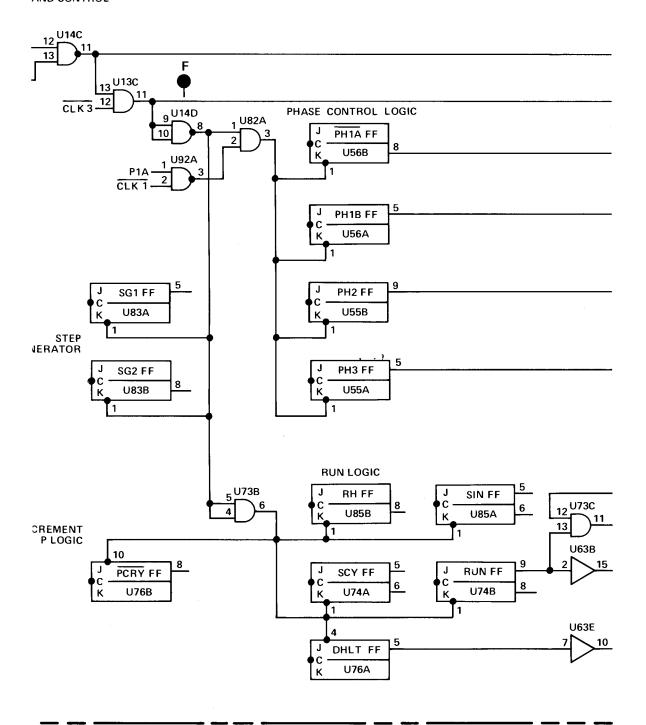

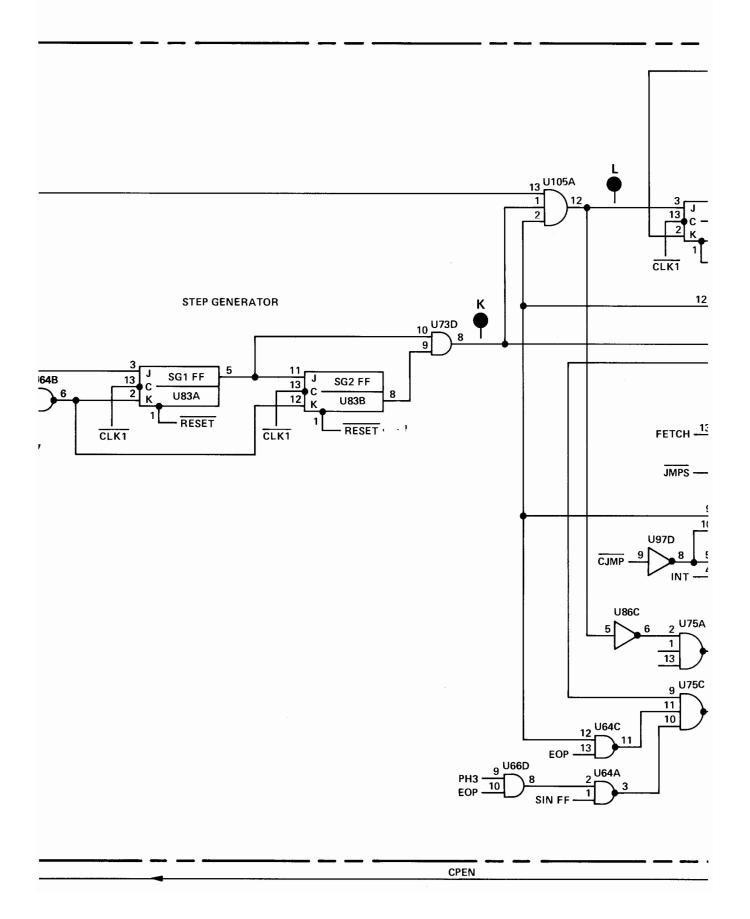

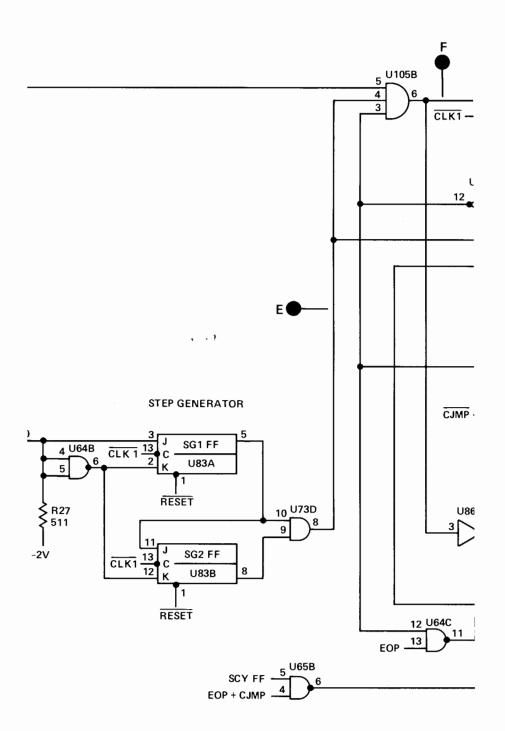

| 3-220.  | Step Generator Logic                     |

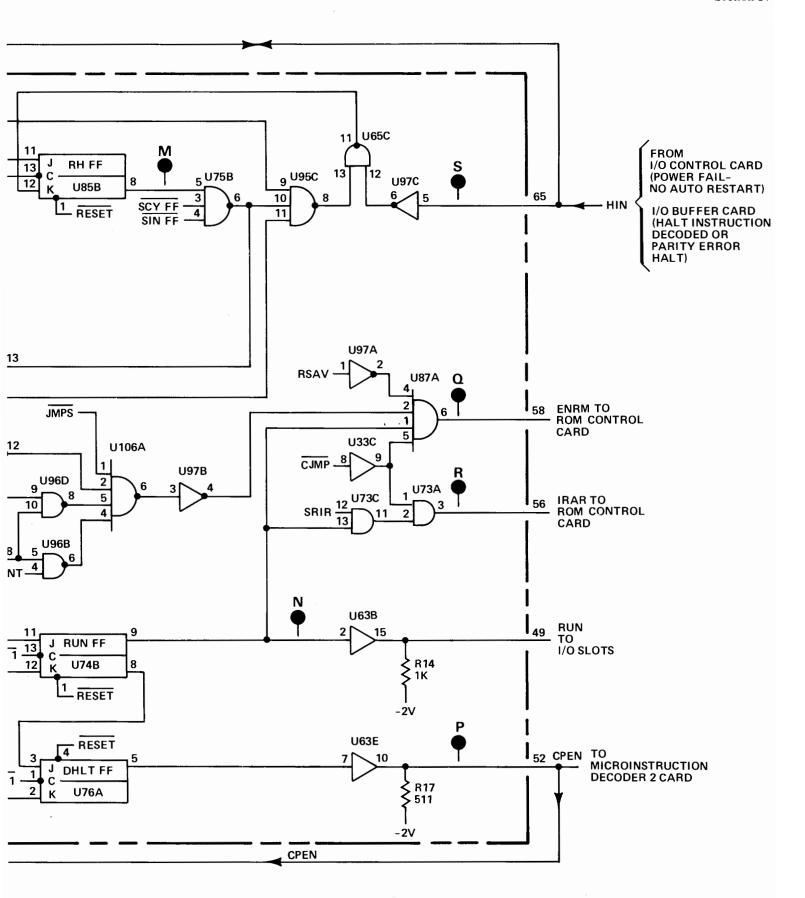

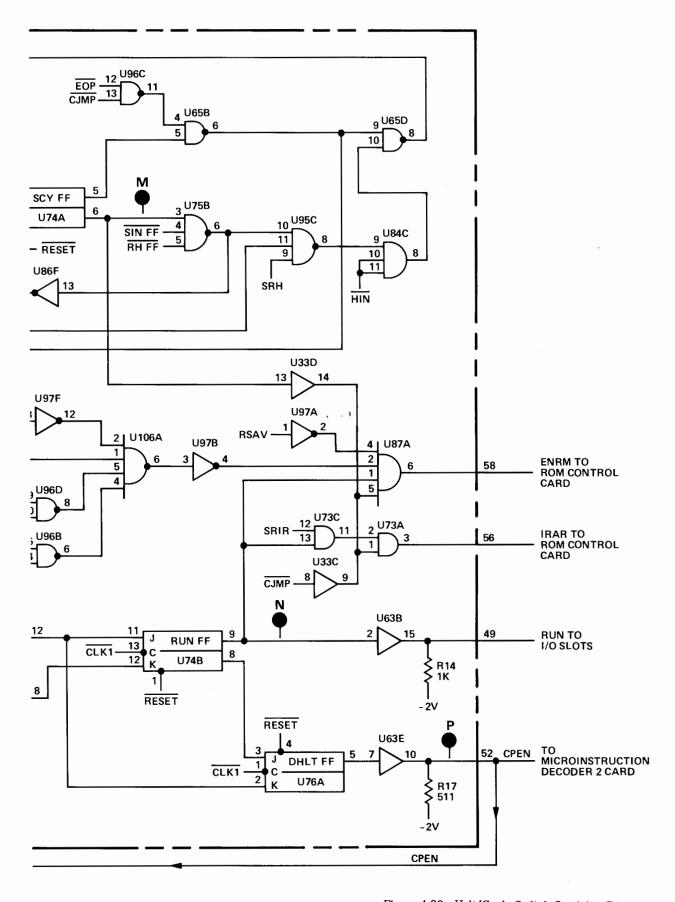

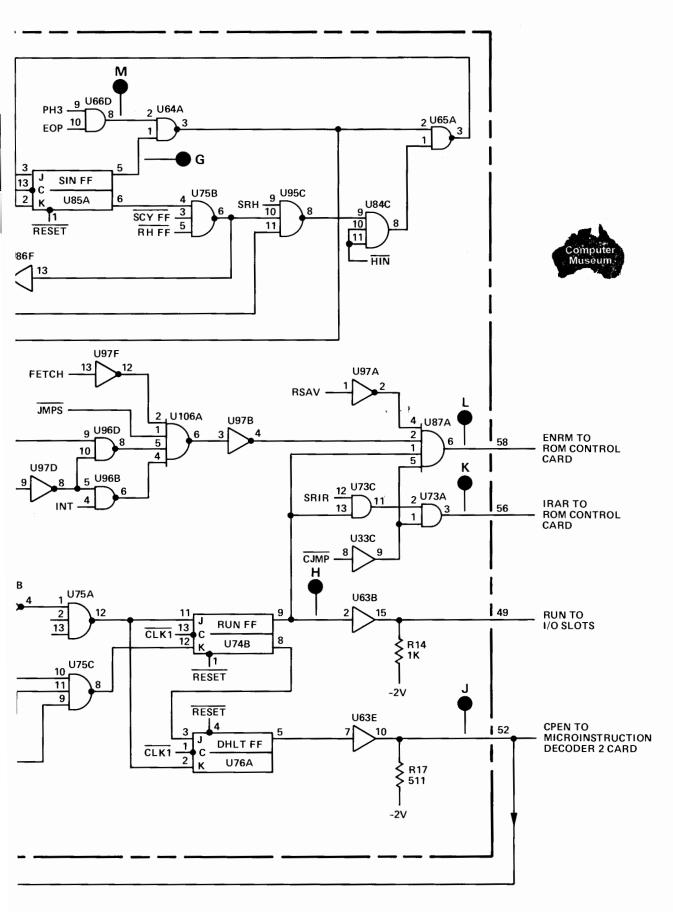

| 3-222.  | Run Logic                                |

| 3-224.  | Run Mode                                 |

| 3-226.  | Single Instruction Mode                  |

| 3-230.  | Single Cycle Mode                        |

| 3-233.  | Halt Mode                                |

| 3-235.  | Automatic Restart                        |

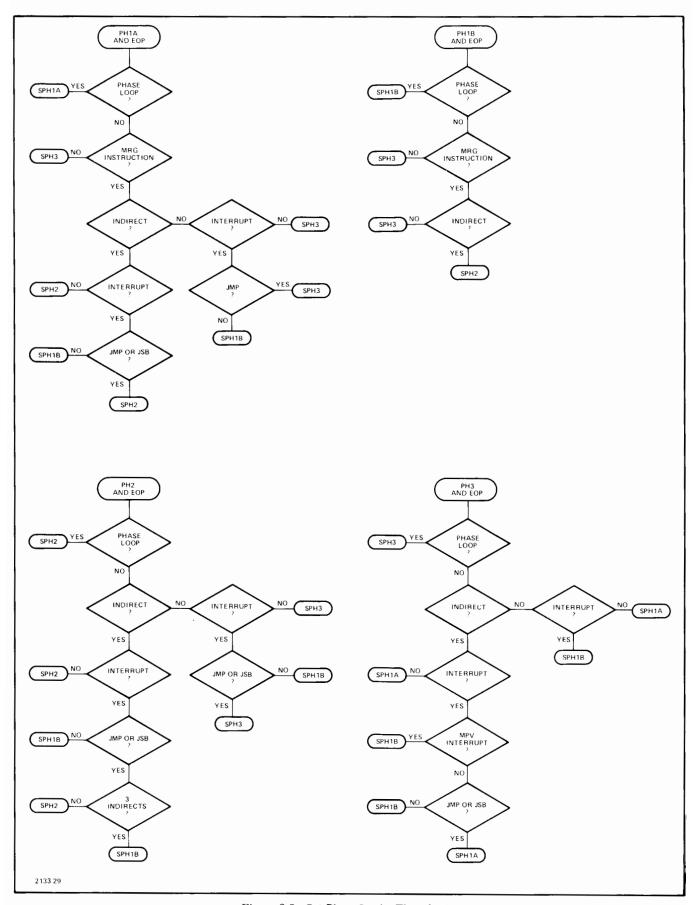

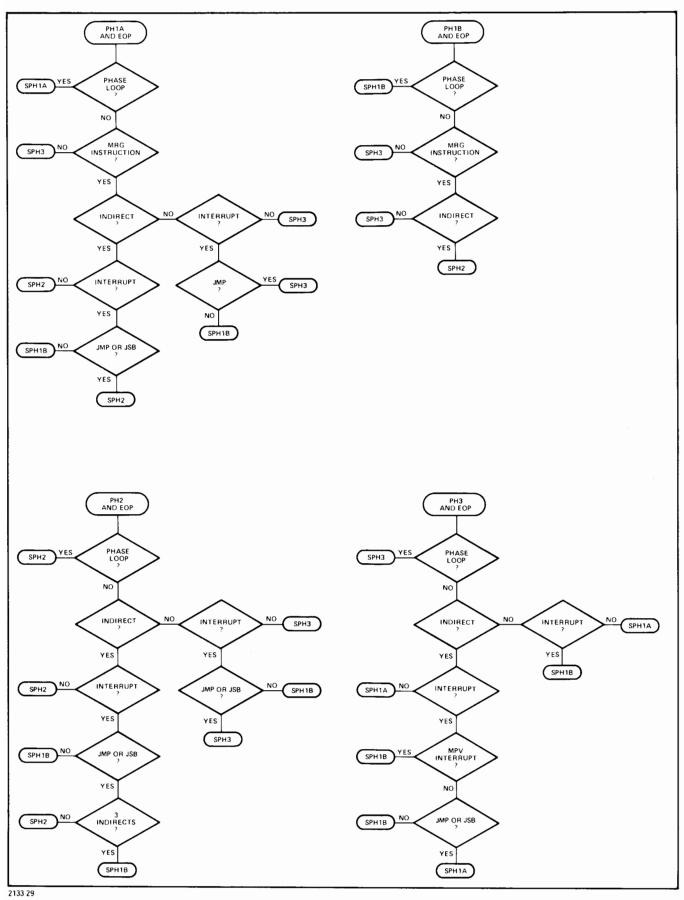

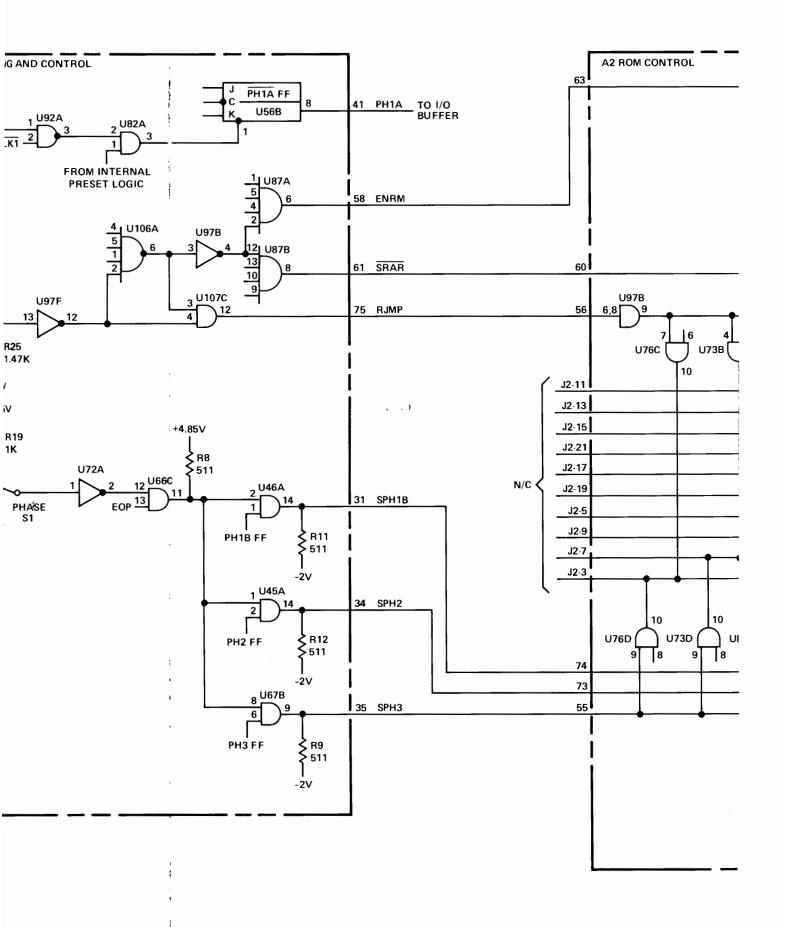

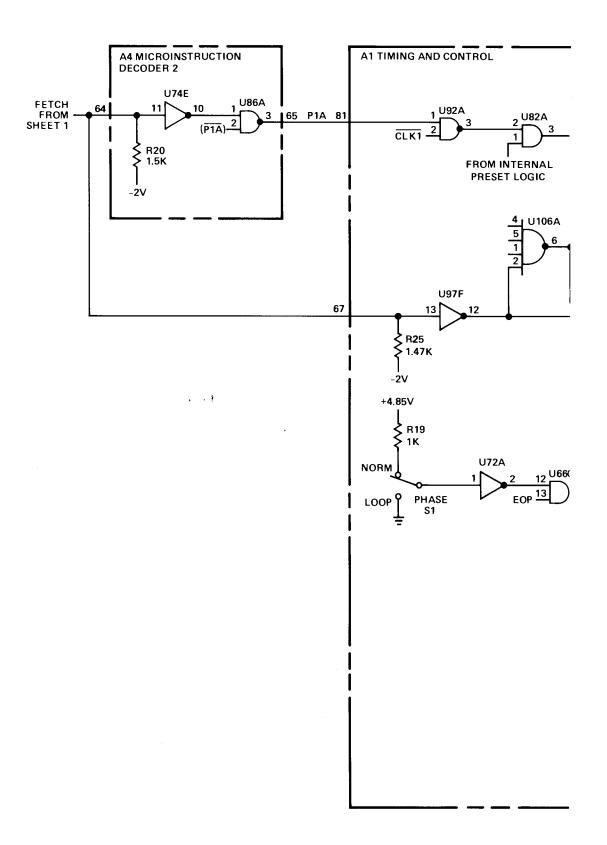

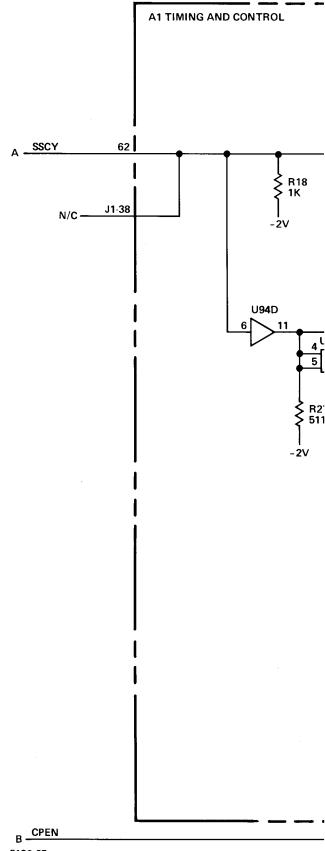

| 3-237.  | Phase Control Logic                      |

| 3-240.  | Phase 1A                                 |

| 3-241.  | Phase 1B                                 |

| 3-245.  | Phase 2                                  |

| 3-249.  | Phase 3                                  |

| 3-253.  | Forcing Phase 1A                         |

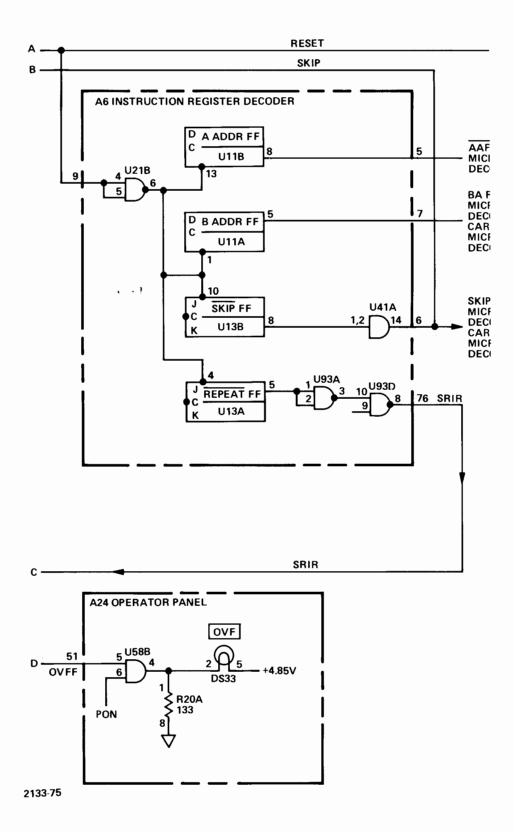

| 3-254.  | Internal Preset                          |

| 3-255.  | P-Switch                                 |

| 3-256.  | Decoding P1A                             |

| 3-257.  | Power On                                 |

| 3-258.  | Forcing Phase 1B                         |

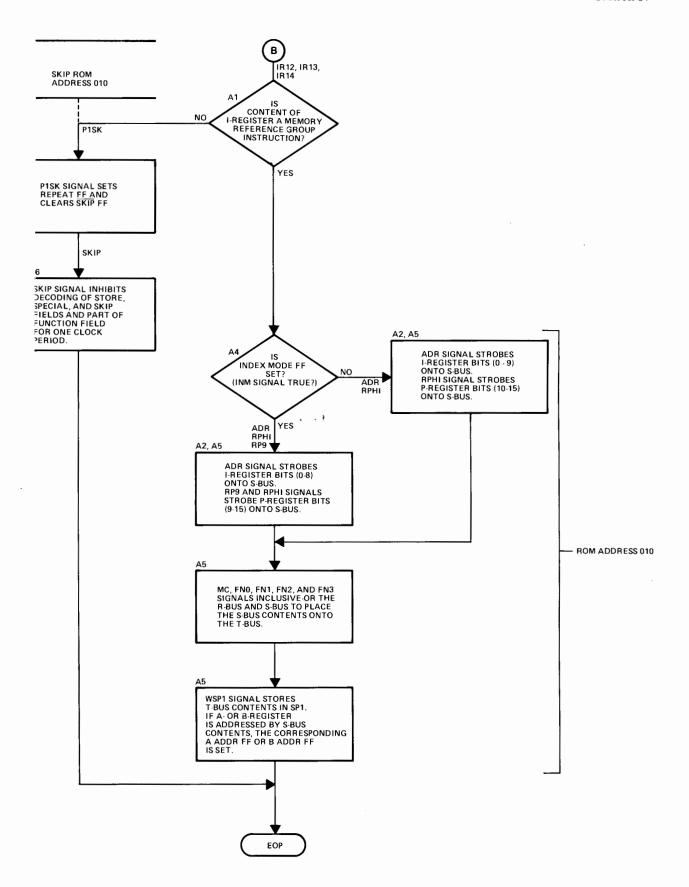

| 3-259.  | Phase 1 Skip                             |

| 3-261.  | Phase Loop                               |

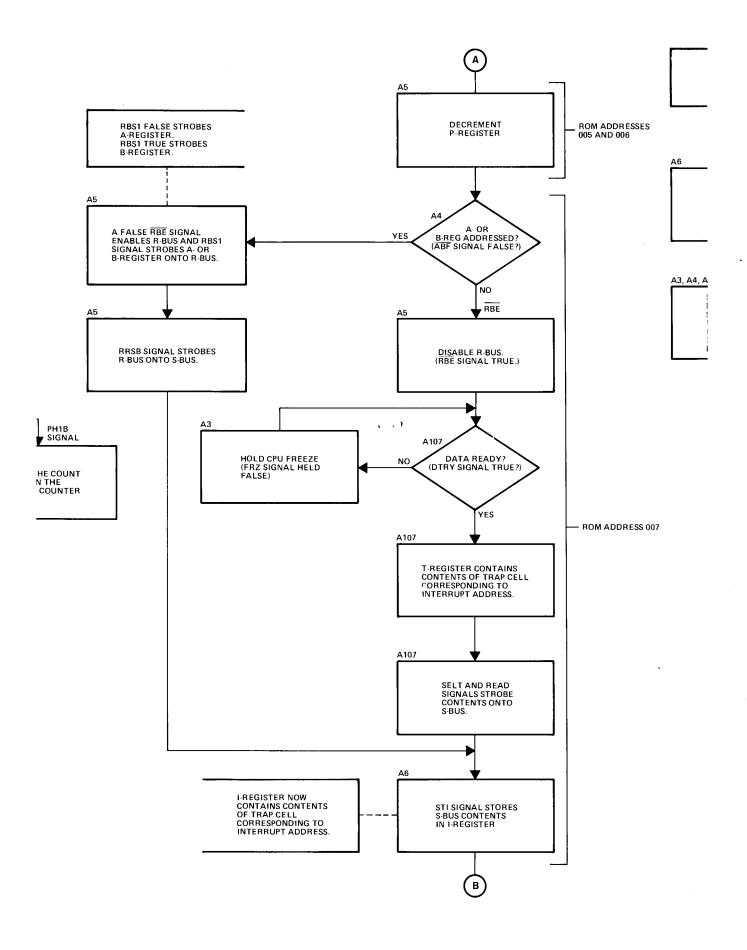

| 3-263.  | Indirect Counter                         |

| 3-267.  | ROM Mapper                               |

| 3-269.  | Set Phase Signals                        |

| 3-270.  | I-Register Bit Decoding                  |

| 3-271.  | ROM Module Addressing                    |

| 3-273.  | ROM Jumps                                |

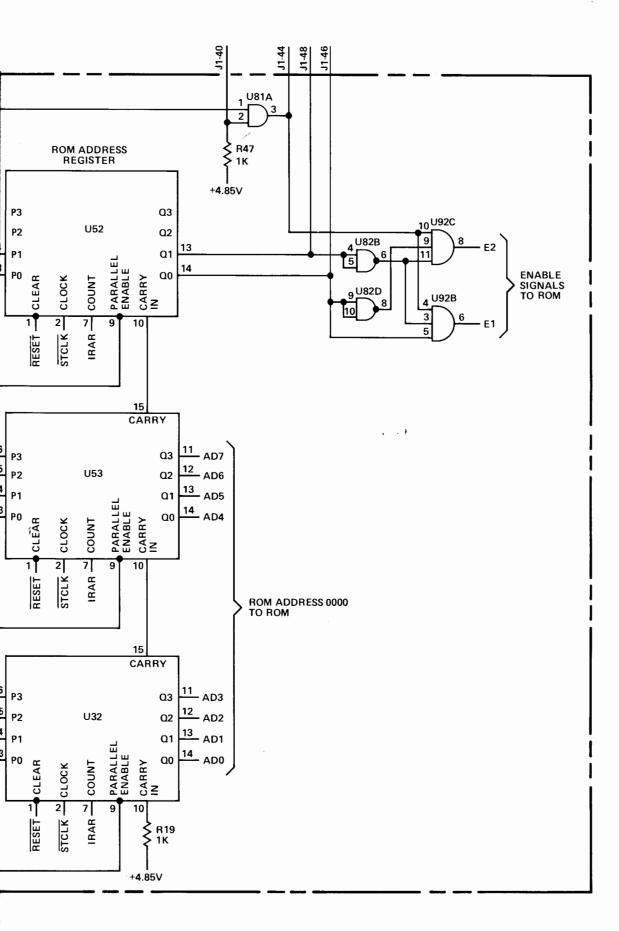

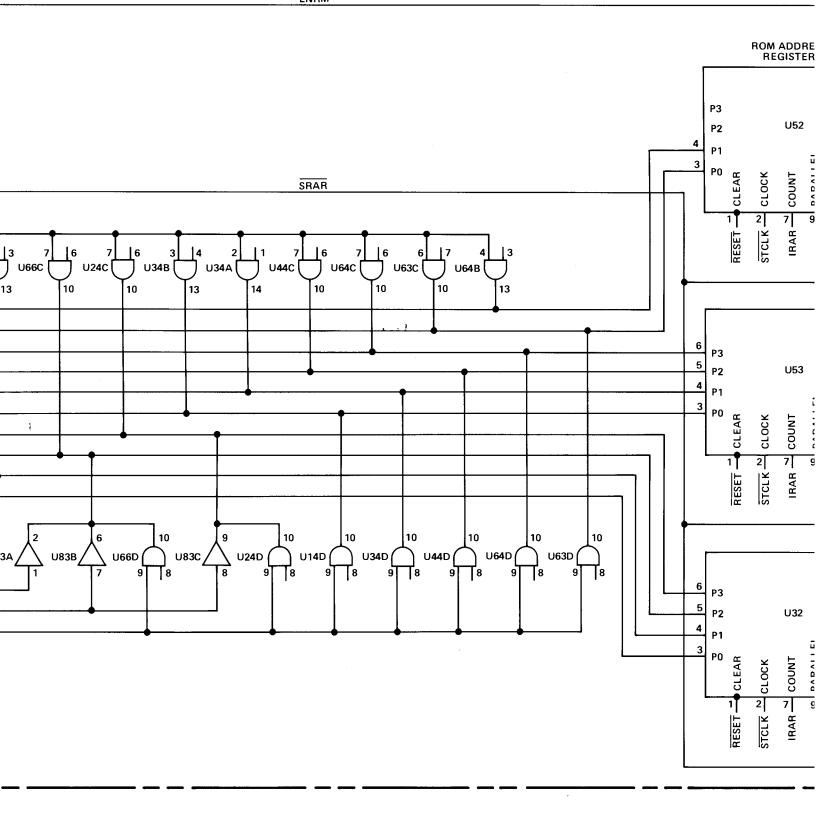

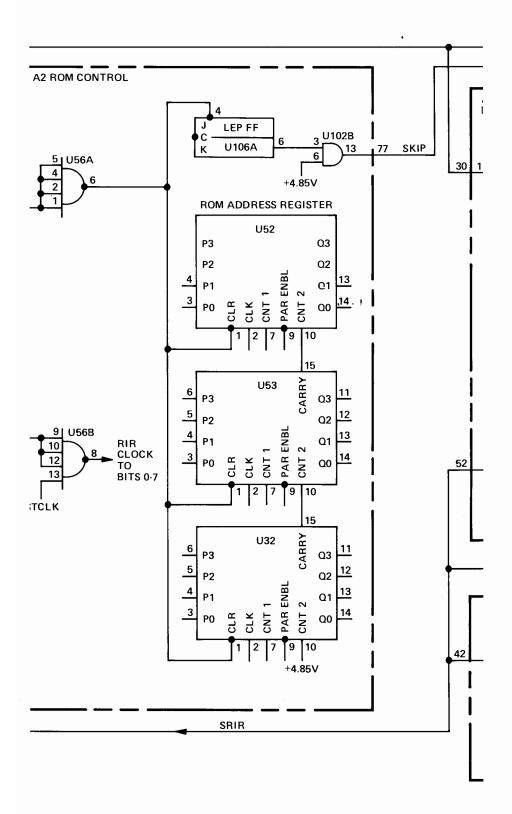

| 3-275.  | ROM Address Register                     |

| 3-277.  | Loading the RAR                          |

| 3-278.  | Incrementing the RAR                     |

| 3-279.  | Clearing the RAR                         |

| 3-280.  | End-of-Phase Logic                       |

| 3-282.  | NER FF                                   |

| 3-284.  | LEP FF                                   |

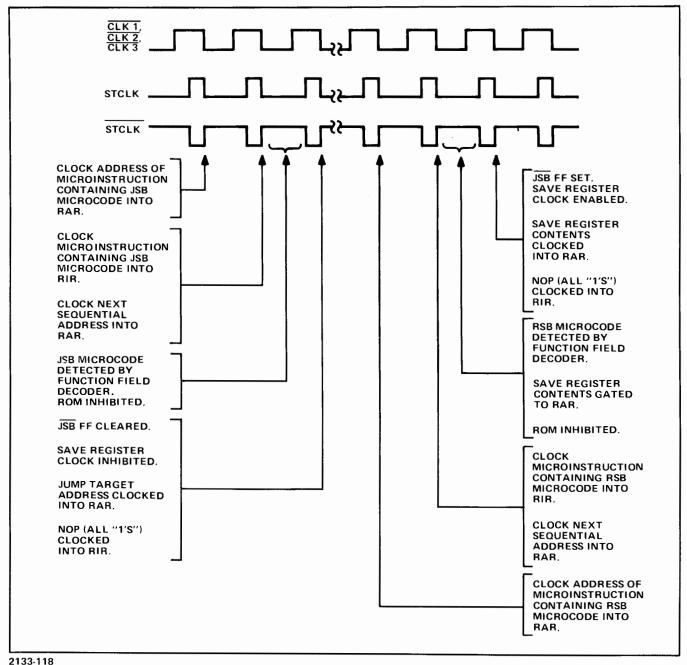

| 3-285.  | Save Register                            |

| 3-292.  | ROM                                      |

| 3-298.  | The ROM Microprogram                     |

| 3-300.  | Microcode                                |

| 3-301.  | Microinstruction                         |

| 3-302.  | Microroutine                             |

| 3-303.  | Subroutine                               |

| 3-304.  | Entry Point Labels                       |

| 3-305.  | Legal Entry Points                       |

| 3-306.  | End-of-Phase                             |

| 3-307.  | ROM Skip Mode                            |

| 3-309.  | ROM Jump Mode                            |

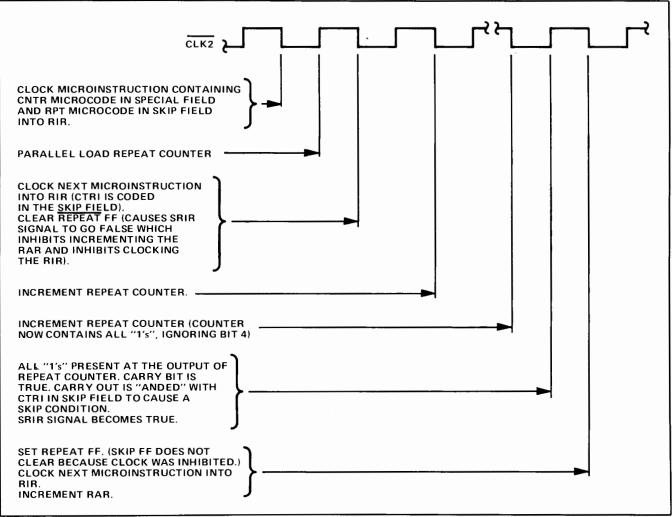

| 3-311.  | ROM Repeat Mode                          |

| 3-311.  | Synchronizing with I/O Time Periods      |

| 3-314.  | ROM Control Logic                        |

| 3-314.  | ROM Jump Control                         |

| 3-310.  | Return from ROM Subroutines 3-40         |

| Section | •                            | Page |

|---------|------------------------------|------|

| 3-321.  | End-of-Phase                 |      |

| 3-322.  | Halt Mode                    | 3-41 |

| 3-323.  | Automatic Restart            | 3-41 |

| 3-324.  | ROM Instruction Register     | 3-41 |

| 3-326.  | Inputs                       |      |

| 3-327.  | Clocking                     |      |

| 3-330.  | Output Destinations          |      |

| 3-331.  | Instruction Register         |      |

| 3-333.  | Clocking                     |      |

| 3-334.  | S-Bus Data                   |      |

| 3-335.  |                              |      |

|         | Function of I-Register Bits  |      |

| 3-336.  | ROM Microinstruction Decoder |      |

| 3-338.  | R-Bus Field Decoder          |      |

| 3-339.  | A (000)                      |      |

| 3-340.  | AAB (101)                    |      |

| 3-341.  | B (001)                      | 3-43 |

| 3-342.  | CAB (100)                    | 3-43 |

| 3-343.  | CQ (110)                     |      |

| 3-344.  | F (011)                      |      |

| 3-345.  | NOP (111)                    |      |

| 3-346.  | Q (010)                      |      |

|         |                              |      |

| 3-347.  | S-Bus Field Decoder          |      |

| 3-348.  | ADR (0110)                   |      |

| 3-349.  | CIR (0000)                   |      |

| 3-350.  | CL (1101)                    |      |

| 3-351.  | CNTR (0101)                  |      |

| 3-352.  | COND (0111)                  | 3-45 |

| 3-353.  | CR (1100)                    | 3-45 |

| 3-354.  | IOI (0001)                   | 3-45 |

| 3-355.  | M(0011)                      |      |

| 3-356.  | NOP (1111)                   |      |

| 3-357.  | P (1110)                     |      |

| 3-358.  | RRS (0100)                   |      |

| 3-359.  | S1 (1011)                    |      |

| 3-360.  | S2 (1010)                    |      |

|         |                              |      |

| 3-361.  | \$3 (1001)                   |      |

| 3-362.  | S4 (1000)                    |      |

| 3-363.  | T (0010)                     |      |

| 3-364.  | Function Field Decoder       | 3-45 |

| 3-368.  | ADD (01011)                  |      |

| 3-369.  | ADDO (01010)                 |      |

| 3-370.  | AND (01100)                  | 3-46 |

| 3-371.  | ARS (11000)                  | 3-46 |

| 3-374.  | CFLG (11011)                 | 3-47 |

| 3-375.  | CJMP (10100 or 11001)        | 3-47 |

| 3-376.  | CLO (11101)                  |      |

| 3-377.  | CRS (10111)                  |      |

| 3-379.  | DEC (00110)                  |      |

| 3-380.  | DIV (00100)                  |      |

|         |                              |      |

| 3-385.  | INC (01001)                  |      |

| 3-386.  | INCO (01000)                 |      |

| 3-387.  | IOR (11111)                  |      |

| 3-388.  | JMP (10010 or 10011)         |      |

| 3-390.  | JSB (10000 or 10001)         |      |

| 3-391.  | LGS (10110)                  |      |

| 3,393   | LWF (11010)                  | 3.49 |

| Page                  |

|-----------------------|

| MPY (00011)           |

| NOR (01101)           |

| P1A (00010)           |

| RFE (00001)           |

| RFI (00000)           |

| RSB (10101)           |

| SFLG (11100)          |

| SOV (11110)           |

| SUB (00101)           |

| XOR (01110)           |

| Store Field Decoder   |

| A (1110)              |

| AAB (1100)            |

| B (1101)              |

| CAB (1011)            |

|                       |

| F (1001)              |

| IR (0011)             |

|                       |

| M (0001)              |

| P(1000)               |

| Q (1010)              |

| \$1 (0111)            |

| \$2 (0110)            |

| S3 (0101)             |

| S4 (0100)             |

| T (0010)              |

| NOP (1111)            |

| Special Field Decoder |

| AAB (0110)            |

| ASG1 (1010)           |

| ASG2 (1011)           |

| CNTR (0011)           |

| CW (1100)             |

| ECYN (1001)           |

| ECYZ (1000)           |

| IOG1 (1101)           |

| L1 (0001)             |

| LEP (0111)            |

| R1 (0010)             |

| RSS (0000)            |

| RW (1110)             |

| SRG1 (0100)           |

| SRG2 (1011)           |

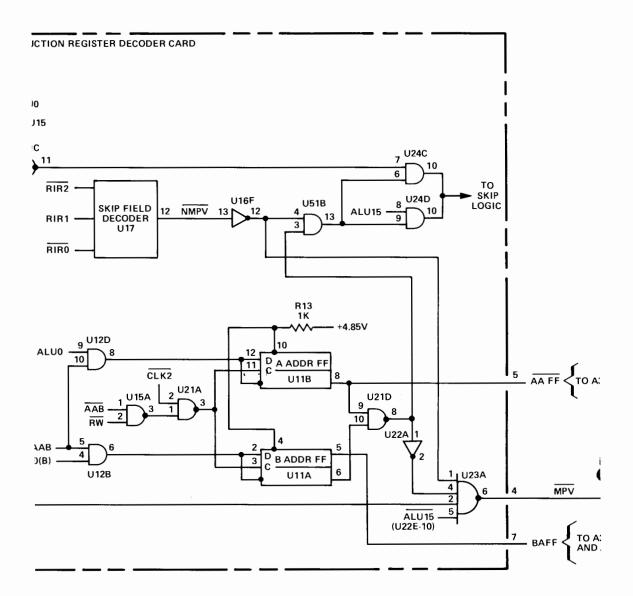

| Skip Field Decoder    |

| AAB (1011)            |

| COUT (0100)           |

| CTR (1001)            |

| CTRI (1000)           |

| EOP (1101)            |

| FLG (0110)            |

| ICTR (0000)           |

| NAAB (1100)           |

| NEG (0011)            |

| NMPV (1010)           |

| ODD (0010)            |

| OVF (0101) 3-5        |

|                       |

| Section        |                                              | Page |

|----------------|----------------------------------------------|------|

| 3-459.         | RPT (0001)                                   | 3-54 |

| 3-460.         | TBZ (0111)                                   |      |

| 3-461.         | UNC (1110)                                   |      |

| 3-462.         | NOP (1111)                                   |      |

| 3-463.         | Repeat Counter                               |      |

| 3-466.         | Loading the Counter                          |      |

| 3-467.         | Incrementing the Counter                     |      |

| 3-470.         | Clearing the Counter                         |      |

| 3-471.         | Gating Onto the S-Bus                        |      |

| 3-472.         | EAG Doubleword Shifts and Rotates            |      |

| 3-473.         | EAG Multiply and Divide Operations           |      |

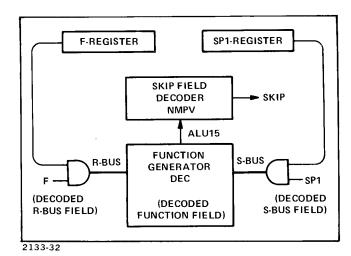

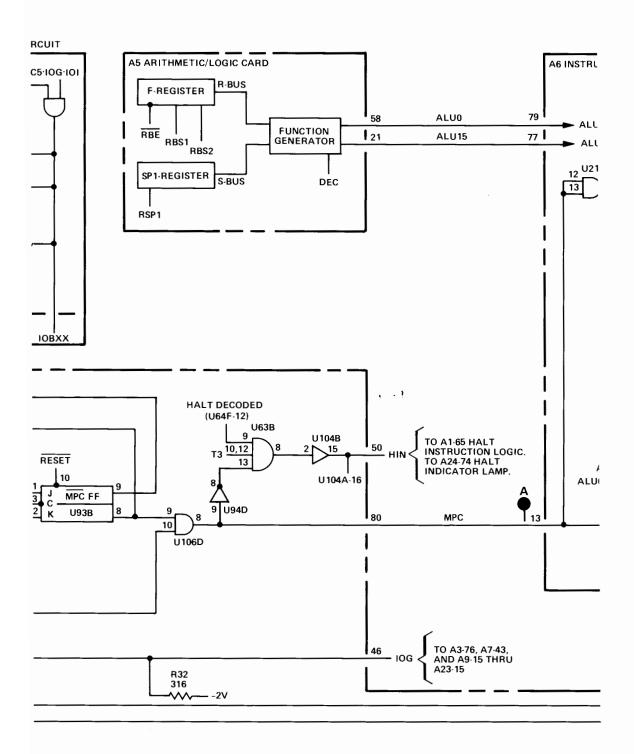

| 3-474.         | Arithmetic and Logic Section Detailed Theory | 3-55 |

| 3-477.         | A-Addressable and B-Addressable FF Logic     |      |

| 3-483.         | A/B Clear and A/B Select Flip-Flop Logic     |      |

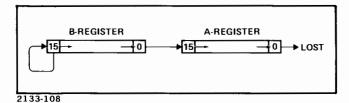

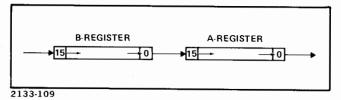

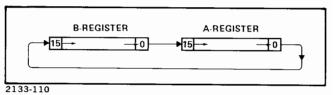

| 3-486.         | A- and B-Registers                           | 3-57 |

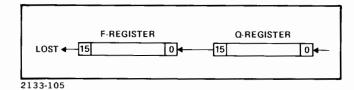

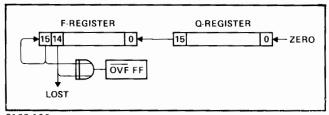

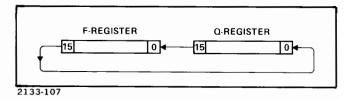

| 3-488.         | F- and Q-Registers                           |      |

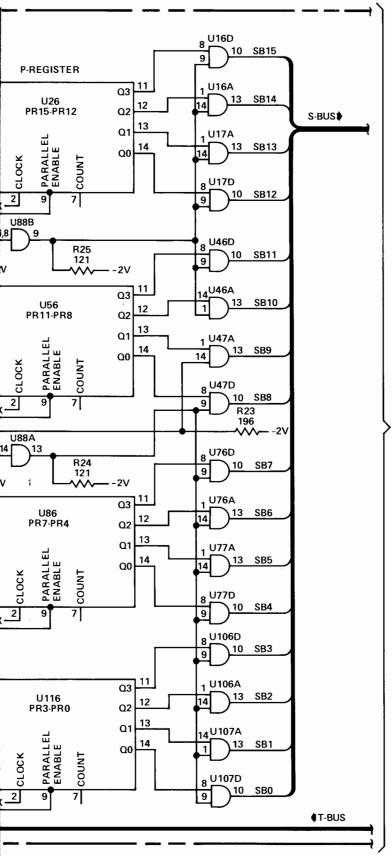

| 3-490.         | P-Register                                   |      |

| 3-493.         | Scratch Pad Registers                        | 3-57 |

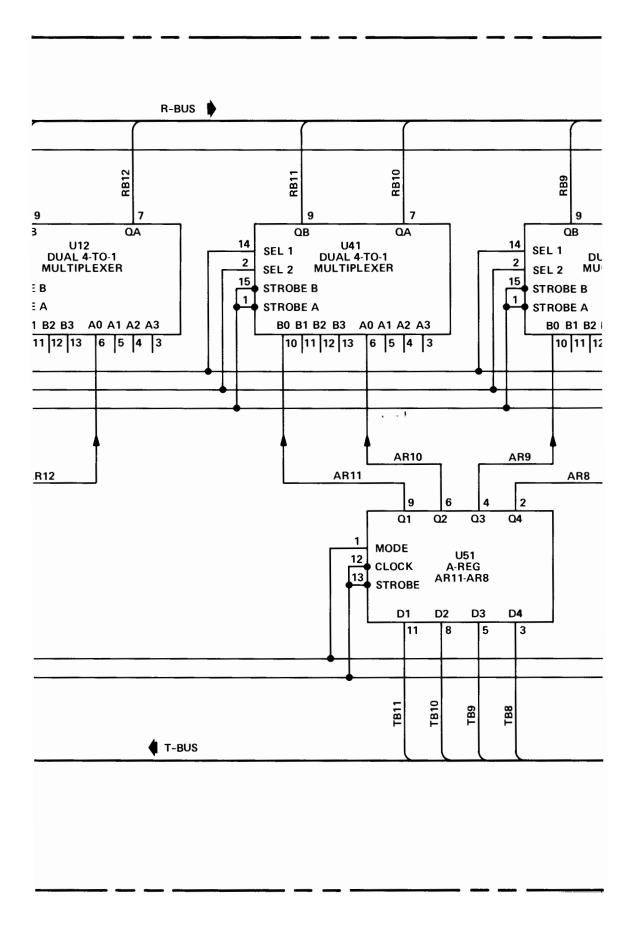

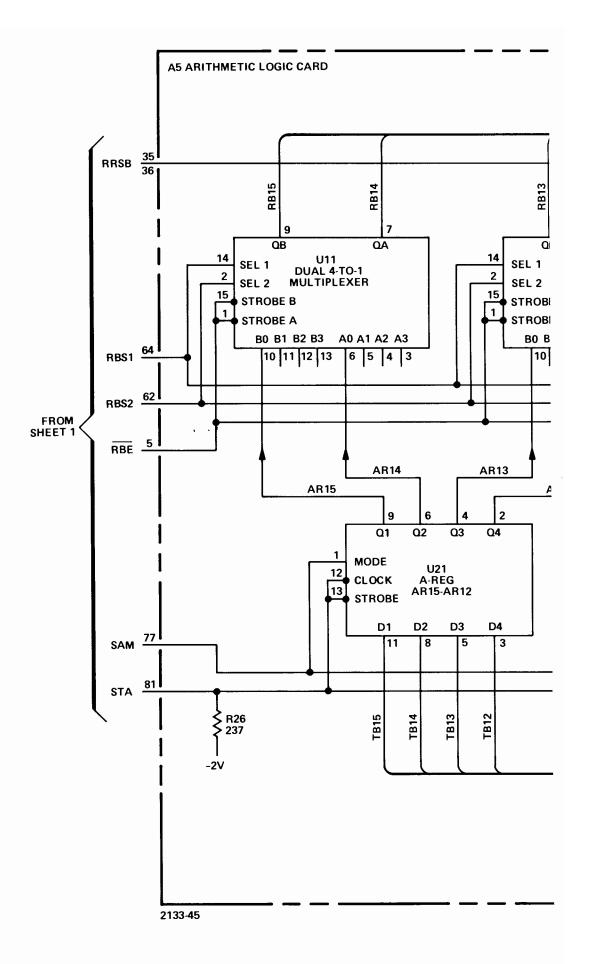

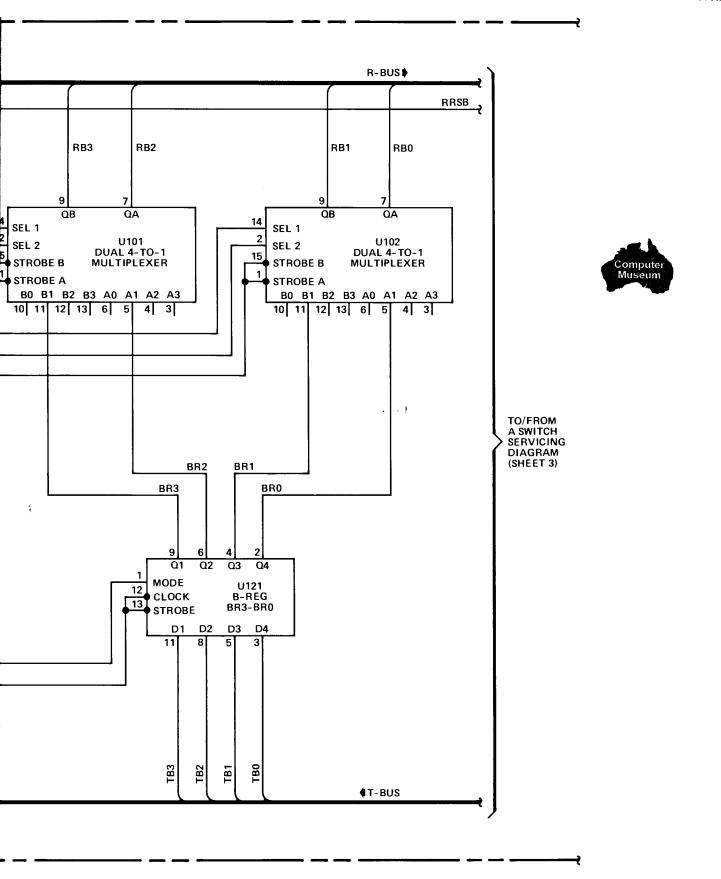

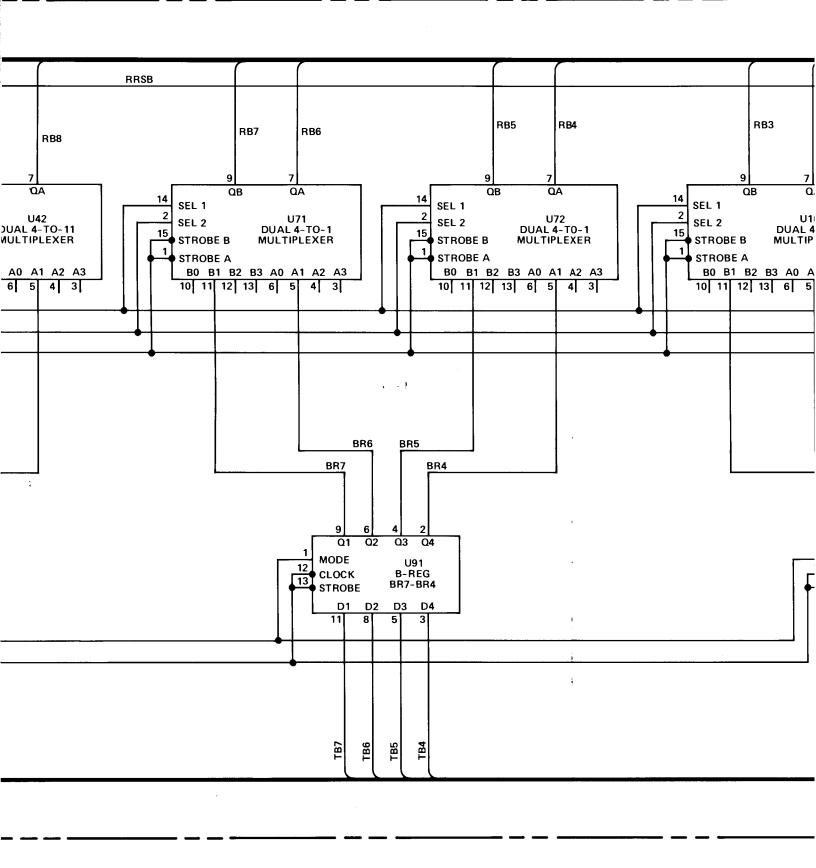

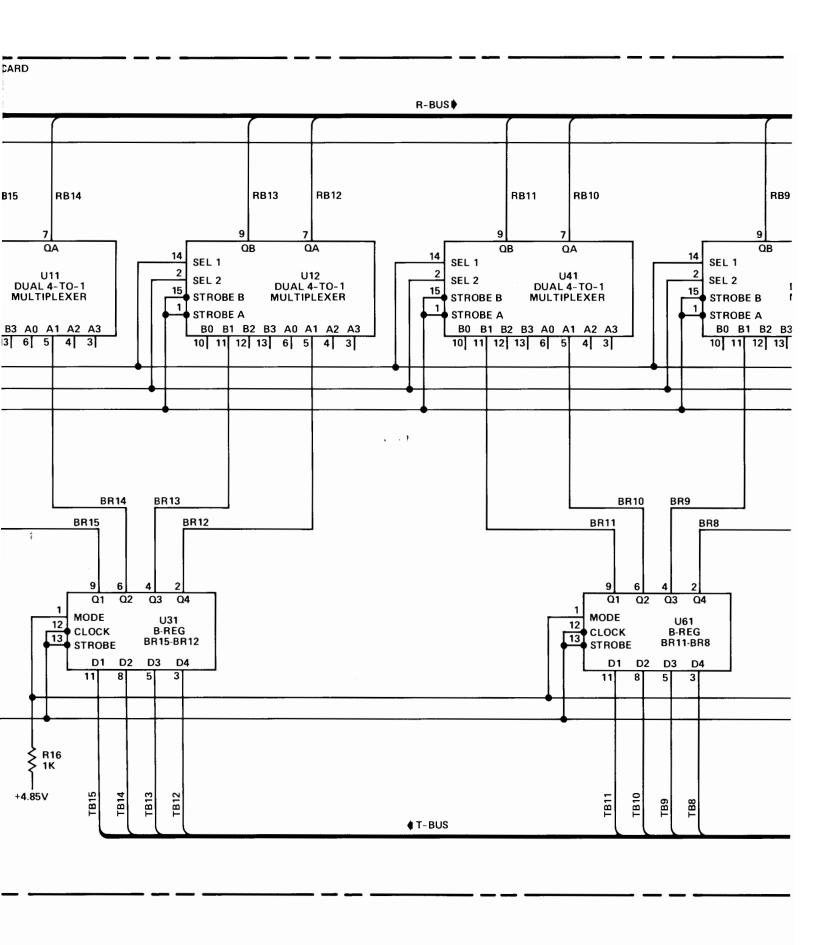

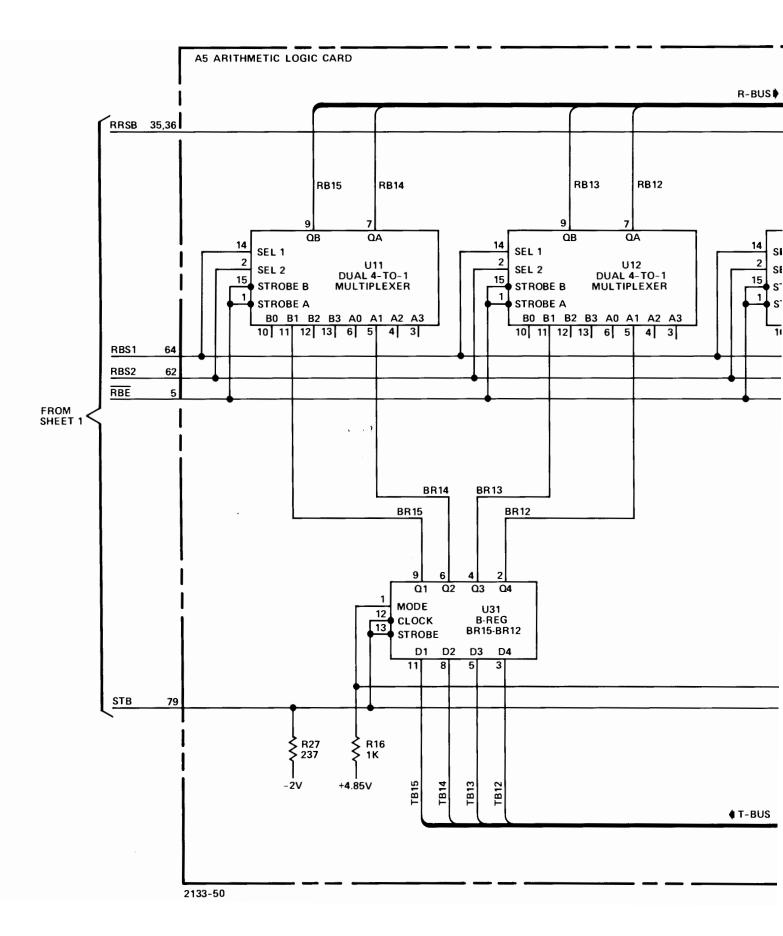

| 3-496.         | R-Bus Multiplexer                            | 3-57 |

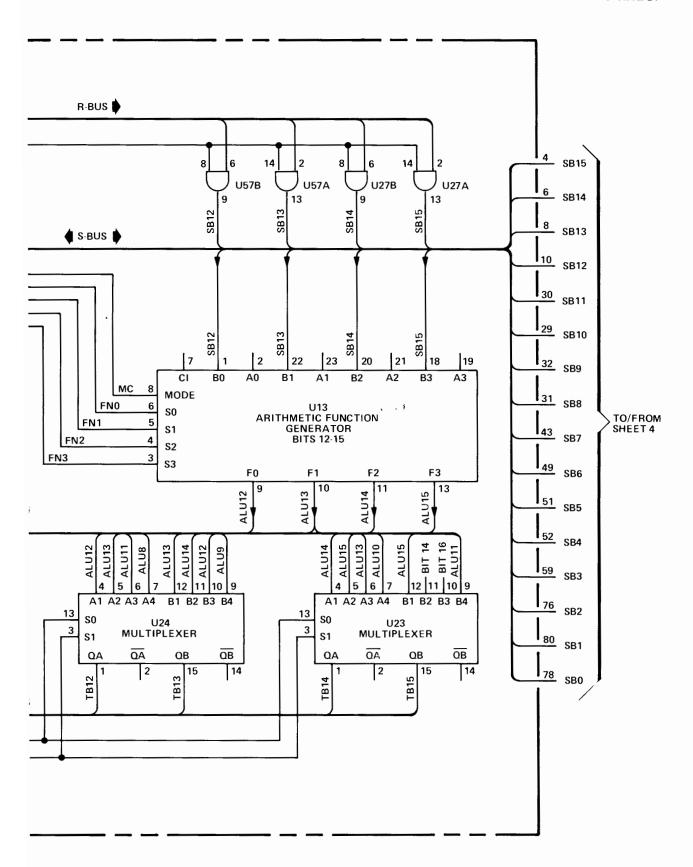

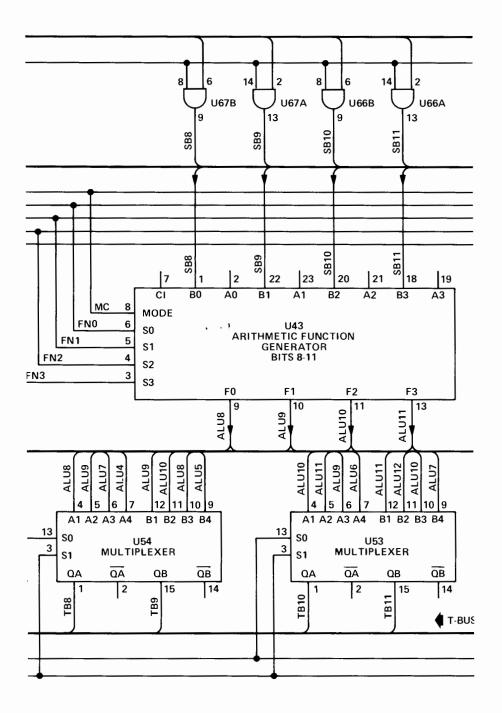

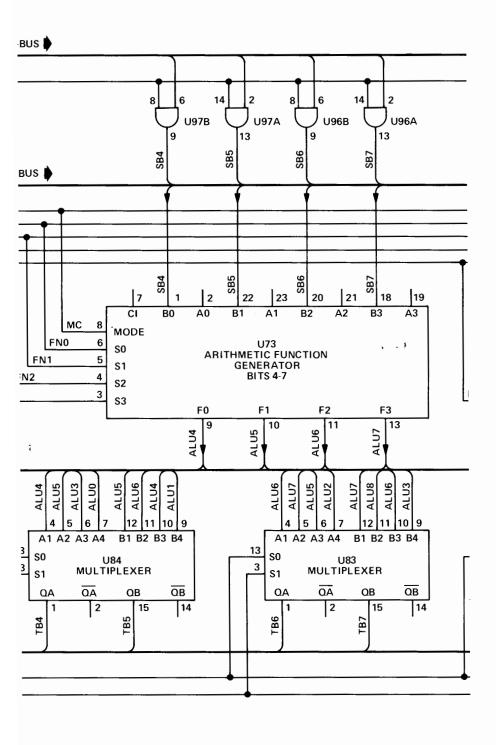

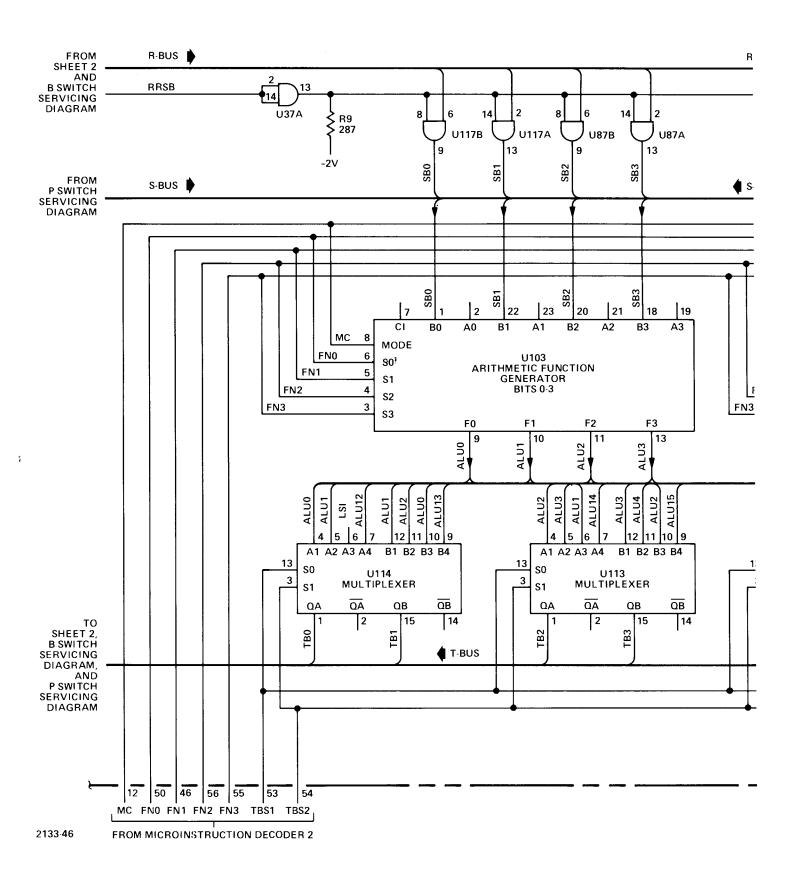

| 3-498.         | Arithmetic Function Generator                | 3-58 |

| 3-500.         | Shifter and Shift Linkage                    | 3-58 |

| 3-502.         | RFE Logic                                    | 3-58 |

| 3-504.         | CPU Flag Logic                               | 3-58 |

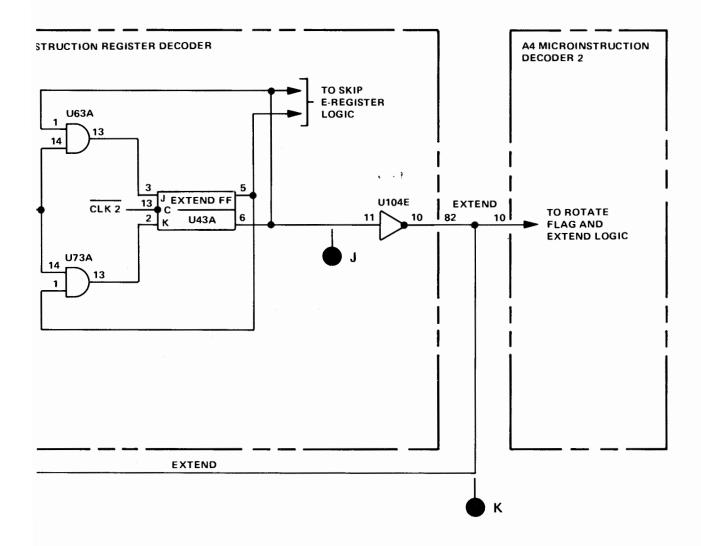

| 3-506.         | Extend Logic                                 | 3-58 |

| 3-508.         | Overflow Logic                               |      |

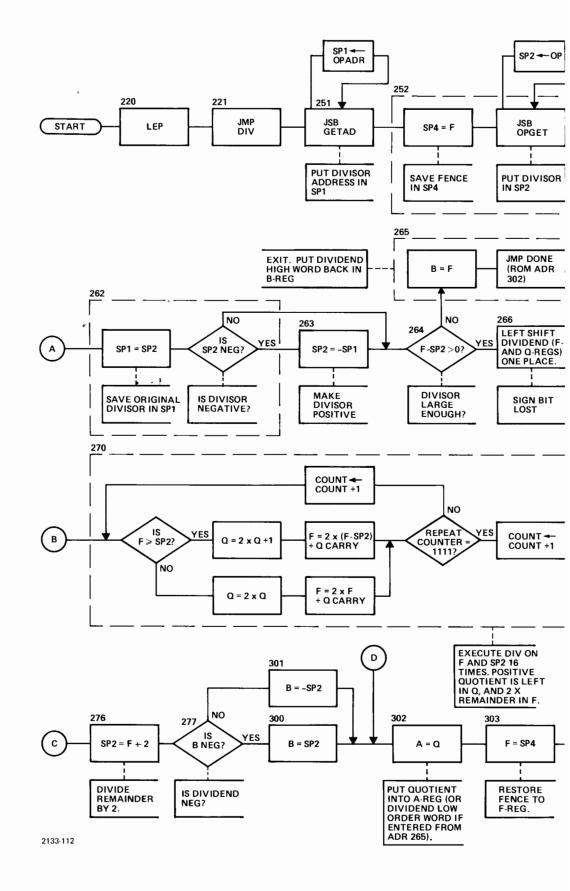

| 3-510.         | Memory Section, Detailed Theory              |      |

| 3-511.         | Functional Description                       | 3-59 |

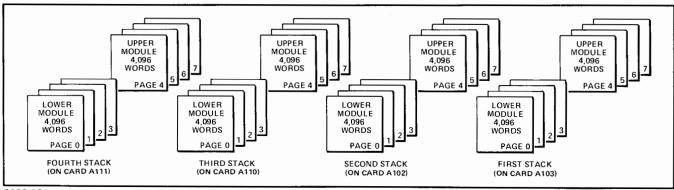

| 3-513.         | Core Stack Construction                      |      |

| 3-514.         | Organization of Data                         | 3-59 |

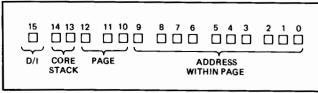

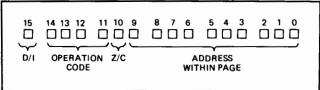

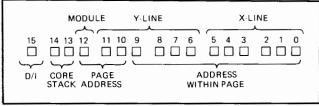

| 3-516.         | Addressing Method                            | 3-59 |

| 3-517.         | Full Address Word                            |      |

| 3-518.         | Addressing by Instruction Word               |      |

| 3-519.         | Memory Read Operations                       |      |

| 3-521.         | Readout for Display                          |      |

| <b>3-52</b> 3. | Instruction Word Readout                     |      |

| 3-525.         | Operand Readout                              |      |

| 3-533.         | Memory Write Operations                      |      |

| 3-534.         | Addressing Beyond Available Memory           |      |

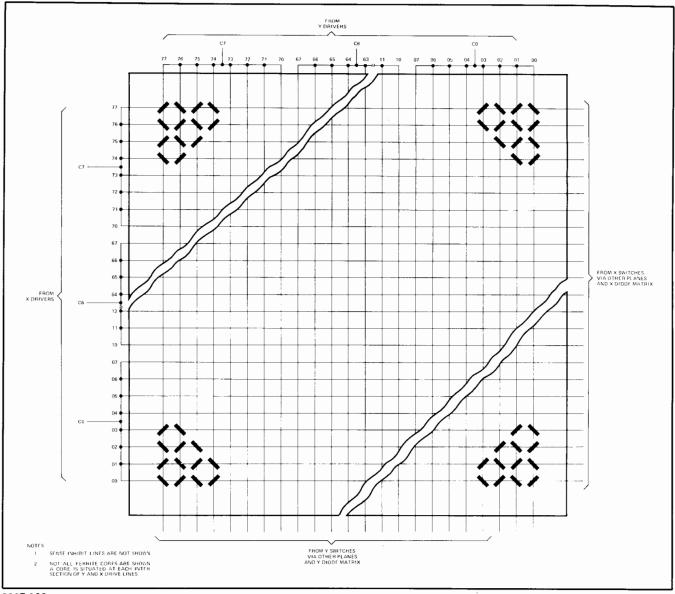

| 3-535.         | Block Diagram Analysis                       | 3-63 |

| 3-536.         | Address Selection                            |      |

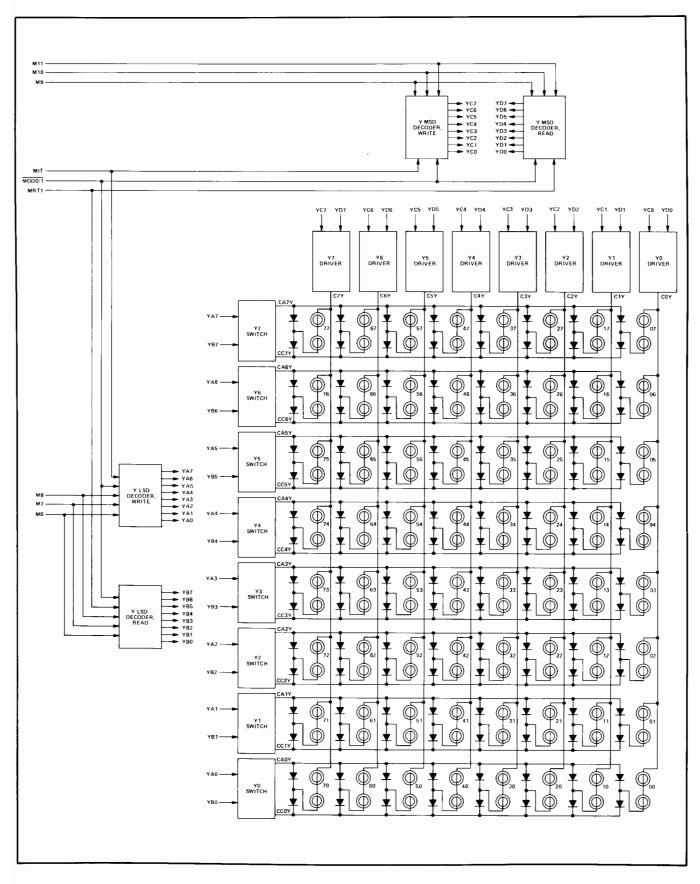

| 3-540.         | Y-Line Selection                             |      |

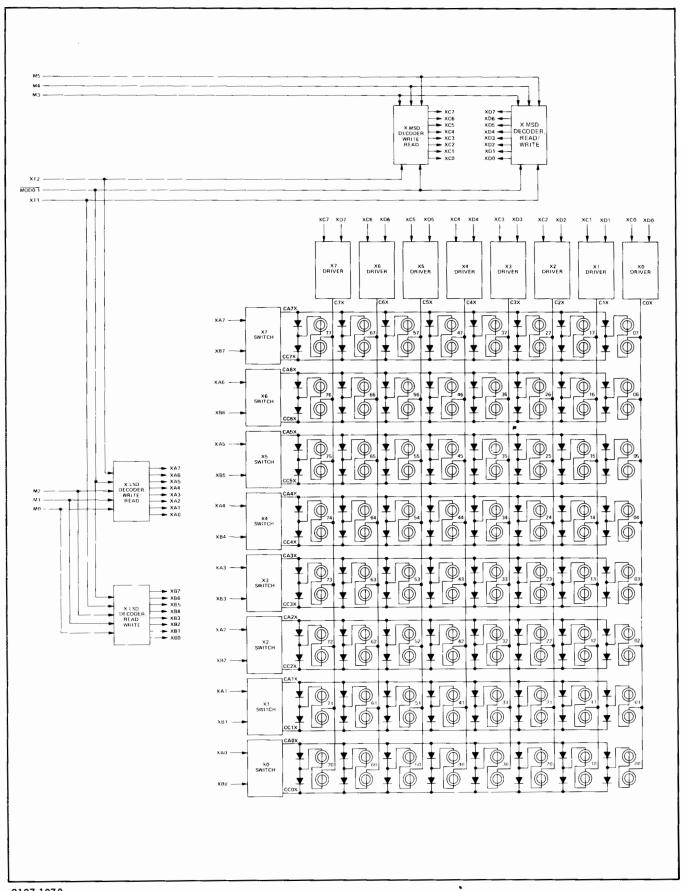

| 3-551.         | X-Line Selection                             |      |

| 3-555.         | Operation of Memory Section                  |      |

| 3-556.         | Core Stack                                   |      |

| 3-558.         | Lower Module Read Operations                 |      |

| 3-568.         | Lower Module Write Operations                |      |

| 3-570.         | Upper Module Read Operations                 |      |

| 3-571.         | Upper Module Write Operations                |      |

| 3-572.         | Logic Circuit Analysis                       |      |

| 3-574.         | Addressing Circuits                          |      |

| 3-582.         | Drivers and Switches                         |      |

| 3-587.         | Sense Amplifiers                             |      |

| 3-593.         | Inhibit Drivers                              |      |

| 3-601.         | Parity                                       |      |

| 3-605.         | Protective Circuits                          |      |

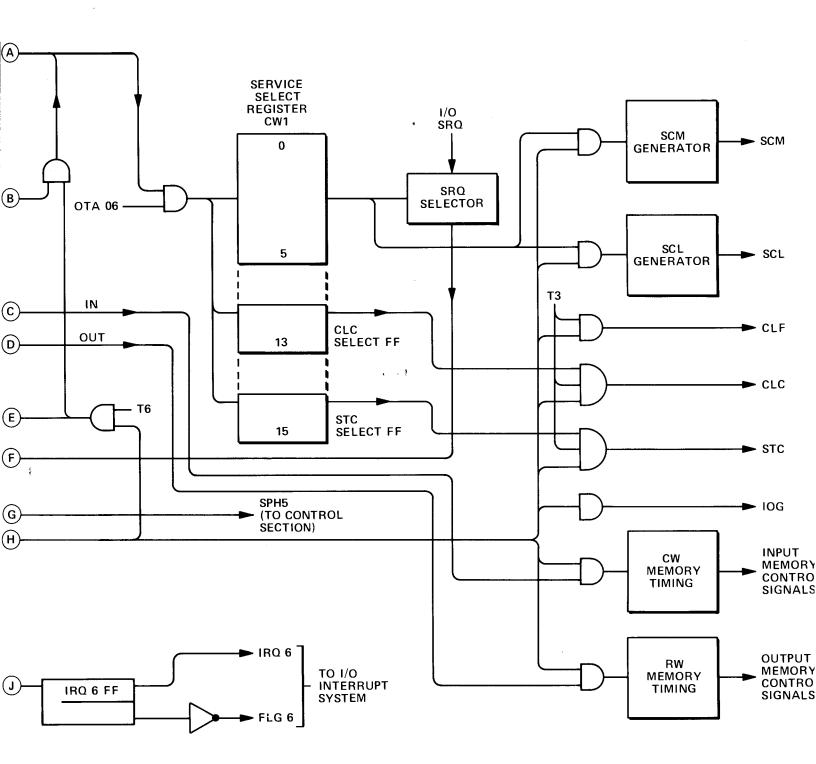

| 3-606.         | I/O Section Detailed Theory                  |      |

| 3-607.         | General                                      | 3-14 |

| Section |                                 | Page   |

|---------|---------------------------------|--------|

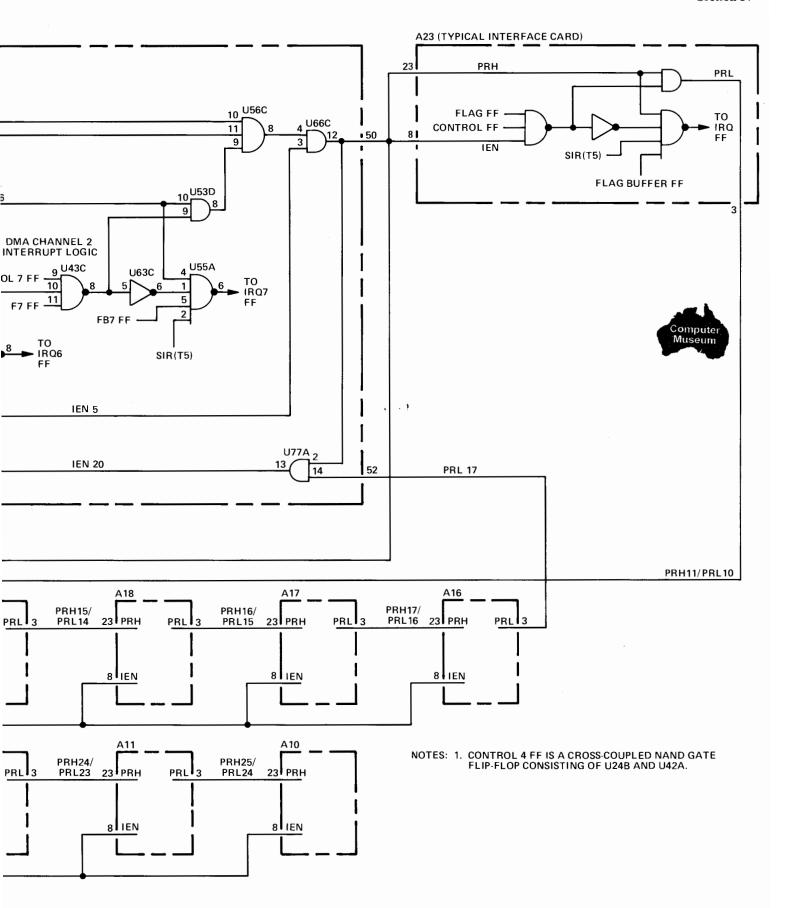

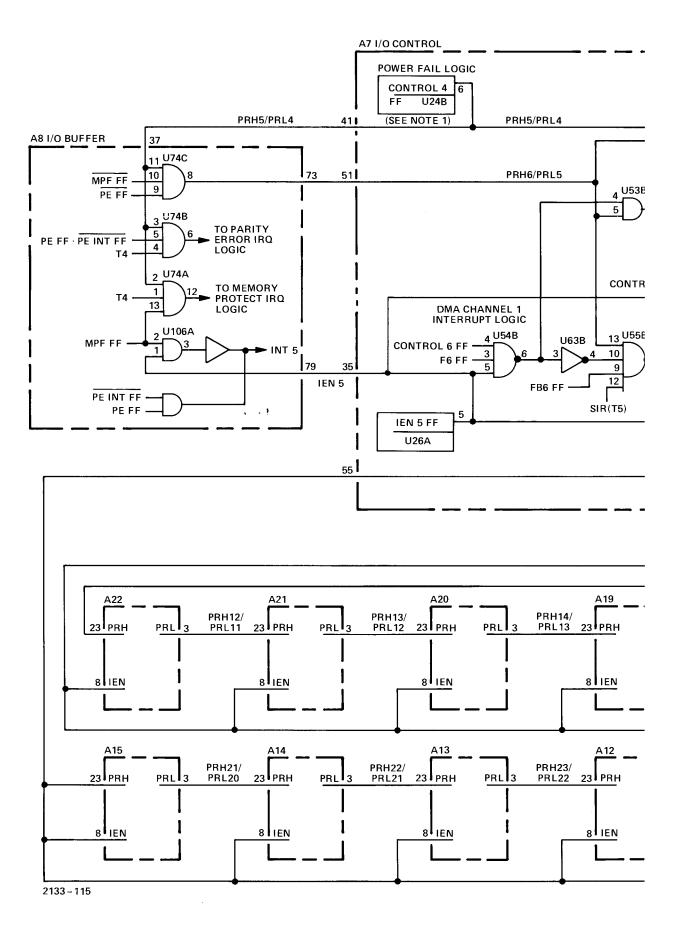

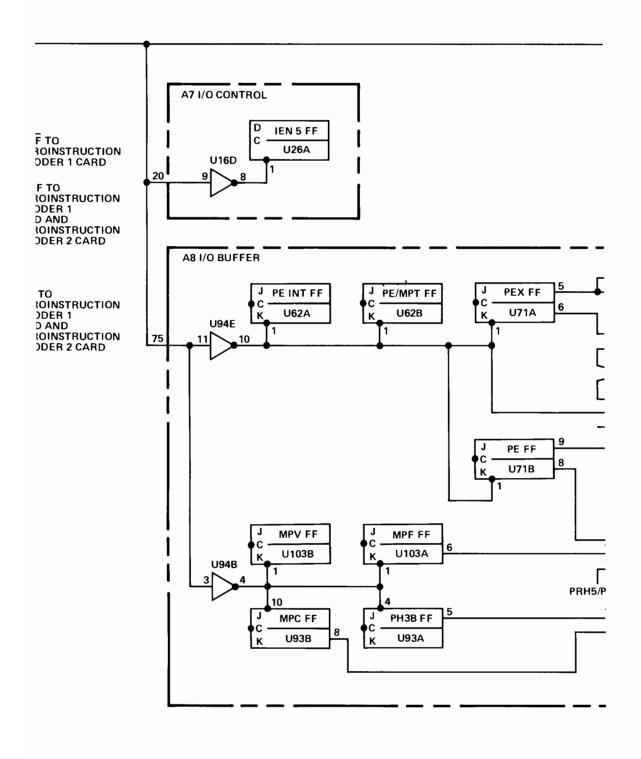

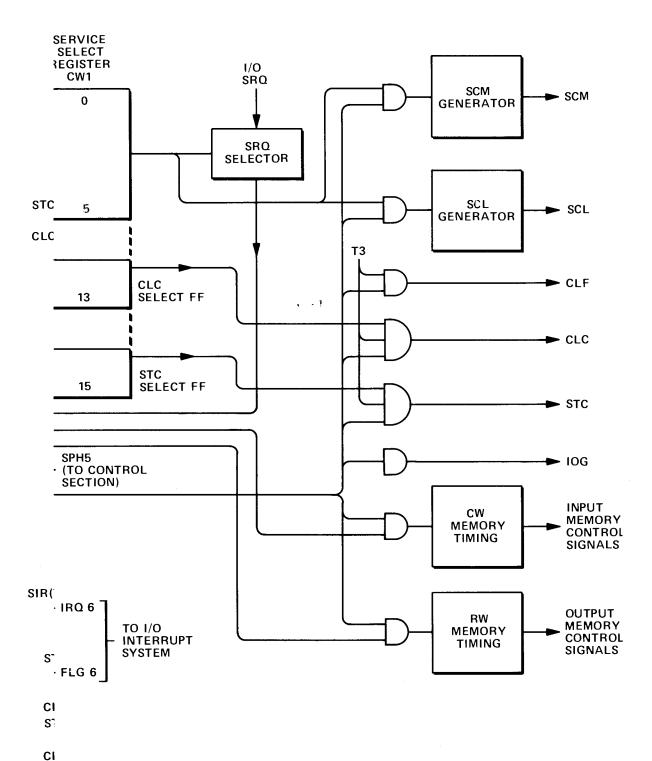

| 3-612.  | I/O Section Control Elements    | . 3-77 |

| 3-613.  | General                         | . 3-77 |

| 3-614.  | Input/Output Instructions       | . 3-77 |

| 3-617.  | Interrupt Requests              | . 3-78 |

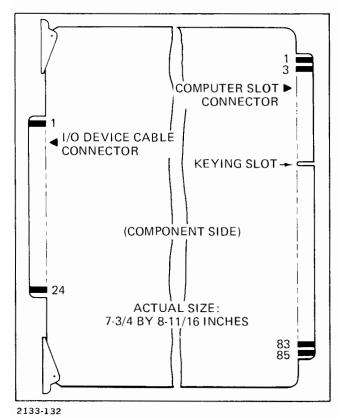

| 3-618.  | Interface Cards                 | . 3-78 |

| 3-619.  | Purpose                         | . 3-78 |

| 3-620.  | Logic Elements                  | . 3-79 |

| 3-621.  | Pin Assignments                 |        |

| 3-624.  | I/O Terminator Card             | . 3-79 |

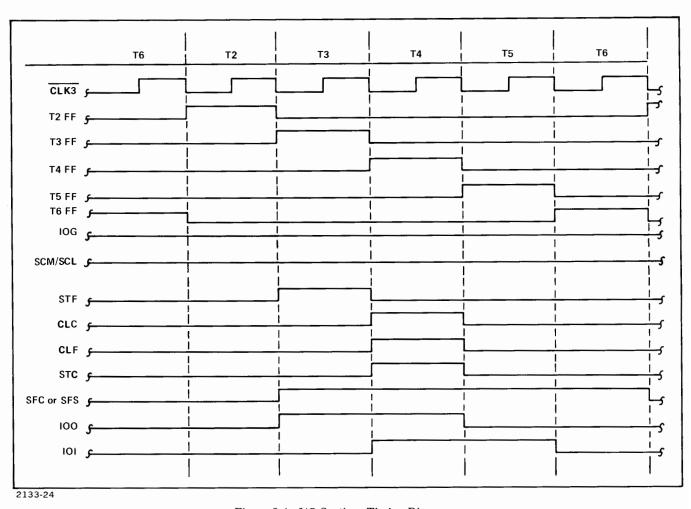

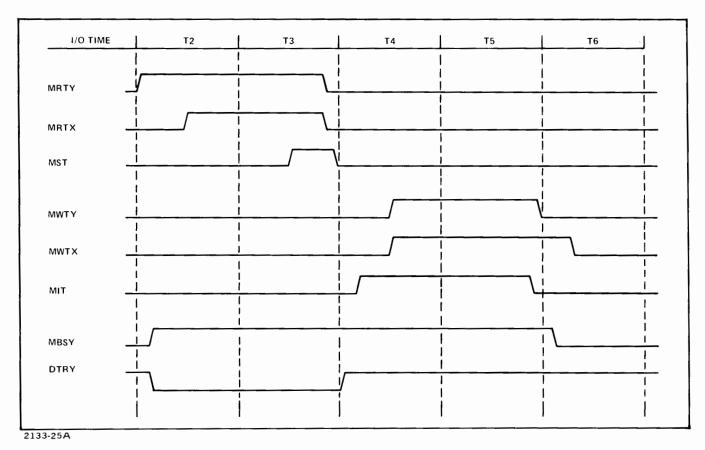

| 3-626.  | I/O Timing                      | . 3-79 |

| 3-627.  | I/O Time Period Generator       |        |

| 3-628.  | I/O Instruction Timing          |        |

| 3-630.  | I/O Control Signals Timing      |        |

| 3-631.  | ENF Signal                      |        |

| 3-632.  | SIR Signal                      |        |

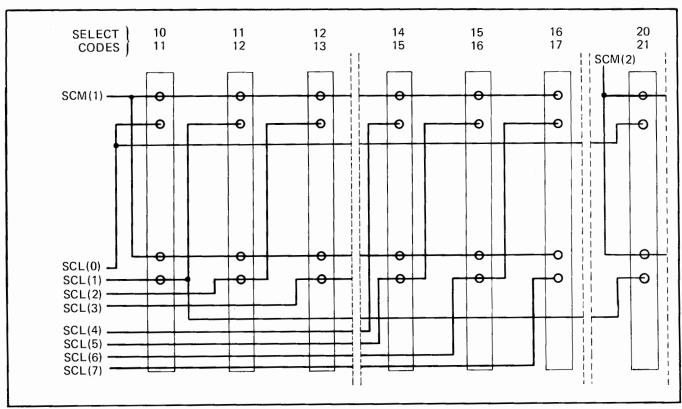

|         | I/O Addressing                  |        |

| 3-633.  |                                 |        |

| 3-637.  | Decoding Function               | . 3-01 |

| 3-643.  | Encoding Function               |        |

| 3-644.  | Central Interrupt Register      |        |

| 3-645.  | Loading                         |        |

| 3-646.  | Clocking                        |        |

| 3-647.  | Output Gating                   |        |

| 3-649.  | I/O Instruction Processing      |        |

| 3-650.  | ROM Program Control             |        |

| 3-652.  | I/O Group Decoder Circuits      |        |

| 3-654.  | Data Transfer Instructions      | . 3-84 |

| 3-655.  | MIA/B                           | . 3-84 |

| 3-657.  | LIA/B                           |        |

| 3-658.  | OTA/B                           | . 3-85 |

| 3-661.  | Control Instructions            | . 3-85 |

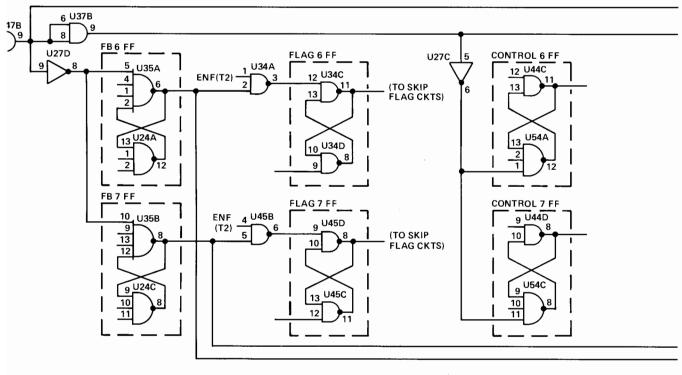

| 3-662.  | Flag Instructions               | . 3-85 |

| 3-663.  | Program Skip Instructions       |        |

| 3-664.  | Halt Instruction                |        |

| 3-667.  | Interrupt System                |        |

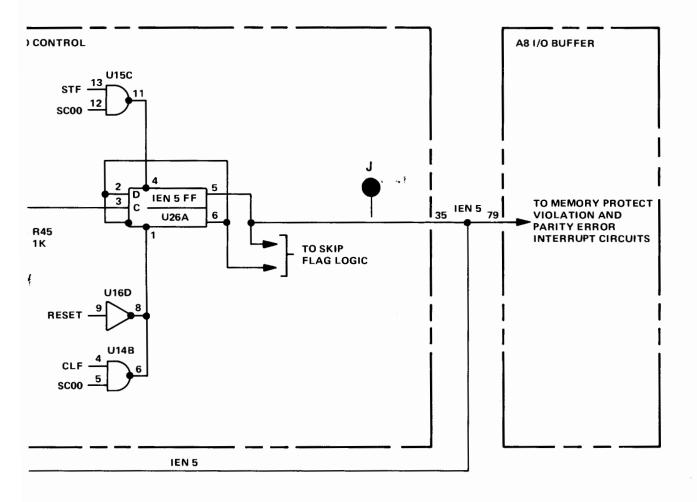

| 3-670.  | Interrupt System Enable/Disable |        |

| 3-674.  | Interrupt Priority              |        |

| 3-675.  | Priority Assignments            |        |

| 3-677.  | Priority Network Operation      |        |

| 3-682.  | Priority Continuity             |        |

| 3-684.  | Priority-Affecting Instructions |        |

| 3-686.  | Interrupt Generation            |        |

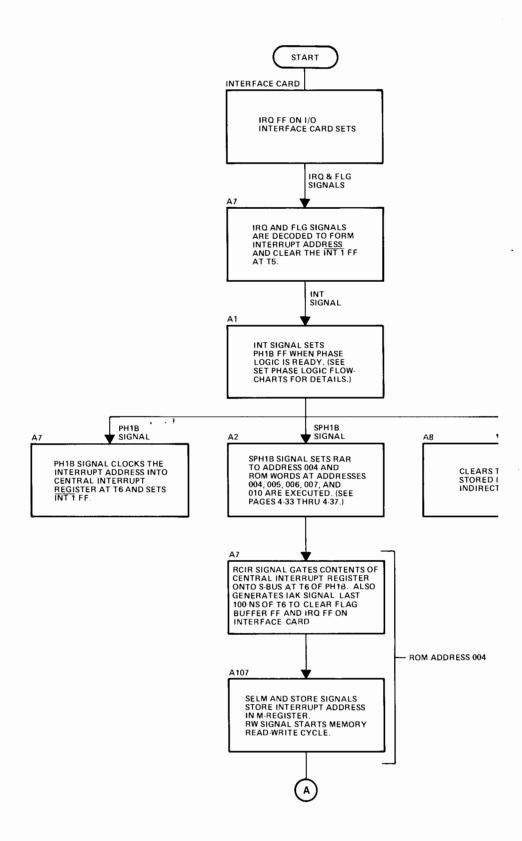

| 3-691.  | Interrupt Processing            |        |

| 3-692.  | Functional Description          |        |

| 3-694.  |                                 |        |

|         |                                 |        |

| 3-695.  | PH1B Signal                     |        |

| 3-697.  | IAK Signal                      |        |

| 3-698.  | ROM Address 004                 |        |

| 3-699.  | ROM Addresses 005 and 006       |        |

| 3-700.  | ROM Address 007                 |        |

| 3-701.  | ROM Address 010                 |        |

| 3-702.  | I/O System Reset                |        |

| 3-704.  | PON Signal                      |        |

| 3-706.  | POPIO and CRS Signals           |        |

| 3-707.  | Reset Signal                    |        |

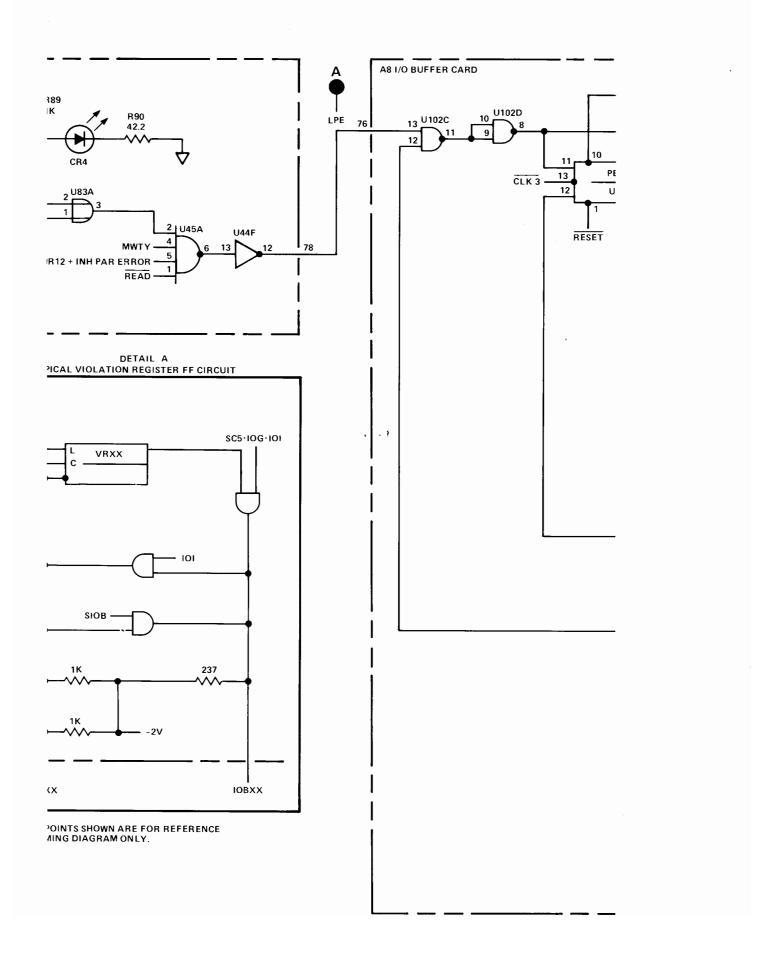

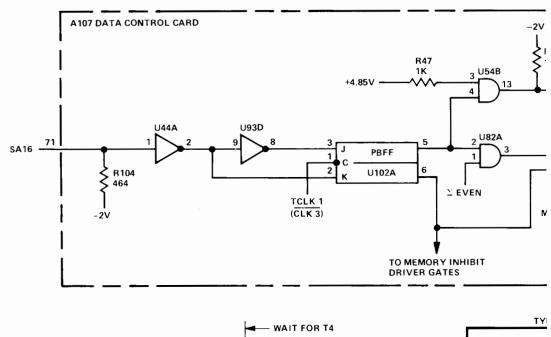

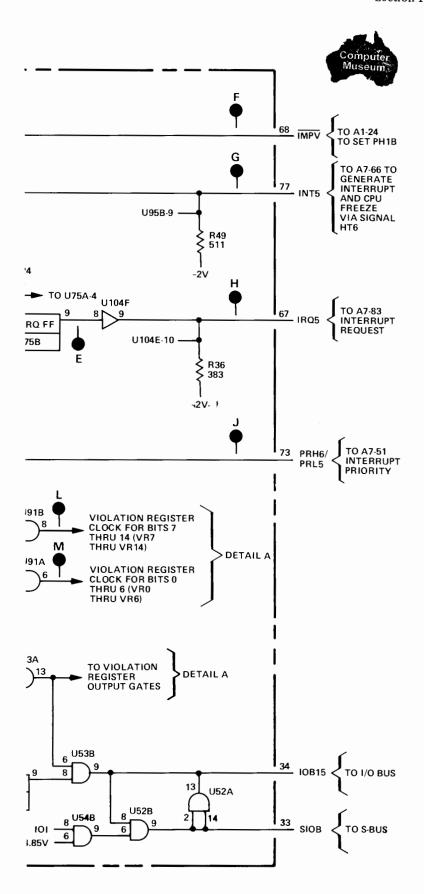

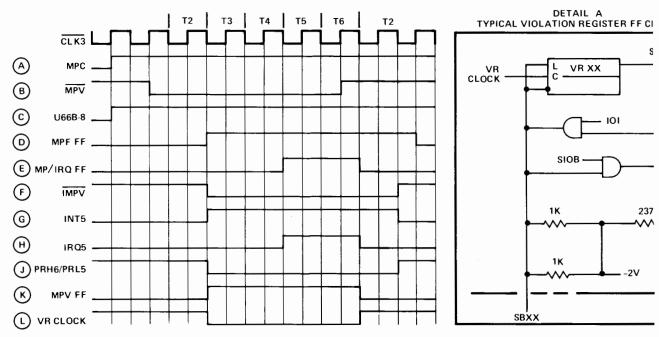

| 3-708.  | I/O Violation Circuits          | . 3-91 |

| Sect | ion            | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page         |

|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| IV   | TROUI          | BLESHOOTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

|      | 4-1.           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-1          |

|      | 4-3.           | General Servicing Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-1          |

|      | 4-5.           | Program Instruction Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-1          |

|      | 4-8.           | Loading Absolute Loader Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-1          |

|      | 4-10.          | Loading from Paper Tape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1          |

|      | 4-13.          | Loading from the Operator Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3          |

|      | 4-14.          | Diagnostic Operating Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3          |

|      | 4-15.          | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-3          |

|      | 4-16.          | Required Diagnostic Program Tapes and Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-3          |

|      | 4-18.          | Test Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-3          |

|      | 4-19.          | Error Halts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-3          |

|      | 4-20.          | Procedures for Loading Diagnostic Tapes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-5          |

|      | 4-22.          | Loading Diagnostic Tapes Using the HP 2748 Tape Reader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-5          |

|      | 4-23.          | Loading Diagnostic Tapes with the HP 2758A Reader-Reroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-6          |

|      | 4-24.          | Loading Diagnostic Tapes Using the HP 2752A Teleprinter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-7          |

|      | 4-25.          | Loading Halts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-8          |