## Operating and Service Manual HP 13192A and HP 13193A

### Write Test and Read Test Accessories

(For The Digital Magnetic Tape Unit)

Printed-Circuit Assemblies: 13192-60010, Series 1037 13192-60020, Series 1028 13192-60030, Series 1028 13193-60010, Series 1405

MANUAL PART NO. 13192-90002

Hewlett-Packard Company Post Office Box 15, Boise, Idaho, U.S.A.

## HP Computer Museum www.hpmuseum.net

For research and education purposes only.

## **Publication History**

Changes in text to document updates subsequent to the initial release are supplied in manual update notices and/or complete revisions to the manual. The history of any changes to this edition of the manual is given below. The last update itemized reflects the machine configuration documented in the manual.

Any changed pages supplied in an update package are identified by an update number adjacent to the page number. Changed information is specifically identified by a vertical line (revision bar) on the outer margin of the page.

| First Edition F   | EB 77 |

|-------------------|-------|

| Revised Edition J | UL 82 |

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

Copyright ©1982 by Hewlett-Packard Company

.

## CONTENTS

| P | a | g | 6 |

|---|---|---|---|

|---|---|---|---|

| Sectio | on     |                                               | Page  |

|--------|--------|-----------------------------------------------|-------|

| I      | GENER  | RAL INFORMATION                               |       |

|        | 1.1.   | Introduction                                  | . 1-1 |

|        | 1-3.   | Description                                   | . 1-1 |

|        | 1-9.   | Related Accessories                           | . 1-1 |

|        | 1-12.  | Related Manuals                               | . 1-1 |

|        | 1-14.  | Identification                                |       |

|        | 1.17.  | Specifications                                |       |

|        |        |                                               |       |

|        |        | LLATION                                       |       |

|        | 2-1.   | Introduction                                  |       |

|        | 2-3.   | Unpacking and Inspection                      |       |

|        | 2-6.   | Installation Preparation                      | . 2-1 |

|        | 2-10.  | Installation                                  | . 2-1 |

|        | 2-12.  | Control and Status Test PCA Installation      | . 2-1 |

|        | 2-14.  | Main Write Test PCA Installation              | . 2-1 |

|        | 2.15.  | Read Test PCA Installation                    | .2.2  |

|        | 2.16.  | Installation Check                            |       |

|        | 2-10.  |                                               |       |

| II     | OPERA  |                                               |       |

|        | 3-1.   | Introduction                                  |       |

|        | 3-5.   | Applicability                                 | . 3-1 |

|        | 3-7.   | Controls and Indicators                       | . 3-1 |

|        | 3-9.   | Write Test Accessory Operation                |       |

|        | 3-15.  | Test Pattern Programs                         | 3-7   |

|        | 3-17.  | Write Program 1 Test PCA                      |       |

|        | 3-19.  | Write Program 2 Test PCA                      |       |

|        | 3-21.  | Read Test Accessory Operation                 |       |

|        | 3-23.  | Continuous Mode                               |       |

|        | 3-25.  | Block Mode                                    | . 3-1 |

| IV     | THEOR  | RY OF OPERATION                               |       |

|        | 4-1.   | Introduction                                  | 4.1   |

|        | 4-3.   | Read-After-Write Test Functional Description  |       |

|        | 4.5.   | Error-Display Reset Time                      |       |

|        | 4.7.   | Read-After-Write Data Time                    |       |

|        | 4.9.   | LRCC Time                                     |       |

|        | 4-9.   |                                               |       |

|        |        | Longitudinal Parity Error Display Time        |       |

|        | 4-13.  | Write Test Accessory                          |       |

|        | 4-15.  | Write Test Accessory Functional Description   |       |

|        | 4-21.  | Main Write Test Accessory Circuit Description |       |

|        | 4-33.  | Write Test Program PCAs                       | . 4-7 |

|        | 4-35.  | Read Test Accessory                           | 4-7   |

|        | 4-37.  | Vertical Parity Checks                        | . 4-8 |

|        | 4-39.  | Longitudinal Parity Checks                    | . 4.8 |

|        | 4-43.  | Read Test Accessory R/W Operation             |       |

|        | 4-55.  | Read Only Test Operation                      |       |

|        |        |                                               |       |

|        |        | ENANCE                                        |       |

|        | 5-1.   | Introduction                                  |       |

|        | 5-3    | Preventive Maintenance                        | . 5-1 |

|        | 5-5.   | Troubleshooting                               | 5-1   |

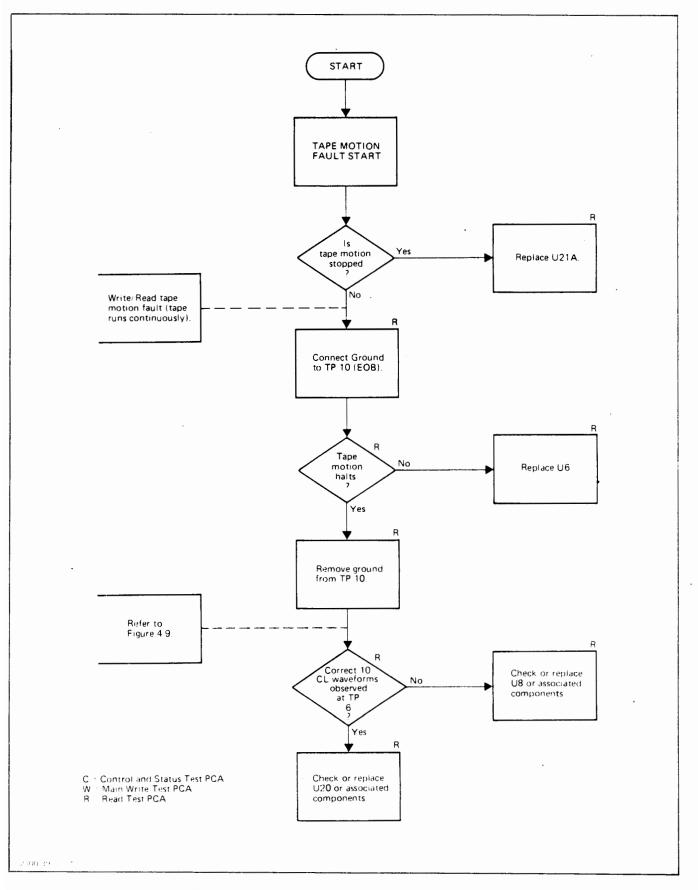

|        | 5-8.   | Troubleshooting Diagrams                      |       |

|        | 5-11.  | Parts Location and Schematic Diagrams         | . 5.1 |

| VI     | REDU V | CEABLE PARTS                                  |       |

|        | 6-1.   | Introduction                                  | G 1   |

|        | 6-3.   |                                               |       |

|        |        | Replaceable Parts List                        |       |

|        | 6-5.   | Ordering Information                          | 6-1   |

## ILLUSTRATIONS

Title

| Figure        | Title                                                                        | • ] | Page  |

|---------------|------------------------------------------------------------------------------|-----|-------|

| 1-1.          | HP 13192A Write Test Accessory and the HP 13193A Read Test Accessory         |     | 1-0   |

| 2-1.          | Test Accessory Installation                                                  |     | 2-3   |

| 2-2.          | Test Accessory Interconnection Diagram                                       |     | 2-4   |

| 3-1.          | Write Test Accessory Controls and Indicator                                  |     | 3-3   |

| 3-2.          | Read Test Accessory Controls and Indicators                                  |     | 3-4   |

| 3-3.          | Block Length Adjustment Waveforms                                            |     | 3-6   |

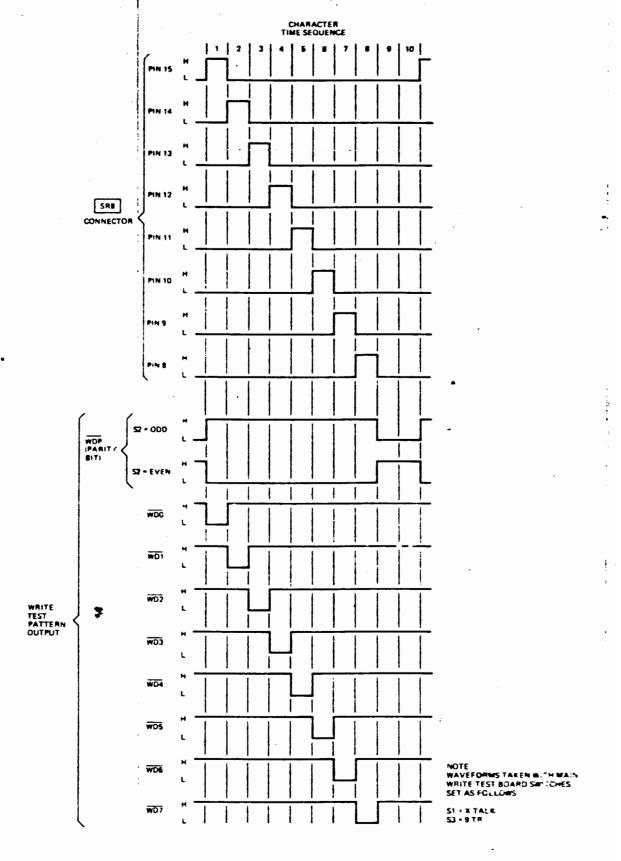

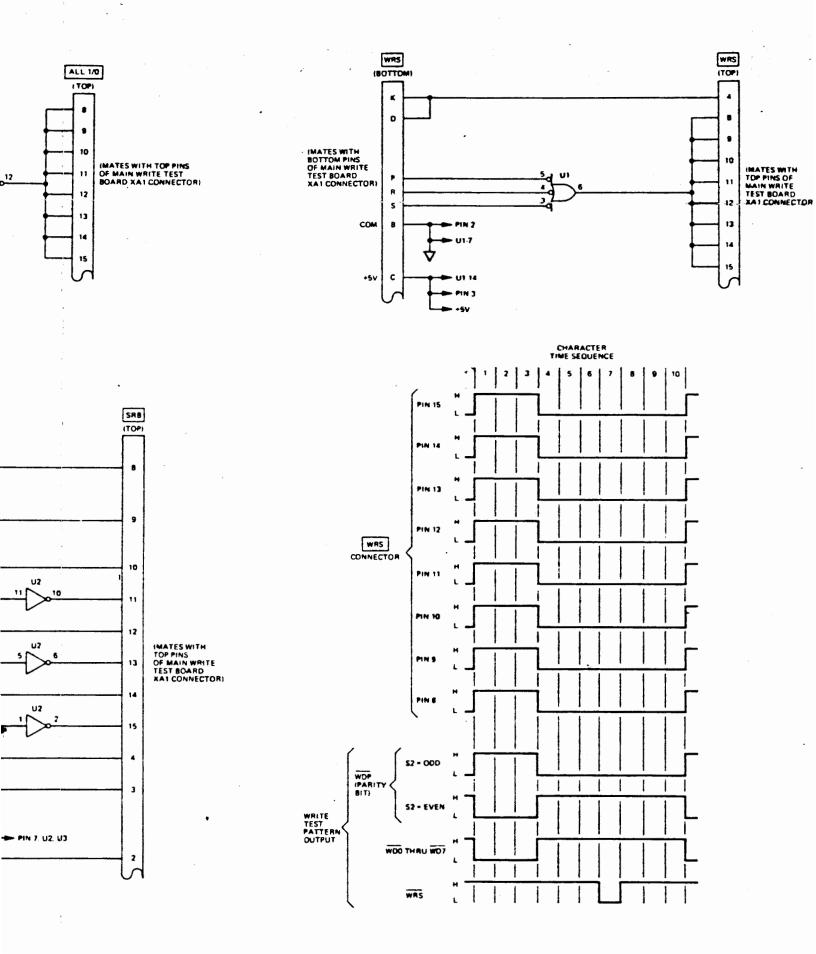

| 3-4.          | Write Test Accessory Data Program 1 Output Pattern                           |     | 3-8   |

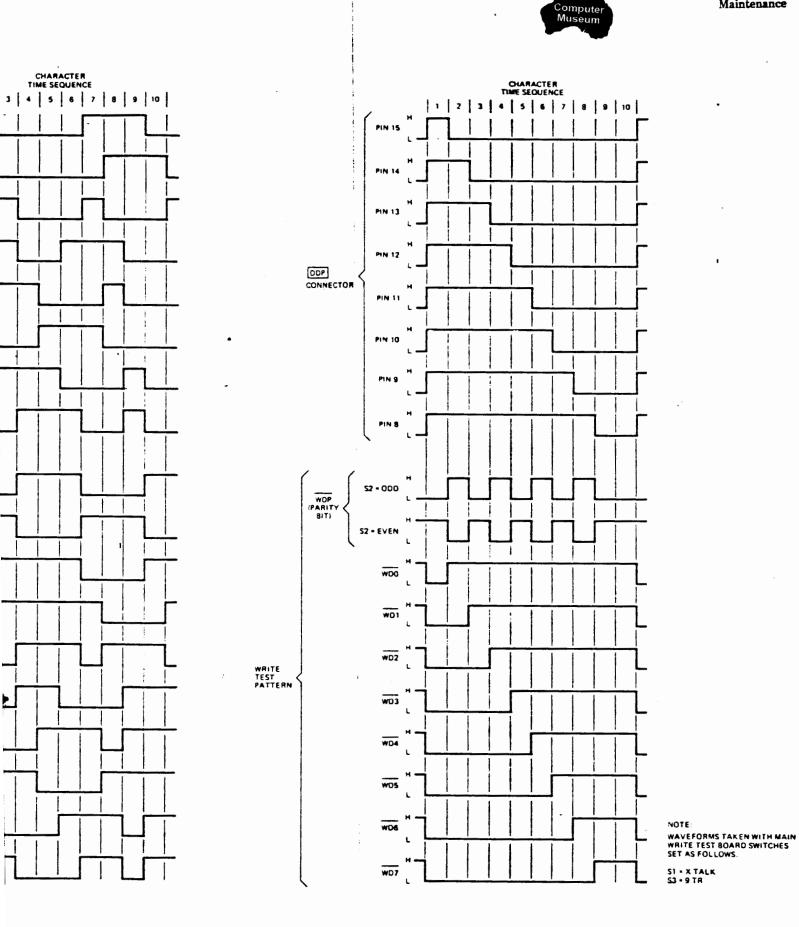

| 3-5.          | Write Test Accessory Data Program 2 Output Pattern                           |     | 3-8   |

| 3-6.          | 10 CL Gate Signal (TP6)                                                      |     | 3-9   |

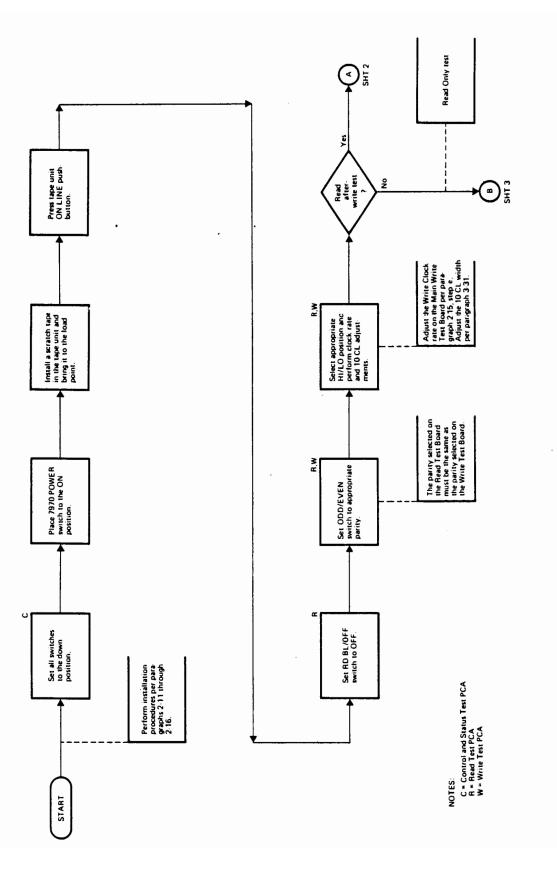

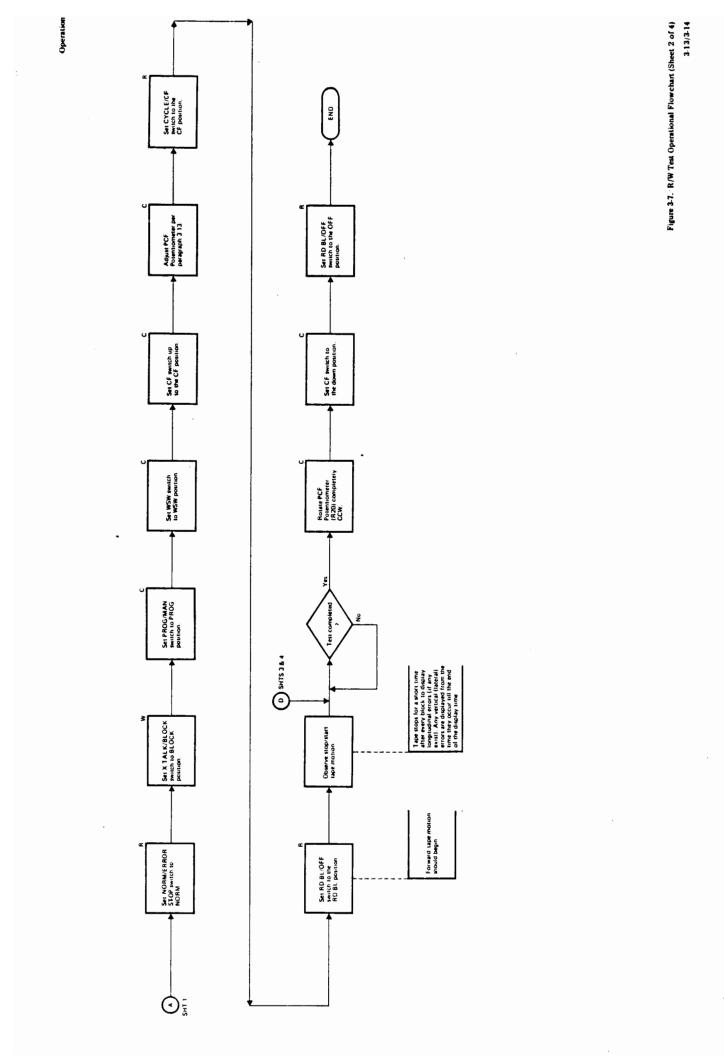

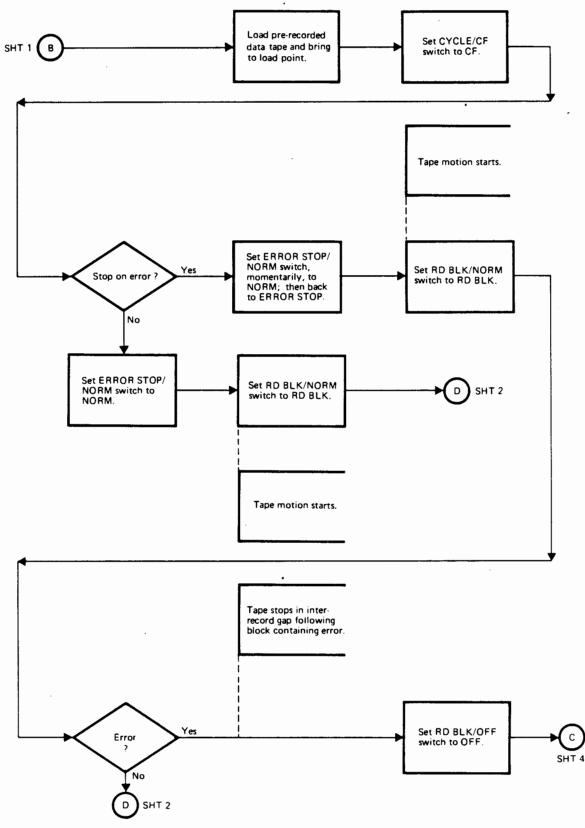

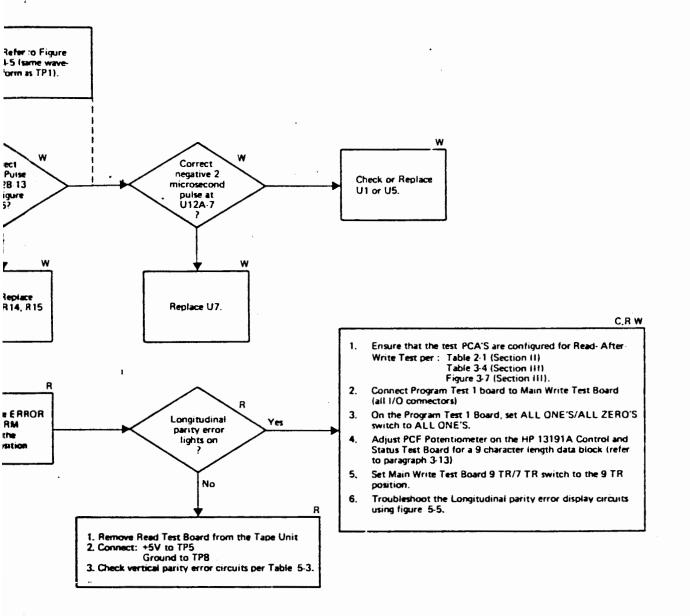

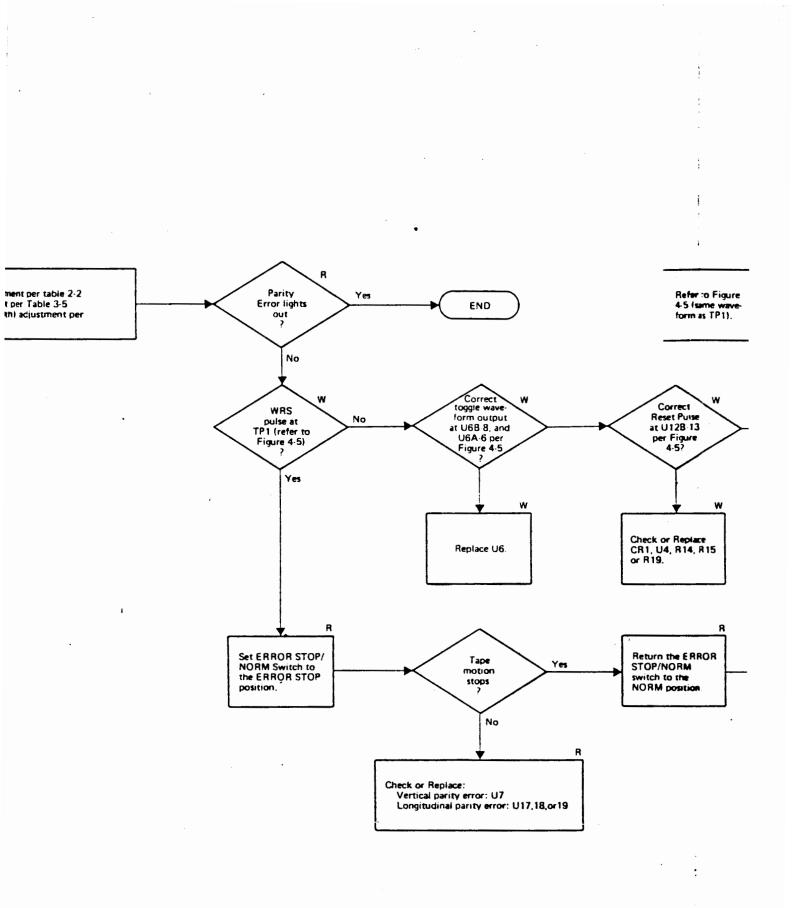

| 3-7.          | R/W Test Operational Flowchart                                               | . : | 3-11  |

| 4-1.          | R/W Test Functional Diagram                                                  |     | 4-2   |

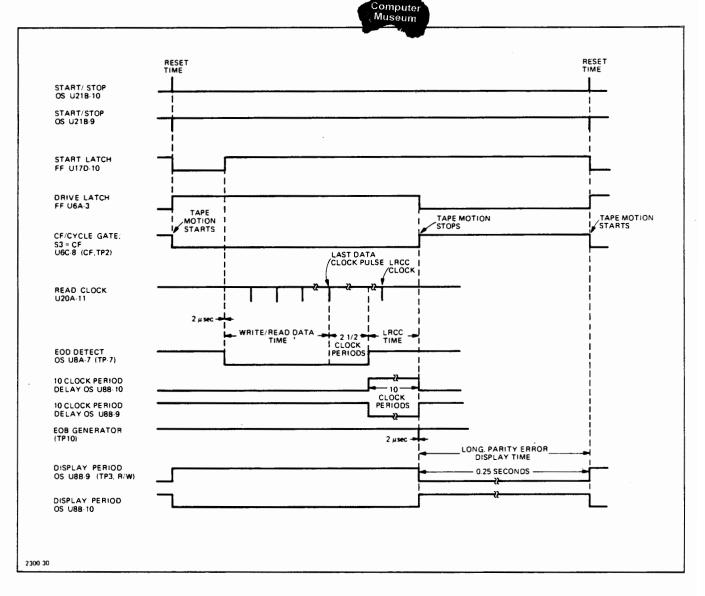

| 4-2.          | R/W Test Timing Diagram                                                      |     | 4-2   |

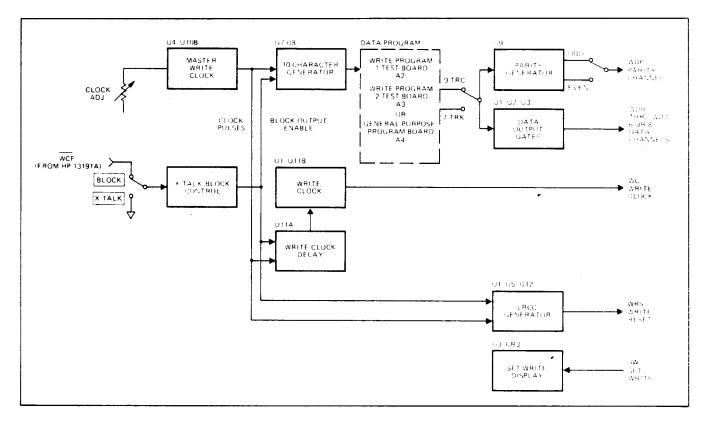

| 4-3.          | Write Test Accessory Simplified Logic Diagram                                |     | 4-3   |

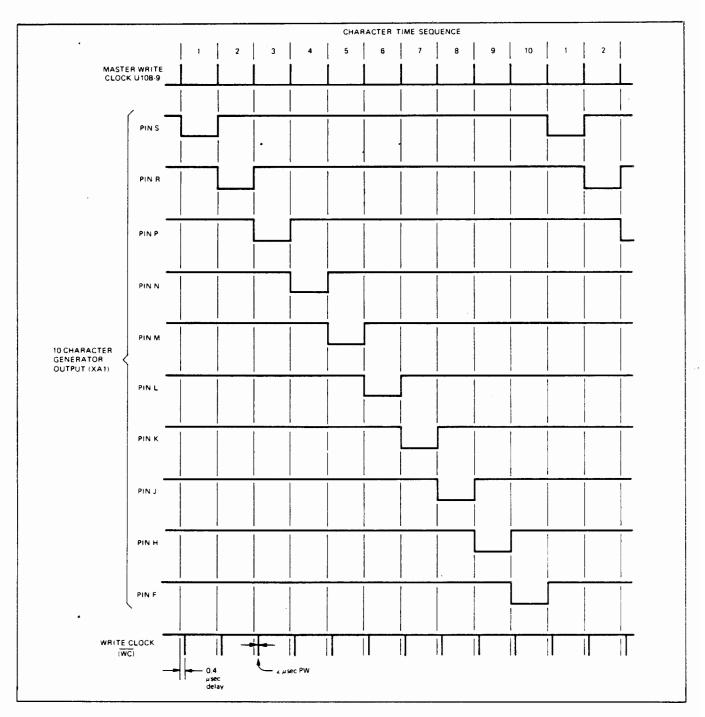

| 4-4.          | Ten-Character Generator and Write Clock (WC) Output in the X TALK            |     |       |

|               | (Continuous) Mode                                                            |     | . 4-5 |

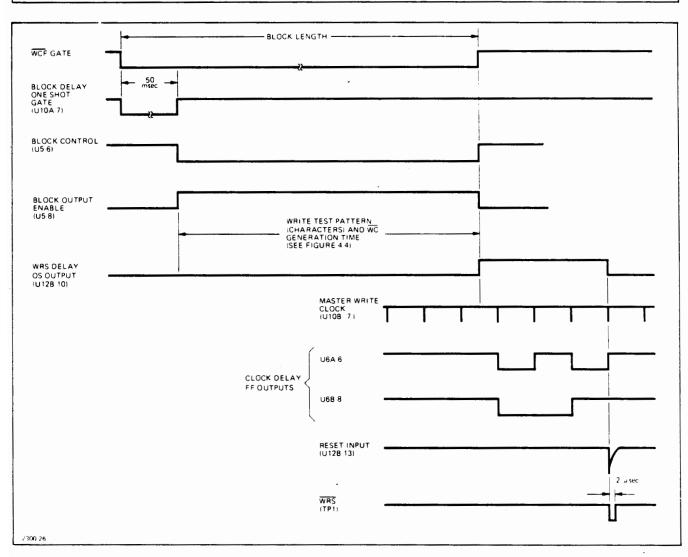

| 4-5.          | Write Test Waveforms (Block Mode)                                            |     | 4.6   |

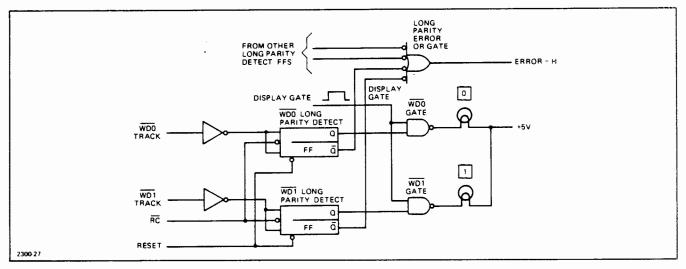

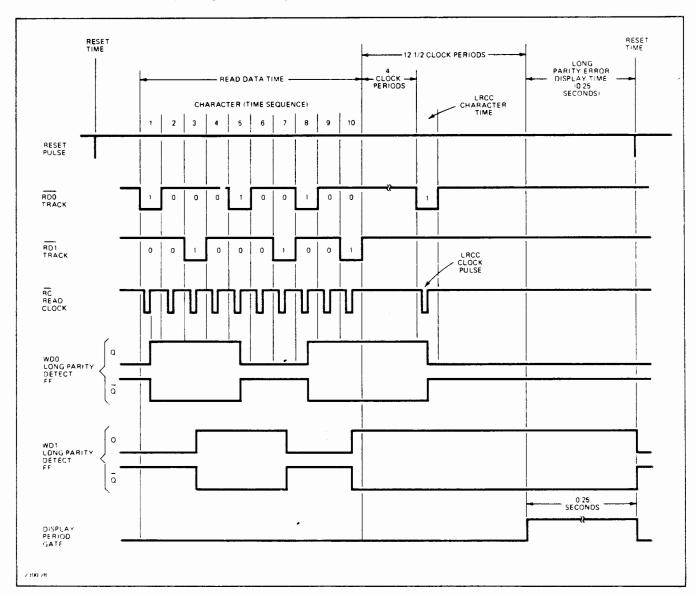

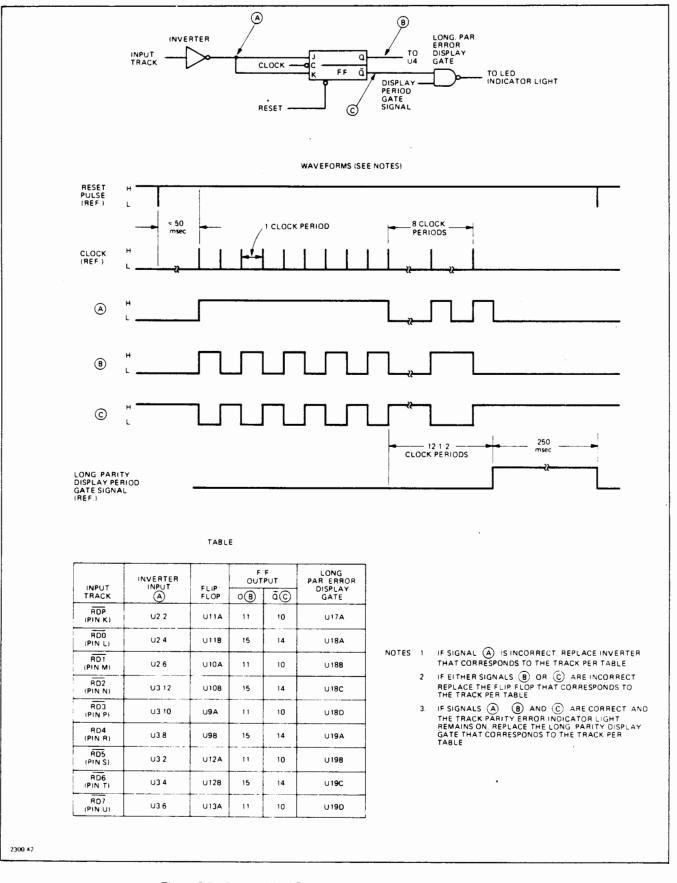

| 4-6.          | Simplified Longitudinal Parity Error Circuits                                |     | . 4-9 |

| 4-7.          | Longitudinal Parity Check Waveforms                                          |     | . 4-9 |

| 4-8.          | Read Test PCA Functional Diagram                                             | . ' | 4-11  |

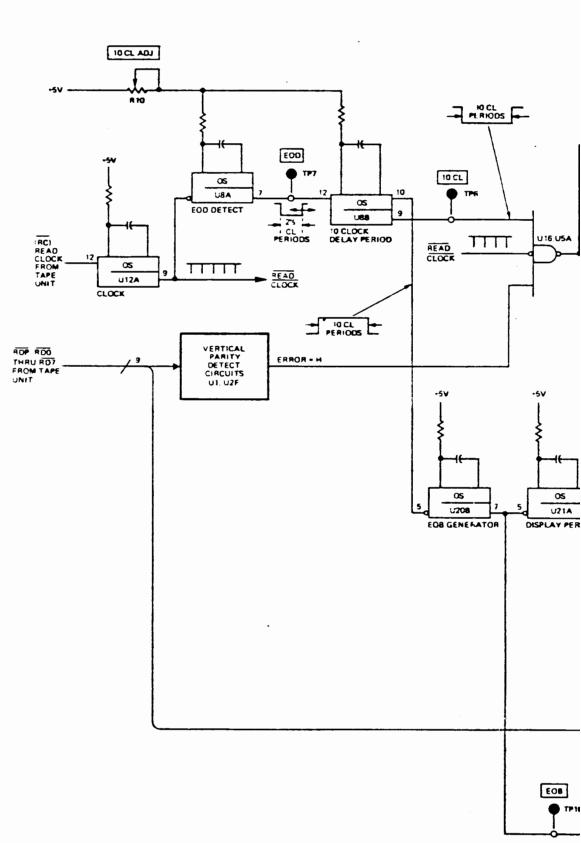

| <b>4-9</b> .  | Read Test PCA R/W Waveforms                                                  |     | 4-13  |

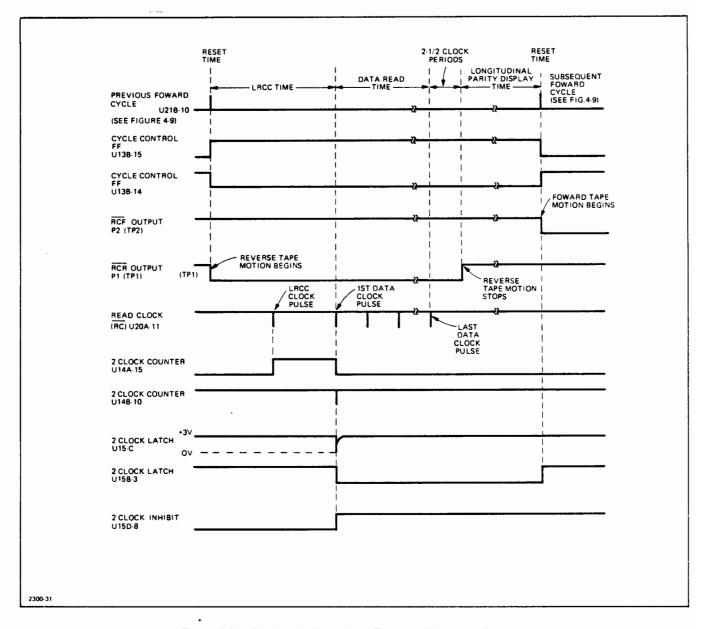

| 4-10.         | Read-Only Test, Cycle Function Waveform Diagram                              |     | 4-15  |

| 5-1.          | Tape Motion Fault Troubleshooting Diagram                                    |     | . 5-2 |

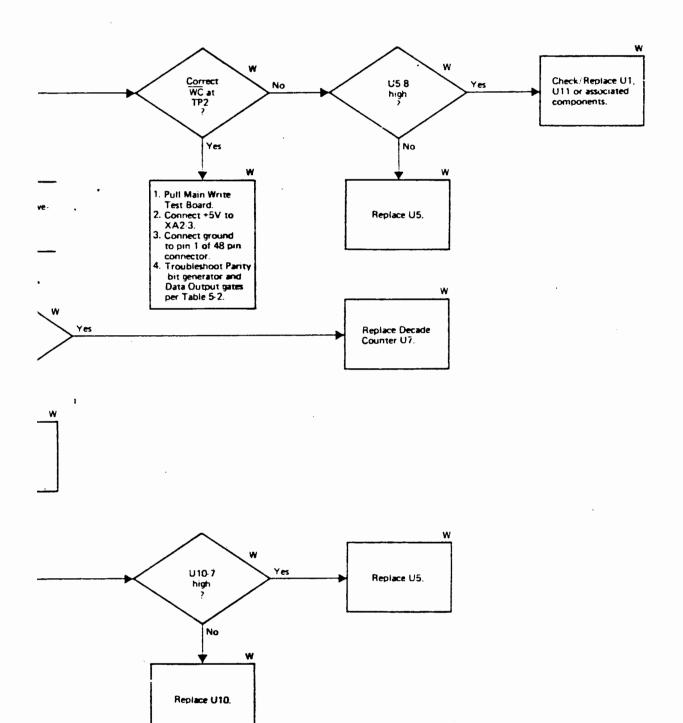

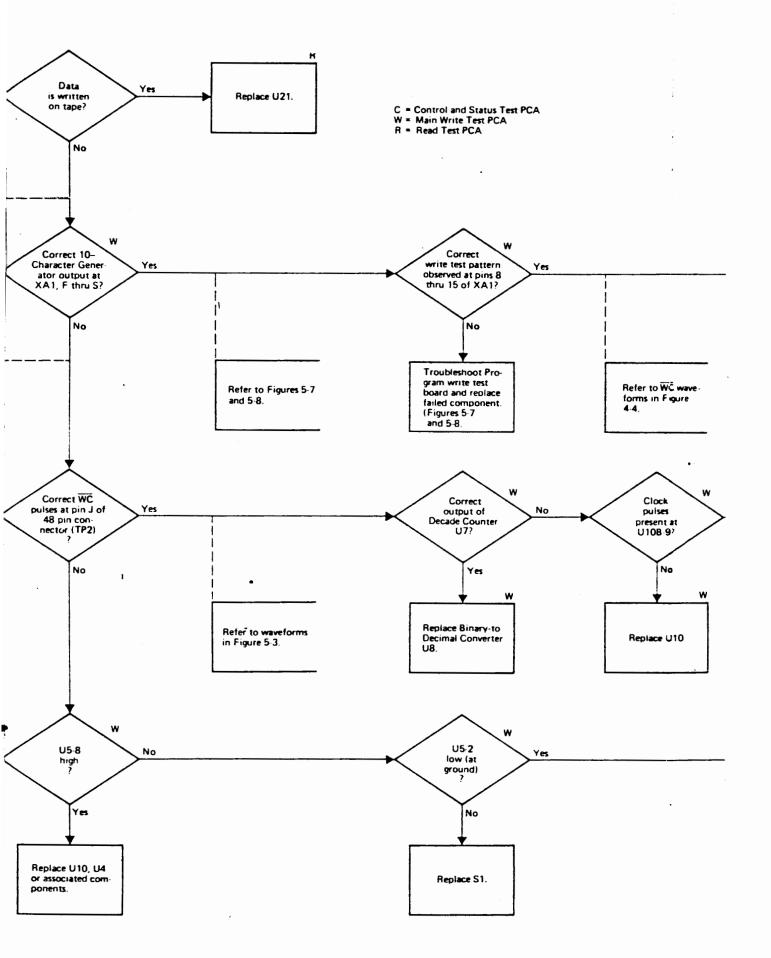

| 5-2.          | Write Data Fault Troubleshooting Diagram                                     |     | . 5-3 |

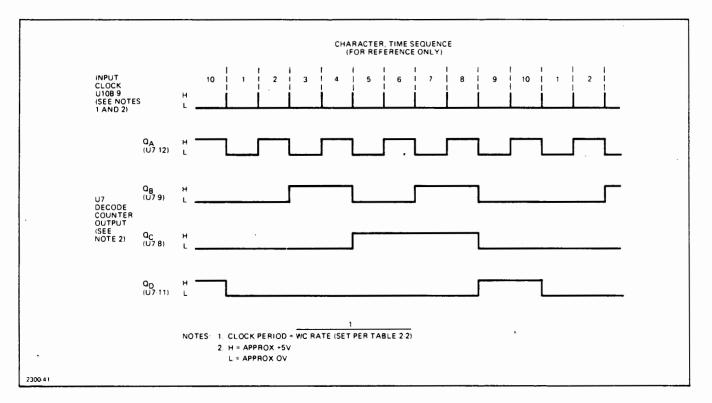

| 5-3.          | Decade Counter Waveform                                                      |     | . 5-5 |

| 5-4.          | False Parity Error Indication Troubleshooting Diagram                        |     | . 5-7 |

| 5-5.          | Longitudinal Parity Circuit Troubleshooting Diagram                          | -   | . 5-9 |

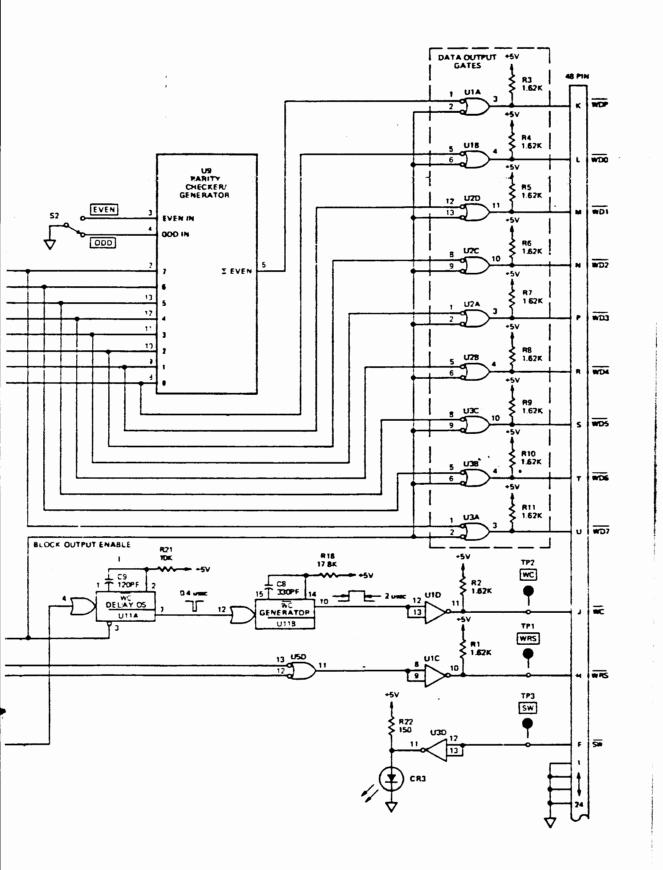

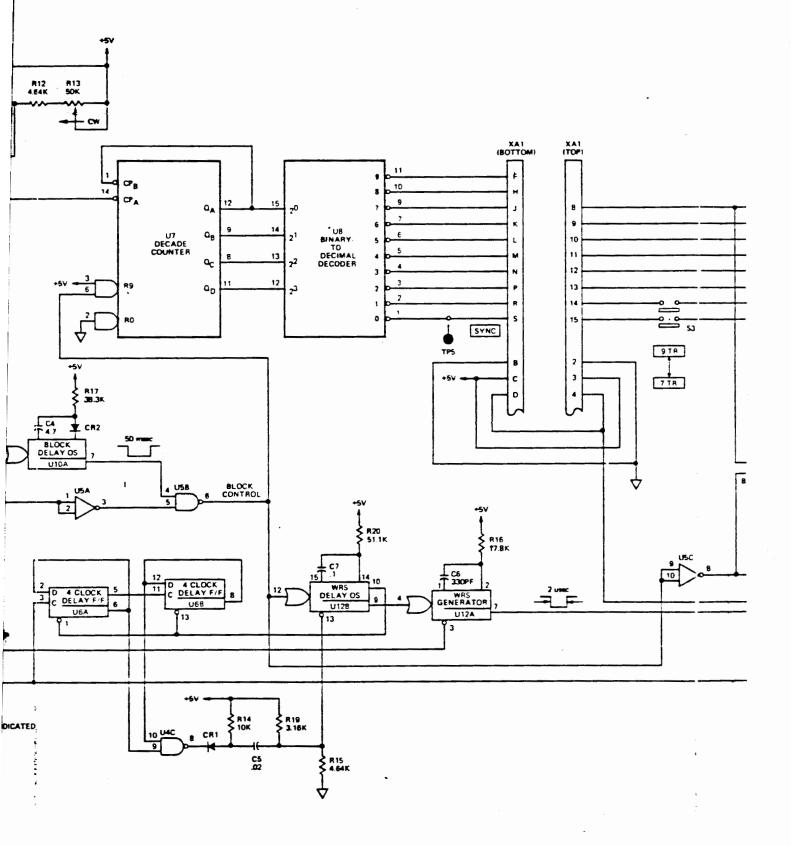

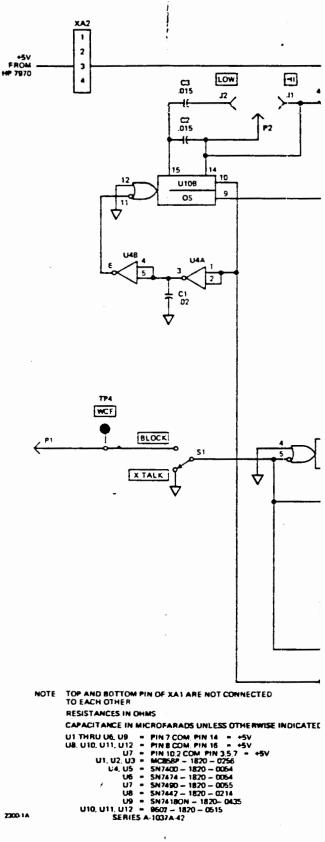

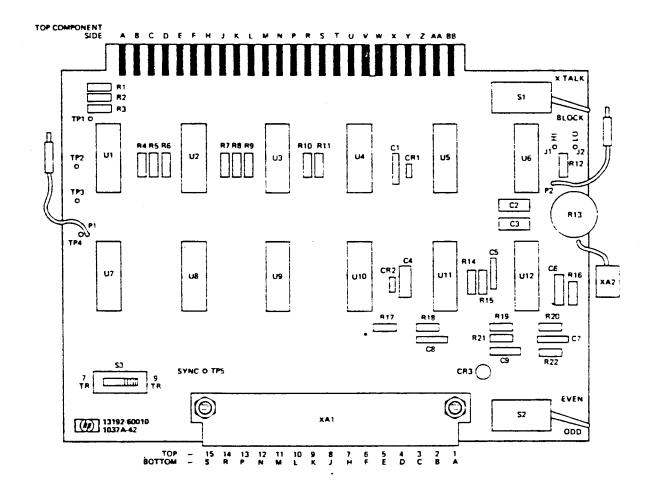

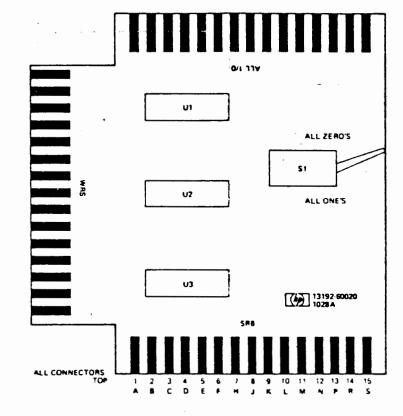

| 5 <b>-6</b> . | Main Write Test Board (A1) Component Location Diagram, Signal Summary Table, |     |       |

|               | and Schematic Diagram                                                        | •   | 5-11  |

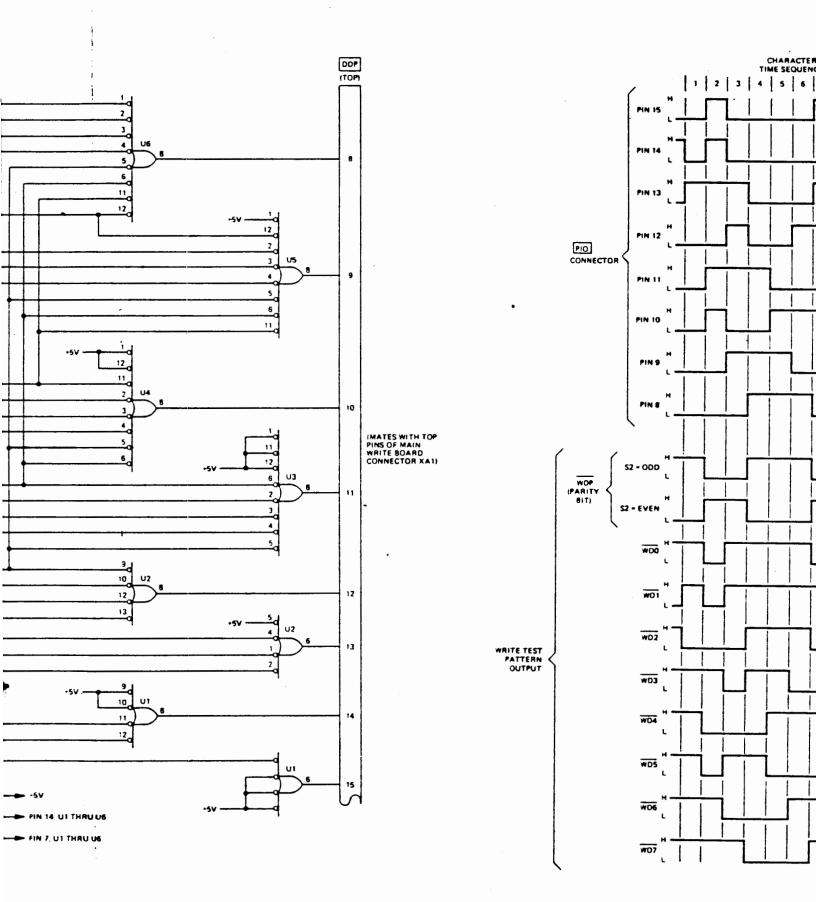

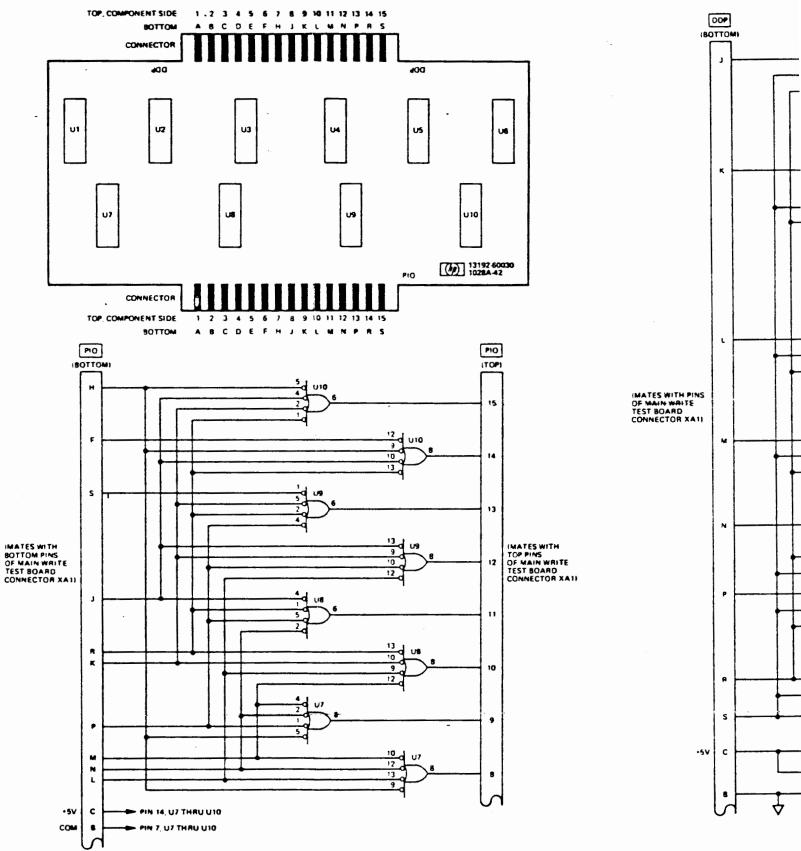

| 5-7.          | Write Program 1 Test Board (A2) Parts Location, Schematic, and               | •   |       |

|               | Waveform Diagrams                                                            |     | 5-13  |

| 5-8.          | Write Program 2 Test Board (A3) Parts Location, Schematic, and               |     | E 1 F |

|               | Waveform Diagrams                                                            | •   | 2-12  |

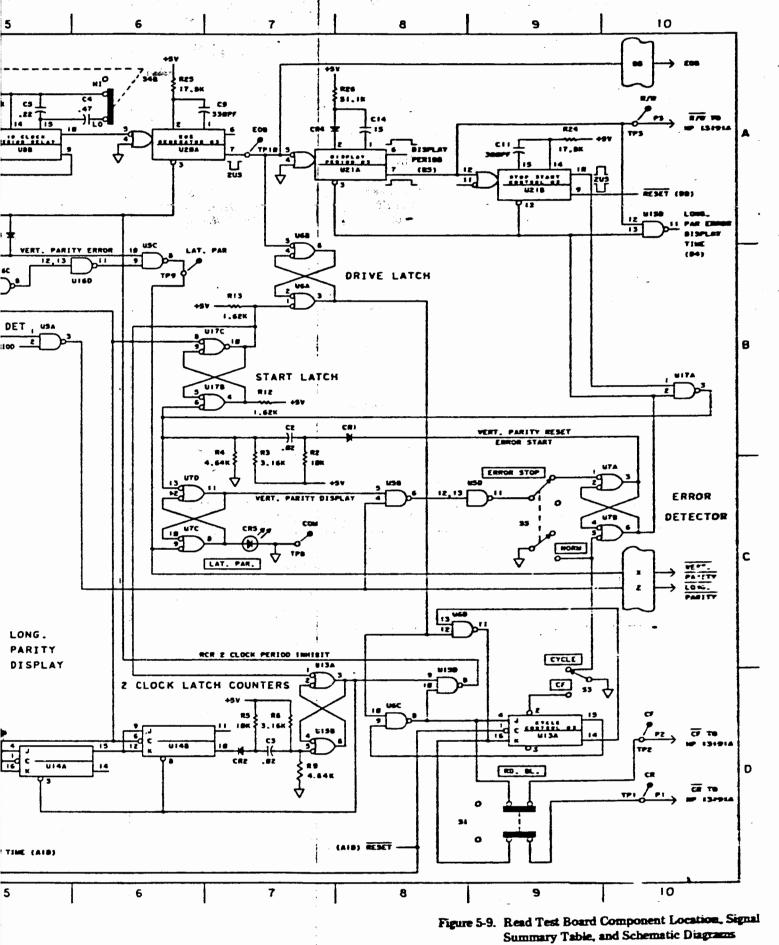

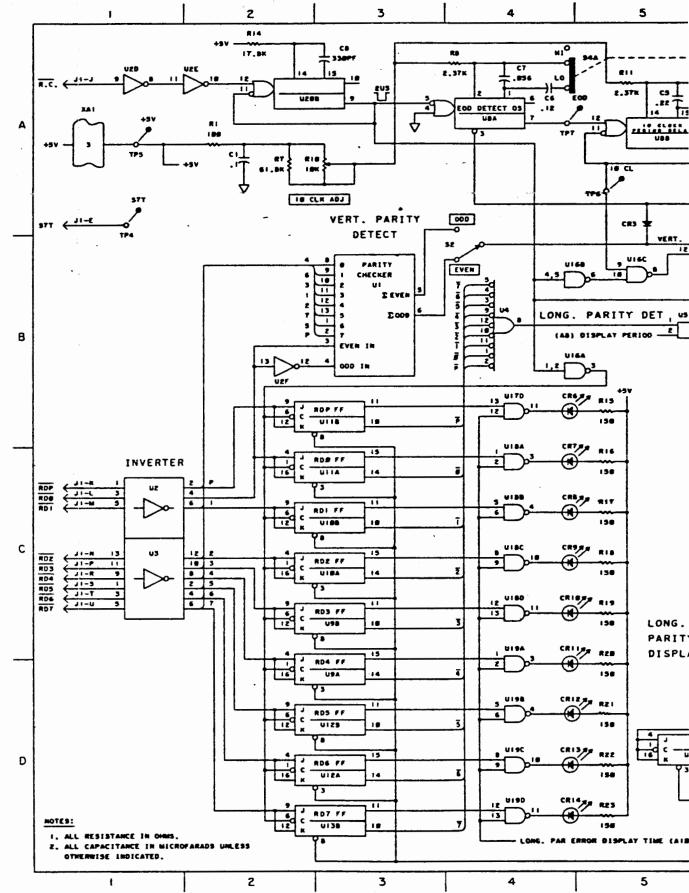

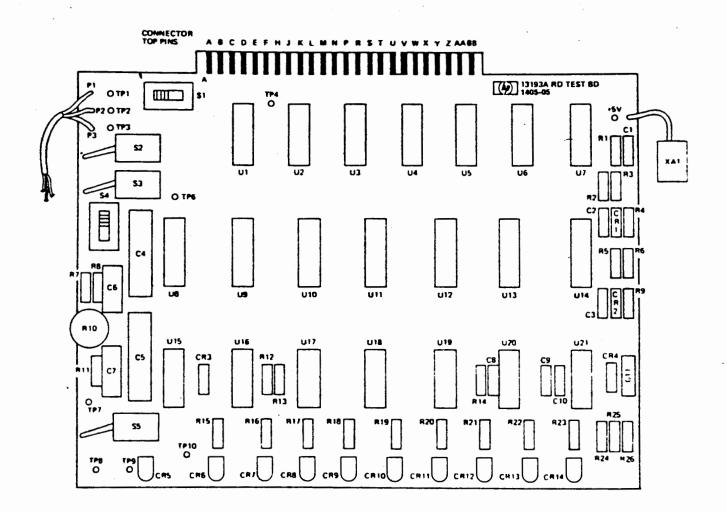

| 5-9.          | Read Test Board Component Location, Signal Summary Table and                 |     | - 1-  |

|               | Schematic Diagrams                                                           |     | 2-1/  |

٠

.

## TABLES

| Table        | Title                                               | Page  |

|--------------|-----------------------------------------------------|-------|

| 1-1.         | Write Test Accessory Specifications                 | . 1-2 |

| 1.2.         | Read Test Accessory Specifications                  | . 1-3 |

| 2-1.         | Test PCA Signal-Jumper Connections                  | . 2.2 |

| <b>2</b> -2. | Main Write Test PCA Clock Rate Adjustment (800 bpi) | . 2-3 |

| 3-1.         | Test PCA Applications                               | . 3-2 |

| 3-2.         | Write Test Accessory Controls and Indicator         | . 3-5 |

| 3-3.         | Read Test Accessory Controls and Indicators         | . 3-5 |

| 3-4.         | Initial Test Accessory Switch Settings              | . 3-6 |

| 3-5.         | Read Test PCA 10 Clock Width Adjustment (800 bpi)   | . 3-9 |

| 4-1.         | U7 Binary Command Outputs                           | . 4-4 |

| 4-2.         | Parity Bit Generation                               | . 4-6 |

| 4-3.         | Write Test Program PCA's                            | . 4-7 |

| 4-4.         | Vertical (Lateral) Parity Check Function            | . 4-8 |

| 5-1.         | Troubleshooting Diagrams Index                      |       |

| 5-2.         | Parity Generator/Output Data Gate Check             |       |

| 5-3.         | Vertical (LAT PAR) Parity Error Circuit Checks      |       |

| 6-1.         | Test Accessory Parts List                           |       |

| 6-2.         | Main Write Test PCA (A1) Parts List                 |       |

| 6-3.         | Write Program 1 Test PCA (A2) Parts List            |       |

| 6-4.         | Write Program 2 Test PCA (A3) Parts List            |       |

| 6-5.         | HP 13193A Read Test PCA Parts List                  |       |

| 6-6.         | Code List of Manufacturers                          |       |

| 6-7.         | List of Reference Designations and Abbreviations    |       |

.

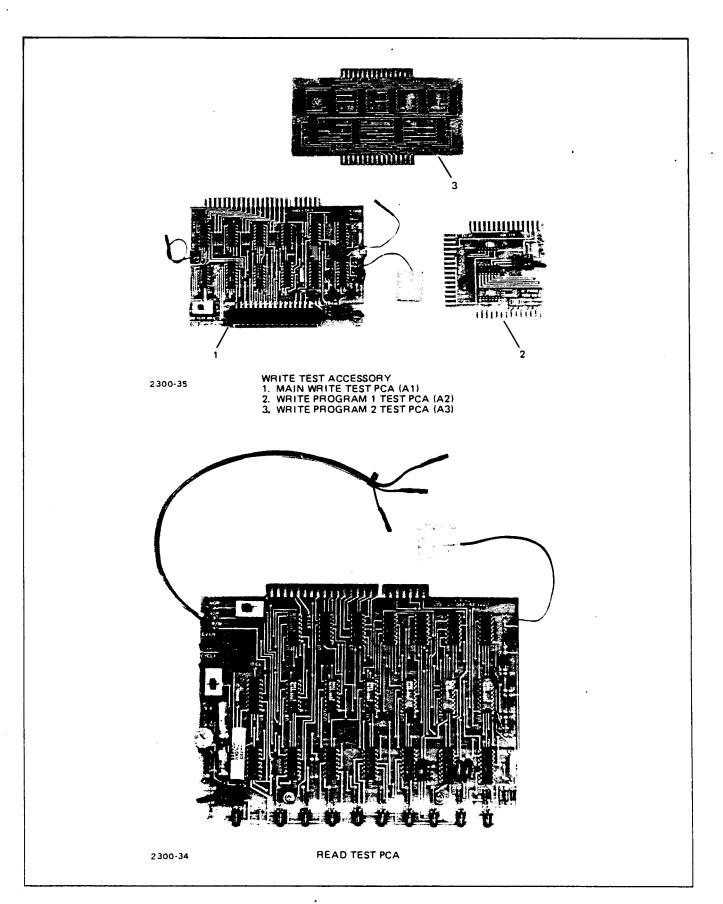

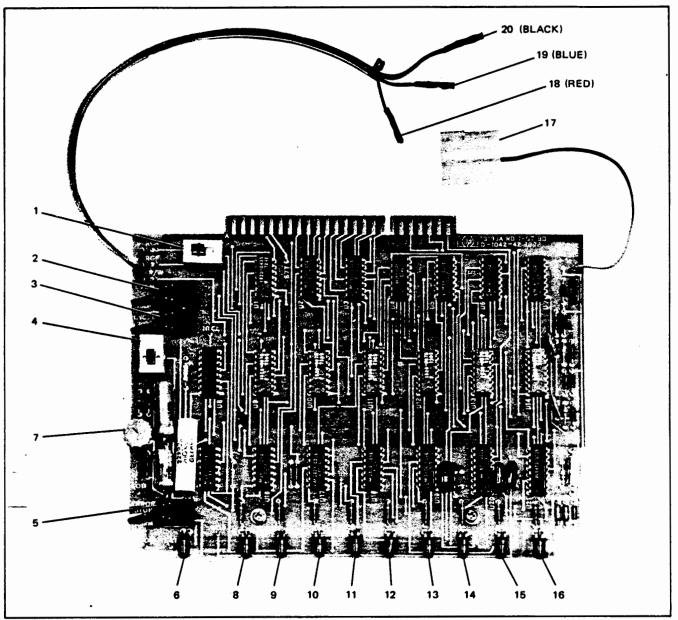

Figure 1-1. HP 13192A Write Test Accessory and HP 13193A Read Test Accessory

#### 1-1. INTRODUCTION.

1-2. This operating and service manual provides general information, installation, operation, theory of operation, and maintenance information for the HP 13192A Write Test Accessory and the HP 13193A Read Test Accessory.

#### 1-3. DESCRIPTION.

1-4. The read test accessory and the write test accessory, in conjunction with related test accessories, provide the means to exercise the write and read capability of HP 7970 Series Digital Magnetic Tape Units that record in non-return-to-zero, inverted (NRZI) format in an off-line environment.

1-5. The HP 13192A Write Test Accessory consists of three printed-circuit assemblies (PCA's) as shown in figure 1-1. The main write test PCA, part no. 13192-60010, plugs directly into a connector on the tape unit write assembly motherboard. Write program 1 and write program 2 PCA's are capable of providing one of five pre-programmed, 10-character write test patterns when plugged into the main write test PCA. There is also a custom-programmed general purpose test PCA, which is available, as an option, to the user who desires his own test pattern.

1-6. In addition to the 10 characters, the write test accessory provides either even or odd parity, initiates a longitudinal redundancy check character (LRCC), and generates a variable-rate write clock (WC). The write clock rate is adjustable to cover magnetic tape recording densities of 200 to 800 bits per inch, (bpi) over a tape speed range of 10-to-45 inches per second (ips). The write test data can be generated in a continuous format for cross-talk (X TALK) checks, or in an interrupted (BLOCK) format. A write status (SW) indicator on the main write test PCA is turned on when write- and erase-head current is established in the tape unit.

1-7. The HP 13193A Read Test Accessory (see figure 1-1) plugs directly into the read assembly motherboard of the tape unit. The read test PCA has several modes of operation to read parity errors when reading data previously written on magnetic tape.

1-8. Both the write test accessory and the read test PCA use TTL and DTL integrated circuits. The write test PCA's derive +5 volts operating power from the tape unit write assembly. The tape unit read assembly also provides 5-volt operating power for the read test PCA.

#### 1-9. RELATED ACCESSORIES.

1-10. There are two related test accessories that are used with the write test accessory and the read test accessory:

a. HP 13191A Control and Status Test Accessory.

b. "Scratch" Tape.

1-11. The control and status test PCA is a requirement for both read and write tests. The "scratch" tape is used when a write, or read-after-write (R/W) test function is being performed.

#### 1-12. RELATED MANUALS.

1-13. The following manuals contain information which is pertinent to the use of the write test accessory and the read test accessory:

- a. HP 13191A Control and Status Test Accessory Operating and Service Manual, part number 13191-90000.

- b. HP 7970A Digital Magnetic Tape Unit Operating and Service Manual, part number 07970-90620.

- c. HP 7970B/C Digital Magnetic Tape Unit Operating and Service Manual, part number 07970-90383.

- d. HP 7970E Digital Magnetic Tape Unit Operating and Service Manual, part number 07970-90765.

#### 1-14. IDENTIFICATION.

1-15. Hewlett-Packard uses five digits and a letter (00000A) for standard accessory identification designations. If the designation of your accessory does not agree with that on the title page of this manual, there are differences between your accessory kit and the kit described in this manual. These differences are described in change sheets and manual supplements that are available at the nearest HP Sales and Service Office. These offices are listed in the back of this manual.

1-16. Printed-circuit assembly revisions are identified by a letter, series code, and a division code stamped on the PCA (e.g. A-1152-22). The letter code identifies the version of the etched trace pattern on the unloaded board. The series code (four middle digits) refers to the 'electrical characteristics of the loaded assembly and the positions of the components. The division code (last two digits) identifies the Hewlett-Packard division which manufactured the PCA. If the series code stamped on the PCA does not agree with the series code shown on the schematic diagram in this manual, there are differences between the PCA and the PCA described in this manual. These differences are described in change sheets and manual supplements that are available at the nearest HP Sales and Service Office.

#### 1-17. SPECIFICATIONS.

1-18. Specifications for the HP 13192A Write Test Accessory are listed in table 1-1. Specifications for the Read Test Accessory are listed in table 1-2.

#### Table 1-1. Write Test Accessory Specifications

| SIZE                                                                                      |                           |                                                                                 |

|-------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------|

| HP 13192-60010 Main Write T<br>HP 13192-60020 Write Progra<br>HP 13192-60030 Write Progra | m 1 Test PCA Board:       | 5-11/16 by 4-5/16 inches<br>3-5/16 by 3-5/16 inches<br>5-11/16 by 3-5/16 inches |

| SHIPPING WEIGHT                                                                           |                           |                                                                                 |

| 4 lbs net                                                                                 |                           |                                                                                 |

|                                                                                           | d by tape unit)           |                                                                                 |

| +5 volts dc @ 400 ma maximu                                                               | m                         |                                                                                 |

| LOGIC LEVELS (negative logic)                                                             |                           |                                                                                 |

| TTL:                                                                                      |                           |                                                                                 |

| Assertion (Logic 1) is le                                                                 | ss than, or equal to +0.8 | SV (7.8 ma @ +0.4V)                                                             |

| Negation (Logic 0) is gre                                                                 | eater than, or equal to + | 2.0V (1.55 ma @ +2.4V)                                                          |

| DTL:                                                                                      |                           |                                                                                 |

| Assertion (Logic 1) is le                                                                 | ss than, or equal to +0.4 | V (33.ma @ +0.4V)                                                               |

| Negation (Logic 0) is gre                                                                 | eater than, or equal to + | 2.4V (1.5 ma @ +2.4V)                                                           |

| WRITE DATA:                                                                               |                           |                                                                                 |

| TAPE DENSITY:                                                                             | 200 to 800 bpi            |                                                                                 |

| TAPE SPEED:                                                                               | 10 to 45 ips              |                                                                                 |

| Seven- or nine-track tape data                                                            | test capability           |                                                                                 |

| DATA PARITY:                                                                              | Odd or even               |                                                                                 |

| RECORDING FORMATS:                                                                        | 6 Standard write pat      | tern programs                                                                   |

|                                                                                           | 1 optional custom w       | rite pattern program                                                            |

| OPERATING MODES:                                                                          | Continuous                |                                                                                 |

|                                                                                           | Block                     |                                                                                 |

|                                                                                           |                           |                                                                                 |

#### SIZE

5-13/16 by 7-1/2 inches

#### SHIPPING WEIGHT

3 lbs net

#### POWER REQUIREMENTS

+5 volts dc @ 300 ma (supplied by tape unit)

#### LOGIC LEVELS (negative Logic)

TTL:

Assertion (Logic 1) is less than, or equal to +0.8V (7.8 ma @ +0.4V)

Negation (Logic 0) is greater than, or equal to +2.0V (1.55 ma@+1.4V)

DTL:

Assertion (Logic 1) is less than, or equal to +0.4V (33 ma@+0.4V) Negation (Logic 0) is greater than, or equal to +2.4V (1.5 ma @ +2.4V)

#### **READ DATA:**

| TAPE DENSITY:     | 200 to 800 bp                                                            |

|-------------------|--------------------------------------------------------------------------|

| TAPE SPEED:       | 10 to 45 ips<br>seven- or nine-track tape test capability                |

| PARITY DETECTION: | Odd or even, vertical (lateral) and longitudinal                         |

| OPERATING MODES:  | Continuous<br>Block<br>Cycle (Alternate forward and reverse tape motion) |

EQUIPMENT COMPATIBILITY: HP 7970A, HP 7970B/C Digital Magnetic Unit

, . .•

#### 2-1. INTRODUCTION.

2-2. The HP 13192A Write Test Accessory and the HP 13193A Read Test Accessory are factory-checked to assure performance to the published specifications before being packed for shipment. This section provides information to determine that these test accessories have been received intact. Installation instructions for these test accessories and other associated tape unit accessory connections are included. Initial plug and jumper connections, as well as tape unit compatibility adjustments for the test PCA's are included in this section.

#### 2-3. UNPACKING AND INSPECTION.

2-4. Before unpacking, inspect the shipping carton for damage. If damage to the shipping carton is evident, request that the carrier's shipping agent be present when the accessories are unpacked. After unpacking, inspect the accessories for mechanical damage (cracks, broken parts, etc).

2-5. If any PCA is damaged, and fails to meet the published specification, notify the carrier and the nearest Hewlett-Packard Sales and Service Office immediately. (HP Sales and Service Offices are listed at 'the back of this manual.) Retain the shipping container and the packing materials for the carrier's inspection. The Hewlett-Packard Sales and Service Office will arrange for the repair or replacement of the damaged PCA without waiting for any claims against the carrier to be settled.

#### 2-6. INSTALLATION PREPARATION.

2-7. Turn off power on the tape unit to be tested (the master tape unit in a master-slave multi-unit application) and take the tape unit physically off-line by removing the computer interface connector cables.

2-8. Installation of the HP 13191A Control and Status Test Accessory is required for operating the HP 13192A Write Test Accessory and the HP 13193A Read Test Accessory. The procedure for installing the control and status test PCA is described in the HP 13191A manual. A part of the control and status test accessory operating and installation procedures is repeated in this manual for convenience.

2-9. For performing a write/read test on read-afterwrite tape units, install a "scratch" tape with a write enable ring inserted. (Inspect the tape pack for damage. Do not use tape that shows signs of abuse.) For testing read-only tape units, install a pre-recorded test tape.

#### 2-10. INSTALLATION.

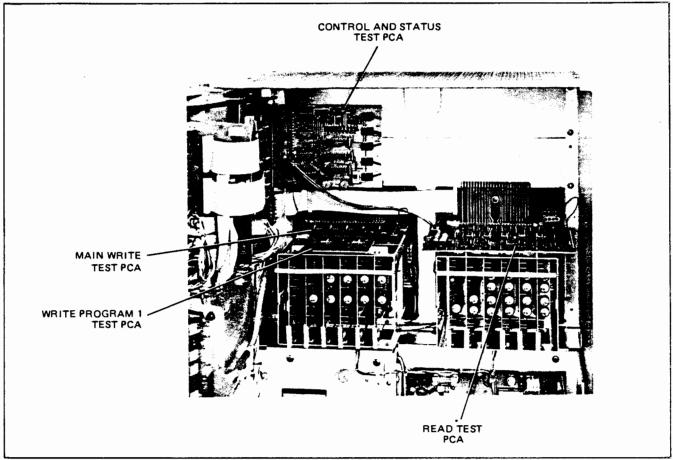

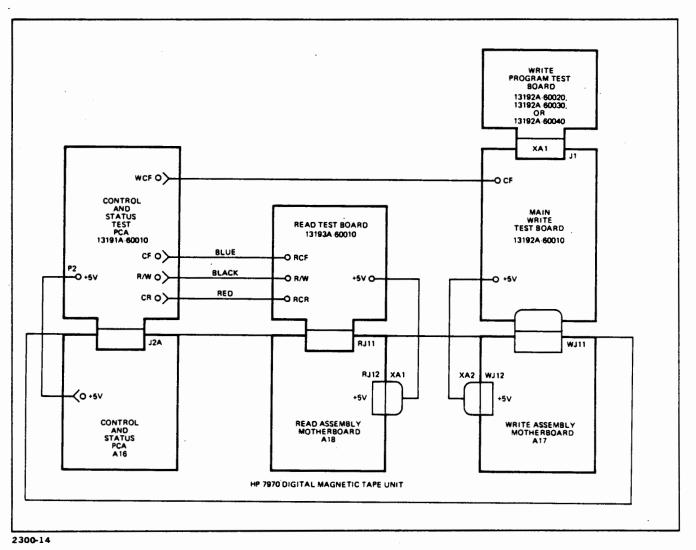

2-11. Installing the HP 13192A Write Test Accessory, the HP 13193A Read Test Accessory, and the HP 13191A Control and Status Test Accessory consists of plugging these boards into the tape unit write assembly, read assembly, and control and status PCA, respectively. Table 2-1 lists the signal-jumper connections that are required for the six basic test operations performed with these test accessories. Figure 2-1 shows the test PCA's installed. Figure 2-2 provides an overall installation and interconnection diagram. Paragraphs 2-12 through 2-14 describe the individual test PCA installations in detail. The write clock (WC) adjustment indicated in paragraph 2-14 must be performed whenever the write test accessory is used.

2-12. CONTROL AND STATUS TEST PCA INSTAL-LATION.

2-13. The following steps are always performed when using the control and status PCA. Other connections and switch positions are according to the particular test function.

- a. Plug the HP 13191A Control and Status Test PCA (component side forward) into J2A of the tape unit control and status PCA (A16), as shown in figure 2-1. Do not force the PCA, a keying slot prevents installation if the board is being inserted incorrectly.

- b. Connect the control and status PCA +5V jumper P2 to the +5V pin of the tape unit control and status PCA (A16) as shown in figure 2-2.

- c. Observe the position of the CS (unit address select) jumper on the tape unit A16 PCA. On the control and status test PCA, connect jumper P1 to the CS pin (i.e. OFF, CS0, CS1, CS2, or CS3) that corresponds to the position of the CS jumper on the tape unit A16 PCA. If the optional tape unit front panel unit address select switches are installed, the test PCA and jumper P1 tape unit A16 CS jumper should be in the OFF position.

#### 2-14. MAIN WRITE TEST PCA INSTALLATION.

- a. Plug the main write test PCA (component side into WJ11 of the tape unit write assembly motherboard, as shown in figure 2-1.

- b. Connect main write test PCA +5V power connector, XA2 to WJ12 of the write assembly motherboard A17, as shown in figure 2.2.

| Basic Test Operation     | Test PCA Signal-Jumper Connections (See Note)                                           |  |

|--------------------------|-----------------------------------------------------------------------------------------|--|

| Write (Block)            | (W)CF jumper to (C)WCF pin                                                              |  |

| Write (Continuous)       | No signal jumpers required                                                              |  |

| Read (Block-CF)          | (R)RCF jumper to (C)CF pin                                                              |  |

| Read (Block-Cycle)       | (R)RCF jumper to (C)CF pin<br>(R)RCR jumper to (C)CR pin                                |  |

| Read After Write         | (R)RCF jumper to (C)CF pin<br>(W)CF jumper to (C)WCF pin<br>(R)R/W jumper to (C)R/W pin |  |

| Read (Continuous)        | (R)RCF jumper to C(CF) pin                                                              |  |

| NOTE: (W) = HP 13191A Ma | in Write Test Accessory                                                                 |  |

| (R) = HP 13193A Re       | ad Test Accessory                                                                       |  |

| (C) = HP 13191A Co       | ntrol and Status Test Accessory                                                         |  |

Table 2-1. Test PCA Signal-Jumper Connections

- c. Connect main write test PCA CF (Forward Command) jumper P1, to the WCF (Write, Forward Command) pin of the control and status test PCA, as shown in figure 2-2.

- d. Plug one of the following write test program PCA's into XA1 (component side up) of the main write test board as shown in figure 2-1:

- (1) Write program 1 test PCA

- (2) Write program 2 test PCA

- e. Set the tape unit power switch to ON and perform the following write clock (WC) rate adjustment:

- (1) Connect an HP 5245L Electronic Frequency Counter or equivalent to the tape unit write PCA (A17A1) WC test point (see figure 2-2).

- (2) On the main write test PCA, connect the HI/LOW jumper (P2), and adjust the clock rate potentiometer (R13) for an 800 bits per inch (bpi) test that corresponds to the speed of the tape unit listed in table 2-2). For any other tape unit recording density or tape speed, use the following formula:

WC Rate = BPI X IPS.

#### 2-15. READ TEST PCA INSTALLATION.

a. Set tape unit power switch to OFF

- b. Plug read test PCA (component side up) into RJ11 of A18, the tape unit read assembly motherboard, as shown in figure 2-1. Do not force the PCA. A keying slot prevents installation if the board is being inserted incorrectly.

- c. Connect the read test PCA +5V power connector XA1 to RJ12 of the Read Assembly Motherboard.

- d. Connect the RCF (Read Command Forward) blue jumper lead on the read test PCA to the CF pin of the control and status test PCA, as shown in figure 2-2.

- e. Connect the (read-after-write) R/W black jumper lead on the read test PCA to the R/W pin of the control and status test PCA, as shown in figure 2-2.

- f. Connect the RCR (Read Command Reverse) red jumper lead on the read test PCA to the CR pin of the control and status test PCA.

#### 2-16. INSTALLATION CHECK.

2-17. The correct performance of the installed test PCA's should be verified as soon as possible after these PCA's have been received. Paragraph 3-28 (in section III) provides a read-after-write (R/W) check procedure that adequately exercises the write test \*PCA and the read test PCA. Successful completion of this check indicates that the test PCA's are operating correctly.

2300-38

Figure 2-1. Test Accessory Installation

| Tape Unit Speed,<br>Inches Per Seconds<br>(ips) | Write Test PCS<br>HI/LOW Jurnper<br>(P2) | WC Rate<br>(Indicated on frequency counter) |

|-------------------------------------------------|------------------------------------------|---------------------------------------------|

| 12.5                                            | LO                                       | 10 ±0.1 kHz                                 |

| 25                                              | н                                        | 20 ±0.2 kHz                                 |

| 37.5                                            | ні                                       | 30 ±0.3 kHz                                 |

| 45                                              | н                                        | 36 ±0.33 kHz                                |

Table 2-2. Main Write Test PCA Clock Rate Adjustment (800 bpi)

Installation

13192A/13193A

`

Figure 2-2. Test Accessory Interconnection Diagram

# OPERATION

#### 3-1. INTRODUCTION.

3-2. This section contains information required to operate the 13192A Write Test Accessory and the HP 13193A Read Test Accessory. Application information, which lists the various HP 7970 Digital Magnetic Tape Unit tests that are performed with these test boards, is included. References are made to the appropriate tape unit operating and service manual sections where the actual test procedures are described.

3-3. Control and indicator descriptions are included in this section. All controls and indicators on the test PCA's are identified, and the function of each is briefly explained. A discussion of the overall operation, and the interrelated functions of the test boards is also presented.

3-4. Part of this section describes a typical test procedure. This procedure specifies that the test boards were properly installed and the tape unit is configured as described in paragraphs 2-11 through 2-17. Certain operations involving the HP 13191A Control and Status Test Accessory are included in this section to provide continuity of the test procedure.

#### 3-5. APPLICABILITY.

3-6. Table 3-1 lists the various off-line tests and adjustments that can be performed on the HP 7970 Series Digital Magnetic Tape Units when using the HP 13192A Write Test Accessory and the HP 13193A Read Test Accessory. References are made to the sections of the tape unit operating and service manuals, where these tests and adjustment procedures are described. Other test accessory requirements, such as the HP 13191A Control and Status Test Accessory oscilloscopes, or special tapes, are also listed in the table.

#### 3-7. CONTROLS AND INDICATORS.

3-8. Figures 3-1 and 3-2 show the controls and indicators of the write test accessory and the read test accessory. Table 3-2 describes the functions of the controls and indicators shown in figure 3-1. Controls and indicators shown in figure 3-2 are described in table 3-3. Table 3-4 lists test PCA initial switch settings for the basic tests performed by the write test and the read test accessories. Paragraphs 3-9 through 3-19 provide a detailed description of the write test procedures. Paragraphs 3-20 through 3-31 describe the read test procedures.

#### **3-9. WRITE TEST ACCESSORY OPERATION.**

3-10. The HP 13192A Write Test Accessory provides the means to simulate write-operation signals and check the write electronic circuits of the tape unit. It is an operational requirement that the HP 13191A Control and Status Test Accessory be installed when performing these write tests. The write test accessory then allows checking of the following performance parameters such as (see table 3-1):

- (1) Write-time Assymetry

- (2) Write head static skew

- (3) Write reset

- (4) Erase/write phasing

- (5) Write crosstalk

Refer to paragraphs 2-12 and 2-13 for initial test set-up.

3-11. The HP 13192A Write Test Accessory operates in either of two modes: continuous or block (as selected by the XTALK/BLOCK switch). The procedure for writing continuous data patterns is as follows:

- a. Set the XTALK/BLOCK switch to the XTALK position.

- b. Check and adjust the Write Clock (WC) rate as described in paragraph 2-13, step e.

- c. Configure the control and status test PCA for continuous operation by:

- (1) Setting the PROG/MAN switch to the MAN position.

- (2) Setting the WSW switch up to the WSW position.

- (3) Setting the CF switch up to the CF position.

3-12. The procedure for writing a block-type pattern is as follows (the block length, i.e. the number of characters per block is variable and is determined by an adjustment on the control and status test PCA.):

- a. Set the XTALK/BLOCK switch to the BLOCK position.

- b. Check and adjust the Write Clock (WC) as described in paragraph 2-13, step e.

#### Table 3-1. Test PCA Applications

| TEST OR ADJUSTMENT<br>PROCEDURE                    | REFERENCE                                                                        | 13192A or 13193A<br>TEST PCA<br>APPLICATION                               | OTHER TEST<br>ACCESSORIES USED                                                |

|----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Write Data Performance Test                        | 7970B/C Operating and Service<br>Manual, Part 1, Section III,<br>Para. 3-49      | HP 13192A (with any pro-<br>gram test board HP 13193A                     | HP 13191A and Scratch tape (write enable ring installed)                      |

| Read Preamplifier Gain Test                        | 7970B/C Operating and Service<br>Manual, Part 3, Section 11,<br>Para. 2-8        | HP 13192A-60010 PCA<br>HP 13192A-60020 PCA<br>{ALL I/O Plug}              | HP 13191A, Oscilloscope, and<br>Scratch tape (write enable ring<br>installed) |

| Read Character Gate Strobe<br>and Read Clock Test  | 7970B/C Operating and Ser-<br>vice Manual, Part 3, Section<br>II, Para. 2-16     | HP 13192A-60010 PCA<br>HP 13192A-60010 (All 1/O,<br>and SRB plug)         | HP 13191A, Oscilloscope, and<br>Scratch tape (write enable ring<br>installed) |

| Pre-Amplifier Gain Adjustment                      | HP 7970B/C Operating and<br>Service Manual, Part 3, Sec-<br>tion II, Para. 2-21  | HP 13192A-60010 PCA<br>HP 13192A-60020 PCA<br>(ALL I/O plug)              | HP 13191A, Oscilloscope, and<br>Scratch tape (write enable ring<br>installed) |

| Write Time Assymetry Test                          | HP 7970B/C Operating and<br>Service Manual, Part 4, Para.<br>2-11                | HP 13192A-60010 PCA<br>HP 13192A-60020 PCA<br>(ALL I/O plug)              | HP 13191A, Oscilloscope, and<br>Scratch tape (write enable ring<br>installed) |

| Write/Read Skew Test                               | HP 7970B/C Operating and<br>Service Manual, Part 4, Sec-<br>tion II, Para. 2-13  | HP 13192A-60010 PCA<br>HP 13192A-60020 PCA<br>(ALL I/O plug)<br>HP 13193A | HP 13191A, Oscilloscope, and<br>Scratch tape (write enable ring<br>installed) |

| Write/Read Phasing and Write<br>Reset Test         | HP 7970B/C Operating and<br>Service Manual, Part 4, Sec-<br>tion II, Para. 2-15  | HP 13192A-60010 PCA<br>HP 13192A-60020 PCA<br>(WRS plug)<br>HP 13193A     | HP 13191A, Oscilloscope, and<br>Scratch tape (write enable ring<br>installed) |

| Erase/Write Phasing Test                           | HP 7970B/C, Operating and<br>Service Manual, Part 4, Sec-<br>tion II, Para. 2-17 | HP 13192A-60010 PCA<br>HP 13192A-60020 PCA<br>(ALL I/O plug)<br>HP 13193A | HP 13191A, Oscilloscope, and<br>Scratch tape (write enable ring<br>installed) |

| Write Cross-Talk Test                              | HP 7970B/C, Operating and<br>Service Manual, Part 4, Sec-<br>tion II, Para. 2-19 | HP 13192-60010 PCA<br>HP 13192-60030 PCA<br>(DDP Plug)                    | HP 13191A, Oscilloscope, and<br>Scratch tape (write enable ring<br>installed) |

| Internal Write Clock Delay<br>and Pulse Width Test | HP 7970B/C Operating and<br>Service Manual, Part 4, Sec-<br>tion II, Para. 2-21  | HP 13192-60010 PCA                                                        | Oscilloscope                                                                  |

| Tape Interchangeability Test                       | HP 7970B/C Operating and<br>Service Manual, Part 4, Sec-<br>tion 11, Para. 2-25  | HP 13193A                                                                 | HP 13191A, Oscilloscope, and Tape with random length blocks                   |

| Write Skew Delay, Adjustment                       | HP 7970B/C Operating and<br>Service Manual, Part 4, Sec-<br>tion II, Para. 2-30  | HP 13192-60010 PCA<br>HP 13192-60020 PCA<br>(ALL I/O plug)                | HP 13191A, Oscilloscope, and<br>Scratch tape (write enable ring<br>installed) |

|                                                    |                                                                                  |                                                                           |                                                                               |

|                                                    |                                                                                  |                                                                           |                                                                               |

.

Figure 3-1. Write Test Accessory Controls and Indicator

Operation

Figure 3-2. Read Test Accessory Controls and Indicators

- c. Configure the HP 13191A Control and Status PCA for programmed operation by:

- (1) Setting the PROG/MAN switch to the PROG position.

- (2) Setting the SET CRW switch to OFF.

- (3) Initially, setting the PCF potentiometer fully counterclockwise, then adjusting block length per paragraph 3-13.

- (4) Setting the WSW switch up to the WSW position.

- (5) Setting the CF switch up to the CF position.

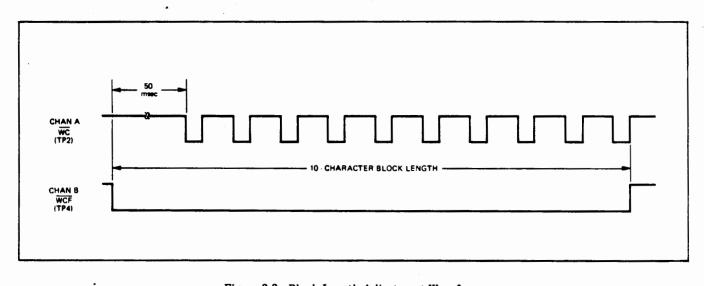

3-13. In the block mode of operation, the length of the block is determined by the PCF adjustment on the control and status test PCA. This block-length is adjusted as follows (refer to figure 3-3):

- a. Connect channel A of a dual-trace oscilloscope to the WC test point (TP2) of the main write test PCA.

- b. Connect channel B of the dual-trace oscilloscope to the WCF test point (TP4) of the main write test PCA.

- c. Synchronize the oscilloscope to the negative slope of the WCF gate observed on the channel B trace.

| FIGURE &<br>INDEX NO. | NAME                              | REF<br>DESIG | FUNCTION                                                                                                  |

|-----------------------|-----------------------------------|--------------|-----------------------------------------------------------------------------------------------------------|

| FIG 3-1               |                                   |              |                                                                                                           |

| 1                     | X-TALK/BLOCK switch               | A 1S 1       | Selects continuous or block mode of operation                                                             |

| 2                     | EVEN/ODD switch                   | A 152        | Selects even or odd vertical parity                                                                       |

| 3                     | 7 TR/9TR switch                   | A1S3         | Selects nine-track or seven-track write test data                                                         |

| 4                     | SW indicator                      | A1CR3        | Indicates whether tape unit is in write mode                                                              |

| 5                     | Clock Adjustment<br>Potentiometer | A1R13        | Allows setting the appropriate clock rate for 10-to-45 ips operation at densities of 200, 556, or 800 bpi |

| 6                     | CF jumper                         | A1P1         | Interfaces with the control and status test PCA for writing block-type data                               |

| 7                     | HI/LO jumper                      | A 1P2        | Selects the appropriate clock rate range (10-to-25 ips, or 20-to-45 ips)                                  |

| 8                     | Program PCA connector             | A1XA1        | Connects input test formats from write program test PCA's                                                 |

| 9                     | +5V connector                     | A1XA2        | Provides operating voltages for the write test accessory PCA's                                            |

| 10                    | ALL ONE'S/ALL ZERO'S<br>switch    | A2S1         | Selects a fixed logic "O" or a fixed logic "1" format for the write test program                          |

| Table 3-2. Write Test Accessory C | Controls and Indicator |

|-----------------------------------|------------------------|

|-----------------------------------|------------------------|

| Table 3-3. Read Test Accessory ( | Controls and Indicators |

|----------------------------------|-------------------------|

|----------------------------------|-------------------------|

| FIGURE &<br>INDEX NO. | NAME               | REF<br>DESIG     | FUNCTION                                                                                                                                   |

|-----------------------|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| FIG 3-2               |                    |                  |                                                                                                                                            |

| 1                     | RD BL/OFF switch   | S1               | Selects read block or continuous test function                                                                                             |

| 2                     | EVEN/ODD switch    | S2               | Selects even or odd vertical (lateral) parity                                                                                              |

| 3                     | CYCLE/CF switch    | \$3              | Selects cyclic forward and reverse (CYCLE) or continuous forward (CF) tape motion in read block mode.                                      |

| 4                     | HI/LO switch       | S4               | Selects appropriate read clock range for high-speed tape operation (20-to-45 ips) or low-speed operation (10-to-20 ips) in read block mode |

| 5                     | NORM/ERROR STOP    | S5               | Selects normal, momentary stop for parity error display (NORM) or per-<br>manent stop on parity error display (ERROR STOP)                 |

| 6                     | LAT P lamp         | CR5              | Displays vertical (lateral) parity error                                                                                                   |

| 7                     | 10 CL ADJ          | R10              | Sets appropriate internal longitudinal parity evaluation interval in the read block mode                                                   |

| 8 thru 16             | P, 0 thru 7 lamps  | CR6 thru<br>CR14 | Displays longitudinal parity error on tracks P, and 0 thru 7                                                                               |

| 17                    | +5V jumper         | XA1              | Provides operating voltage for the read test PCA                                                                                           |

| 18                    | RCR jumper (red)   | W 1              | Provides the means of issuing the reverse tape motion command to the HP 13191A                                                             |

| 19                    | RCF jumper (blue)  | W2               | Provides the means of issuing tape forward motion command to the HP 13191A                                                                 |

| 20                    | R/W jumper (black) | W3               | Provides the means of issuing the read-after-write command to the HP 13191A                                                                |

.

.

~

:

| Test Operation                   | Write-Block<br>(See Notes 4, 6)                         | Write-Continuous<br>(See Note 4)   | Read Only-Block<br>(See Note 5)         | Read Only-<br>Continuous                | Read-After-Write<br>(See Notes 4,5,6)   |

|----------------------------------|---------------------------------------------------------|------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| HP 13191A Control                | 1: CF switch on (up)                                    | 1. CF switch on (up)               | 1. CF switch on (up)                    | 1. CF switch on (up)                    | 1. CF switch on (up)                    |

| and Status Test PCA              | 2. PROG/MAN<br>switch to PROG                           | 2. PROG/MAN<br>switch to MAN       | 2. WSW switch off<br>(down)             | 2. WSW switch off<br>(down)             | 2. WSW switch on<br>(up)                |

|                                  | 3. WSW switch on<br>(up)                                | 3. WSW switch on<br>(up)           |                                         |                                         |                                         |

| HP 13192A Main<br>Write Test PCA | 1. BLOCK/X TALK<br>switch to BLOCK                      | 1. BLOCK/X TALK<br>switch to XTALK | Not Used                                | Not Used                                | 1. BLOCK/X TALK<br>switch to BLOCK      |

| HP 13193A Read<br>Test PCA       | Not Used                                                | Not Used                           | 1. RD BL switch to<br>RD BL             | 1. RD BL'switch to<br>OFF (right)       | 1. RD BL switch to<br>RD BL             |

|                                  |                                                         |                                    | 2. CF/CYCLE<br>switch to CF             | 2. NORM/ERROR<br>STOP switch to<br>NORM | 2. CYCLE/CF switch<br>to CF             |

|                                  |                                                         |                                    | 3. NORM/ERROR<br>STOP TO NORM<br>switch |                                         | 3. NORM/ERROR<br>STOP switch to<br>NORM |

| NOTE: 1. Parity                  | switches are set as requir                              | red on main write test P           | CA and read test PCA.                   |                                         | • • • • • • • • • • • • • • • • • • •   |

| 2. 7-TR/                         | TR switch set as requir                                 | ed on the main write te            | at PCA.                                 |                                         |                                         |

|                                  | R STOP/NORM switch //////////////////////////////////// | (on the read test PCA)ca           | n be set in the ERROR                   | STOP position as an op                  | tion for the read tests                 |

| 4. All wr                        | ite tests require a clock r                             | ate adjustment as descri           | bed in paragraph 2-14e.                 |                                         |                                         |

| 5. Read I                        | block and R/W tests requ                                | ire adjustment as descri           | bed in paragraph 3-26.                  |                                         |                                         |

| 6. Write                         | Block and R/W Tests req                                 | uire PCF adjustment as             | described in paragraph 3                | 3-26.                                   |                                         |

#### Table 3-4. Initial Test Accessory Switch Settings

#### Figure 3-3. Block Length Adjustment Waveforms

3-6

d. Adjust the PCF potentiometer on the control and status test PCA so that the gate duration of the WCF signal is equal to 10 WC pulses. The block length is then adjusted to generate ten characters per block. (One character is generated with every WC pulse).

3-14. The block length may be adjusted to accommodate any number of characters within the limits dictated by the recording density and tape speed handling capacity of the tape unit. Caution is advised, however, when making this adjustment. The gate width of the WCF signal should exceed 50 milliseconds. If the gate width is less than 50 milliseconds, the tape will be erased, since the write clocks (WC) and the character output of the write test accessory are delayed 50 milliseconds after the leading edge of the WCF gate.

#### 3-15. TEST PATTERN PROGRAMS.

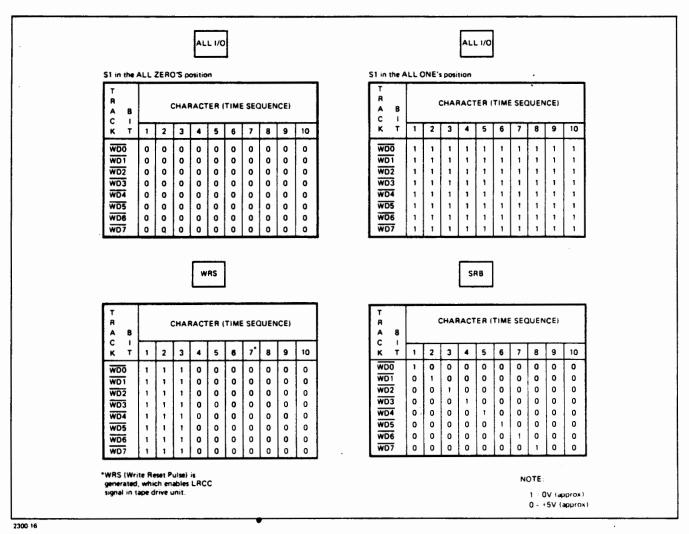

3-16. Programmed test patterns may be generated using the HP 13192-60020 Write Program 1 Test PCA, or the HP 13192-60030 Write Program 2 Test PCA. Together, these two program PCA's provide as many as six different write data patterns to the user.

#### 3-17. WRITE PROGRAM 1 TEST PCA.

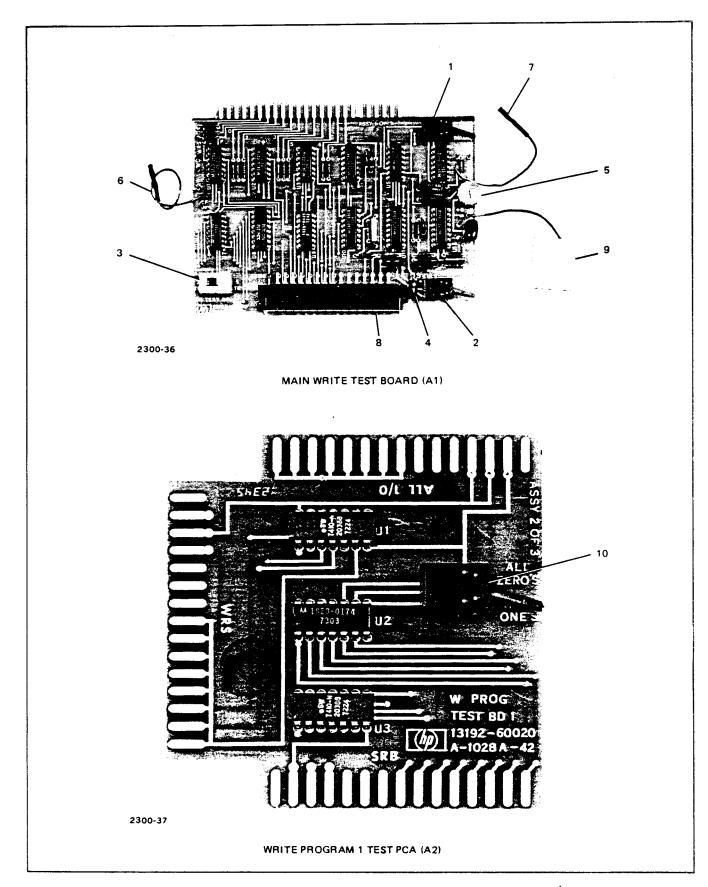

3-18. The write program 1 test PCA has three connectors that can be inserted into the main write test PCA. Each connector is marked with the mnemonic title that identifies the selected data pattern. These four programmed test patterns are shown in chart form in figure 3-4, and the waveforms generated are shown in figures 5-7, 5-8, and 5-9. The mnemonic titles are explained below:

#### MNEMONIC FUNCTION

- ALL 1/0 Provides a pattern of all one's or all zero's, depending on the position of S1.

- SRB Provides a single-rotating-bit pattern that progresses from track to track, on a character-by-character basis to verify that each data track will generate a read clock.

- WRS Provides a data pattern of three one's, followed by seven zero's on each data channel. A write reset (WRS) pulse will be generated during every seventh character time sequence.

#### 3-19. WRITE PROGRAM 2 TEST PCA.

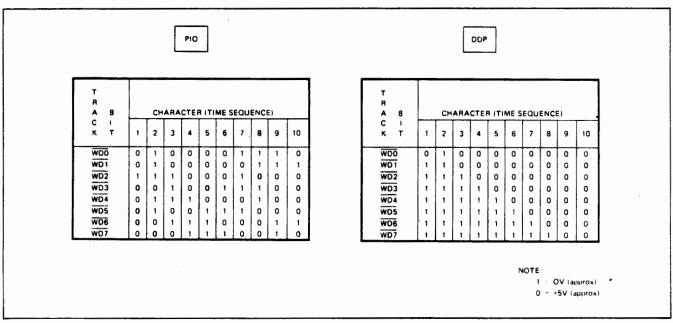

3-20. The write program 2 test PCA has two connectors that may be inserted into the main write test PCA. The mnemonic titles are marked at each connector to indicate the selected pattern. The two programmed test patterns available are shown in figure 3-5). The mnemonics are explained below:

# MNEMONICFUNCTIONDDPProvides a dynamic data pattern to<br/>create a maximum combination of flux<br/>relationships for verifying total dy-<br/>namic skew characteristics of the tape<br/>unit.PIOProvides a pattern of "isolated-one"<br/>in combination with "triple-one" se-<br/>quences for checking isolated and<br/>crowded pulses.

#### 3-21. READ TEST ACCESSORY OPERATION.

3-22. The HP 13193A Read Test Accessory reads recorded data, then detects and displays both vertical and longitudinal parity errors. It is a requirement that the HP 13191A Control and Status Test Accessory be used in conjunction with the read test accessory to perform all read tests. The read test accessory may be operated in either of two basic modes: continuous or block mode.

#### 3-23. CONTINUOUS MODE.

3-24. In the continuous mode of operation, even or odd vertical (lateral) parity errors (as selected by the EVEN/ ODD parity select switch, S2) are detected and displayed. The first vertical parity error, sensed by the test PCA, is displayed on the LAT P indicator (CR5), which then remains lit until manually cleared. To clear this error indication, the operator should toggle the ERROR STOP/NORM switch S5. The number of vertical parity errors detected may be counted by monitoring the LAT P test point (TP9) with an oscilloscope, during the test interval. During the continuous read test operation, tape motion is continuous, and is exclusively controlled by the control and status test accessory.

#### 3-25. BLOCK MODE.

3-26. In the block mode of operation, the read test accessory evaluates "blocked" or interrupted tape data. Tape motion is interrupted, and controlled jointly by the read and the control and status test accessories. In this mode, the read test accessory provides an error-stop option which halts further tape motion when a parity error is detected. This option is activated by setting the ERROR STOP/NORMAL switch to the ERROR STOP position.

Note: In the read block or the read-after-write modes of operation, the first block read after tape motion begins may light the parity error lamps. This is an erroneous parity fault indication that should be ignored. This applies to the first block only.

3.7

Operation

Figure 3-4. Write Test Accessory Data Program 1 Output Pattern

Figure 3-5. Write Test Accessory Data Program 2 Output Pattern

3-27. READ TEST ACCESSORY ADJUSTMENT. To provide the correct longitudinal parity, the tape unit under test generates a longitudinal redundancy check character (LRCC). This LRCC is checked by the read test accessory during the time interval which immediately follows read data time. The "check time interval" (i.e. the interval during which the LRCC and longitudinal parity is evaluated as described in paragraph 4-54 of section IV) is determined by the adjustment of the 10 CL potentiometer, R10. This adjustment is critical to the test operation and, if improperly set, erroneous parity errors are displayed. The adjustment is made while reading an 800-bpi tape, and is accomplished in the following manner:

a. Connect the oscilloscope to the 10 CL test point (TP6) on the read test PCA. Set the oscilloscope to trigger on the negative slope of the waveform shown in figure 3-6.

Figure 3-6. 10 CL Gate Signal (TP6)

b. On the read test PCA, set the LO/HI switch as required, and adjust the 10 CL ADJ potentiometer to obtain the 10 Clock Width (CW) that conforms to tape-speed parameters listed in table 3-5.

For any other tape unit density or speed; use the following . formula to determine the correct CW:

$$CW = \frac{10}{BPI X IPS}$$

The read test accessory provides other options such as the cycle test and the read-after-write (R/W) test functions when operating in the block mode of operation.

3-28. CYCLE TEST FUNCTION. The cycle test function is usually initiated by the read test PCA operator when an error halt condition exists (resulting from incorrect parity). Setting the CYCLE/CF switch, S3 to the CYCLE position, causes tape motion to resume. The read test PCA then issue alternate forward and reverse tape motion commands which permits the operator to view a specific data block repeatedly, to identify the incorrect character.

3-29. READ-AFTER-WRITE TEST FUNCTION. When the read-after-write function is employed, the read test accessory, as well as the write test and control and status test accessories combine synchronous operations, to evaluate the read-after-write (R/W) performance of the tape unit.

3-30. The R/W (read-after-write) test is used to detect and display vertical or horizontal parity errors that could occur when the tape unit is in the read-after-write mode of operation. The main write test PCA (HP 13192-60010) is programmed with a write program 2 test PCA (HP 13192-60030) to provide a unique data patter. This data is written on scratch tape which is equipped with a write enable ring. The following test components are required to perform a read-after-write test on the tape unit:

- a. Main write test PCA, HP part no. 13192-60010

- b. Write program 2 test PCA, HP part no. 13192-60030

- c. Control and status test PCA, HP part no. 13191-60010

- d. Read test PCA, HP part no. 13193-60010

- e. Scratch tape (with write enable ring installed, HP part no. 9162-0025 or 0026

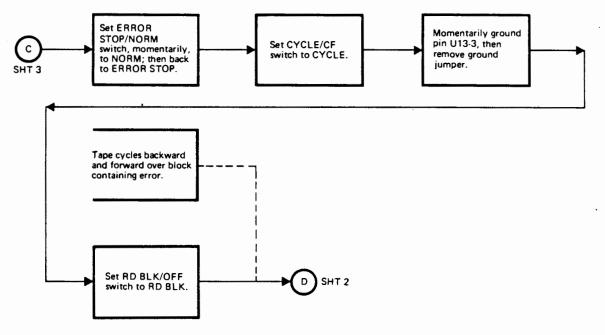

3-31. Figure 3-7 provides a flow diagram which shows the sequence of operations performed on the tape unit and the test components described in paragraph 3-30. Prior to performing this test, install the test PCA's per paragraphs 2-10 through 2-15.

3-32. On the flow diagram (figure 3-7), the letter appearing at the upper right-hand corner of each block denotes the test PCA on which the operation (described by the block) is performed. These letters are explained below:

- C = control and status test PCA

- W = write test PCA

- R = read test PCA

| Tape Unit Speed;<br>inches per second<br>(ips) | Read Test PCA<br>LO/HI Switch (S4)<br>Position | 10 Clock Gate Width CW<br>(in microseconds) |

|------------------------------------------------|------------------------------------------------|---------------------------------------------|

| 12.5                                           | LO                                             | 1000                                        |

| 25                                             | н                                              | 500                                         |

| 37.5                                           | н                                              | 333                                         |

| 45                                             | н                                              | 277                                         |

Table 3-5. Read Test PCA 10 Clock Width Adjustment (800 bpi)

.

2300-20A (SHT 1)

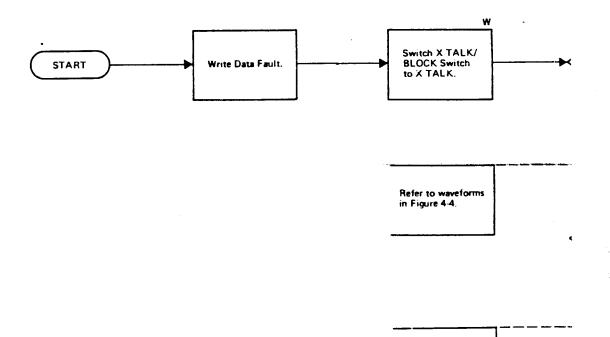

Figure 3-7. R/W Test Operational Flowchart (Sheet 1 of 4) 3-11/3-12

2300-20A

Figure 3-7. R/W Test Operational Flowchart (Sheet 3 of 4)

2300-20A

Figure 3-7. R/W Test Operational Flowchart (Sheet 4 of 4)

# THEORY OF OPERATION

#### 4-1. INTRODUCTION.

4-2. This section contains general and detailed descriptions of how the HP 13192A Write Test and the HP 13193A Read Test Accessories perform the test operations described in section III. When required, information concerning the HP 13191A Control and Status Test Accessory to provide continuity of the test function theory of operation. If necessary, refer to the HP 13191A Control and Status Test Accessory Operating and Service Manual for more complete circuit theory. The combined operations of the three test PCA's are discussed first in the functional description of the read-after-write (R/W) test. This description relates the test function to the operation of the tape unit-under-test, thereby providing an over-view of the test accessory operation. Next, the pertinent details of the read test accessory and the write test accessory circuit operations are separately described.

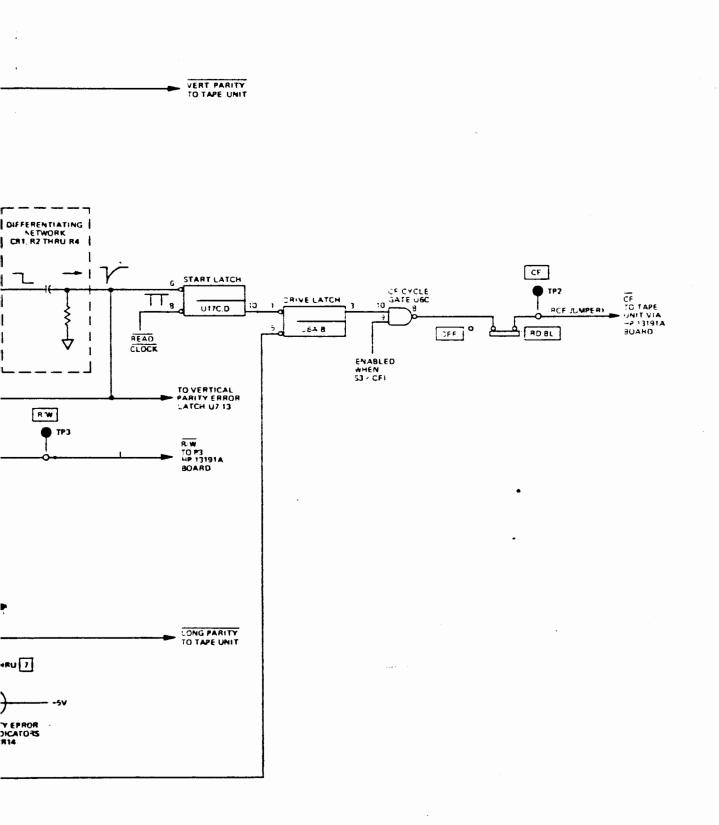

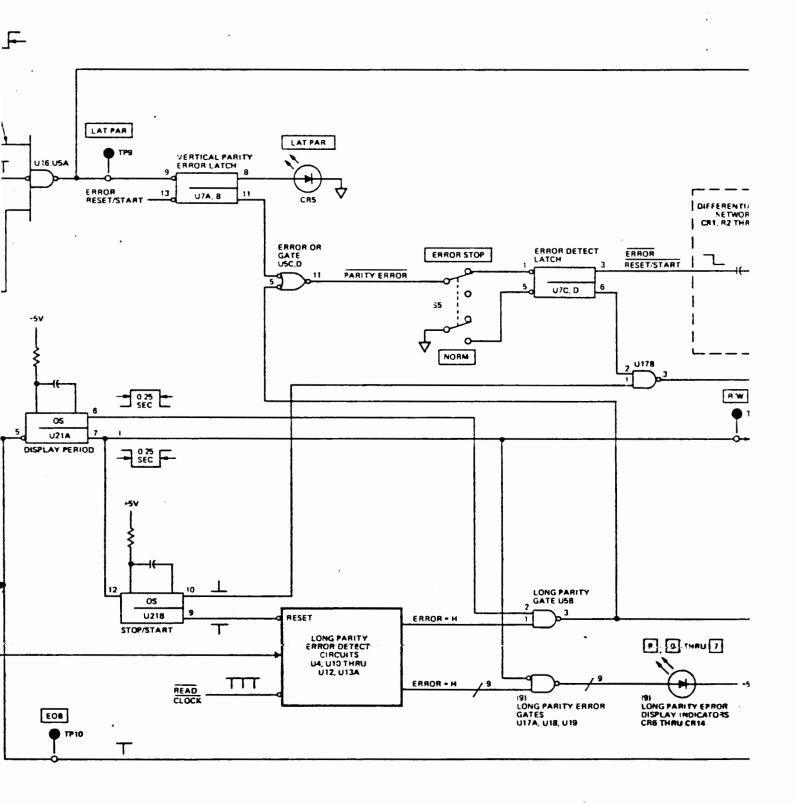

#### 4-3. READ-AFTER-WRITE TEST FUNCTIONAL DESCRIPTION.

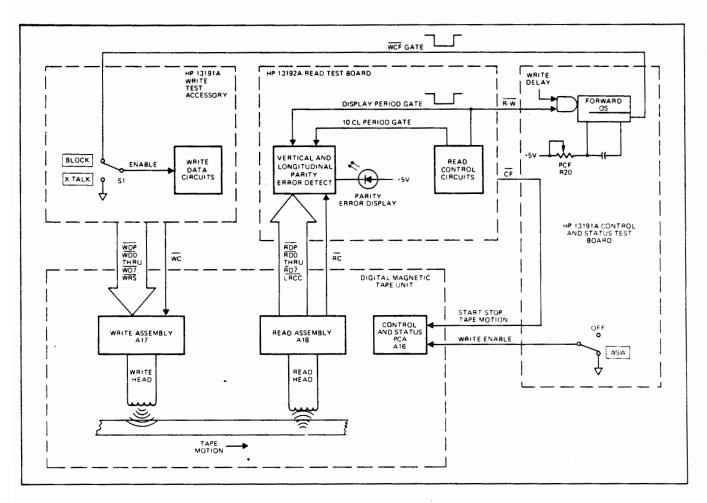

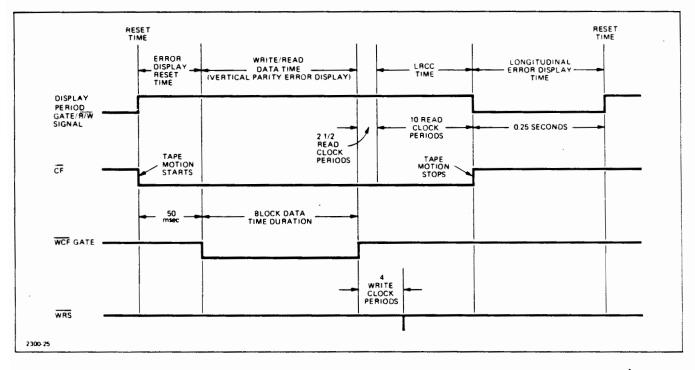

4-4. The read-after-write test description provides a general overview of the write test accessory and the read test accessory operation. This test, which evaluates the capability of the tape unit to write and read data blocks correctly, can be functionally broken down into four time-sequenced operations (Refer to figures 4-1 and 4-2):

- (1) Error-display time

- (2) Read-after-write data time

- (3) Longitudinal Redundancy Check Character (LRCC) time

- (4) Longitudinal Parity error display time

#### 4-5. ERROR-DISPLAY RESET TIME.

4-6. The end of a previous longitudinal error display period initiates another read-after-write data block operation cycle by clearing the parity error display circuits on the read test PCA. The clear signal that accomplishes this also activates the command forward (CF) signal. This signal is applied to the tape unit via the control and status test PCA to initiate forward tape motion.

#### 4-7. READ-AFTER-WRITE DATA TIME.

4-8. Approximately 50 milliseconds after forward tape motion is initiated, the control and status test PCA generates the Write Command Forward (WCF) signal, which is applied to the write test accessory. This signal is a variableduration negative gate. The gate duration is controlled by

R20, the PCF potentiometer on the control and status test PCA. As a result, the PCF potentiometer controls the read-after-write data time duration. The WCF gate signal enables the write test accessory circuits. The enabled circuits then generates data to be written, (WDP, WD0 through WD8), a write reset pulse (WRS) and the write clock (WC). These signals are applied to the tape unit write assembly (A17). When the control and status test PCA WSW switch is in the WSW position, a write enable signal input to the tape unit (control and status PCA A16) allows data to be written on tape. During the same operation, the tape unit read assembly (A18), reads the tape, and responds to the data input by generating read data (RDP, RD0 through RD7), an LRCC, and read clock pulses (RC). These signals are applied to the Read Test PCA, which checks each character of the data block for correct vertical parity. If parity errors are detected during this read-after-write data time interval, the LAT PAR indicator is lit. Data ceases to be written and read when the WCF gate terminates.

4-9. LRCC TIME.

4-10. The tape unit responds to the write test accessory WRS input pulse by generating the LRCC character approximately four write clock periods after the WCF signal ends when a seven-track tape is used. When a nine-track tape is used, the LRCC is delayed eight clock periods after WCF time. Approximately 2-1/2 read clock periods after WCF signal termination, the read test PCA senses an end-of-data condition, and goes into the LRCC-read mode of operation. This mode time is adjusted by the 10 CL potentiometer for an approximate 10 read clock period duration.

## 4-11. LONGITUDINAL PARITY ERROR DISPLAY TIME.

4-12. The end of LRCC time initiates the longitudinal parity error display time and stops tape motion by terminating the true CF signal. The generated 250-millisecond display period gate signal allows longitudinal parity errors (if any are detected) to be displayed. This negative gate signal is recognized as a true R/W signal by the control and status test PCA. As a result, the WCF gate generator on the control and status test PCA is inhibited and data cannot be written during the display period. When the display period gate signal terminates, both the longitudinal and vertical parity circuits are cleared to the no-error state, and another read-after-write test cycle is started.

#### 4-13. WRITE TEST ACCESSORY.

4-14. The HP 13192A Write Test Accessory consists of a main write test PCA, and two programming PCA's which plug into the main write PCA to provide six different write

Figure 4-1. R/W Test Functional Diagram

data patterns. These patterns are rotating, ten-character sequences. Each pattern is designed to exercise a particular tape unit write capability. The write tests are generated in a continuous format when the X TALK/BLOCK switch S1 is in the X TALK position, or in a burst or interrupted format when S1 is in the BLOCK position. The duration of the burst write data pattern is determined by settings on the HP 13191A Control and Status Test Accessory. Paragraphs 4-15 through 4-19 provide a functional description of the over-all write test accessory operation. The paragraphs following the functional description provide detailed circuit analysis of the write test accessory cross-talk block operation. Lastly, the write test program PCAs are briefly discussed.

#### 4-15. WRITE TEST ACCESSORY FUNCTIONAL DESCRIPTION

4-16. A simplified write test accessory logic diagram is shown in figure 4-3. The master write clock generates pulses that provide output signals and appropriate output signal timing. This pulse, or clock rate, is adjustable to provide a frequency range of 2 kHz to 16 kHz when LOW is selected, or a range of 16 kHz to 36 kHz when HI is selected. As a result, the write test accessory is capable of writing with tape speeds of 10 to 20 inches per seconds (ips) in LOW, and 20 to 45 ips in the HI range; at recording densities of 200, 556, or 800 bits per inch (bpi).

4-17. The 10-character generator provides a continuous or block write test pattern as determined by the X TALK /BLOCK control circuits. In the block mode of operation, a write command forward (WCF) gate, derived from the control and status test accessory, initiates generation of the write clock and data characters to be written after a 50-millisecond delay. This delay compensates for the time necessary for tape units to reach normal speeds before writing the data patterns. The type of test data pattern to be generated is determined by the selection of one of three available write program test PCA's (see paragraph 3-15).

4-18. The write clock is delayed approximately 400 nanoseconds after the character generator is pulled by the master clock. This delay ensures that the data characters (WDP, WD0 through WD7) are available at the write test accessory output when the write clock is generated.

4-19. The 7-TR/9-TR switch allows formatting of the write test accessory output to accommodate seven-track or nine-track tapes. Write-data tracks 0 and 1 (WD0 and WD1) are not used when the switch is in the 7-TR position. The parity generator samples data in all test modes and provides the appropriate parity bit for either even or odd parity (as selected by the ODD/EVEN switch).

4-20. In the block mode, the write reset (WRS) pulse generator provides a pulse output four clock pulses after the termination of the WCF signal. The WRS pulse causes the tape unit to provide an even number of one bits in each data track (WDP, WD0 through WD7), by generating a longitudinal redundancy check character (LRCC).

Figure 4-3. Write Test Accessory Simplified Logic Diagram

#### 4-21. MAIN WRITE TEST ACCESSORY CIRCUIT DE-SCRIPTION.

4-22. The HP 13192A Write Test Accessory schematic diagrams are shown in figures 5-6 through 5-11. On the main write test PCA, the master write clock, consisting of U10B and U4, provides frequency-adjustable clock pulses that trigger decade counter U7, WD Delay one-shot U11A, and WRS Delay one-shot U12B. This clock frequency is adjusted by connecting HI/LOW jumper P2 to either J1 or J2 and adjusting potentiometer R13 for the desired clock rate. Connector XA2 provides +5V operating power which originates from the tape unit write assembly. S1 selects either a continuous data pattern in the X TALK position, or an interrupted data pattern in the BLOCK position.

CONTINUOUS X TALK MODE. When S1 is in the 4-23. X TALK position, a continuous data pattern is written. Ground is applied to "nand" gate U5A, Block Delay oneshot U10A, and to the direct-clear input of the WRS generator U12A. Inverter U5A remains high at pin 3 and the clear-side Q output of one-shot U10A stays high as a result of the ground input from S1. These high inputs to "nand" gate U5B causes its output to be low at pin 6. This fixed low on the Block Control line inhibits the Reset-9 (R9) input of the decade counter U7, and disables WRS Delay one-shot U12B. As a result U12B provides a constant low to the direct-clear input of 4-clock Delay flip/flops U6A and U6B, disabling these flip/flops. "Nand" gate U5A responds to the constant-low input by providing a constanthigh Block Output Enable signal. This high enables "nor" gates U1A/b, U2A/B/C/C, U3A/B and the WC Delay oneshot U11A.

4-24. The master write clock pulses trigger Decade Counter U7. U7 counts these clock pulses and provides a four-bit binary command output that continuously counts from zero to nine, then back to zero. (See figure 4-4.) These cycling, binary commands are applied to binary-todecimal converter U8. Table 4-1 shows the command outputs of U7 as they relate to the master clock pulses, and the write character time sequences. U8 responds to the binary command inputs by generating ten, staggered-character output gates (see 10-character generator output in figure 4-4) which are applied to the selected write test program PCA via pins F through S of connector XA1.

4-25. The negative master clock pulses from U10B pin 10 triggers the WC Delay one-shot U11A at pin 4. The one-shot responds to these clock pulse inputs by generating a negative, 400-nanosecond pulse output, which is applied to WC Generator U11B. U11B is a two-microsecond oneshot which is triggered by the positive transition of the input pulse. As a result, the WC generator provides 2microsecond pulses which are delayed 400 nanoseconds after the master clock pulses. This delay compensates for the transient time of the character generator signal and allows simultaneous generation of the write data pattern and the write clock pulses.

| Table 4-1. U7 I | Binary | Command | Outputs |

|-----------------|--------|---------|---------|

|-----------------|--------|---------|---------|

|    | Master<br>ck Pulses                   | 1 | 2 | 3 | 4 | 5 | 6    | 7    | 8   | 9     | 10             | 11    | 12 |

|----|---------------------------------------|---|---|---|---|---|------|------|-----|-------|----------------|-------|----|

|    | aracter<br>Sequence                   | 1 | 2 | 3 | 4 | 5 | 6    | 7    | 8   | 9     | 10             | 1     | 2  |

|    | 0 <sub>A</sub><br>(Pin 12)            | 0 | 1 | 0 | 1 | 0 | 1    | 0    | 1   | 0     | 1              | 0     | 1  |

|    | Q <sub>B</sub><br>(Pin 9)             | 0 | 0 | 1 | 1 | 0 | 0    | 1    | 1   | 0     | 0              | 0     | 0  |

| U7 | Q <sub>C</sub><br>(Pin 9)             | 0 | 0 | 0 | 0 | 1 | 1    | 1    | 1   | 0     | 0              | 0     | 0  |

|    | Q <sub>D</sub><br>(Pin 11)            | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0   | 1     | 1              | 0     | 0  |

| NC | NOTE: 1 = approx +5V<br>2 = approx 0V |   |   |   |   | F | or L | 17 Q | A t | nru ( | ° <sup>D</sup> | utput | s. |

4-26. The character-pattern output from the selected write program test PCA is applied back to the main write test PCA via pins 8 through 15 of XA1. These character bits are applied to parity checker/generator U9 and to "nor" gates U1A/B, U2A/b/C/D, and U3A/B. Table 4-2 shows that the  $\Sigma$ -even output of parity generator U9 depends on two conditions: the number of bits that comprise the input character, and the position of EVEN/ODD switch S2.

4-27. Assume, for example, a character consisting of six one-bits is generated by the test program PCA which is plugged into XA1. U9 then detects an even number of input bits ( $\Sigma$  -character one bits = even). If S2 were in the EVEN position, U9 pin 4 would be high, activating the odd parity generation function. As a result, the  $\Sigma$ -even output (U9 pin 5) responds to the six-bit input by generating no more bits (ie remaining low), thereby maintaining an even parity character. Had S2 been in the ODD position, U9 would be in the even parity generation mode, resulting in the generation of another bit (ie. the  $\Sigma$ -even output going high) to obtain odd parity.

4-28. "Nor" gates U1A/B, U2A/B/C/D, and U3A/B are enabled by a constant high on the Block Output Enable line. This allows the output-character pattern (WDP, WD0 through WD7), and the write clock (WC) to be generated by the main write test PCA. Each time the tape unit establishes the set write condition, that is when current flows through the write head, a low SW signal is applied to U3, pins 12 and 13. U3 inverts this input to provide high signal drive that lights the SW indicator, CR3.

4-29. BLOCK MODE. (Refer to figures 5-6 and 4-5). When the main write test PCA BLOCK/X TALK switch A1S1 is in the BLOCK position, the output pattern appears in an interrupted or "burst" form. In the block mode, the low WCF (Write Forward Command), originating in the control and status test PCA, controls the time duration of 13192A/13193A

Figure 4-4. Ten-Character Generator and Write Clock (WC) Output in the X TALK (Continuous) Mode

the write test pattern output. This signal also initiates generation of the WRS (Write Reset) pulse. The WCF Gate signal triggers Block Delay one-shot U10A, direct-clears WRS Generator U12A, and is inverted to provide an enabling input to pin 4 of "nand" gate U5B.

4-30. The Block Delay one-shot responds to the . negative-going transition of the WCF leading edge by generating a low gate which holds the output of U5B pin 6 high

for 50 milliseconds. This high Block Control signal disables decade counter U7 (i.e. the counter is held in the reset-9 state) and inhibits WRS Delay one-shot U12B. U5B inverts this high signal to provide a low signal which inhibits "nor" gates U1A/B, U2A/B/C/D, and U3A/B, and keeps WC Delay one-shot U11A in the reset state. In other words, during the 50-millisecond interval of the Block Delay one-shot output, generation of write test patterns and write clock pulses is inhibited.

.

.

| $\Sigma$ Character one Bits | S2<br>Position | U7 Function<br>Activated  | *Σ-even Output<br>(U9 pin 5) |

|-----------------------------|----------------|---------------------------|------------------------------|

| . <u></u>                   | ODD            | Even Parity<br>Generation | 1                            |

| EVEN                        | EVEN           | Odd Parity Generation     | 0                            |

|                             | ODD            | Even Parity<br>Generation | 0                            |

| ODD                         | EVEN           | Odd Parity<br>Generation  | 1                            |

Table 4-2. Parity Bit Generation