# HP 12821A Disc Interface installation and service manual

### PRINTING HISTORY

The Printing History below identifies the Edition of this Manual and any Updates that are included. Periodically, Update packages are distributed which contain replacement pages to be merged into the manual, including an updated copy of this Printing History page. Also, the update may contain write-in instructions.

Each reprinting of this manual will incorporate all past Updates, however, no new information will be added. Thus, the reprinted copy will be identical in content to prior printings of the same edition with its user-inserted update information. New editions of this manual will contain new information, as well as all Updates.

To determine what software manual edition and update is compatible with your current software revision code, refer to the appropriate Software Numbering Catalog, Software Product Catalog, or Diagnostic Configurator Manual.

| First | Editi | on . |  |  |      |  |  |  |  | <br> |  |  |      |  |  | Jan | 198 | 0 |

|-------|-------|------|--|--|------|--|--|--|--|------|--|--|------|--|--|-----|-----|---|

| Ur    | date  | 1    |  |  | <br> |  |  |  |  | <br> |  |  | <br> |  |  | Jan | 198 | 2 |

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO. THE IMPLIED WARRANTIES OF MERCHANT-ABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another program language without the prior written consent of Hewlett-Packard Company.

## MANUAL UPDATE

MANUAL IDENTIFICATION

Title:

HP 12821A Disc Interface

Installation and Service Manual

Part Number: 12821-90006

UPDATE IDENTIFICATION

Update Number: 1 (January 1982)

This Packet also Includes:

THIS UPDATE GOES WITH:

First Edition January 1980

#### THE PURPOSE OF THIS MANUAL UPDATE

is to provide new information for your manual to bring it up to date. This is important because it ensures that your manual accurately documents the current version of the product.

#### THIS UPDATE CONSISTS OF

this cover sheet, a printing history page, all replacement pages, and write-in instructions (if any). Replacement pages are identified by the update number at the bottom of the page. A vertical line (change bar) in the margin indicates new or changed text material. The change bar is not used for typographical or editorial changes that do not affect the text. New pages to be added do not contain change bars.

#### TO UPDATE YOUR MANUAL

identify the latest Update (if any) already contained in your manual by referring to the Printing History Page (page ii). Incorporate only the Updates from this packet not already included in your manual. Following the instructions on the back of this page, replace existing pages with the Update pages and insert new pages as indicated. If any page is changed in two or more Updates, such as the Printing History Page which is furnished new for each Update, only the latest page will be included in the Update package. Destroy all replaced pages. If "write-in" instructions are included they are listed on the back of this page.

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

# TECHNICAL MANUAL UPDATE (12821-90006)

Note that "" indicates a changed page.

#### UPDATE

#### DESCRIPTION

1

A. Replace the following pages with the pages supplied.

i\*/ii\* 1-1\*/1-2\* iii\*/iv\* 1-3\*/1-4\* v\*/vi\* 2-1\*/2-2\* vii\*/viii\* 2-3\*/2-4\* ix\*/x\* xi\*

# SAFETY CONSIDERATIONS

GENERAL - This product and related documentation must be reviewed for familiarization with safety markings and instructions before operation.

#### SAFETY SYMBOLS

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect the product against damage.

Indicates hazardous voltages.

Indicates earth (ground) terminal (sometimes used in manual to indicate circuit common connected to grounded chassis).

#### WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

#### CAUTION

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

#### CAUTION

#### STATIC SENSITIVE DEVICES

Some of the semiconductor devices used in this equipment are susceptible to damage by static discharge. Depending on the magnitude of the charge, device substrates can be punctured or destroyed by contact or mere proximity to a static charge. These charges are generated in numerous ways such as simple contact, separation of materials, and normal motions of persons working with static sensitive devices.

When handling or servicing equipment containing static sensitive devices, adequate precautions must be taken to prevent device damage or destruction. Only those who are thoroughly familiar with industry accepted techniques for handling static sensitive devices should attempt to service the cards with these devices. In all instances, measures must be taken to prevent static charge buildup on work surfaces and persons handling the devices. Cautions are included through this manual where handling and maintenance involve static sensitive devices.

SAFETY EARTH GROUND - This is a safety class I product and is provided with a protective earthing terminal. An uninterruptible safety earth ground must be provided from the main power source to the product input wiring terminals, power cord, or supplied power cord set. Whenever it is likely that the protection has been impaired, the product must be made inoperative and be secured against any unintended operation.

BEFORE APPLYING POWER - Verify that the product is configured to match the available main power source per the input power configuration instructions provided in this manual.

If this product is to be energized via an auto-transformer (for voltage reduction) make sure the common terminal is connected to the earth terminal of the main power source.

#### SERVICING

#### WARNING

Any servicing, adjustment, maintenance, or repair of this product must be performed only by qualified personnel.

Adjustments described in this manual may be performed with power supplied to the product while protective covers are removed. Energy available at many points may, if contacted, result in personal injury.

Capacitors inside this product may still be charged even when disconnected from its power source.

To avoid a fire hazard, only fuses with the required current rating and of the specified type (normal blow, time delay, etc.) are to be used for replacement.

#### WARNING

#### EYE HAZARD

Eye protection must be worn when removing or inserting integrated circuits held in place with retaining clips.

#### PREFACE

This manual provides installation and service instructions for the HP 12821A, Disc Interface Card (DI). The 12821A is a single, logic circuit card used as the HP 1000 M/E/F Series hardware interface for the H-Series and CS80-Series disc drives operating under the control of either the RTE-IVB (92068A) or RTE-6/VM (92084A) Operating System Driver DVA 32 or DVM/DVN 33 respectively.

Other publications which should be available for reference when using this manual for the following purposes are:

#### General

-----

- 1) Disc Loader ROM Installation and Service Manual, HP Part No. 12992-90001

- 2) DVR/DVA 32 Reference Manual, HP Part No. 92068-90012 for H-Series disc drives

- 3) DVM/DVN 33 Reference Manual, HP Part No. 92084-90025 for CS80 Series disc drives

#### Diagnostics

\_\_\_\_\_

- 1) 12821-90002, Diagnostic Reference Manual

- 2) 91711B, Diagnostics And Verification Package, which includes the following:

- \* Diagnostics And Verification Reference Manual, HP Part No. 91711-90006 for System Processor, I/O Cards and Peripherals

- \* Integrated Controller Disc Utilities Reference Manual, HP Part No. 5955-4355 for H-Series disc drives

- \* CS80 External Exerciser Reference Manual, HP Part No. 5955-3462 for CS80-Series disc drives

Update 1

iv

#### Table of Contents

|   | SAFET | Y         | •     | •          | •          | •     | •    | •    | •    | •   | •   | •            | •          | •    | •  | •    | •  | • | •   | •  | • | • | • | • | • | 111  | L |

|---|-------|-----------|-------|------------|------------|-------|------|------|------|-----|-----|--------------|------------|------|----|------|----|---|-----|----|---|---|---|---|---|------|---|

|   | PREFA | CE .      | •     | •          | •          | •     | •    | •    | •    | •   | •   | •            | •          | •    | •  | •    | •  | • | •   | •  | • | • |   | • | • | •1v  | 7 |

|   | GLOSS | ARY.      | •     | •          | •          | •     | •    | •    | •    | •   | •   | •            | •          | •    | •  | •    | •  | • | •   | •  | • | • | • | • | • | ·ix  | 2 |

| 1 | INTRO | DUCI      | 10    | N          |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   |      |   |

|   | 1.1   | Des       | CT    | ipt        | :10        | n     | •    | •    | •    | •   | •   | •            |            | •    | •  |      |    | • |     | •  |   |   | • |   |   | 1-1  |   |

|   | 1.2   |           |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 1-1  |   |

|   | 1     | . 2 . 1   |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 1-1  |   |

|   | 1.3   | Pro       | du.   |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 1-2  |   |

|   | 1.4   |           |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 1-3  |   |

|   | 1.5   |           |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 1-3  |   |

|   | 1     | .5.1      |       | Pı         | c o d      | uc    | t    |      |      |     |     |              | •          |      |    |      |    |   |     |    |   |   |   |   |   | 1-3  | 3 |

|   |       | . 5. 2    |       | Ci         | lrc        | ui    | t    | Ca   | rd   | l   | •   | •            |            | •    | •  | •    | •  |   | •   | •  | • | • | • | • | • | 1-3  | 3 |

|   | 1.6   |           |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 1-4  |   |

|   | 1.7   |           |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 1-4  |   |

|   | 1.8   | Out       | pu    | t l        | 10 d       | es    |      |      | •    |     | •   |              |            |      | •  | •    | •  | • |     |    |   | • | • |   |   | 1-6  | ċ |

|   | 1.9   | Dat       | a     | Mo d       | i e        | (C    | 0 1  | tr   | 0]   | . 1 | 11: | Lp-          | Fl         | . op |    | ie t | :) | • |     |    | • |   |   |   |   | 1-7  | 7 |

|   | 1.10  | Co        | nf    | 121        | ıre        | . M   | lo d | le   | ((   | or  | ti  | :01          | . 1        | 11   | D- | -F1  | OP | C | 1 e | ar | ) | • |   |   | • | 1-7  | 7 |

|   | 1.11  | In        | рu    | t l        | 10 d       | es    |      | •    |      | •   | •   | •            | •          | •    | •  | •    | •  | • | •   | •  | • |   |   |   |   | 1-10 | ) |

|   | 1.12  | Da        | ta    | Mo         | d e        | (     | Co   | nt   | r    | 1   | F   | 1p           | <b>-</b> F | 10   | P  | Se   | t) |   |     | •  | • |   |   | • | 1 | -10  | ) |

|   | 1.13  |           |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | l-11 |   |

|   |       | Ma        |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 1-12 |   |

|   | 1     | . 14.     | 1     | ٠-,        | ía s       | te    | 7    | R.   | 3 6  | t   | Fı  | י<br>וחכ     | <u>.</u>   | OT   | 8  |      |    |   |     |    |   |   |   |   |   | 1-12 |   |

|   | ī     | . 14.     | 2     | F          | Rul        | es    |      | OI   | 100  | r   | 111 | 1g           | MI         | 1    | •  | •    | •  | • | •   | •  | • | • | • | • |   | 1-13 | 3 |

| 2 | INSTA | T. T. A 7 | י ד ח | N          |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   |      |   |

| - | 2.1   |           |       |            |            |       | _    |      | _    |     |     | _            | _          |      | _  | _    |    |   | _   |    |   |   |   |   |   | 2-1  | ı |

|   | 2.2   | Unt       | ac    | kir        | 1 2        | an    | ď    | Īπ   | 151  |     | £ : | Lon          | 1          |      |    |      |    |   |     |    |   |   |   |   |   | 2-1  | i |

|   | 2.3   | Che       | ck    | out        | •          |       | •    |      |      | •   |     |              | •          | •    |    |      |    |   |     |    |   |   |   |   |   | 2-2  | 2 |

|   | 2.4   |           |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 2-2  |   |

|   | 2.5   | Svs       | te    | m (        | Con        |       | 01   | 1 4  | ,    | ומ  | P   | ระ           | , 1 1      | c h  |    |      |    |   |     |    |   |   |   |   |   | 2-2  | , |

|   | 2.6   |           |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 2-3  |   |

|   | 2.7   | Int       |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   |      |   |

|   | 2 . 8 | Sys       | te    | m (        | ונים<br>פר | Su    | bs   | y s  | te   |     | Cl  | 1 <b>e</b> c | ko         | ut   | •  |      | :  | : | •   |    | : | : | • | : | • | 2-4  | • |

| 3 | PRINC | T D1 E    |       | OF         | 0.5        | T P   | A T  |      | N NT |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   |      |   |

| _ | 3.1   | T         |       | J          | UP         | - A   | A    | . 10 | , I  |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 3-1  |   |

|   | 3.2   | TH 2      |       | 1 1        | : []<br>]  | 01    |      |      | ٠,   | •   | •   | • • •        | •          | . •  | •  | •    | •  | • | •   | •  | • | • | • | • | • | 3-1  | L |

|   | 3.3   | _         |       |            |            |       |      |      |      |     |     |              |            |      |    |      |    |   |     |    |   |   |   |   |   | 3-1  |   |

|   | 3.3   | டாக       | יחח   | <b>e</b> 1 | 3.0        | . L 🗪 | CI   | : 1  | .n • | 710 |     | •            |            | -    | •  | •    | •  | - |     | •  |   |   |   | _ |   | 3-   | 4 |

Update 1

| 3 - 4   | Contro                     | ol Log         | gic     |       |              | •     | •    | •     | •   | •          | •  |     | •   | • | •  | •  |     | • | 3-1  |

|---------|----------------------------|----------------|---------|-------|--------------|-------|------|-------|-----|------------|----|-----|-----|---|----|----|-----|---|------|

| 3 -     | 4.1                        | Cont           | rol     | F1 1  | lp-          | Flo   | P    | an    | ď   | Lo         | gi | ٠,  |     | • | •  | •  |     | • | 3-1  |

| 3.      | . 4 . 2                    | Conti          | rol     | Wor   | -d           | Reg   | 1 9  | t e   | •   |            |    |     |     |   |    |    |     |   | 3-2  |

| 3       | . 4 . 3                    | Bus            | Tran    | sc e  | iv           | ers   | a    | nd    | C   | o n        | tr | 01  | Lin | e | La | 21 | ٠.  |   | 3-2  |

| 3.5     | Output                     | Dat            | a Re    | 915   | ite          | 7     |      | •     | . ` |            |    |     |     |   |    |    |     |   | 3-3  |

| 3.7     | Tabut                      | Data           | 941     | 0.1   |              | •     |      |       |     |            |    |     |     |   | •  | •  |     | Ī | 3-4  |

| 3.8     | Input The FI               | TROS           | 361     |       | •            | •     | •    | •     | •   | •          | •  | •   | •   | • | •  | •  | • • | • | 3-4  |

| 3.0     | .8.1                       | T              | • •     | • • • | •            | •     | •    | •     | •   | •          | •  | •   | •   | • | •  | •  | • • | • | 3-4  |

|         |                            | THEF           | 24 4 6  |       | , <u>u</u>   | •     | •    | •     | •   | •          | •  | •   | •   | • | •  | •  | • • | • | 3-4  |

| 3       | . 8 . 2                    | The            | 9403    | 10    | :            | •     | •    | •     | •   | •          | •  | •   | •   | • | •  | •  | • • | • | 3-4  |

| 3       | . 8 . 3                    | The            | DT F    | TFU   | , א          | ull   | er   | S     | •   | •          | •  | •   | •   | • | •  | •  | • • | • | 3-5  |

| 3.9     |                            | : Byt          | e Se    | Lec   | : t          | Log   | 10   |       | •   | •          | •  | • • | •   | • | •  | •  | • • | • | 3-7  |

| 3.10    | Outpu                      | it Da          | ta S    | ele   | ec t         | •     | •    | •     | •   | •          | •  | •   | •   | • | •  | •  | • • | • | 3-7  |

| 3.11    | Input                      | : Data         | a Re    | g 1 s | te           | r     | •    | •     | •   | •          | •  |     | •   | • | •  | •  |     | • | 3-7  |

| 3.12    | End                        | of Da          | ta D    | ete   | ct           | La    | gi   | C     |     |            | (  | Ll) | •   | • | •  | •  |     | • | 3-9  |

| 3.13    | Trans                      | smit           | Hand    | sha   | ıke          | Lo    | gi   | C     |     |            | (  | Ll) | •   | • | •  | •  |     | • | 3-9  |

| 3.14    | Hooks                      | smit :         | the     | Di    | ag           | nos   | 21   | C     | •   | •          | •  |     | •   | • | •  | •  |     |   | 3-9  |

| 3.15    | Recei                      | ive H          | ands    | hak   | Le           | Log   | 10   |       |     | •          | •  |     |     |   |    |    |     |   | 3-11 |

| 3.16    | The I                      | Last           | Byte    | In    | L            | ogi   | c    |       |     | •          |    |     |     |   |    |    |     |   | 3-13 |

| 3.17    | FIFO                       | Load           | Log     | 16    | -            |       | •    |       |     |            |    |     |     |   |    |    |     |   | 3-14 |

| 3.18    | FIFO                       | Unloa          | ad I    | , 1   | آ م ا        | •     | •    | •     | •   | •          | •  |     | •   | • | •  | •  | • • |   | 3-15 |

| 3.19    | Tage                       | Rupa           | 0       | T     |              | _ •   | •    | •     | •   | •          | •  | •   | •   | • | •  | •  | • • |   | 3-17 |

| 3.20    | Inter                      | Byte<br>rrupt  | Sau     |       | 8 -          | Wa a  | · •  | ·     | •   | •          | •  | •   | •   | • | •  | •  | • • |   | 3-19 |

| 3.21    | Tanus                      | Mul            | -4-1    | 2 - 4 | ,            | rue a | -    | LU    | 8 - | C          | •  | •   | •   | • | •  | •  | • • |   | 3-10 |

|         | Input                      | Mul            | C1 P1   | ex e  | 1 5          | •     | ٠.   | •     | •   | ٠,         | •  | •   | •   | • | •  | •  | • • |   | 3-13 |

| 3.22    | Laput                      | Mul<br>Flag    | tipi    | ex e  | IT           | Ena   | DI   | e<br> | Lo  | <b>g</b> 1 | C  | •   | •   | • | •  | •  | • • |   | 3-19 |

| 3.23    | Clear                      | Flag           | g De    | tec   | :t           | Fl 1  | p-   | FL    | op  |            | •  | •   | •   | • | •  | •  | • • |   | 3-20 |

| 3 • 2 4 | End                        | of Da          | ta T    | ran   | ısī          | er    | Fl   | 1p    | -F  | 10         | P  | •   | •   | • | •  | •  | • • |   | 3-20 |

| 3.25    | Servi                      | ice Re         | e que   | st    | Lo           | gio   |      | •     | •   | •          | •  | •   | •   | • | •  | •  | • • |   | 3-21 |

| 3.26    | Flag                       | ice Ro<br>Buff | er F    | 111   | ) <b>-</b> F | Lop   | )    | •     | •   | •          | •  |     | •   | • | •  | •  |     |   | 3-22 |

| 3 • 27  | Flag                       | Logic          | ٠.      |       |              |       |      |       |     |            |    |     |     |   |    |    |     |   | 3-23 |

| 3.28    | Inter                      | rupt           | Req     | ues   | ιt           | Log   | ic   |       | •   | •          | •  |     | •   | • |    | •  |     |   | 3-25 |

| 3.29    | Inter                      | face           | C1 e    | ar    | 10           | 0 8   | 11 c | ro    | s e | co         | nd | Tí  | mer |   |    | •  |     |   | 3-26 |

| 3.30    | Inter                      | face           | C1 e    | ar    | F1           | in-   | F1   | 00    |     | •          | •  |     |     |   |    |    |     |   | 3-26 |

| 3.31    | Paral                      | 11-1           | Po 1 1  | Co    |              |       | T.   | ~ ~   | 1 6 | •          |    |     |     | • | ·  | •  |     |   | 3-26 |

| 3.32    | Bus                        | llel<br>Addre: | 33 5    | u i t | ch           |       | ٠    |       | •   |            | :  |     |     | : | :  | •  | • • |   | 3-27 |

| 3.33    | Bu e                       | Addre          |         | 0.00  |              | a + a | -    | •     | •   | •          | •  |     |     |   | Ĭ  | •  |     |   | 3-27 |

| 3.34    | Conn                       | and D          |         | io my |              | 1.0   | •    | •     | •   | •          | •  | •   | •   | • | •  | •  | • • |   | 3-27 |

| 3.35    | Comma                      | and Do         | 2000    |       | .og          | 16    | •    | •     | •   | •          | •  | •   | •   | • | •  | •  | • • |   | 3-27 |

| 3.33    | Syste                      | 3 m CO         | itro    | TTE   | 1 .          | •     | •    | •     | •   | •          | •  | •   | •   | • | •  | •  | • • |   | 3-27 |

|         | ENANCE                     |                |         |       |              |       |      |       |     |            |    |     |     |   |    |    |     |   |      |

| 4 • 1   | Introd                     | luction        | o n     |       |              | •     | •    | •     | •   | •          | •  |     | •   | • | •  | •  |     | • | 4-1  |

| 4.2     | Safety                     | , Pre          | caut    | 100   | iS           | •     | •    | •     | •   | •          | •  |     | •   | • | •  | •  |     | • | 4-1  |

| 4.3     | Preven                     | tive           | Ma i    | nte   | na           | nce   | 1    | •     | •   |            |    |     | •   |   | •  |    |     |   | 4-1  |

| 4 . 4   | Preven<br>Troubl<br>Diagno | esho           | o t i o | g e   |              | •     | •    | •     |     |            | •  |     | •   | • |    |    |     |   | 4-2  |

| 4.5     | Diagno                     | stic           | Tes     | ts    |              |       |      |       |     |            |    |     |     |   |    | •  |     |   | 4-2  |

| 4.6     | Replac                     | emen           | e Pr    | 000   | du           | T.    |      |       | •   |            |    |     |     |   |    |    |     | Ĭ | 4-2  |

vi Update 1

#### List of Illustrations

| M | u.         | 1          | t:         | į.         | <b>-</b> D | i  | . s | c |   | С | 0 1 | a f | 1   | g | u  | r          | a 1        | : : | Lo  | ם   | L | •          |            |     | • | ,        |   | •          |     |   | •   |    |     |   | • | • | • |     | 1 - | . 2 |  |

|---|------------|------------|------------|------------|------------|----|-----|---|---|---|-----|-----|-----|---|----|------------|------------|-----|-----|-----|---|------------|------------|-----|---|----------|---|------------|-----|---|-----|----|-----|---|---|---|---|-----|-----|-----|--|

| В | 1          | 0 (        | <b>c</b> 1 | k          | I          | ì  | a   | g | r | a |     | ,   | D   | 1 | S  | c          | •          | Ιı  | t   | e   | r | fa         | 10         | : e |   | Dà       | t | a          | P   | a | t h | s  | •   |   | • | • | • |     | 1-  | 6   |  |

| U | n          | ΡĄ         | a (        | c l        | دe         | d  | l   | D | a | t | а   | 1   | o   | r | ₪. | a          | t          |     | •   | •   |   | •          | •          | •   | • | ,        |   | •          |     |   | •   | •  | •   |   | • | • | • |     | 1-  | 7   |  |

| P | a          | ا ء        | k (        | e          | i          | I  | )a  | t | a |   | Mo  | ò   | i e |   | •  |            | •          |     |     | •   |   | •          | •          |     | • |          |   | •          |     |   |     | •  |     |   |   | • | • |     | 1 - | . 7 |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

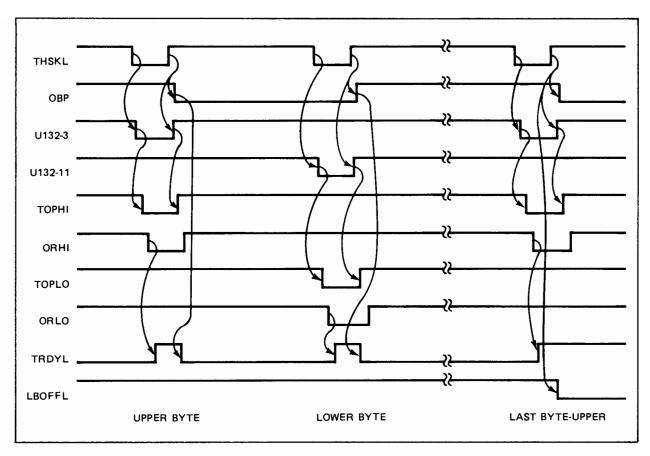

| Ü | P          | P          | <b>e</b> : | ľ          | E          | Зy | t   | e |   | F | I   | F ( | )   | U | n  | 1          | 0 8        | 10  | 1   | n   | g | •          | •          | •   | • |          | • | •          | •   |   | •   | •  | •   |   | • | • | • |     | 3-  | 7   |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

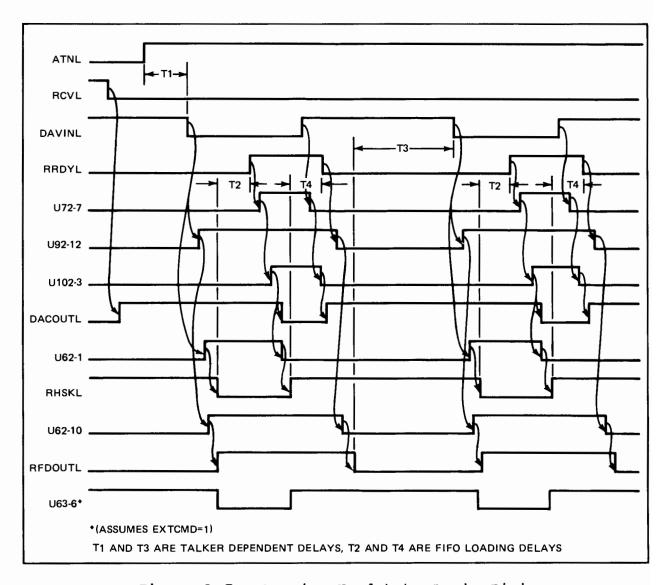

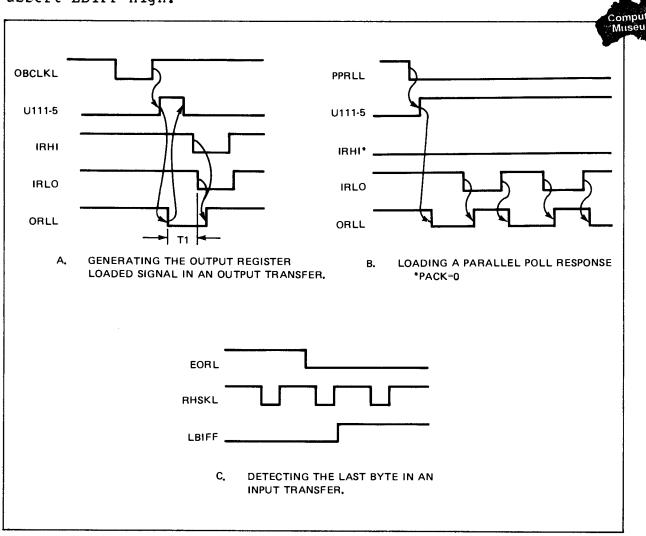

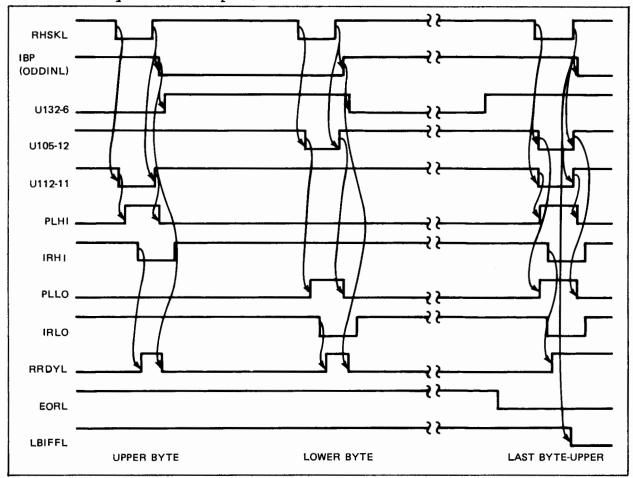

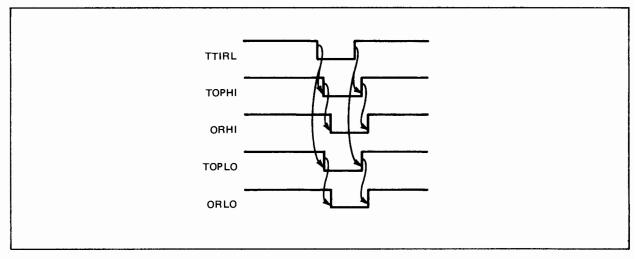

| Τ | r          | <b>a</b> 1 | 1          | <b>S</b> 1 | n í        | t  | :   | H | a | n | d:  | s h | ı a | k | e  |            | L          | 9   | į   | . c |   | T          | į          | ıí  | n | g .      |   | •          | •   |   | •   | •  | •   |   | • | • | • | 3.  | - 1 | 0   |  |

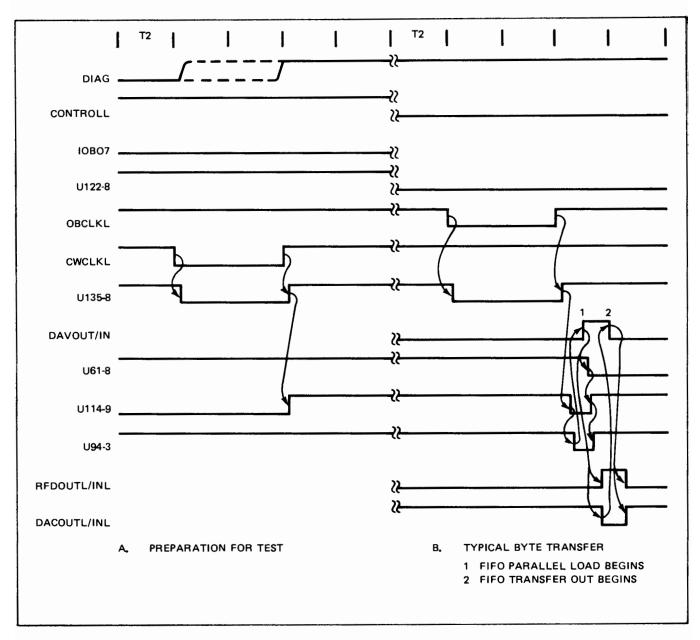

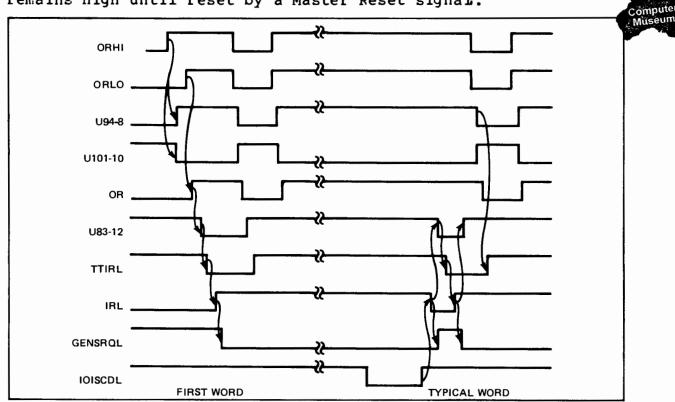

| D | 1          | <b>a</b> § | g 1        | 1          | 9          | t  | 1   | c |   | T | 11  | n ź | 'n  | g |    | L          | 0 8        | 3   | Ĺc  | •   |   | •          | •          | •   | • | ٠,       | • | •          | •   |   | •   | •  | •   |   | • | • | • | 3-  | -1  | 1   |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

| L | <b>a</b> : | s t        | t          | 1          | Зу         | t  | e   |   | I | n | 1   | Lo  | g   | 1 | c  |            | •          | •   | •   | •   |   | •          | •          | •   | • | •        | • | •          | •   |   | •   | •  | •   |   | • | • | • | 3-  | - 1 | 3   |  |

| F | I          | (          | 0          | 1          | Lo         | a  | d   |   | L | 0 | g:  | Ĺ   | :   | ( | P  | <b>a</b> ( | c i        | ٤ ( | d   | l   | D | <b>a</b> 1 | t a        | l.  | F | 0 1      |   | at         |     | I | n p | uţ | :   |   |   |   |   |     |     |     |  |

|   | 1          | Ē 1        | •          | ) I        |            | E  | lu  | S | ) |   | •   | •   | •   | • |    | ٠          | ,          | •   | •   | •   | • |            | •          | •   | • | •        | • | •          | •   |   | •   | •  | •   |   | • | • | • | 3 - | -1  | 4   |  |

| F | I          | (          | )          | 1          | Lo         | a  | d   |   | L | 0 | g:  | Ĺ   | :   | ( | L  | 0          | <b>a</b> ( | i   | C   | )u  | t | p١         | ıţ         | :   | D | a t      | a | F          | l e | g | 19  | te | ľ   |   |   |   |   |     |     |     |  |

|   | :          | Ĺ          | 1          | t          | •          | F  | I   | F | 0 | S | )   | •   | •   |   | •  |            | •          | •   | •   | •   |   | •          | •          | •   | • | •        | • | •          | •   |   | •   | •  | •   |   | • | • | • | 3-  | - 1 | 5   |  |

| F | IJ         | (          | )          | Į          | Jn         | 1  | 0   | a | d |   | L   | 9   | įi  | C |    | (          | Pa         | 10  | : k | e   | d | 1          | ) a        | t   | a | 1        | 0 | r          | 1 8 | t |     |    |     |   |   |   |   |     |     |     |  |

|   | (          | Ìι         | 1 (        | į          | u          | ιt |     | t | 0 |   | Βι  | 1 9 | ;)  |   | •  |            | •          | •   | •   | •   |   | •          | •          | •   | • | •        | • | •          | •   |   | •   | •  | •   |   | • | • | • | 3 - | -1  | 6   |  |

| F | I!         | (          | 0          | Į          | Jn         | 1  | 0   | a | d |   | L   | 9   | įi  | C |    | (          | Pá         | 1   | : k | e   | d | 1          | <b>)</b> 8 | t   | a | 1        | 0 | r          | a   | t | ,   | F  | F   | 0 | S |   |   |     |     |     |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

| I | n          | PΙ         | u t        | t          | M          | ſu | 1   | t | 1 | P | 1   | 2 X | e   | ľ |    | E          | n 8        | ı t | 1   | . e |   | L          | 9          | įi  | C | •        | • | •          | •   |   | •   | •  | •   |   | • | • | • | 3.  | - 1 | 9   |  |

| С | 1          | 2 8        | 2 7        | •          | I          | 1  | a   | g |   | D | e i | : € | C   | t |    | F.         | 1          | ļ   | -   | F   | 1 | 0 1        | •          | (   | A | <b>s</b> | u | <b>m</b> € | 2   | P | a c | k. | • 1 | ) | • | • | • | 3.  | -2  | 0   |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • | • | 3.  | -2  | 1   |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     | s  |     |   |   |   |   |     |     |     |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

| F | 1          | 1 8        | 3          | 1          | 3u         | ι£ | f   | e | ľ | _ | F.  | 1   | P   | 7 | F. | 1          | 0 [        | •   | •   | •   |   | •          | •          | •   | • | •        | • | •          | •   |   | •   | •  | •   |   | • | • | • | 3•  | -2  | 3   |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   |            |     |   |     |    |     |   |   | • |   |     |     |     |  |

| P | <b>a</b> : | . 1        | <b>a</b> ] |            | L e        | 1  |     | P | 0 | 1 | 1   | I   | -0  | g | 1  | C          | •          | •   | •   | •   |   | •          | •          | •   | • | •        | • | •          | •   |   | •   | •  | •   |   | • | • | • | 3.  | - 2 | 6   |  |

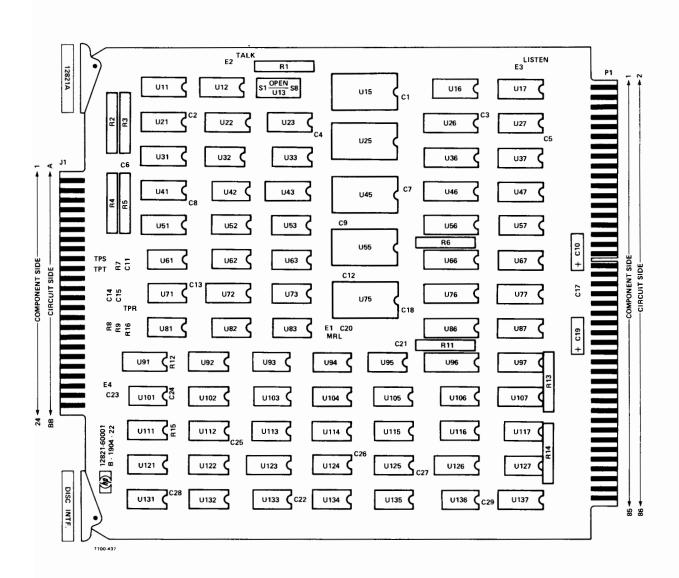

| P | 8          | <b>r</b> 1 | t s        | 3          | I          | ٥٠ | C   | 8 | t | 1 | 0 1 | 1   | D   | i | 8  | g          | r          | 1   | 1   | •   |   | •          | •          | •   | • | •        | • | •          | •   |   | •   | •  | •   |   | • | • | • |     | 4-  | ٠3  |  |

|   |            |            |            |            |            |    |     |   |   |   |     |     |     |   |    |            |            |     |     |     |   |            |            |     |   |          |   | r          |     |   |     |    |     |   |   |   |   |     |     |     |  |

|   | (          | 30         | ) 1        | 1          | 1 6        | C  | t   | 1 | 0 | п | S   | •   | •   |   | •  |            | •          |     | •   | •   |   | •          |            | •   | • |          |   |            |     |   | •   |    |     |   | • |   |   |     | 4-  | ٠6  |  |

#### List of Tables

| Disc Cable | 25     |        |          | • | • | • | • | • | • | • | • | • | . 1-1 |

|------------|--------|--------|----------|---|---|---|---|---|---|---|---|---|-------|

| Interrupt  | Source | e, Mas | sk Logic | • | • | • | • | • | • | • | • | • | .3-18 |

| Reference  | Parts  | List   |          | • | • | • | • | • | • | • | • | • | . 4-4 |

| Reference  | Parts  | List   | Cont'd.  | • | • | • | • | • | • | • | • | • | . 4-5 |

viii

Update 1

#### GLOSSARY

This is a basic list of mnemonics and acronyms which will be helpful in using this manual. With your addition of an appropriate prefix or suffix (such as EN, IN, OUT, etc. to indicate enable, input, output) this basic list can be leveraged to cover those situations likely to arise in the use of this manual:

| MNEMONIC     | DESCRIPTION                           |

|--------------|---------------------------------------|

|              |                                       |

|              | <del></del>                           |

| ADD          | Address Detected                      |

| ATNL         | Attention, Low True                   |

| ATNEN        | Attention Enable                      |

| ATNIN        | Attention In                          |

| CHSEL<br>CIC | Channel Select                        |

|              | Controller-In-Charge                  |

| CLCSCL       | Clear Control Select Code, Low True   |

| CLFSCL       | Clear Flag Select Code, Low True      |

| CONTROL      | Control                               |

| CONTROLL     | Control, Low True                     |

| CRSL         | Control Reset, Low True               |

| CWCLKL       | Control Word Clock, Low True          |

| CS80-Series  | HP Model 7908x, 7911x, 7912x or 7935x |

|              | disc drive using HP-IB controller     |

| DACIN        | Data Accepted In                      |

| DACOUTL      | Data Accepted Out, Low True           |

| DAVINL       | Data Valid In, Low True               |

| DAVL         | Data Valid, Low True                  |

| DAVOUTL      | Data Valid Out, Low True              |

| DIAG         | Diagnostic                            |

| DSEL         | Data Word Selected                    |

| EDT          | End Data Transmission                 |

| ENFL         | Enable Flag, Low True                 |

| EOIIN        | End Or Indentify IN                   |

| EOIL         | End Or Identify, Low True             |

| EOILBO       | End Or Identify Last Byte Out         |

| EORL         | End Of Record, Low True               |

| EDT          | End Data Transfer                     |

| FLAGL        | Flag, Low True                        |

| GENSRQL      | Generate SRQ, Low True                |

| H-Series     | HP Model 7906H, 7920H, 7925H or 9895A |

|              | disc drive using HP-IB controller     |

Update 1

```

IBP

Input Byte Pointer

ICD

Another name for H-Series disc drives

Serial Input Enable, Low True

IESL

Interface Clear Enable

IFCEN

Interface Clear Input

IFCIN

IFCL

Interface Clear, Low True

IFCOUT

Interface Clear Output

IOI

I/O Input

IOISCDL

I/O Input of Data

I/O Output

100

IRHI

Input Register full-upper byte, Low True

IRL

Input Register Loaded

IRLEN

Input Register Loaded Enable

IRLO

Input Register full-lower byte, Low True

Listen

LBIFF

Last Byte In Flip-Flop

LBOFF

Last Byte Out Flip-Flop

LF

Line Feed

Master Reset

MR

NCLFL

No Clear Flag, Low True

NDACL

Not Data Accepted, Low True

NRFDL

Not Ready For Data, Low True

O/E

Odd-Even

OBCLKL

Output Byte Clock, Low True

OBP

Output Byte Pointer

ODDIN

Odd IN

OR

Output Ready

OREL

Output Register Empty, Low True

ORHI

Output Register full-upper byte FIFO

ORLL

Output Register Loaded, Low True

ORLO

Output Register Full-Lower Byte and Tag FIFOs

PACK

Enable Packing

PLHI

Parallel Load-upper byte

PLLO

Parallel Load-lower byte

PP

Parallel Poll

PPC

Parallel Poll Conduct

PPE

Parallel Poll Enable

PPRL

Parallel Poll Response, Low True

Parallel Poll Response Load, Low True

PPRLL

RCV

Receive

Remote Enable, Low True

RENL

RFDIN

Ready For Data In

RFDOUTL

Ready For Data Out, Low True

Receive Handshake, Low True

RHSKL

RRDYL

Receive Ready, Low True

```

| SETFLG<br>SRQL | Set Flag<br>Service Request, Low True         |

|----------------|-----------------------------------------------|

| SSEL           | Status Select                                 |

| SYSCTL<br>T    | System Controller<br>Talk                     |

| THSKL          | Transmit Handshake, Low True                  |

| TOPHI          | Transfer Out Parallel-Upper Byte FIFO         |

| TOPLO          | Transfer Out Parallel-Lower Byte and Tag FIFO |

| TRDYL          | Transmit Ready, Low True                      |

| TTIRL          | Transfer To Input Register, Low True          |

| TTSL           | Transfer To Stack, Low True                   |

| XMITL          | Transmit, Low True                            |

INTRODUCTION CHAPTER 1

#### 1.1 Description

The HP 12821A is HP's implementation of IEEE Standard 488-1978 conforming to the Higher Speed Operations Guidelines of paragraph 5.2.3 to provide high speed, bidirectional interchange of digital data between the computer and its disc drive.

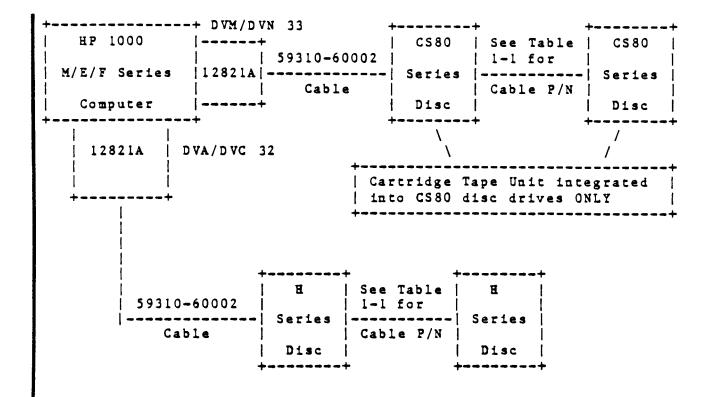

Both the H-Series (7906H, 7920H, 7925H, 9895A) and the CS80-Series (7908x, 7911x, 7912x, 7935x) disc drives are supported on the 12821A. This compatibility extends to the integrated Cartridge Tape Unit found in certain models of the CS80-Series disc drives (7908x, 7911x and 7912x]. While both the H-Series and CS80-Series disc drives are supported under RTE=6/VM, only the H-Series discs are supported under RTE-IVB. See Figure 1-1 for representative Multi-Disc configuration.

#### 1.2 Multi-Disc Configurations

Each 12821A will support either two H-Series or four CS80-Series disc drives (maximum). However, when both series disc drives are interfaced to the same computer, each series must be configured on a separate interface, each with its own driver.

#### 1.2.1 Interconnection Disc Cabling

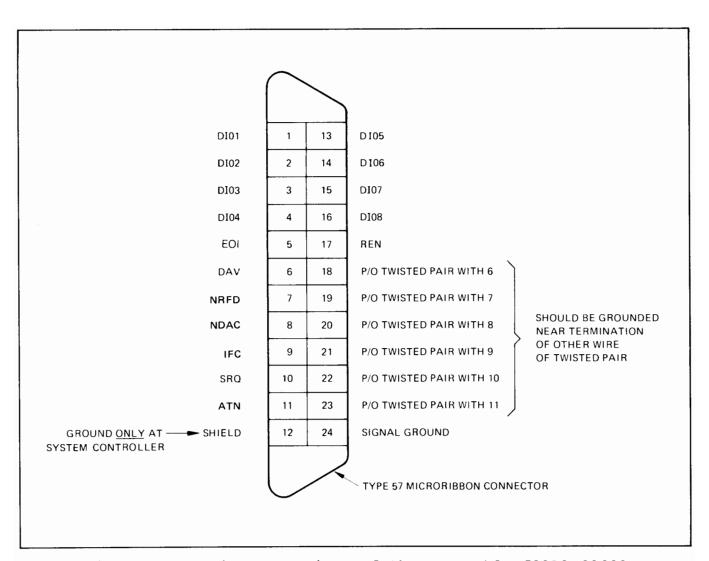

The disc drive is supplied with a standard 4 meter cable used to connect the DI. Table 1-1 lists the HP supported interconnection cables used to connect additional disc drives (either series):

Update 1 1-1

Figure 1-1 Multi-Disc Configuration

#### 1.3 Product Contents

The 12821A Disc Interface product consists of:

- 1) Disc Interface Card, HP Part No. 12821-60001.

- 2) HP-IB Cable Assembly, HP Part No. 59310-60002.

- 3) Disc Interface Installation And Service Manual, HP Part No. 12821-90006.

- 4) 12992 Loader ROM Installation Manual, HP Part No. 12992-90001.

- 5) 12992H, Disc Loader ROM (for H-Series disc drive only).

-0R-

6) For CS80-Series, Option 001 is ordered (deletes item 5) and 12992J, Disc Loader ROM is ordered as a line item.

#### 1.4 Related Items

The following items are not included in 12821A component shipments but are included in HP 1000 Computer System shipments. When purchasing a component product or system or adding to or upgrading a previously purchased system, these items will be needed (as indicated) for typical system operation:

- Software Driver DVA/DVC 32, HP Part No. 92067-16553 for H-Series disc drive. Included with the RTE-IVB (92068A) or the RTE-6/VM (92084) Operating System.

- 2) Software Driver DVM/DVN 33, HP Part No. 92084-16650, for CS80 Series disc drive. Included in the RTE-6/VM (92084A) Operating System.

- 3) HP-IB bus cables (see Table 1-1) for multi-disc installation.

- 4) 12992J, Disc Loader ROM for CS80-Series disc drives (see item 6, Related Items above).

- 5) 24998-14002, HP 1000 Computer System Diagnostic Library, supplied with shipments of HP 1000 Systems.

- 6) 91711B, Diagnostics And Verification Package, supplied with current shipments of HP1000 Systems.

#### 1.5 Identification

#### 1.5.1 Product

Five digits and a letter suffix (12821A in this case) are used to define and identify HP products used with HP computers. The five digits identify the product while the letter indicates the revision level of the product.

#### 1.5.2 Circuit Card

The interface circuit card assembly is further identified by a part number marked on the card. In addition to this a letter and a date code consisting of four digits are placed below the part number.

Update 1 1-3

The letter identifies the etched circuit on the card. The four-digit series code identifies the electrical characteristics of the loaded circuit card:

12821-60001 A-1926

If this series code does not exactly agree with the series code on the title page of this manual, there are differences between your circuit card and the one described in this manual. These differences are covered either in manual supplements (accompanying this manual) or the supplements are available through the nearest HP Sales and Service Office (listed in the back of this manual).

#### 1.6 Power and Environmental Requirements

The 12821A operating temperature range is 0 to 55 degrees Celsius. Power requirements are:

| SUPPLY  | MAX. CURRENT |

|---------|--------------|

| VOLTAGE | REQUIRED     |

| +30     | NONE         |

| +12     | NONE         |

| +5      | 3 · 3 4 A    |

| -2      | 0 • 1 0 A    |

| -12     | NO NE        |

#### 1.7 Operation

The 12821A architecture has been optimized for DMA transfer. However, this does not inhibit the ease of interrupt-driven transfers of small data buffers. The DI operates under control of either RTE-IVB (92068A) or RTE-6/VM (92084) operating system drivers making efficient data transfers approaching a full megabyte per second without user intervention (user transparency). To achieve this high transfer rate, the DI is preloaded with seven unit resistive loads. Because drivers are device specific routines, the following drivers will be used with the indicated Series disc:

\*DVA/DVC 32 for H-Series disc drives \*DVM/DVN 33 for CS80-Series disc drives

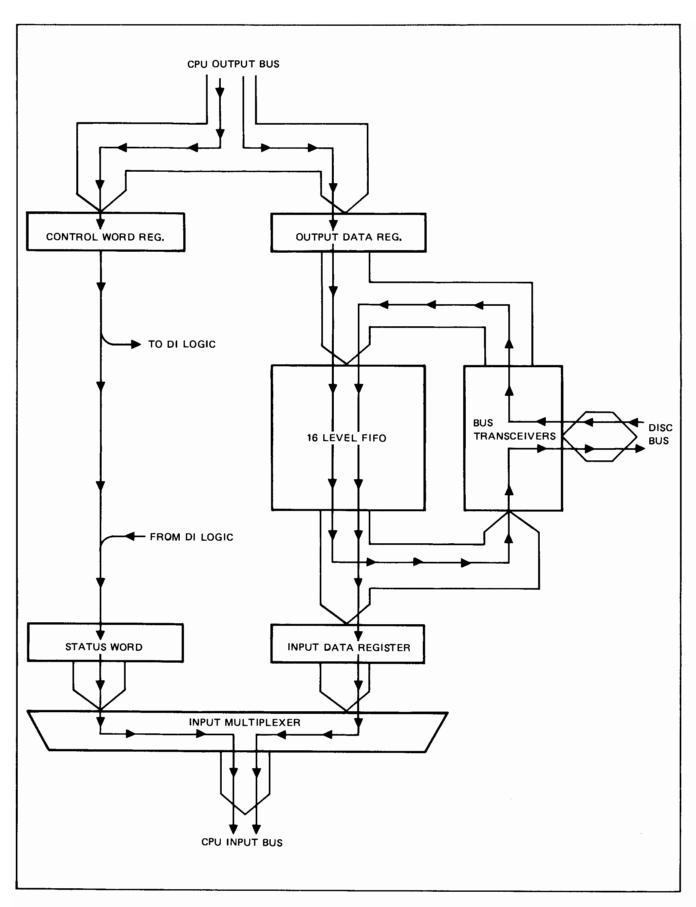

Figure 1-2. Disc Interface Data Paths Block Diagram

#### 1-9. FUNCTIONAL DESCRIPTION

The HP 12821A Disc Interface PCA architecture has been optimized for DMA transfer; however, interrupt-driven transfers of small data buffers are easily performed. The PCA operates under control of a software driver (DVA 32) supplied with the operating system, thus the transfer method is transparent to the user. The PCA is capable of transferring data up to a full one megabyte rate. To achieve this transfer rate the PCA is preloaded with seven unit resistive loads.

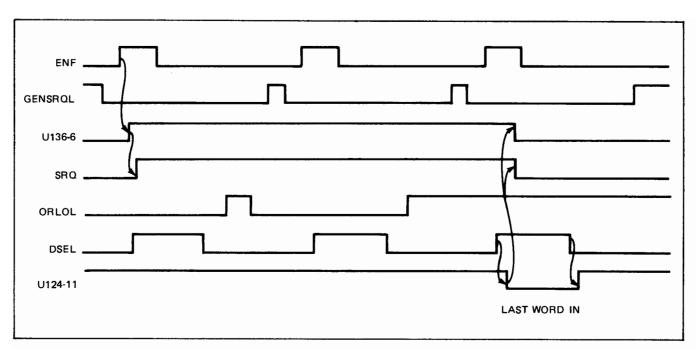

The Disc Interface (DI) in the Data Mode is bi-directional, data may be transfered from the CPU or memory to a disc or from a disc to the CPU or memory. The DI is defined to be a talker when transferring data from the computer to the disc and to be a listener when transferring data from the disc to the computer. In addition to the Data Mode the CPU can place the DI in the Configure Mode as a talker or the Status Mode as a listener.

Figure 1-2 is a functional block diagram showing the data paths within the DI. Information from the computer I/O bus can be seen to have two possible destinations the Control Word Register (Configure Mode) or the Output Data Register (Data Mode). The Control Word sets up the DI logic and alerts the disc that data is to be transmitted. When the disc acknowledges the request and is ready to receive, the data is processed through the FIFO and the tranceivers to the disc. To obtain data from the disc the DI must first be set up as a talker to inform the disc that data is going to be requested. When the disc acknowledges the commands the DI is then made a listener and the data transfer takes place through the Transceivers, FIFO, Input Data Register, and Input Multiplexer to the computer.

The key to the high transfer rate of the DI is the 16 word FIFO buffer. The FIFO can be loaded from the Output Data Register when the DI is a talker or from the transceivers when a listener. Data from the computer, being 16 bits wide, is loaded directly into the FIFO, while byte data from the disc can be packed two bytes per word.

Similarly, data out of the FIFO can be sent to the computer from the Input Data Register when DI is a listener, or to the disc from the transceivers when DI is a talker. FIFO words can be unpacked to form two 8-bit bytes. The routing of data into and out of the FIFO is done by Tri-state logic. If packing is used the upper byte of each FIFO word is the first to be sent or received. If no packing is specified, the lower byte FIFO is always selected.

Data for the computer is selected by the Input Multiplexer. The input mode will determine whether the Input Data Register or the Status Word will be read by the computer.

#### 1-10. OUTPUT MODES

The formats for the Data Mode and the Configure Mode are shown in the following paragraphs. Data output to the DI will be received by Output Data Register or the Control Word Register depending on the previously selected mode. The Control Word Register (Configure Mode) is selected by clearing the Control Flip-Flop.

#### 1-11. Data Mode (Control Flip-Flop set)

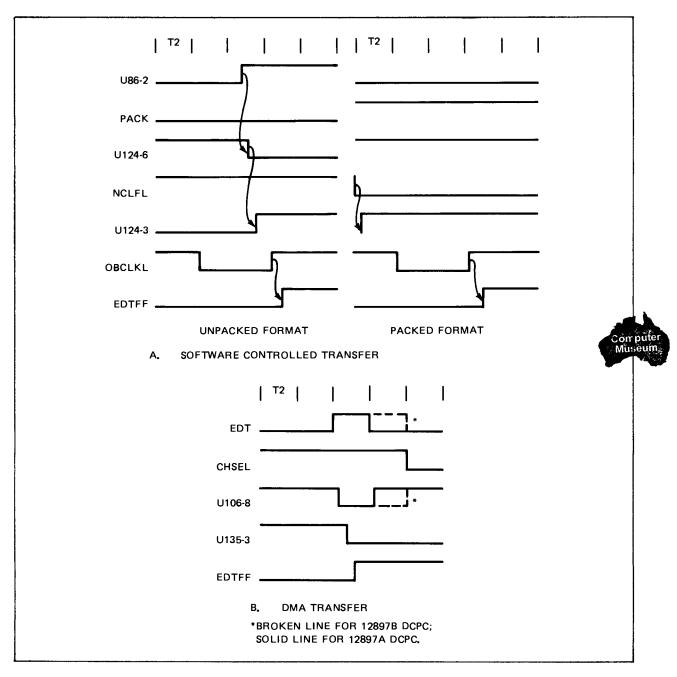

Data can be output to the DI in two formats, packed or unpacked. In general, the unpacked format will be used when outputting less than 17 bytes of commands and/or data in a software controlled transfer. The packed format is most often used when outputting more than 17 bytes of data in a DMA transfer.

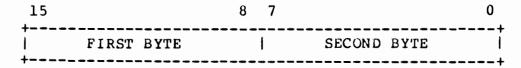

The unpacked data output format is shown in Figure 1-3.

| 15  |   | 10 | •   | •   | • |           | 0 |

|-----|---|----|-----|-----|---|-----------|---|

| LBO | х |    | EOI | ATN | ł | DATA BYTE | ĺ |

Figure 1-3. Unpacked Data Format

Bits 0-7 contain the data byte, while bits 8 and 9 contain the values of the disc ATN and EOI lines to be associated with this data. Note that this format allows disc commands (ATN=1) and data (ATN=0) to be mixed in any order within the FIFO.

Bits 10-14 are ignored by the DI in the unpacked format. Bit 15 signals to the DI that this is the last byte of the current output string. (See description of LBO.)

The packed data output format is shown in Figure 1-4.

Figure 1-4. Packed Data Format

Here two 8-bit bytes are contained within the word. The values of ATN and EOI associated with each byte are determined by two bits of the Control Word Register (see paragraph 1-12).

#### 1-12. Configure Mode (Control Flip-Flop Clear)

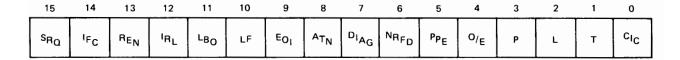

The data format of the Control Word Register is shown in Figure 1-5.

#### Figure 1-5. Control Word Format

Note that each bit has a specific function, and that no multibit encoding is used. The functions of each Control Word Register bit are as follows:

CIC (Controller In Charge, Bit 0) - tells the DI that it is currently controlling the disc.

T (Talk, Bit 1) - indicates that the DI a talker to the disc

L (Listen, Bit 2) - indicates that the DI a listener (from disc)

Pack (Enable Packing, Bit 3) - indicates that the packed data format is to be used for input or output.

O/E (Odd-even, Bit 4) - If set, indicates that for the current Packed Output operation an odd number of bytes is to be output to the disc (i.e., the second byte of the last word will not be sent). For the definition of "last word" see the description of LBO control bit.

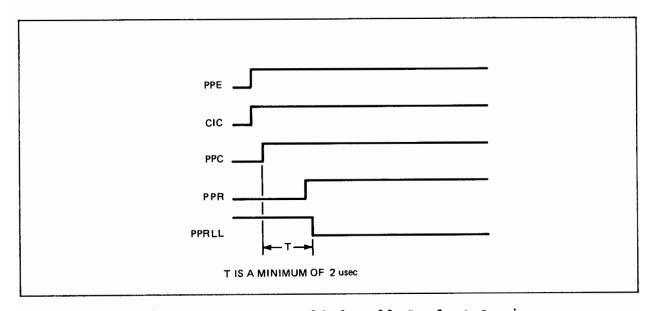

PPE (Parallel Poll Enable, Bit 5) - sets ATN and EOI on the bus, indicating that a Parallel Poll is being conducted. T and L must also be set for a parllel poll. After 2 microseconds, the DI looks for a response. When the response occurs it is automatically loaded into the FIFO.

NRFD (Not Ready for Data, Bit 6) - sets the corresponding line on the bus, indicating that the DI is not ready to receive data. This function is required when the DI has been receiving data from a disc and now wishes to untalk the device. NRFD will prevent the disc from placing any further data on the bus while the DI is being reconfigured to talk and the untalk command is being loaded into the FIFO.

DIAG (Diagnostic, bit 7) This bit is used by the diagnostic program. When set, this bit enables the diagnostic program to circle data from the FIFOs thru the transceivers back into the FIFOs.

ATN (Attention, Bit 8) - in the Packed output mode, specifies the value of the bus Attention line. The CIC bit in the control register must also be set.

EOI (End or Identify, Bit 9) - in the Packed output mode, specifies that the last byte sent will be tagged with EOI (see following description of LBO).

when the DI is inputting, EOI specifies that reception of a byte tagged with EOI will set the EOR (End of Record) Flip-Flop. EOR will generate NRFD, indicating to the disc that the DI is no longer ready to receive data. A tag indicating that this is the last word of the current input transfer is placed in the FIFO with the data. When this word has been read by the CPU the DI flag will be set. Any byte signaling EOR will automatically be loaded into the lower byte of the FIFO. Thus if an odd number of bytes are received, the EOR byte will be put in both halves of the FIFO and appear twice in memory. This mechanism is necessary to insure that an odd-numbered byte tagged with EOI will be sent to the CPU. The possible ambiguity of a double last byte in memory can be resolved by reading the O/E bit in the DI Status word.

LF (Line Feed, Bit 10) - enables the line feed detector to set EOR if a line feed is received by the DI. (The results of EOR are the same as described above).

LBO (Last Byte Output, Bit 11) - causes the DI flag to be set when the last byte of the current output transfer has been accepted by the disc.

The last word of an output transfer is signalled to the DI in either of two ways. If a DMA transfer is occurring, the DCPC will automatically signal when the last word is output. This tag will be placed in the FIFO along with the data word.

If the data is being output via software (in the unpacked mode), bit 15 of the data word will indicate to the DI that this word is the last of the current transfer. If the data is output in the packed format the last word is indicated by outputing the word with an OTA DI instruction rather than outputing with an OTA DI,C instruction.

If the output data format is packed, the last byte of the transfer will be the byte of the last word specified by the O/E bit of the Control Word Register (Bit 4). If the output data format is unpacked, the lower byte is automatically assumed to be the last byte.

IRL (Input Register Loaded, Bit 12) - will cause the DI flag to be set when the Input Data Register is loaded. If packing is disabled, reception of one data byte from the disc will load the register; if packing is enabled, 2 bytes must be received. The IRL interrupt is useful for notifying the software that a Parallel Poll response has been received.

REN (Remote Enable, Bit 13) - determines the state of the disc REN line. The system controller switch must be set on the DI for this signal to be output to the disc.

IFC (Interface Clear, Bit 14) - the positive going transition of this bit will generate a 100 microsecond IFC signal to the disc. The System Controller switch must be set on the DI for this signal to be generated.

SRQ (Service Request, Bit 15) - allows any SRQ received by the DI to set the DI flag. The DI must be Controller.-In-Charge.

The Control Flip-Flop is cleared by the CPU backplane signal CRS, which occurs at power-up, or when the "PRESET" button is pressed and also when a CLC 0 instruction is executed.

#### 1-13. INPUT MODES

Data input from the DI will come from either the Input Data Register or the Status Word, depending upon the previously selected mode. The Status Mode is selected by clearing the DI Control Flip-Flop; input will then be the Status Word. (Reading status will not change the mode of the DI.)

Similarly, when the DI Control Flip-Flop is set, the Data Mode is selected and data will be input from the Input Data Register.

#### 1-14. Data Mode (Control Flip-Flop set)

Data is input from the DI in two formats, packed or unpacked.

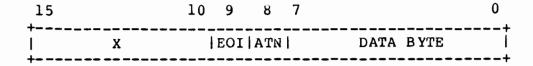

The unpacked data input format is shown in Figure 1-6.

Figure 1-6. Unpacked Data Input Format

Bits 0-7 contain the data byte, while bits 8 and 9 contain the values of the disc ATN and EOI line associated with the data. If the DI is conducting a Parallel Poll, the poll response will be in the data positions and both bits 8 and 9 will be set, indicating the poll function. Bits 10-15 are undefined in the unpacked format, and should be masked by software.

The packed data input format is shown in Figure 1-7.

Figure 1-7. Packed Data Input Format

Here two 8-bit bytes are contained within the word. As described in "EOI" paragraph 1-12, an odd numbered byte signalling End of Record will appear in both bytes of the data word.

1-15. Status Mode (Control Flip-Flop clear)

The data format of the Status Word is shown in Figure 1-8.

| _ | 15              | 14   | 13  | 12              | 11              | 10  | 9   | 8               | 7                | 6 | 5 | 4               | 3          | 2 | 1 | 0               |

|---|-----------------|------|-----|-----------------|-----------------|-----|-----|-----------------|------------------|---|---|-----------------|------------|---|---|-----------------|

|   | s <sub>RQ</sub> | IFCI | REN | <sup>I</sup> RL | L <sub>BO</sub> | LBI | EOI | A <sub>TN</sub> | I <sub>FCO</sub> | × | x | o <sub>/E</sub> | SYS<br>CTL | L | Т | c <sub>IC</sub> |

Figure 1-8 Status Word Format

The definition of each Status Bit is as follows:

CIC- (Controller-In-Charge bit 0) Indicates that the DI is currently controlling the disc.

T (Talk, Bit 1) - indicates that the DI is currently a talker to the disc.

L (Listen, Bit 2) - indicates that the DI is currently a listener to the disc.

SYSCTL (System Controller, Bit 3) - indicates the position of the System Controller Switch on the DI.

ODDIN (Bit 4) - if set, indicates that an odd number of bytes were received in the last (packed) input transfer. (In the unpacked mode, this bit is always set.)

IFCO (Interface Clear Output, Bit 7) - indicates that the 100 microsecond IFC one-shot is still fired.

ATN (Attention, Bit 8) - indicates the instantaneous state of the disc ATN line. This may or may not be the same as the values of ATN stored in the FIFO for each data byte.

EOI (End Identify, Bit 9) - same as above for the disc EOI line.

LBI (Last Byte Input, Bit 10) - indicates that the EOR Flip-Flop has been set.

LBO (Last Byte Output, Bit 11) - indicates that the LBO Flip-Flop has been set.

IRL (Input Register Loaded, Bit 12) - indicates that a byte (unpacked) or 2 bytes (packed) are valid in the Input Data Register.

REN (Remote Enable, Bit 13) - indicates the state of the disc REN line.

IFCI (Interface Clear Input, Bit 14) - indicates that the IFC Flip-Flop has been set due to IFC asserted on the bus.

SRQ (Service Request, Bit 15) - indicates the state of the disc SRQ line.

#### 1-16. MASTER RESET

#### 1-17. Master Reset Functions

The Master Reset signal is used to reset and/or initialize all data paths and Flip-Flops on the DI. MR will affect the following logic elements of the DI:

- Clear the DI Control Flip-Flop

- Clear the DI Flag Flip-Flop (2)

- Reset the DI FIFO (3)

- (4)Clear the Input Data Register

- Reset the LBO (Last Byte Output) Flip-Flop Reset the LBI (Last Byte Input) Flip-Flop (5)

- (6)

- (7) Reset the IRL (Input Register Loaded) Flip-Flop

- (8) Set the input byte pointer to upper byte (if packed)

- (9) Set the output byte pointer to upper byte (if packed)

- (10) Reset the IFCI (Interface Clear) Flip-Flop

The MR signal is also generated by the CPU backplane signal CRS.

1-18. Rules Concerning MR

Two rules must be followed for generating MR prior to a data transfer:

- a. MR must be generated before the DI is made a Talker or a Listener. This will prevent "garbage" left in the FIFO from some previous transfer from either being transmitted to the bus or read into the DI Input Data Register.

- b. MR must also be generated after Packing is enabled but before the first data word is transferred.

This is necessary because in the unpacked mode, the input and output byte pointers are held in the "lower byte" position and cannot be changed. When Packing is enabled, MR must then be sent to position these pointers at the "upper byte" position, to be ready for the first byte of data.

Thus, to make the DI a Talker in Packed output format, the proper sequence is:

- (1) MR (Rule 1)

- (2) Control Register = Talk, Packing

- (3) MR (Rule 2)

- (4) Output Data to DI

| T |              |   |         |   |   |

|---|--------------|---|---------|---|---|

| 1 |              | ŀ |         |   |   |

| 1 |              | ! |         | _ |   |

| 1 | INSTALLATION | l | CHAPTER | 2 |   |

|   |              | i |         |   | i |

| 1 |              | i |         |   |   |

|   |              | L |         |   |   |

#### 2.1 General

This section provides installation information needed to interface the 12821A, Disc Interface (DI) to an HP compatible disc. The H-Series (7906H, 7920H, 7925H and 9895A) and the CS80-Series (7908x, 7911x, 7912x and 7935x) disc drives are compatible with the DI. This interface is supported only when installed on an HP 1000 M/E/F Series CPU configured under either the RTE-IVB (92068A) or the RTE-6/VM (92084A) operating system. The user choice of operating system is supplied with an HP 1000 System or may be ordered separately under one of several options. Consult your local HP Sales and Service Office (listing in back of this manual) to determine which is most advantageous to you. Included in this section are installation requirements, DIP switch settings, cabling instructions and recommended packaging and shipping procedures for product reshipment.

#### 2.2 Unpacking and Inspection

Inspect the product shipping container before opening. If there is external evidence of damage, request that the carrier's agent be present when the container is first opened. Carefully inspect each item for damage. If there is physical damage, immediately notify your local Hewlett Packard Sales and Service Office (listing included in the back of this manual) and the common carrier. If the product fails to meet HP's published specifications or the diagnostics cannot be successfully run (see Installation Checkout, next section and Chapter 4), notify your local Hewlett Packard Sales and Service Office.

Retain the shipping container and packing material for the carrier's and HP inspection. The HP Sales and Service Office will arrange for the repair or replacement of your shipment, without waiting for your claim against the carrier to be resolved.

Update 1 2-1

#### 2.3 Checkout

To verify operation of this product, perform the diagnostics included in the 24998-14002 Diagnostic Library, included in your HP 1000 Model 60 or 65 System.

#### 2.4 Storage and Reshipment

If your local HP Sales and Service Office instructs you to return the shipment for repair, attach a tag identifying the owner and (if possible) the HP Sales Order Number. Indicate on the tag the service to be performed or the problem encountered with this shipment. If the original, factory packaging material is available and in reusable condition, it may be useful. Whether packaged for reshipment by your Traffic Department, or a third party, good grade commercial material should be used. Carefully follow the local HP Sales and Service Office's instructions for expeditious repair or replacement of your defective product.

#### 2.5 System Controller DIP Switch

Before installation of the DI in the CPU backplane, the System Controller function must be enabled. The eight position DIP Switch located at position Ul3 (see Figure 4-1) on the PCA has switch eight (Ul3-S8) assigned to the system controller function. Set S8 to the OPEN (OPEN = 1) position to enable the system controller function. Switches 1 through 7 are used by the diagnostic only. Setting S1-S7 to be closed position will provide an address of 0 when requested by the diagnostic.

#### WARNING

Hazardous voltages are present inside the computer mainframe! Before installing the DI or the loader ROM, set the <u>POWER</u> switch to <u>OFF</u>. Failure to observe this warning can result in serious injury.

#### 2.6 Installation

Install the DI as follows:

- 1) Set the computer TPOWER switch to OFF.

- 2) Remove the I/O card cage cover.

- 3) If you are installing the DI in an HP 1000 system, insert the DI into the I/O slot (select code) reserved for it (refer to Table 1 of your HP 1000 Primary System Configuration Data Data Manual) otherwise install it in any convenient I/O slot.

- 4) Install the HP 12992H Disc Loader ROM for H-Series disc drive operation using the instructions contained in the 12992 Loader ROM's Installation Manual, HP Part No. 12992-90001.

-0 R -

5) If CS80-Series disc drives are to be used, Option 001 was ordered to delete the H-Series Loader ROM and the 12992J, CS-80 Series Loader ROM was ordered as a separate line item. Install it using the instructions contained in the 12992J Loader ROM Installation Manual, HP Part No. 12992-90001.

NOTE

If the DI was purchased as part of an original HP 1000 System, order the DI and the loader ROM will have been installed. Refer to the decal on the inside of the cabinet front door to determine the DI and loader ROM location.

- 6) Turn OFF all disc drives before connecting cables to the DI or the disc drive.

- 7) Perform the disc installation and checkout procedures described in your Disc Installation and Service Manual before connecting the 59310-60002 cable from the DI to the first disc drive.

Update 1 2-3

#### CAUTION

ALL disc drives must be OFF before connecting cables

#### 2.7 Interconnecting Cables

- a) If you are installing an HP 1000 Model 60 or 65 System, attach the 59310-60002 cable (3.69 meters) from the DI to the first disc drive and interconnection cables to any additional disc drives (see Figure 1-1 and Table 1-1). Then perform the primary system tests described in your "Getting Started" manual.

- b. If you are installing an HP 1000 Series M/E/F computer, run the 24998 diagnostics (refer to the Disc Interface Diagnostic Manual, 12821-90002). Then connect the 59310-60002 cable from the DI to the first disc drive, and the interconnecting cable to any additional disc drive.

#### 2.8 System or Subsystem Checkout

Refer to the HP 1000 Model 60/65 Installation And Service Manual, HP Part Number 5955- 4359 for system checkout procedures or to the diagnostic manual 12821-90002 for DI checkout procedures. If a disc or system level problem is indicated, use the 91711B, Diagnostics And Verification Package to isolate.

#### NOTE

In order to prevent degraded operation,  $\underline{ALL}$  disc drives cabled to the disc interface (DI) must be powered  $\underline{ON}$  whenever your computer or system is operating.

| +                       |         |

|-------------------------|---------|

| j l                     | SECTION |

| PRINCIPLES OF OPERATION |         |

| · ·                     | III     |

| +                       | + ++    |

#### 3-1. INTRODUCTION

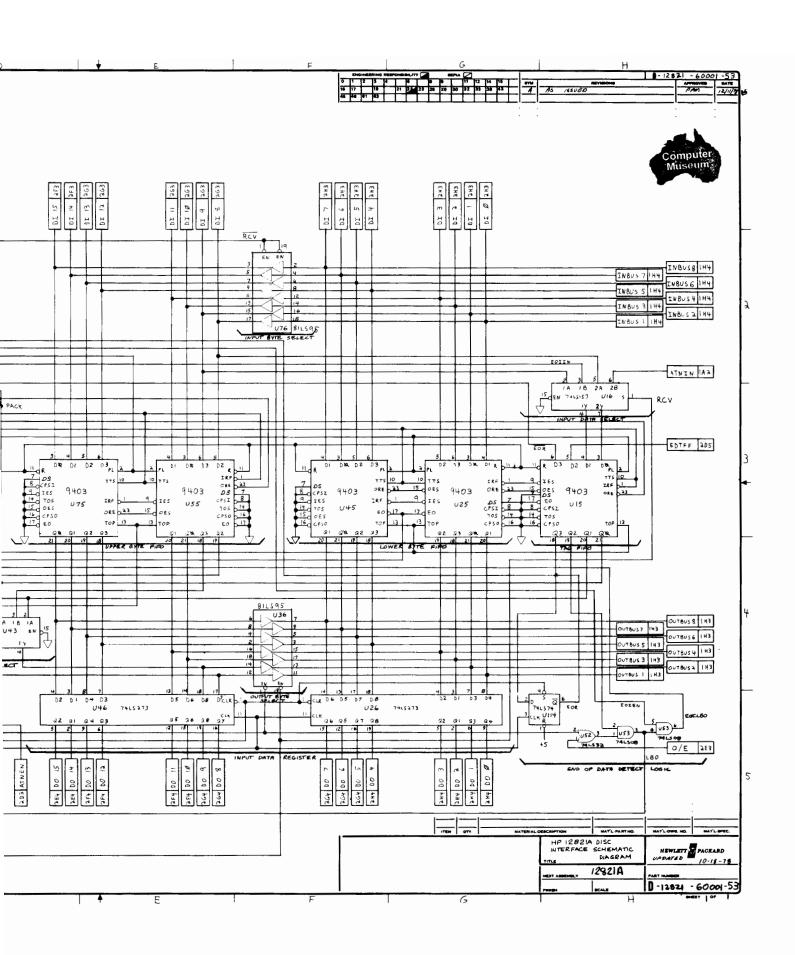

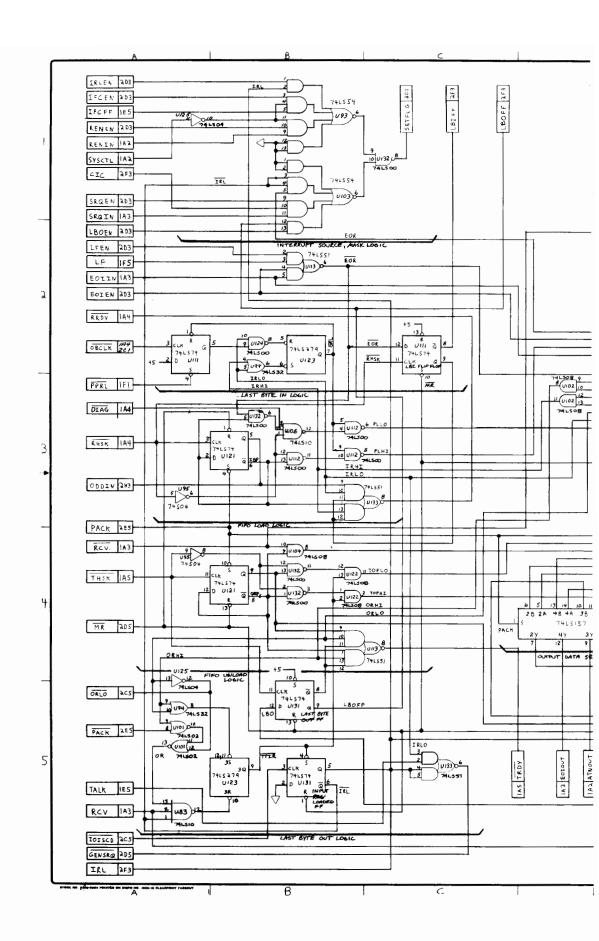

This section provides a brief description of the logical operation of the Disc Interface. This theory is presented to aid in confirming that a problem exists on the DI rather than another component of the subsystem. The DI is a multilayer PCA and should be returned to a Hewlett-Packard service center for repair, warranty may be voided if repaired by unqualified personnel. Assembly and schematic diagrams to be used in conjunction with this discussion are located in section IV.

#### 3-2. SIGNAL NAMES AND LOCATIONS

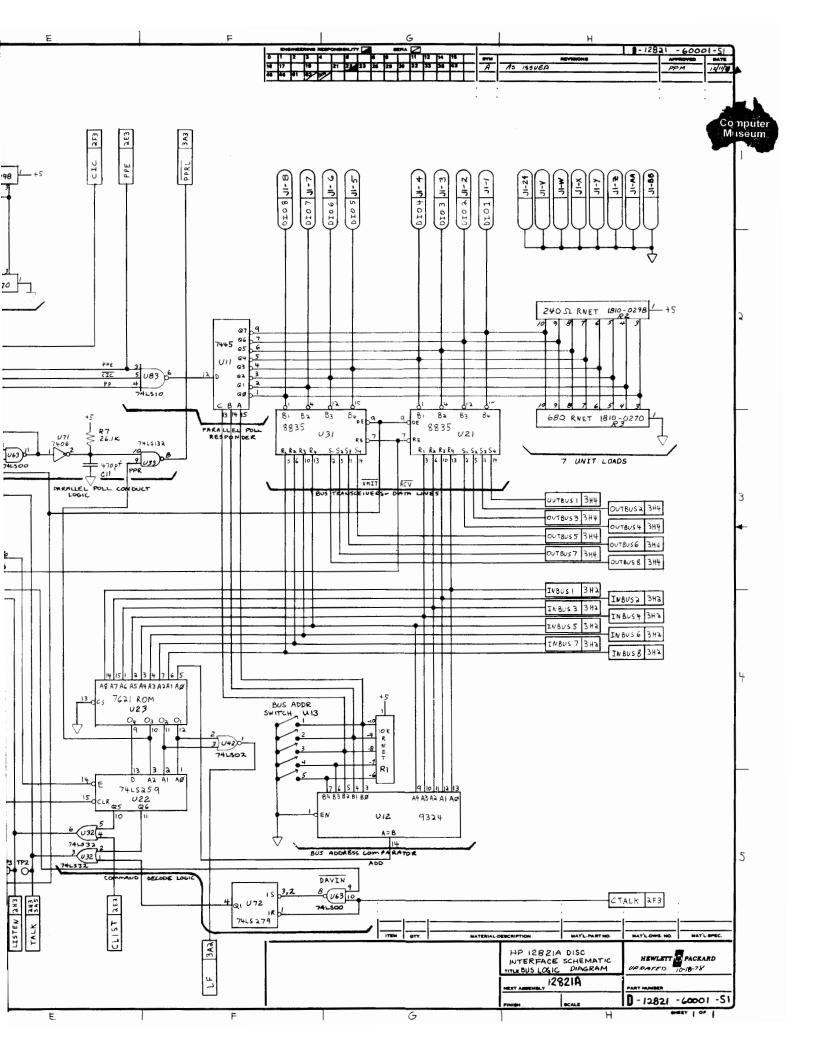

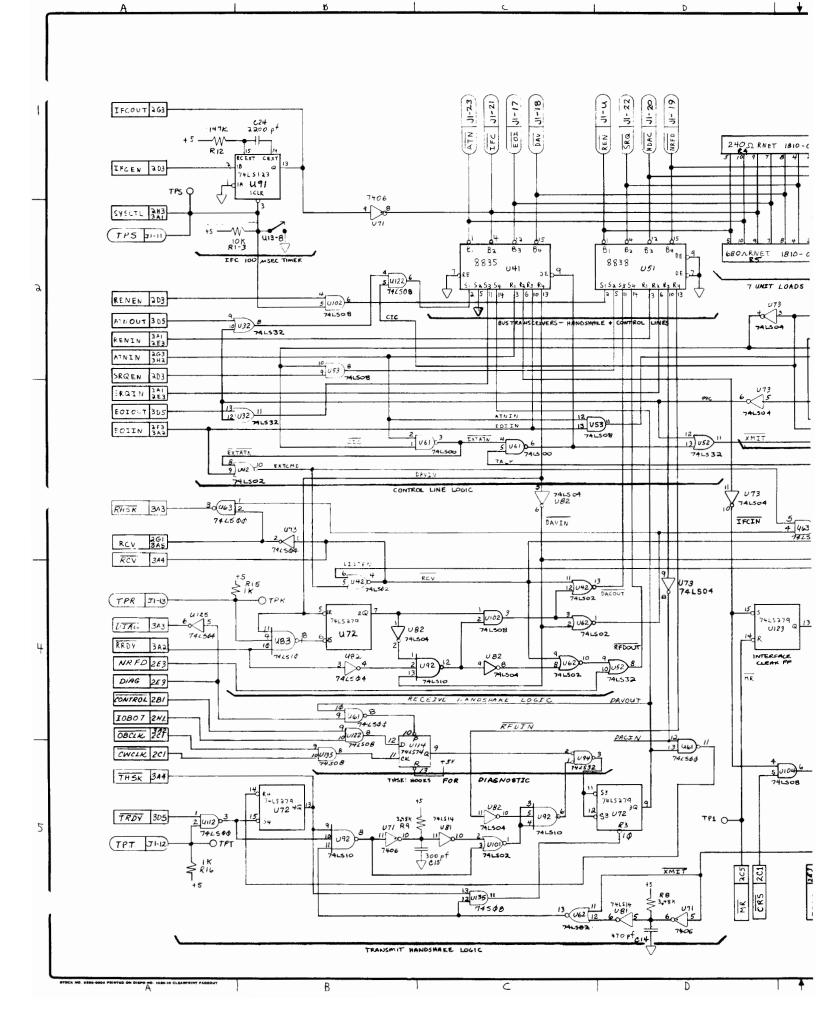

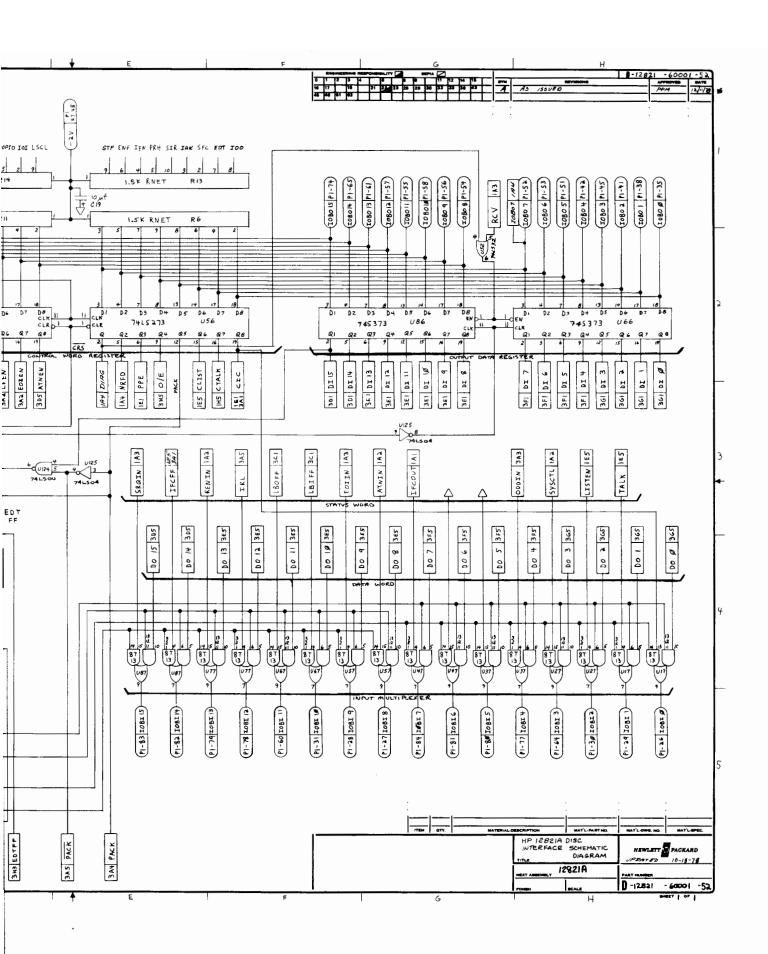

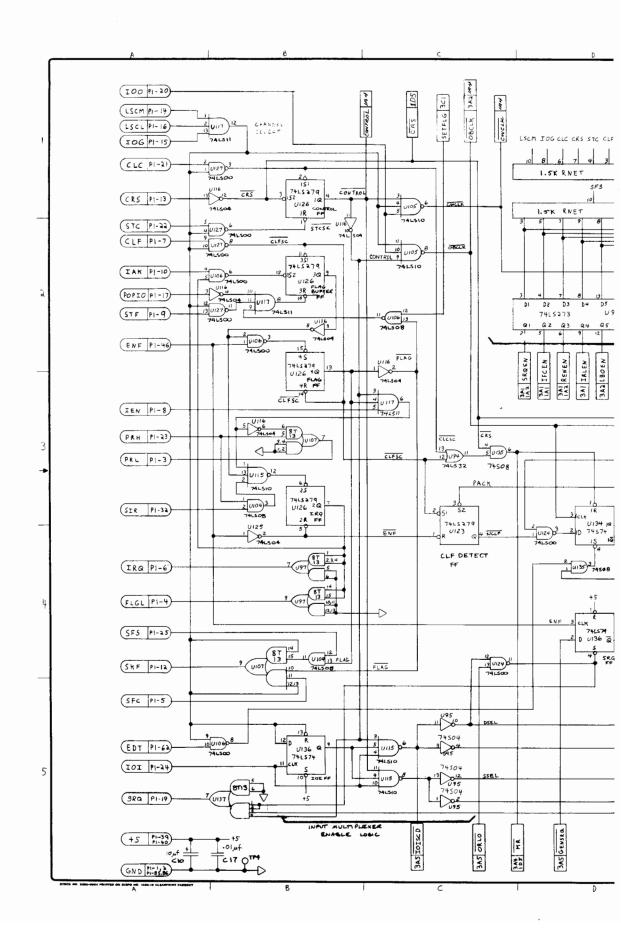

Signal names are mnemonic identifiers usually chosen to be as close to the signal usage as possible. These signal identifiers may have a bar over them on the schematics to indicate the signal is active low. In text the same signal will contain an "L" at the end of the signal name to indicate the active low condititon. This section references the the disc interface logic diagram D-12821-60001-51 through 53. During the discussion, sheet number and coordinates are indicated by brackets. The coordinates will be that of an area of the schematic which contains the logic circuit described in the text.

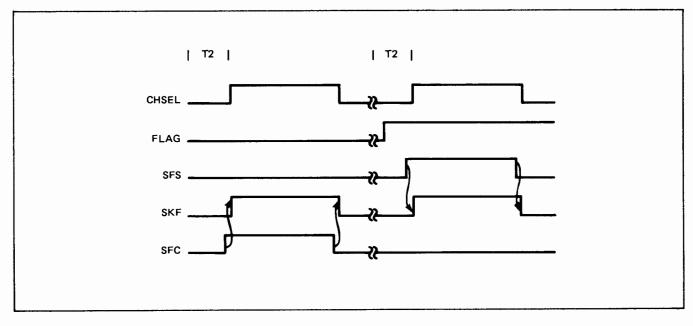

#### 3-3. CHANNEL SELECT LOGIC

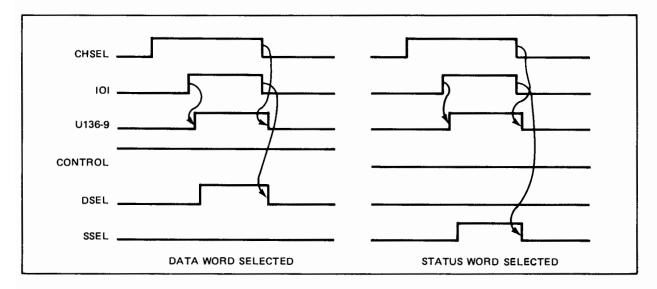

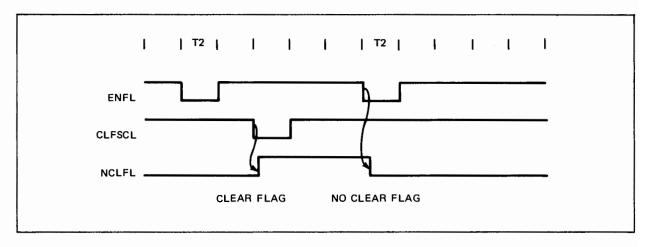

The CHSEL (Channel Select Ul17-4) signal [52A-1] is the logical AND of IOG (I/O Group Instruction), LSCM (Lower Select Code, Most Significant Digit), and LSCL (Lower Select Code, Least Significant Digit). It is used to enable the Control, Flag Buffer, Flag, and Input Multiplexer Enable logic blocks when an I/O instruction is being executed and is directed to the DI's select code.

#### 3-4. CONTROL LOGIC

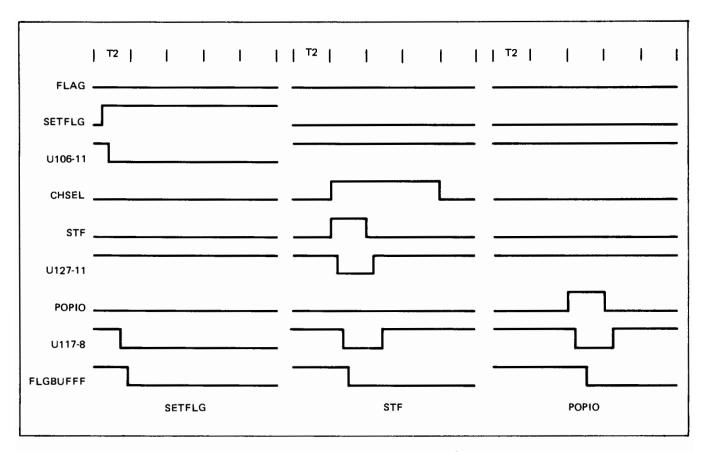

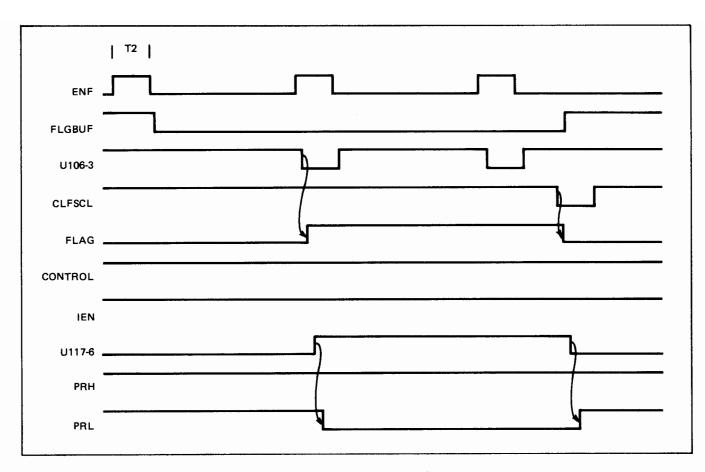

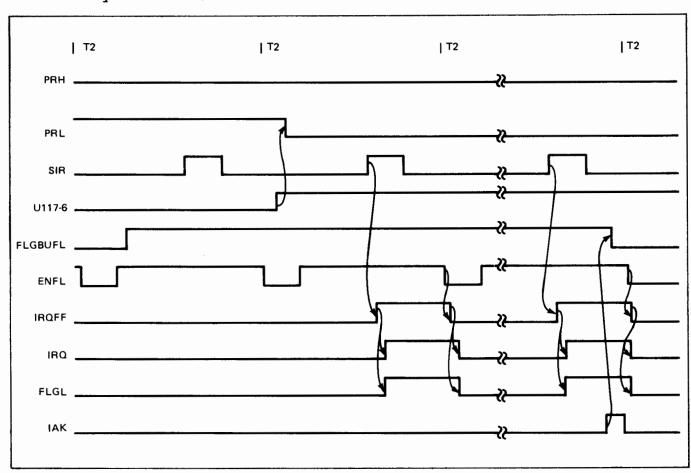

#### 3-5. Control Flip-Flop and Logic

The Control Flip-Flop Output signal CONTROLL [52B-1] (Ul26-4, low true) determines whether the DI is in Data Mode or in Configure/Status Mode. Data Mode is selected by executing an STC DI instruction. The CHSEL signal (Ul17-4) enables the STC signal [52B-2] (Ul27-5) to the Control Flip-Flop. STC is inverted through the NAND gate (Ul27) and resets the Control Flip-Flop

(Ul26-1) so that CONTROLL is low. CONTROLL is inverted and is input to the NAND gate which generates OBCLKL [52C-2](Ul05-8) in addition to being input to the Flag and input Mux Enable logic. OBCLKL is derived from IOO when CONTROLL is zero and CHSEL is one, i.e., when an I/O output instruction to the DI is executed and the card is in data mode. OBCLKL is used to clock the Output Data Register.

Similarly a CLC DI instruction selects Configure/Status mode by setting the Control Flip-Flop (CONTROLL = 1). CONTROLL enables the NAND gate which generates CWCLKL [52C-1]. CWCLKL is derived from IOO when CONTROLL and CHSEL are one, i.e. when an I/O output instruction to the DI is executed and the card is in configure mode. CWCLKL is used to clock the Control Word Register [52E-2].

#### 3-6. Control Word Register

The Control Word Register is made up of two Octal D-type flip-flops (U96, U56, 74LS273) with a common clock. The inputs are the IOBO (Input/Output Bus Output) lines from the CPU. Data is latched on the rising edge of CWCLKL. The Control Word Register is cleared by the CRSL (Control Reset, low true) [52C-1] signal and not by MR.

#### 3-7. Bus Transceivers and Control Line Logic

The bus transceivers used are National 8835 inverting quad tri-state party line transceivers (U41, U31, U21) and National 8838 inverting quad unified bus transceiver (U51) with open collector drivers [51C,D-2 and 51G-3].

The 8838 is used for the NDACL, NRFDL, SRQL and RENL control lines. The open collector drivers allow wired-OR connection of the lines. The drivers are always enabled so that any signal seen on the S inputs are sent to the bus and any signal seen on the bus is received at the R outputs.

In general, a signal to be sent to the disc will be called XXXOUT, and one received from the disc will be called XXXIN where XXX is the mnemonic of the appropriate control line (ATN, REN, NDAC etc.)

An 8835 is used for the other bus transceiver on the control lines. Its receivers are always enabled. Its drivers, however, are enabled only when the DI is controller-in-charge and the DI is a talker. The driver enable signal is generated by some of the combinational logic referred to as the Control Line Logic (U61-3, U61-6) [51C-3].

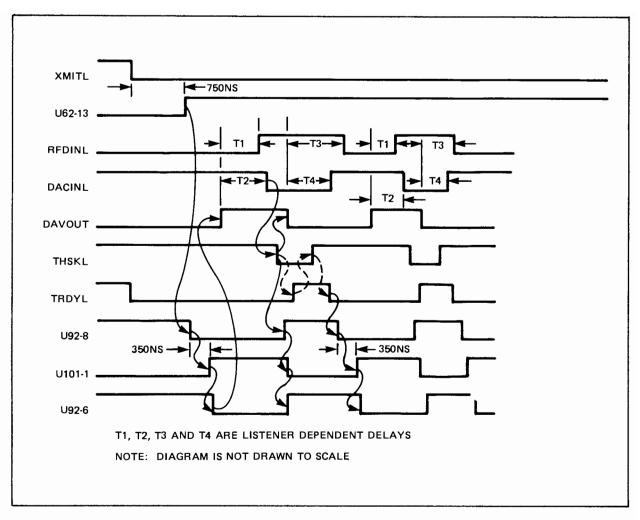

The driver enable signal is ORed with the PPC (Parallel Poll Conduct) signal to generage XMITL (U52-11) [51D-3]. XMITL is used to enable the drivers on the Data Line Bus Transceivers (U31,21) and also tells the transmit handshake logic that a data transfer is about to begin.

Ul02-6 [51B-2] allows RENL to go low if the DI is System Controller and the RENEN bit in the Control Register is set. Similarly, U53-8 [51B-3] allows SRQL to go low if the DI is not controller-in-charge and the SRQEN bit in the Control Register is set. The gates Ul22-6 [51B-2] and U32-11 [51A-3] are used to assert ATNL (DI must be Controllerin-Charge) or EOIL respectively, if ATNOUT or EOIOUT are asserted, or if a parallel poll is being conducted (PPC is high) by the DI.

The bus transceivers on the data lines (U31,21) have the FIFO and Output Byte Select logic outputs (OUTBUS1-8) [51H-3,4] as their driver inputs. The drivers are enabled whenever XMITL is low. Their receiver outputs (INBUS1-8) are input to the FIFOs [53D,H-3] and Input Byte Select logic. The receivers are enabled whenever RCVL is low.

The bus lines are loaded by seven equivalent HP-IB loads. The loading is done by the 240 (R2,R4) and 680 ohm (R3,R5) biasing resistors [51E-1 and H-3]. In their high state the lines are at 3.7V with no external devices connected to the DI.

#### 3-8. OUTPUT DATA REGISTER

The Output Data Register is made up of two octal latches (U86, U66) [52G-2] with common clock and enable. While OBCLKL is low the latch outputs follow the IOBO lines. Data is latched when OBCLKL returns high. Typically the latch outputs are enabled. The outputs will be high impedence if RCV is a one indicating that the DI is receiving data from the disc or if the DIAG bit of the Control Register [52E-2] is set (see paragraph 3-20). The latch outputs are input to the FIFOs and the Input Byte Select logic [53F-2].

#### 3-9. INPUT BYTE SELECT LOGIC

The Input Byte Select logic [53F-2] is used to enable the INBUS to the Upper Byte FIFO when the DI is receiving data from the disc. National's 81LS95 Tristate Octal Buffer (U76) is used with RCVL as the enable.

## 3-10. INPUT DATA SELECT

The Input Data Selector [51H-3] is a 74LS157 Quad 2 to 1 Data Selector (U16). Its outputs are always enabled and are input to the Tag FIFO. RCV is used as the select. When the DI is receiving data from the disc (RCV = 1), the ATN (ATNIN) and EOI (EOIIN) values associated with the current byte on the bus are selected. When the DI is transmitting data over the bus (RCV=0) bits DI8 and DI9 are selected. Note that these bits correspond to ATN and EOI when in unpacked data format.

# 3-11. THE FIFO's

### 3-12. Introduction

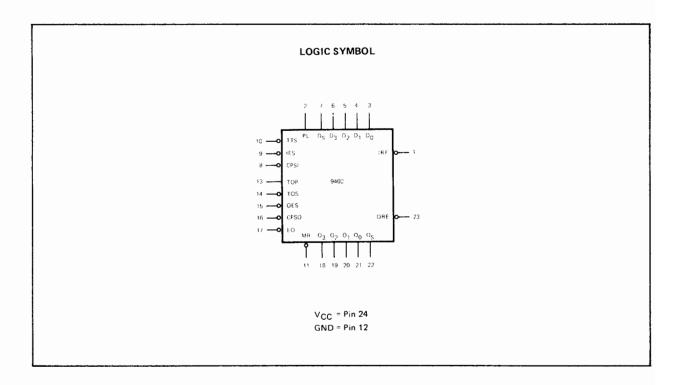

The Fairchild 9403 First In First Out Buffer Memory is used as the basic building block for the DI FIFO Buffers [53F-3]. A general description of the 9403 will be given first, then a more detailed description of how the DI utilizes this part. For a more complete description of the 9403 consult the Fairchild Macrologic Bipolar Microprocessor Data Book.

#### 3-13. The 9403 IC

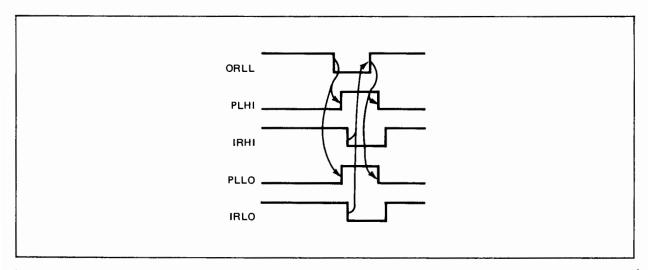

The 9403 is organized as 16 words by four bits (Figure 3-1). It is capable of being expanded to any number of bits and may be loaded and unloaded asynchronously and parallel. The outputs are tristate.

Figure 3-1. The 9403 FIFO IC

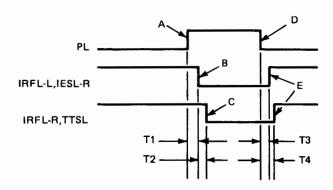

A high on PL (Parallel Load Input) parallel loads the D inputs into the input register internal to the FIFO, and IRFL (Input Register Full Output, low true) goes low indicating the register is full. (Note: IESL (Serial Input Enable) must be low to enable parallel inputs). The input register feeds the FIFO stacks and if the top location of the stack is empty then when TTSL (Transfer to Stack input, low true) goes low the data falls through to the stack automatically - pausing only when necessary to wait for the next location to empty. The input register is reinitialized when PL returns low. When the FIFO's input data register contents have been transferred to the stack IRFL returns high, assuming horizontal expansion to more than 4 bits in width, automatic FIFO action is achieved by connecting the IRFL output of the rightmost tip of a logical block to the TTSL input of all the FIFOs of that block.

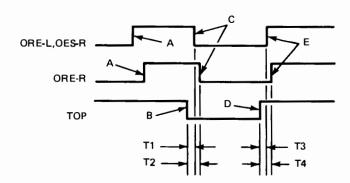

After data has entered the 9403 and fallen through to the last stack location it is transferred into the FIFOs output data register if TOP (Transfer Out Parallel Input) is high. After this transfer OREL (Output Register Empty Output, low true) goes high indicating there is valid data in the FIFO's output data register. If EOL (Output Enable, low true) is low the output data register contents are seen at the FIFO outputs.