# HP 12025A/B Input/Output Extender

Hardware Support Manual

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

# HP 12025A/B Input/Output Extender

**Hardware Support Manual**

**Options Covered**

This manual also covers Options 001, 002, and 015 of the HP 12025A/B I/O Extender.

Data Systems Division 11000 Wolfe Road Cupertino, California 95014

Part No. 12025-90001

E0385

Printed in U.S.A. March 85

# Federal Communications Commission Radio Frequency Interference Statement

The Federal Communications Commission (in Subpart J, of Part 15, Docket 20780) has specified that the following notice be brought to the attention of the users of this product.

WARNING: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

#### **NOTICE**

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company.

Copyright © 1985 by HEWLETT-PACKARD COMPANY

# **Printing History**

The Printing History below identifies the Edition of this Manual and any Updates that are included. Periodically, Update packages are distributed which contain replacement pages to be merged into the manual, including an updated copy of this Printing History page. Also, the update may contain write-in instructions.

Each reprinting of this manual will incorporate all past Updates, however, no new information will be added. Thus, the reprinted copy will be identical in content to prior printings of the same edition with its user-inserted update information. New editions of this manual will contain new information, as well as all Updates.

To determine what manual edition and update is compatible with your current software revision code, refer to the appropriate Software Numbering Catalog, Software Product Catalog, or Diagnostic Configurator Manual.

| m' . m 1''    | 34 1006  |      |  |  |  |  |  |  |

|---------------|----------|------|--|--|--|--|--|--|

| First Edition | Mar 1985 | <br> |  |  |  |  |  |  |

# **Safety Considerations**

GENERAL - This product and related documentation must be reviewed for familiarization with safety markings and instructions before operation.

#### SAFETY SYMBOLS

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect the product against damage.

Indicates hazardous voltages.

Indicates earth (ground) terminal (sometimes used in manual to indicate circuit common connected to grounded chassis).

## WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

## CAUTION

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

### **CAUTION**

### STATIC SENSITIVE DEVICES

Some of the semiconductor devices used in this equipment are susceptible to damage by static discharge. Depending on the magnitude of the charge, device substrates can be punctured or destroyed by contact or mere proximity to a static charge. These charges are generated in numerous ways such as simple contact, separation of materials, and normal motions of persons working with static sensitive devices.

When handling or servicing equipment containing static sensitive devices, adequate precautions must be taken to prevent device damage or destruction. Only those who are thoroughly familiar with industry accepted techniques for handling static sensitive devices should attempt to service the cards with these devices. In all instances, measures must be taken to prevent static charge buildup on work surfaces and persons handling the devices. Cautions are included through this manual where handling and maintenance involve static sensitive devices.

SAFETY EARTH GROUND - This is a safety class I product and is provided with a protective earthing terminal. An uninterruptible safety earth ground must be provided from the main power source to the product input wiring terminals, power cord, or supplied power cord set. Whenever it is likely that the protection has been impaired, the product must be made inoperative and be secured against any unintended operation.

**BEFORE APPLYING POWER** - Verify that the product is configured to match the available main power source per the input power configuration instructions provided in this manual.

If this product is to be energized via an auto-transformer (for voltage reduction) make sure the common terminal is connected to the earth terminal of the main power source.

### **SERVICING**

## WARNING

Any servicing, adjustment, maintenance, or repair of this product must be performed only by qualified personnel.

Adjustments described in this manual may be performed with power supplied to the product while protective covers are removed. Energy available at many points may, if contacted, result in personal injury.

Capacitors inside this product may still be charged even when disconnected from its power source.

To avoid a fire hazard, only fuses with the required current rating and of the specified type (normal blow, time delay, etc.) are to be used for replacement.

#### WARNING

#### **EYE HAZARD**

Eye protection must be worn when removing or inserting integrated circuits held in place with retaining clips.

# **Table of Contents**

|              | oter 1                               |

|--------------|--------------------------------------|

| roc          | uct Information                      |

|              | Introduction                         |

|              | Product Description                  |

|              | Options                              |

|              | Accessories                          |

|              | Specifications                       |

|              | Identification                       |

|              | Supported Equipment                  |

| <b>~</b> h _ | -to: 0                               |

|              | oter 2 Preparation and Requirements  |

|              | Introduction                         |

|              | Electrical Specifications            |

|              | Environmental Specifications         |

|              | Physical Specifications              |

|              |                                      |

|              | oter 3                               |

| nst          | allation and Configuration           |

|              | Introduction                         |

|              | Storage Before Unpacking             |

|              | Unpacking and Inspection             |

|              | Claims Procedure                     |

|              | Repacking For Shipment               |

|              | Shipment Using Original Packaging    |

|              | Shipment Using New Packaging         |

|              | Extender Switches                    |

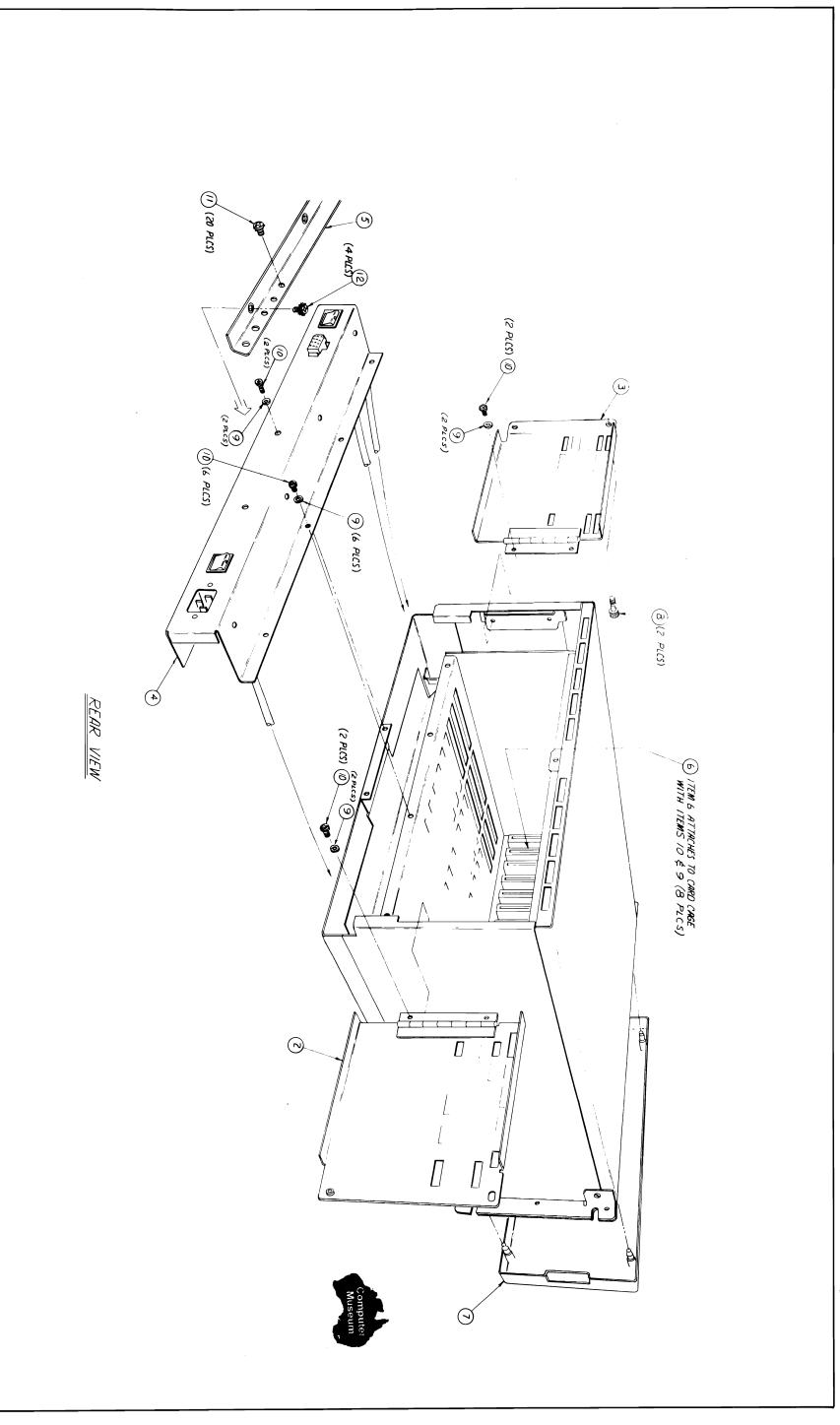

|              | Rack Mounting Instructions           |

|              | Cable Limitations In Older Cabinets  |

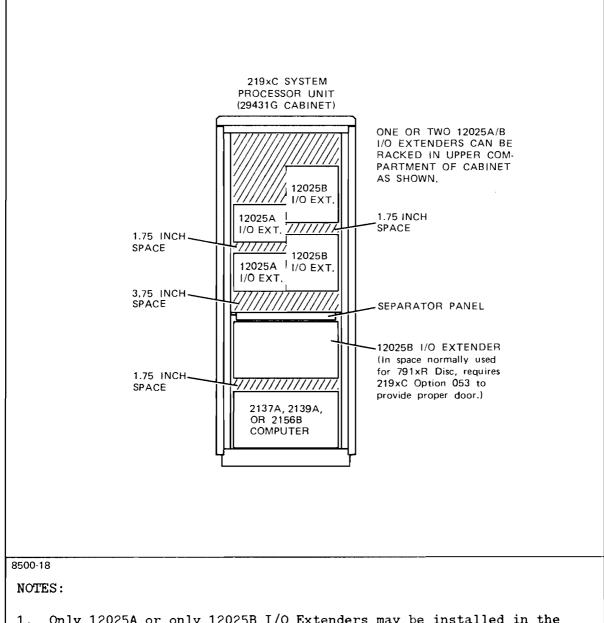

|              | HP 12025A Rack Mounting              |

|              | HP 12025B Rack Mounting              |

|              | Mounting In Standard EIA Rack        |

|              | Floor Mounting (HP 12025A)           |

|              | Extender Cable                       |

|              | Installing the I/O Extender Cards    |

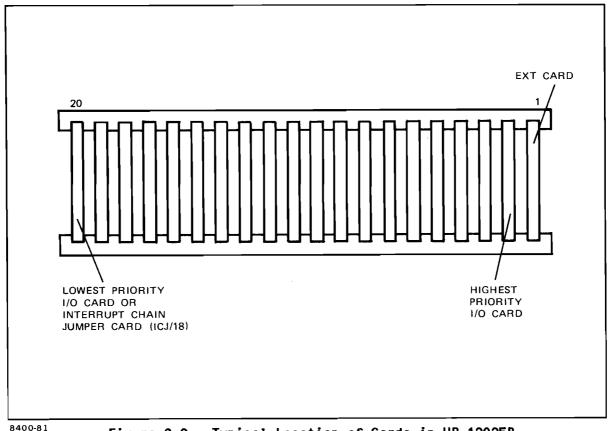

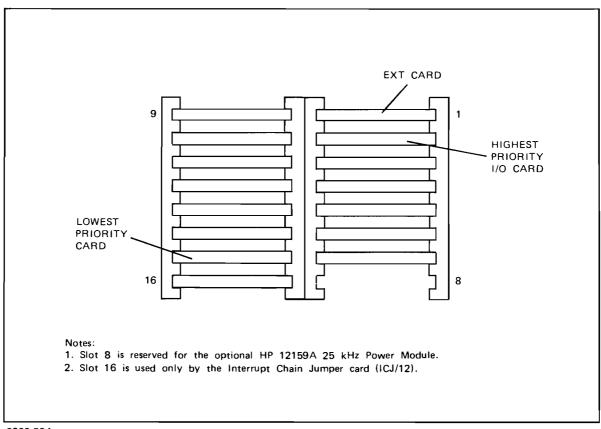

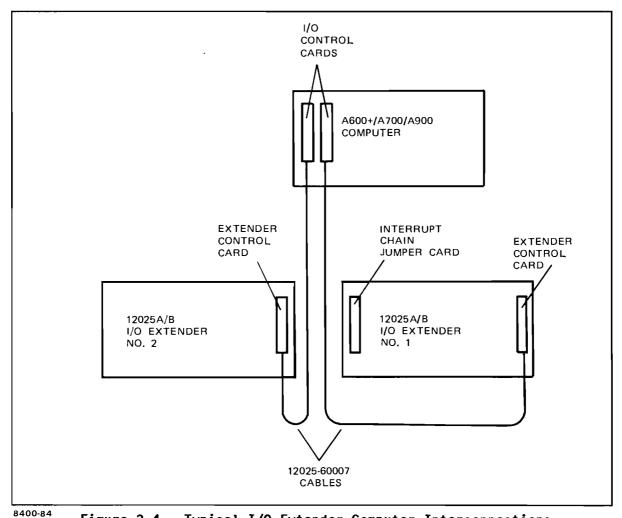

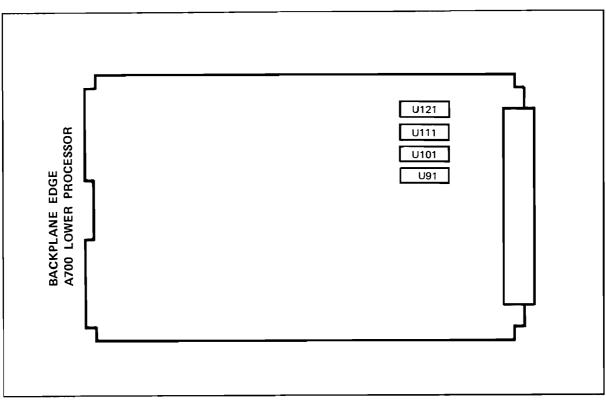

|              | I/O Priority                         |

|              |                                      |

|              | Installation                         |

|              | I/O Priority Within the I/O Extender |

|              | Interface Cabling                    |

|              | Installation of Upgrade Options      |

|              | Option 001 Upgrade Card              |

|              | Option 002 Upgrade Kit               |

|              | Initial Checkout Procedure           |

|              | Checkout Using Diagnostics           |

|              | 115/230 Vac Reconfiguration          |

|              | HP 12025A I/O Extender               |

|              | HP 12025B I/O Extender               |

| Introduction                                                           |   |   |       |   |   |   |   |   |      |

|------------------------------------------------------------------------|---|---|-------|---|---|---|---|---|------|

| Preventive Maintenance Procedures                                      | • | • | <br>• | • | ٠ | • | • | • | . 4- |

| pter 5                                                                 |   |   |       |   |   |   |   |   |      |

| ctional Description                                                    |   |   |       |   |   |   |   |   |      |

| Introduction                                                           |   |   |       |   |   |   |   |   | . 5- |

| Functional Overview                                                    |   |   |       |   |   |   |   |   |      |

| I/O Instruction Processing                                             |   |   |       |   |   |   |   |   |      |

| DMA Processing                                                         |   |   |       |   |   |   |   |   |      |

| Interrupt and Slave Processing                                         |   |   |       |   |   |   |   |   |      |

| General Description                                                    |   |   |       |   |   |   |   |   |      |

| I/O Extender Components                                                |   |   |       |   |   |   |   |   |      |

| Naming Conventions                                                     |   |   |       |   |   |   |   |   |      |

| IOC to EXT Communication                                               |   |   |       |   |   |   |   |   |      |

| Priority Chain Lines                                                   |   |   |       |   |   |   |   |   |      |

| I/O Control (IOC) Board Description                                    |   |   |       |   |   |   |   |   |      |

| Identification of Processor Type                                       |   |   |       |   |   |   |   |   |      |

| DMA State Machine                                                      |   |   |       |   |   |   |   |   |      |

| I/O Handshake State Machine                                            |   |   |       |   |   |   |   |   |      |

| Address and Data Bus Transfers                                         |   |   |       |   |   |   |   |   | -    |

| I/O Instruction Processing                                             |   |   |       |   |   |   |   |   |      |

| Interrupts and Slave Processing                                        |   |   |       |   |   |   |   |   |      |

| Status LEDs and Extender NotReady Flag                                 |   |   |       |   |   |   |   |   |      |

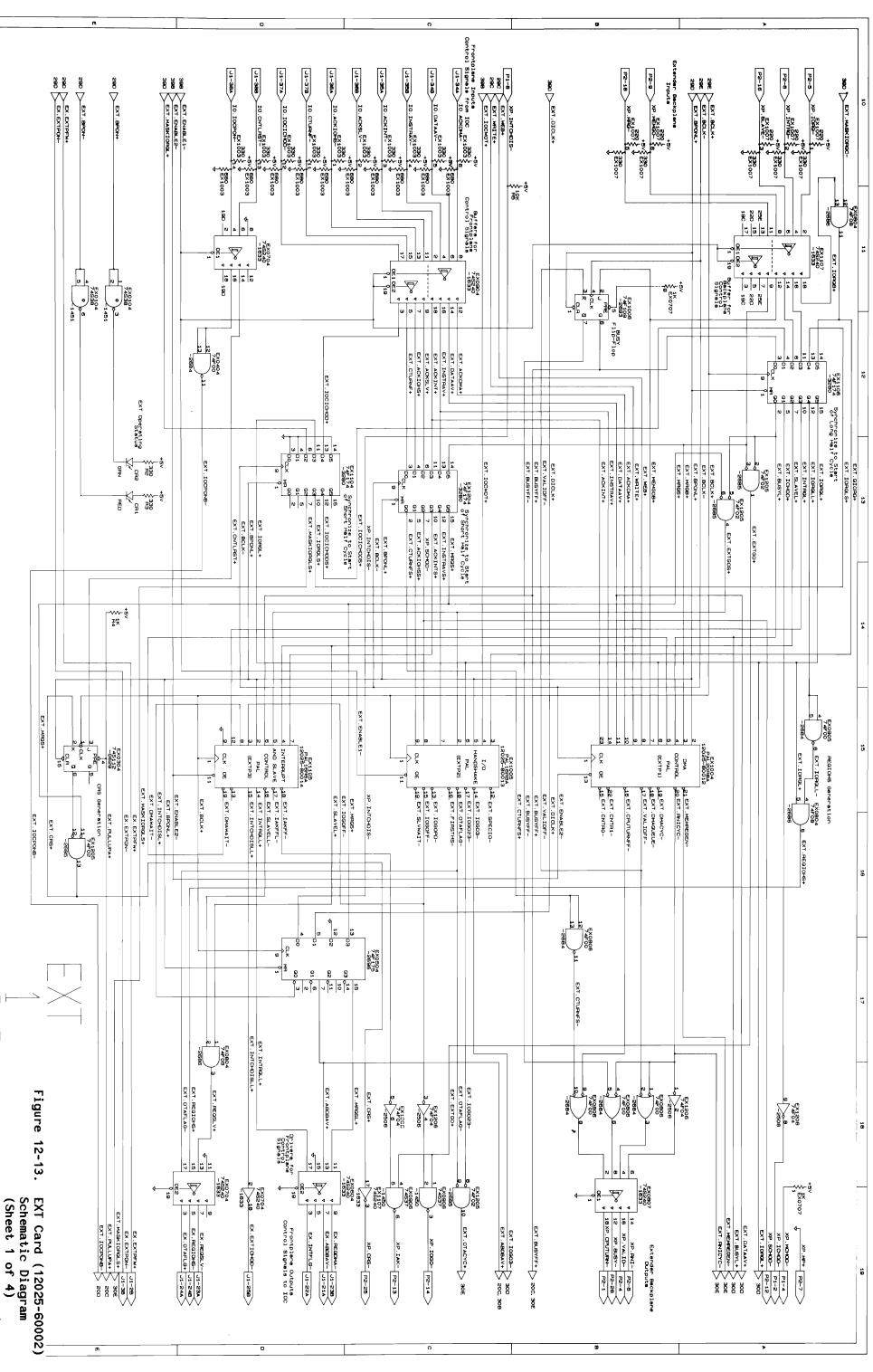

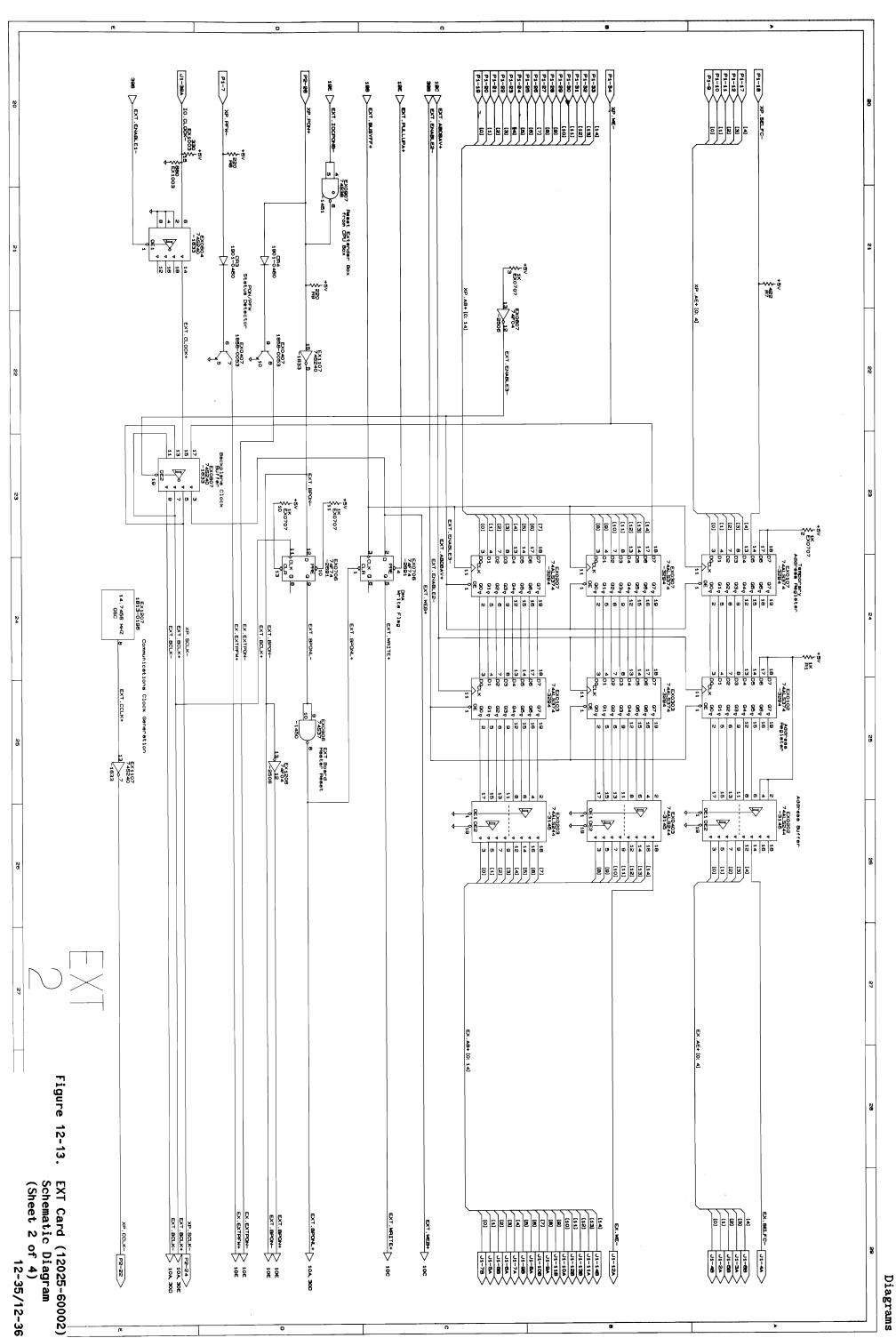

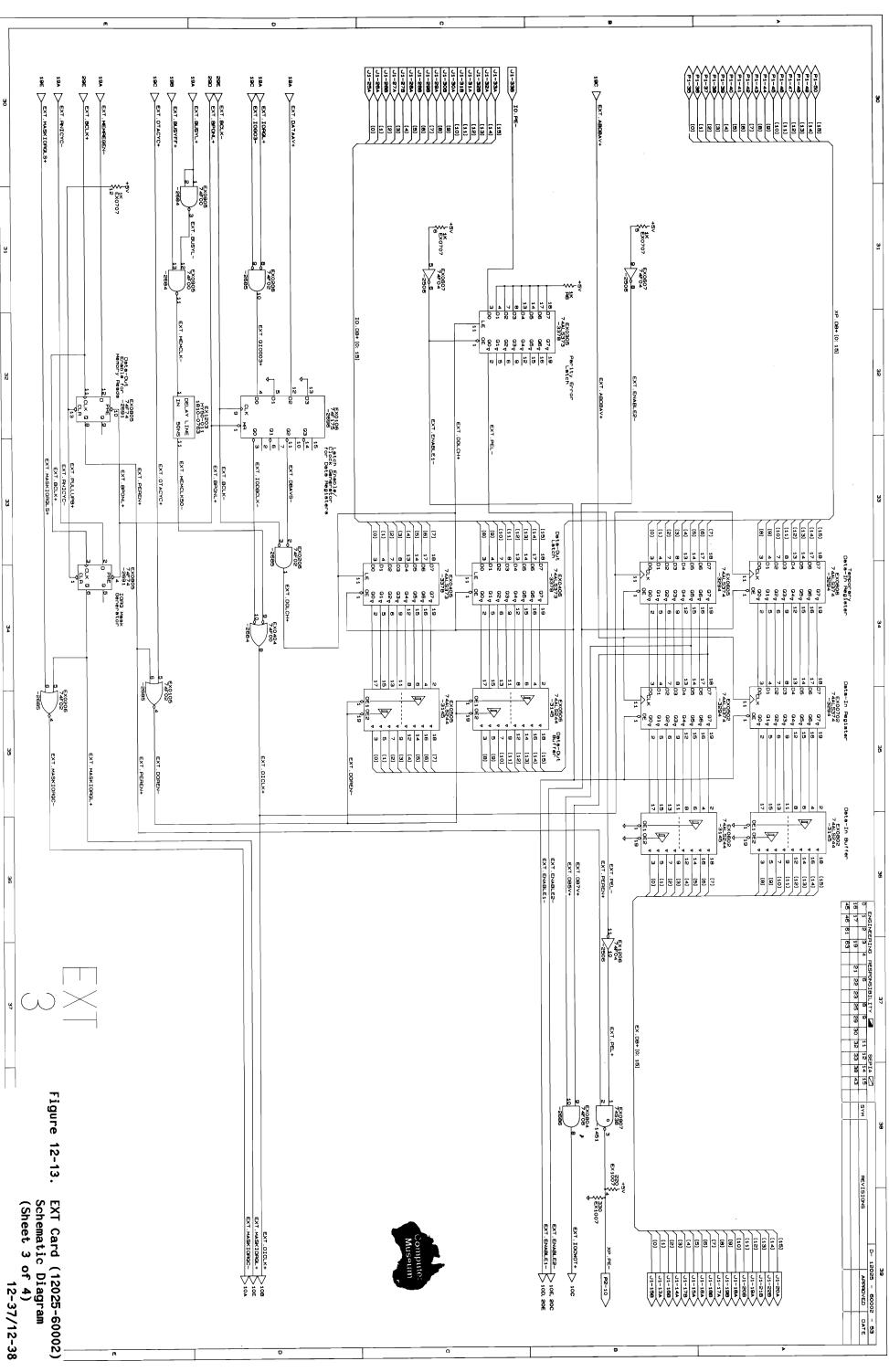

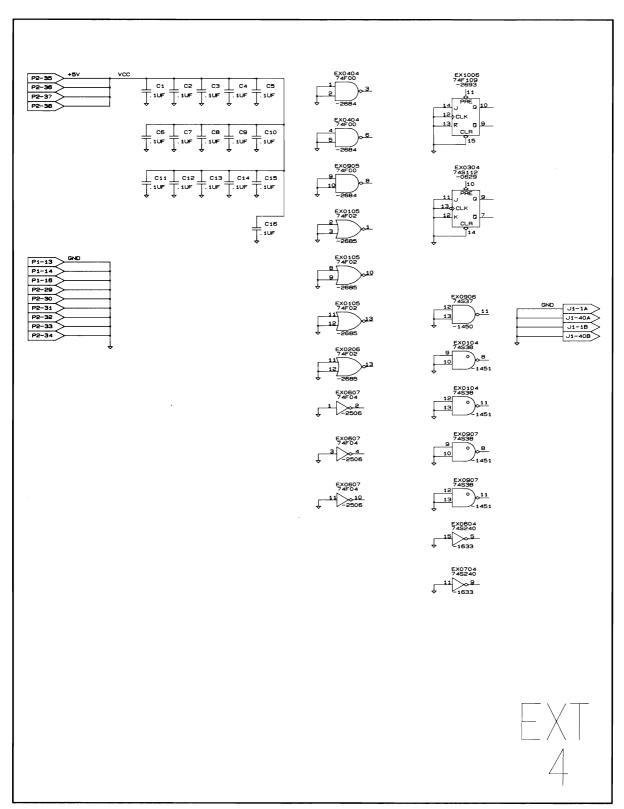

| Extender Control (EXT) Board Description                               |   |   |       |   |   |   |   |   |      |

| DMA and Instruction Broadcast State Machine                            |   |   |       |   |   |   |   |   |      |

|                                                                        |   |   |       |   |   |   |   |   | -    |

| I/O Handshake State Machine                                            |   |   |       |   |   |   |   |   | -    |

|                                                                        |   |   |       |   |   |   |   |   |      |

| Status LEDs                                                            |   |   |       |   |   |   |   |   | -    |

|                                                                        |   |   |       |   |   |   |   |   | -    |

| Introduction to Detailed Description                                   |   |   |       |   |   |   |   |   |      |

| The A/L-Series I/O Architecture The Expanded A-Series I/O Architecture |   |   |       |   |   |   |   |   |      |

|                                                                        |   |   |       |   |   |   |   |   |      |

| The A600+ Environment                                                  |   |   |       |   |   |   |   |   | -    |

| Instruction Recognition                                                |   |   |       |   |   |   |   |   |      |

| I/O Instruction Processing                                             |   |   |       |   |   |   |   |   | 5-   |

| Direct Memory Access                                                   |   |   |       |   |   |   |   |   | 5-   |

| Interrupts                                                             |   |   |       |   |   |   |   |   | 5-   |

| The A700 Environment                                                   |   |   |       |   |   |   |   |   | 5-   |

| Instruction Recognition                                                |   |   |       |   |   |   |   |   | 5-3  |

| I/O Instruction Processing                                             |   |   |       |   |   |   | • | • | 5-3  |

| Direct Memory Access                                                   |   |   |       |   |   |   | • | • | 5-3  |

| Interrupts                                                             |   |   |       |   |   |   | ٠ | • | 5-   |

| The A900 Environment                                                   |   |   |       |   |   |   | • | ٠ | 5-:  |

| Instruction Recognition                                                |   |   |       |   |   |   |   |   | 5-3  |

| I/O Instruction Processing                                             |   |   |       |   |   |   |   |   | 5-2  |

| Direct Memory Access                                                   | • | • | <br>• | • | • | • | • | • | 5-2  |

| Interrupts                                                             |   |   |       |   |   |   |   |   | 5-2  |

| Extender Architectural Characteristics 5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Maximum Select Codes 5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21           |

| Cannot Have Only I/O Extenders on CPU Backplane 5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22           |

| Custom Designed I/O Cards 5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22           |

| Why I/O Extenders Cannot Have I/O Extenders 5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

| I/O Instruction Throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

| DMA Throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

| Interrupts and DMA Interaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

| Maximum Number of Concurrent DMA Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

| regarded and arrest to be a first to the second of the sec |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

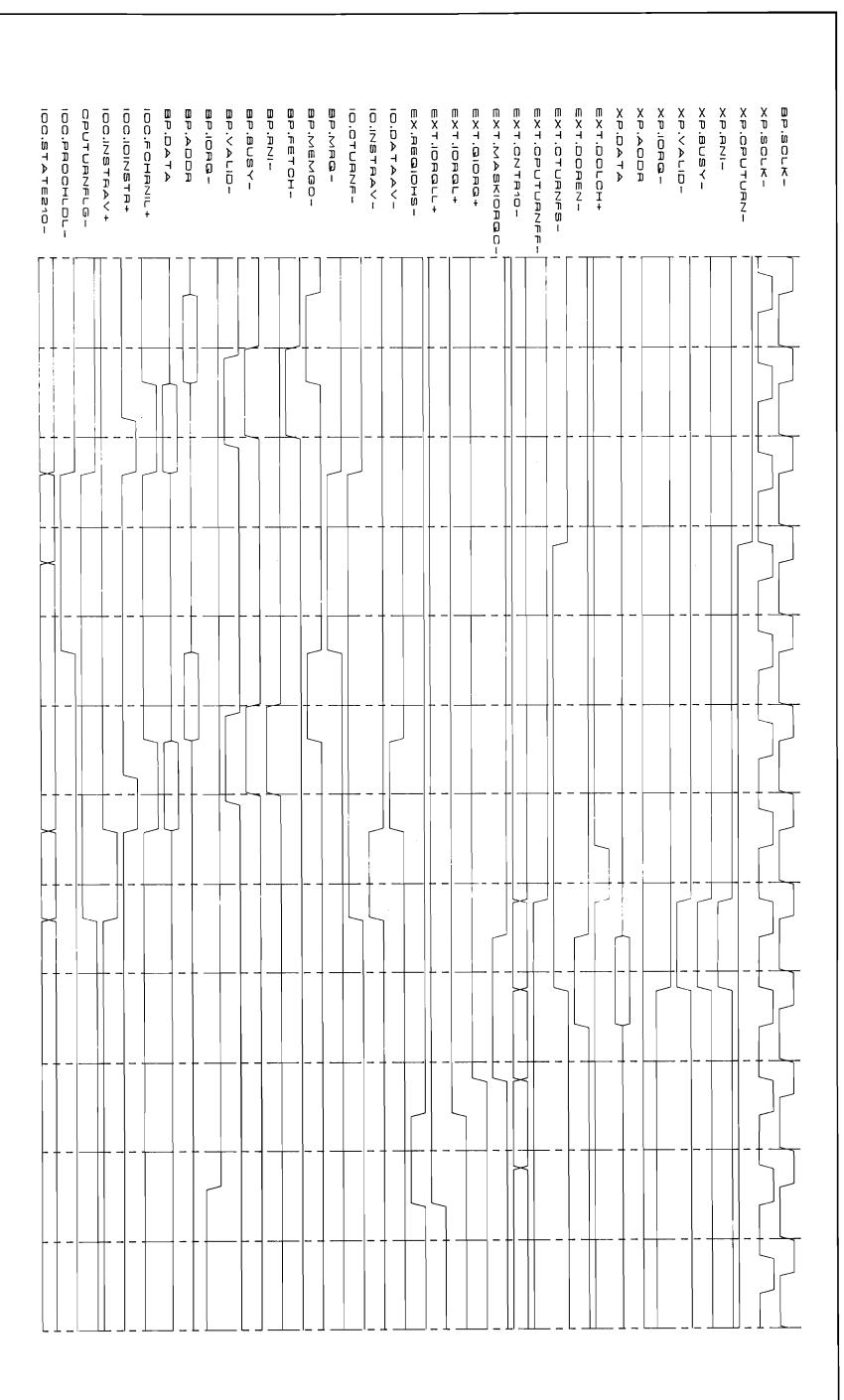

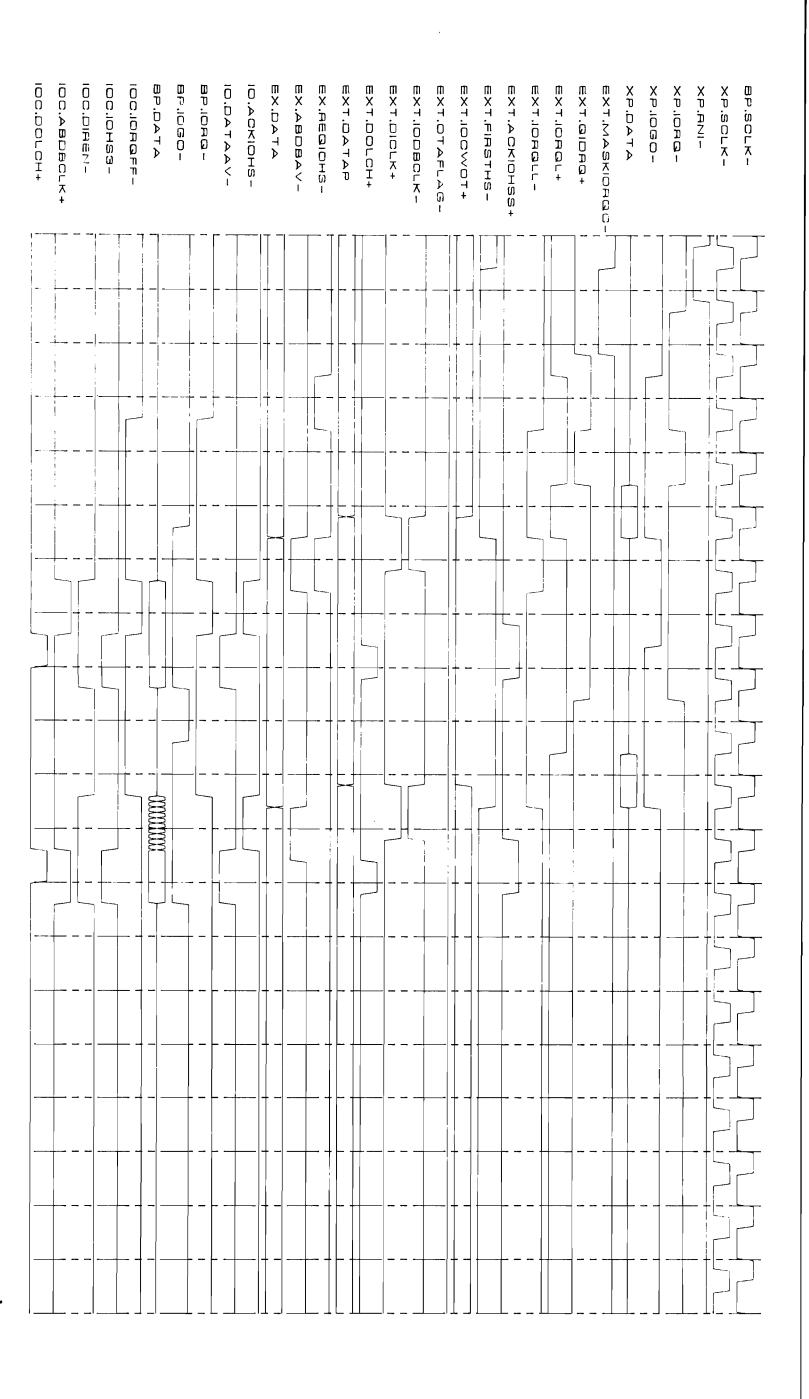

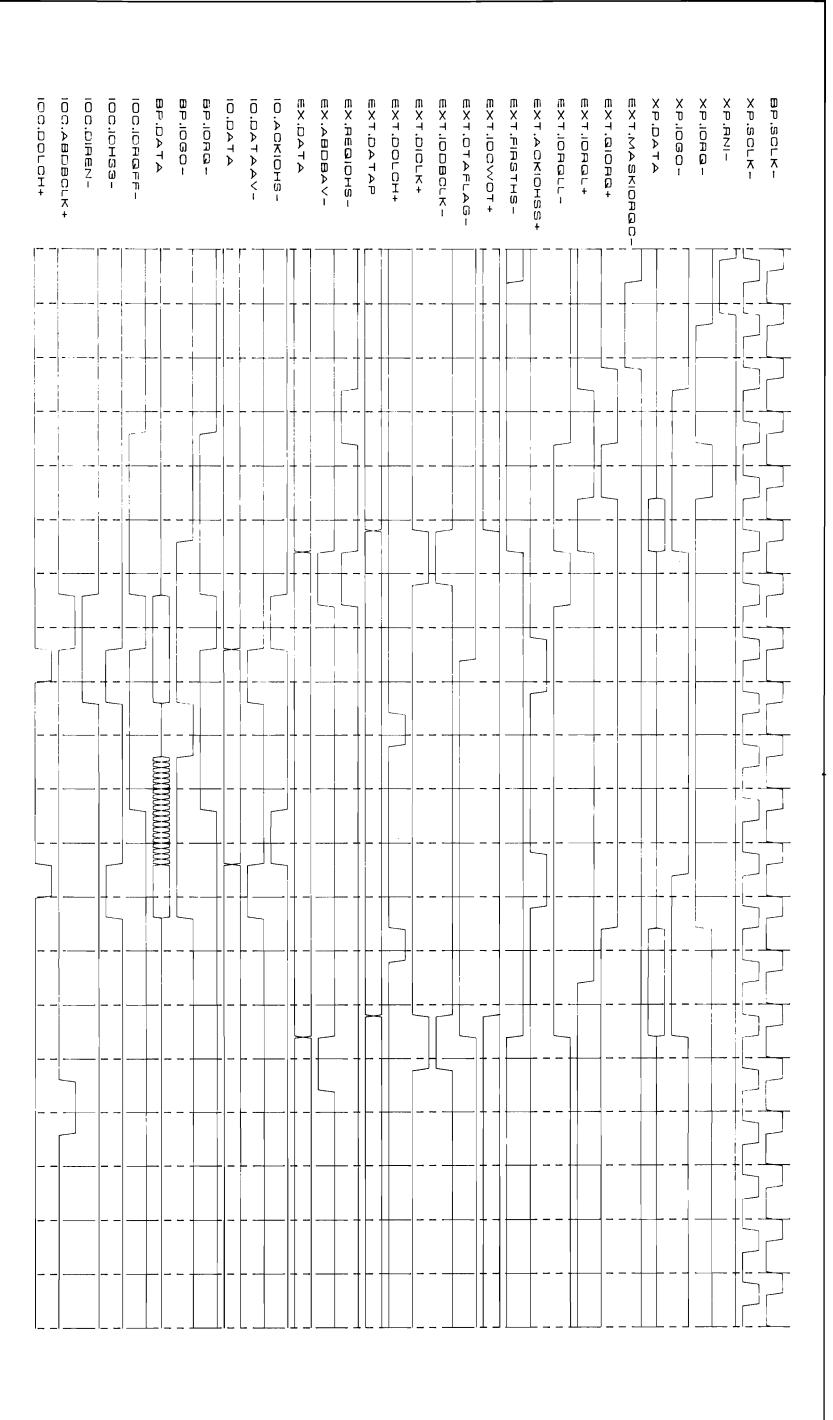

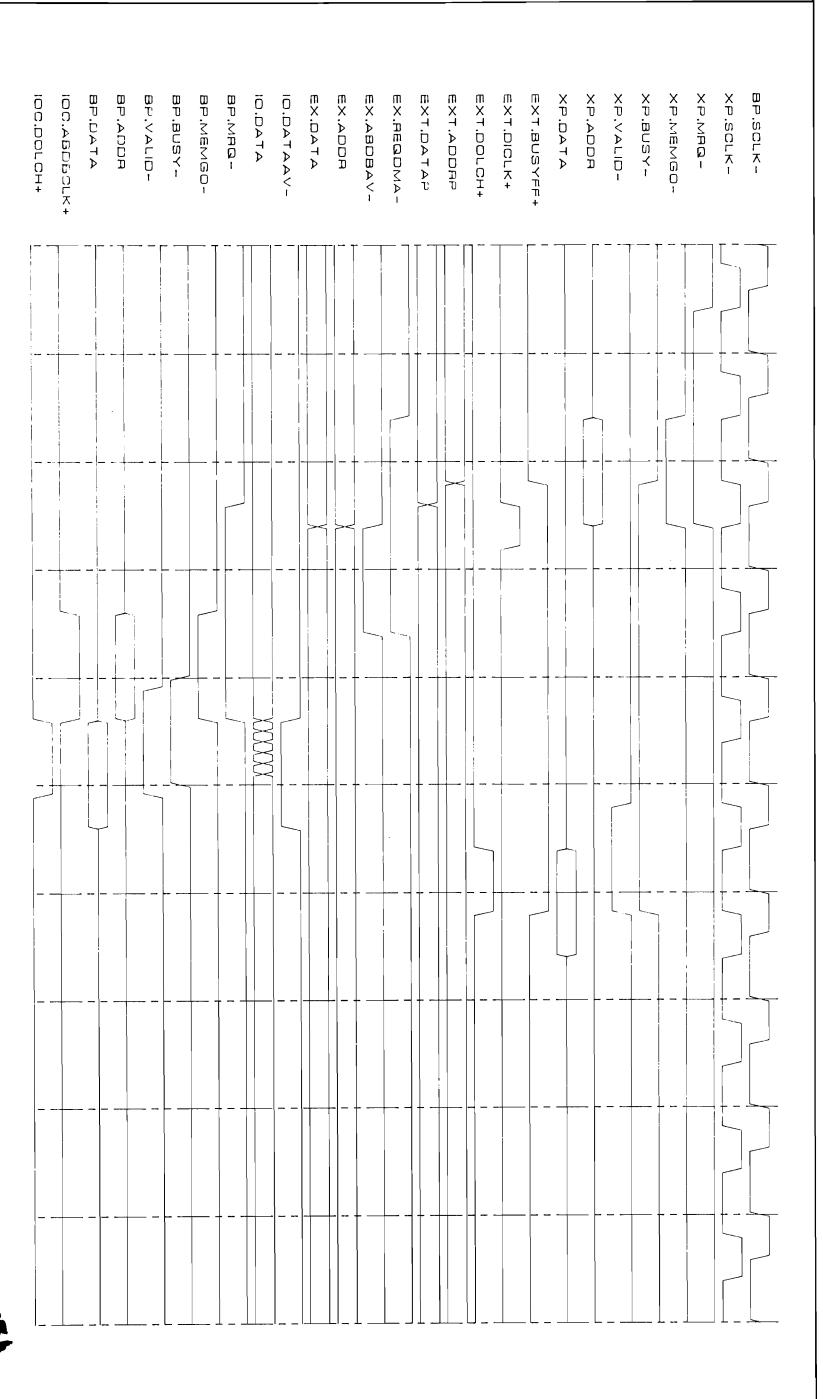

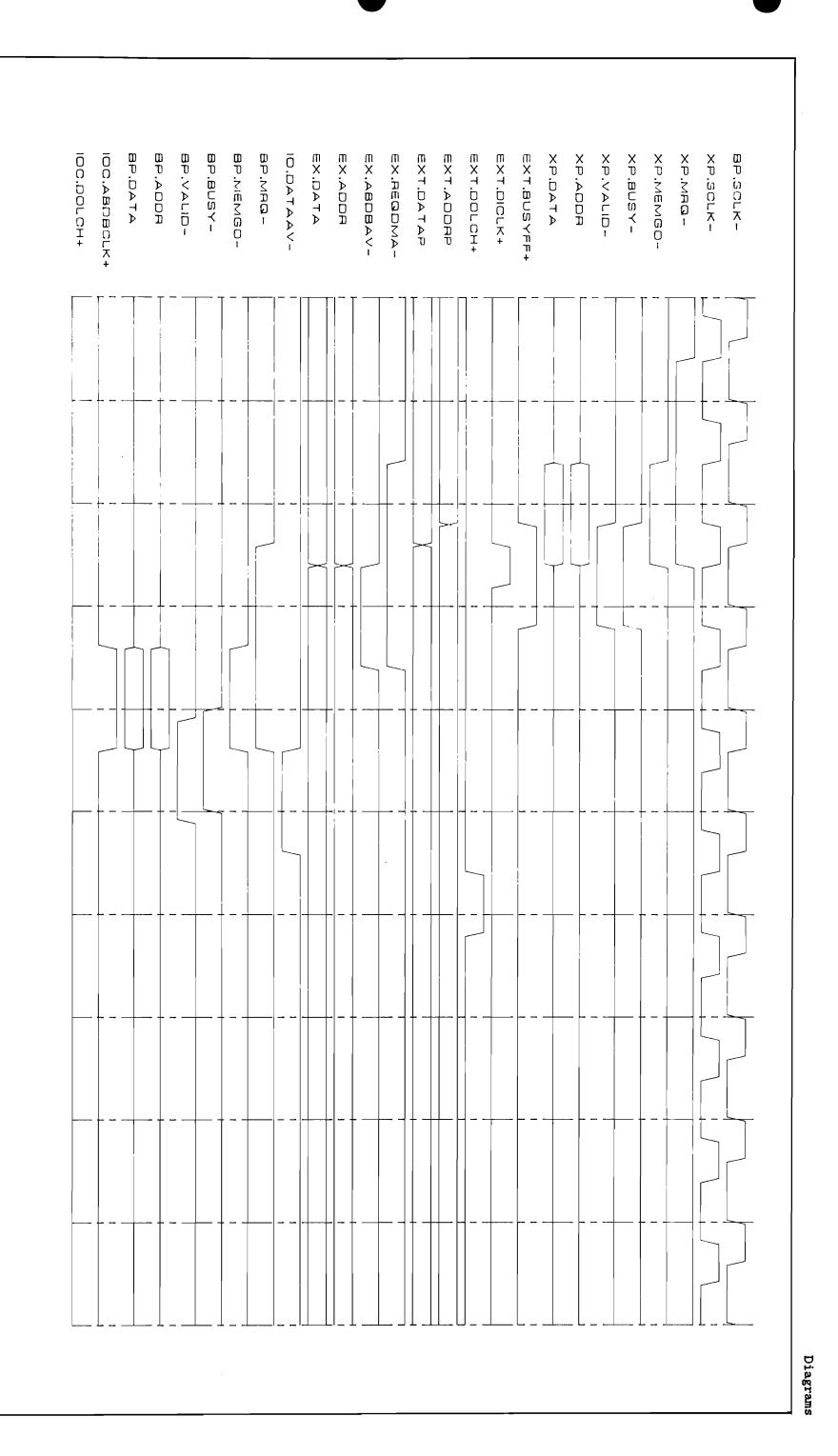

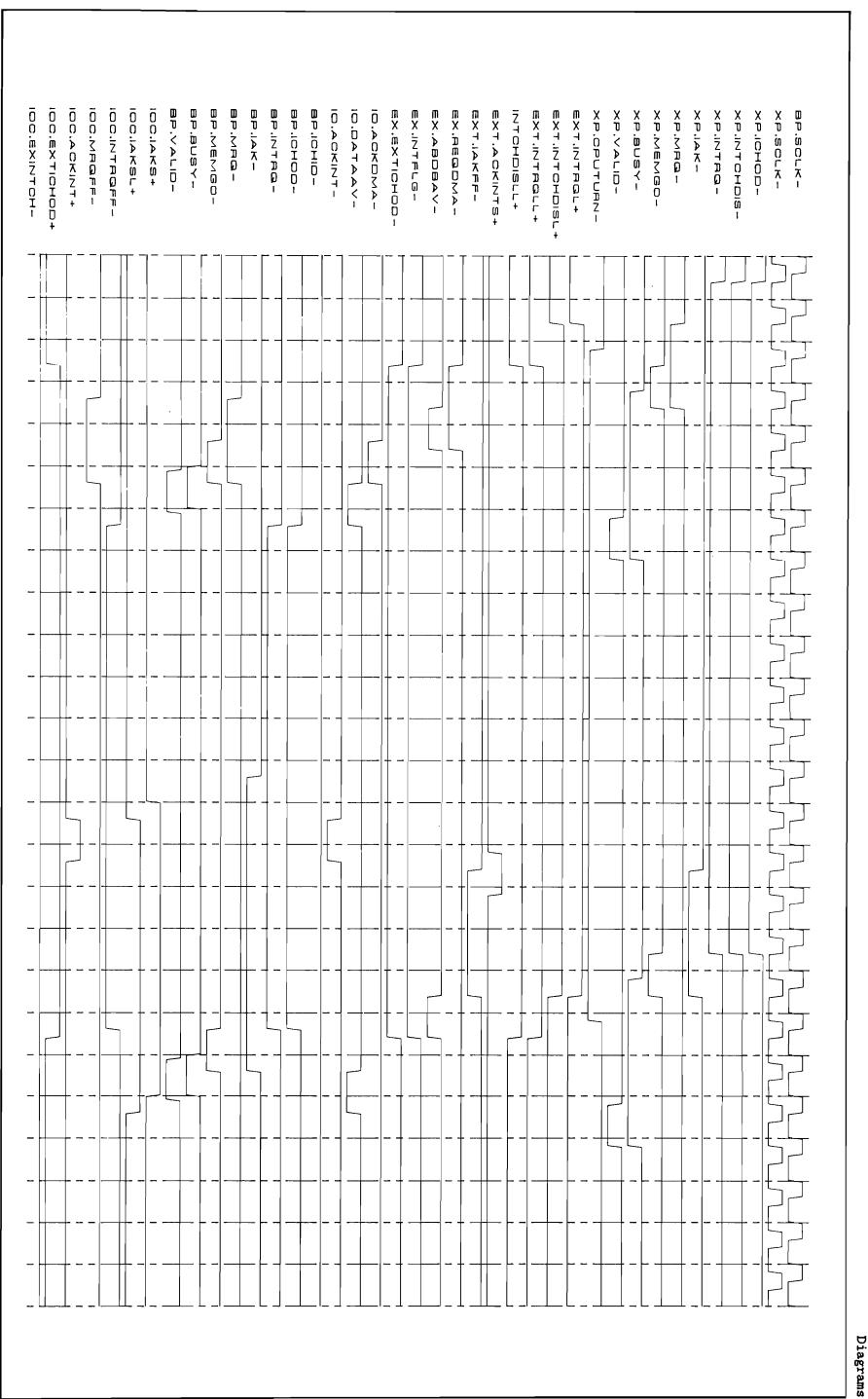

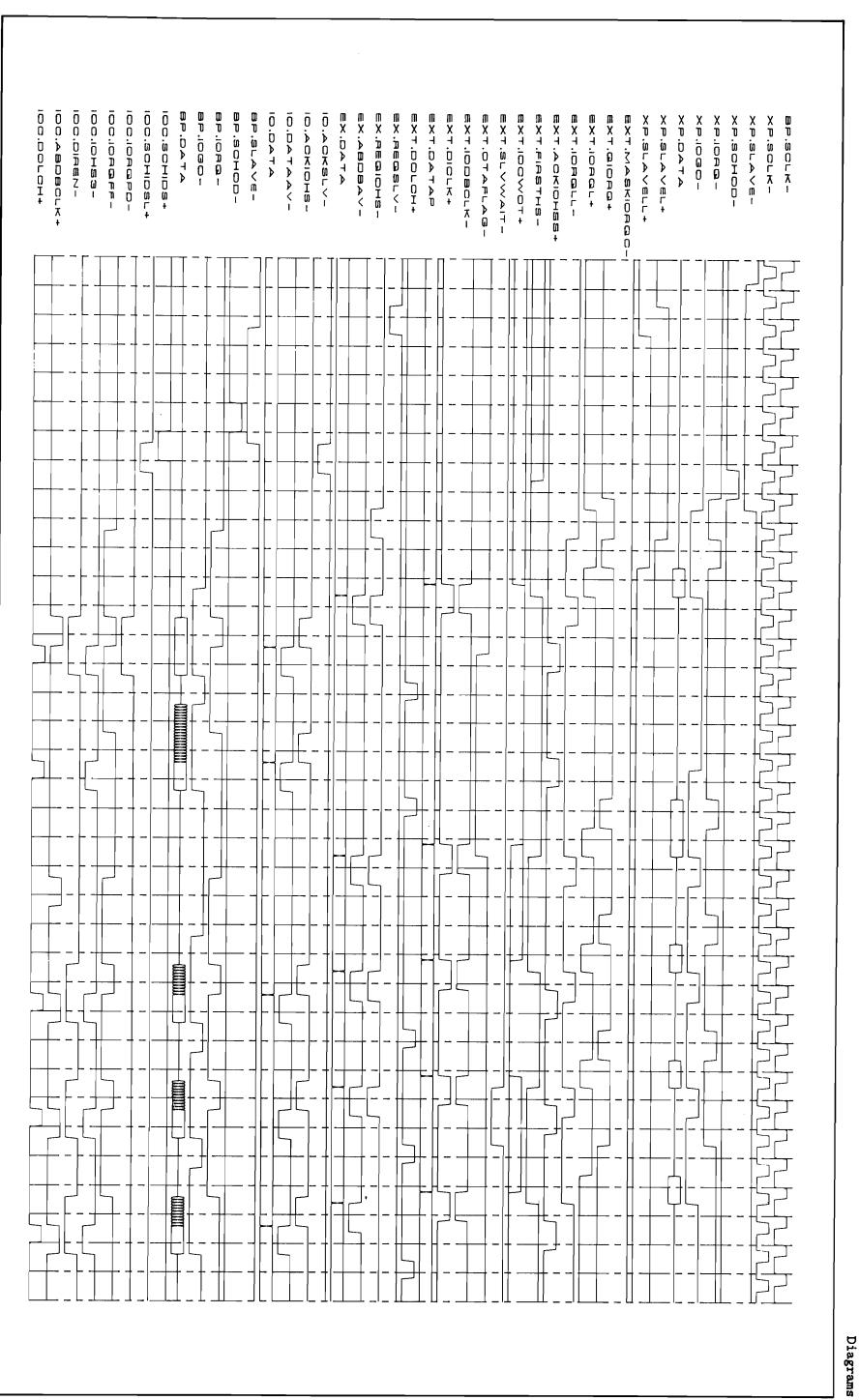

| Reading the Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

| Clock Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

| System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| Communications Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

| What Happens at Power Up and Power Down 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

| PON Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

| Extender Box Power Transitions 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

| LED Status Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| Processor Freeze at Power Up 5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31           |

| Power Fail Auto Restart Features 5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31           |

| Power Fail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32           |

| Power Up Auto Restart 5-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33           |

| Maintaining MLOST Status 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·36          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ∙38          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -38          |