# HP 12005A Asynchronous Serial Interface

# **†** Reference Manual

**REFERENCE MANUAL**

# HP 12005A ASYNCHRONOUS SERIAL INTERFACE

Manual Part No. 12005-90001

Printed in U.S.A. January 1980

Card Assembly: 12005-60001 Date Code: A-2001, B-2001

HEWLETT-PACKARD COMPANY Data Systems Division 11000 Wolfe Road Cupertino. California 95014

Library Index No. 12005.320.12005-90001

# **MANUAL UPDATE**

#### MANUAL IDENTIFICATION

Title: HP 12005A Asynchronous Serial Interface Reference Manual Part Number: 12005-90001

### **UPDATE IDENTIFICATION**

Update Number: 1 June 1980 This Packet 2 May 1981 also Includes:

Edition: First Edition

Edition or Reprint Date: Jan 1980

# THE PURPOSE OF THIS MANUAL UPDATE

is to provide new information for your manual to bring it up to date. This is important because it ensures that your manual accurately documents the current version of the software.

#### THIS UPDATE CONSISTS OF

this cover sheet, a printing history page or a revised "List of Effective Pages," all replacement pages, and write-in instructions (if any). Replacement pages are identified by the update number at the bottom of the page. A vertical line (change bar) in the outside margin indicates new or changed text material. The change bar is not used for typographical or editorial changes that do not affect the text.

#### TO UPDATE YOUR MANUAL

identify the latest Update (if any) already contained in your manual by referring to the Printing History Page or List of Effective Pages (page ii). Incorporate only the Updates from this packet not already included in your manual. Following the instructions on the back of this page, replace existing pages with the Update pages and insert new pages as indicated. If any page is changed in two or more Updates, such as the Printing History Page which is furnished new for each Update, only the latest page will be included in the Update package. Destroy all replaced pages. If "write-in" instructions are included they are listed on the back of this page.

HEWLETT-PACKARD COMPANY Data Systems Division 11000 Wolfe Road Cupertino, California 95014

#### TECHNICAL MANUAL UPDATE

(12005 - 90001)

٠,

#### UPDATE NO.

1

#### DESCRIPTION

Page 1-1. Under Sections 1-8 entitled options add:

Option 004: 48 pin connector kit Option 005: Cable 12005-60005, used for 2645A.

Insert page 7-19.

Page vii. Under <u>Tables</u> add:

Interface cable wire list for 12005 Page 7-19

Page 2-6. Under Section 2-15 entitled Baud Rate Selection add:

The external clock (x16) setting (U21S1-U21S4 all closed) is not supported with prefabricated HP supplied cables.

Title Page/ii and iii/iv. Remove and replace with new pages.

UPDATE NO

#### DESCRIPTION

2

This manual update does not apply to 12005A with Date Code earlier than 2104.

Replace every where: Card Assembly 12005-60001 by Card Assembly 12005-60007 Date Code is : A-2104

Page 2-6 Delete Note : Switches U21 S7 and S8 are not used

Page 2-6 P.2-18C Add : U21 S7 Must be open (up)

U21 S8 Must be closed (down)

۰.

**REFERENCE MANUAL**

# HP 12005A ASYNCHRONOUS SERIAL INTERFACE

Manual Part No. 12005-90001

Printed in U.S.A. January 1980 Update 1 - June 1980

Card Assembly: 12005-60001 Date Code: A-2001, B-2001

HEWLETT-PACKARD COMPANY Data Systems Division 11000 Wolfe Road Cupertino, California 95014

ي ا

Library Index No. 12005.320.12005-90001

# **PRINTING HISTORY**

New editions are complete revisions of the manual. Update packages contain replacement pages or write-in instructions to be merged into the manual by the customer. Manuals will be reprinted as necessary to incorporate all prior updates. A reprinted manual is identical in content (but not in appearance) to the previous edition with all updates incorporated. No information is incorporated into a reprinting unless it appears as a prior update. The edition does not change.

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATER-IAL, INCLUDING, BUT NOT LIMITED TO. THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

# LIST OF EFFECTIVE PAGES

The List of Effective Pages gives the most recent update number on which the technical material on any given page was altered. If a page is simply re-arranged due to a technical change on a previous page, it is not listed as a updated page. Within the manual, changes are marked with a vertical bar in the margin. When a update is incorporated in a reprinted manual, the update number and vertical bar in the margin is removed but the update number will remain on this List of Effective Pages page.

| Pages                                       | Update No.            | Pages | Update No. |

|---------------------------------------------|-----------------------|-------|------------|

| Title<br>ii<br>iii/iv<br>1-1<br>2-6<br>7-19 | 1<br>1<br>1<br>1<br>1 |       |            |

1 ... N.

# Table 7-1. Interface cable wire list for 12005.

| (PCA)<br>J1- | SIGNAL<br>NAME | SIGNAL DEFINITION                          | WIRE<br>COLOR<br>NOTE 1) | RS-<br>232C | RS-<br>449 | SIGNAL<br>SOURCE | J2       | J2    | J2  | J2      |

|--------------|----------------|--------------------------------------------|--------------------------|-------------|------------|------------------|----------|-------|-----|---------|

| A            | GND            |                                            |                          |             |            |                  |          |       |     |         |

| 1            | GND            |                                            | <b>NT 11</b>             | CE          | IC         | Dev              |          |       | 22  |         |

| в            | *IC(A)         | Incoming Call (A)                          | BLU                      |             | RS         | Intfc '          |          |       |     |         |

| 2            | *RS(B)         | Request to Send (B)                        |                          | U.A.        | ~~         | Incre            |          | · ۱   |     |         |

| С            | RIC            | Used by diagnostics only                   |                          | CA          | RS         | Intfc            |          |       |     |         |

| 3            | *RS(A)         | Request to Send (A)                        |                          |             | <b>N</b> 0 | 1                | •        |       |     |         |

| D            | TTYI           | Teleprinter Input                          |                          |             |            |                  |          |       |     |         |

| 4            | TTYI           | Teleprinter Input                          | RED                      | CA          | +          | Intfc            | 44       | 5     | 4   | E,J (OR |

| Е            | **RS(U)        | Request to Send (U)                        | KED .                    | ~~          | -          |                  | 1        |       |     | -       |

| 5            | DRST           | Reset line used by diagnostics only        |                          | CE          | IC         | Dev              |          |       | Δ   |         |

| F            | *IC(B)         | Incoming Call (B)                          |                          |             |            | 500              |          |       |     |         |

| 6            | RDM            | Used by diagnostics only                   |                          |             | 1          |                  |          |       | 1   |         |

| н            | RCS            | Used by diagnostics only                   |                          |             |            |                  | 1        |       | 1   |         |

| 7            | EXTCLK         | Clock from External Device(if any)(16X)    |                          |             |            |                  |          |       |     |         |

| J            | +5V            | +5 to terminal                             |                          |             |            | 1                |          |       |     | 1       |

| 8            | ECHOM          | Used by diagnostics only                   |                          |             | 1          |                  | <u>ا</u> | 1     |     |         |

| к            | SPC2           | Used by diagnostics only                   | l.                       | ВА          | SD         | Intfc            |          |       |     | 1       |

| 9            | *SD(B)         | Send Date (B)                              |                          | <b></b>     |            |                  |          |       |     | 1       |

| L            | RRR            | Used by diagnostics only                   |                          | ВА          | SD         | Intfc            |          |       | 1   | 1       |

| 10           | *SD(A)         | Send Data (A)                              | GRN                      | CD          | TR         | Intfc            |          | 8     | 20  |         |

| м            | TR             | Terminal Ready                             | GRA                      |             | 1          |                  |          |       |     | l       |

| 11           | SBS            | Stop Bit Select                            | GRN                      |             |            | Intfc            | 46       |       |     |         |

| N            | TTY+12         | +12 to teleprinter                         | GAN                      |             |            | 1                |          |       |     | 1       |

| 12           | TTY+12         | +12 to teleprinter                         |                          |             |            |                  |          |       |     |         |

| Р            | RDRCNTL        | Reader Control (GND)                       |                          |             | 1          |                  |          |       |     |         |

| 13           | RDRCNTL        | Reader Control (GND)                       |                          |             | -          | 1                |          |       |     |         |

| R            | TTY-12         | -12 to teleprinter                         | 1                        | 1           |            |                  |          |       |     | 1       |

| 14           | TTY-12         | -12 to teleprinter                         | WHT                      | BB          | RD         | Dev              | 12       | 2     | 3   | B (BR   |

| S            | *RD(B)         | Receive Data (B)                           | WHT-BRN                  | -           | SRD        | Dev              | 1        |       | 16  |         |

| 15           | *SRD(A)        | Secondary Receive Data (A)                 | WHI-DIG                  |             | 1          |                  |          |       |     | 1       |

| Т            | TTYO           | Output to teleprinter                      | 1                        |             |            |                  |          |       | 1   |         |

| 16           | TTYO           | Output to teleprinter                      | 1                        | BB          | RD         | Dev              | Δ        | Δ     | Δ   | △       |

| U            | *RD(A)         | Receive Data (A)                           | l                        | SBB         | SRD        |                  |          |       | Δ   |         |

| 17           | *SRD(B)        | Secondary Receive Data (B)                 | WHT-BLK                  |             | RR         |                  |          |       | 8   |         |

| v            | *RR(A)         | Receiver Ready (A)                         |                          | CF          | RR         | Dev              |          |       | ∆   |         |

| 18           | *RR(B)         | Receiver Ready (B)                         | BRN                      | BA          | 1 1        | Intfc            |          | 1 3   | 3 2 | C (RE   |

| W            | **SD(U)        | Send Data (U)                              | 1                        |             |            |                  |          |       |     |         |

| 19           | MSB-           | Most significant bit of baud rate select   | YEL                      | СВ          | l cs       | Dev              |          | 4     | 5 5 |         |

| х            | *CS(A)         | Clear to Send (A)                          |                          |             |            |                  |          |       |     |         |

| 20           | NMSB-          | Next to most significant bit of baud rate  |                          |             |            |                  | 1        | 1     |     | 1       |

|              |                | select                                     |                          | CB          | l cs       | Dev              |          | Δ     | Δ   |         |

| Y            | *CS(B)         | Clear to Send (B)                          |                          |             |            |                  |          |       |     |         |

| 21           | NLSB+          | Next to least significant bit of baud rate | ·                        |             |            | 1                |          |       |     |         |

|              |                | select                                     | GRA                      | l cc        | DM         | [ Dev            |          |       | 6   | 5       |

| Z            | *DM(A)         | Data Mode (A)                              |                          | 1           |            | 1                |          | 1     |     | 1       |

| 22           | LSB+           | Least significant bit of baud rate select  |                          | CC CC       | DN         | 1 Dev            |          |       | Δ   |         |

| AA           | *DM(B)         | Data Mode (B)                              |                          | SBA         |            |                  |          | 1     |     |         |

| 23           | SSD            | Secondary Send Data                        | BLK                      |             | 1          | 1                | Δ        | .   ∆ | Δ   | Δ       |

| BB           | GND            |                                            | BLK                      |             |            |                  | _   ∆    | .   ∆ | Δ   |         |

| 24           | GND            |                                            |                          | 1           |            | 1                |          |       |     | 1       |

NOTE: 1. Wire colors do not apply for 12005-60005.

\* Indicates differential driver or receiver used on this signal.

\*\* Indicates single-ended driver used on this signal.

+ RS-449 recommends the use of differential drivers.

$\Delta$  These pins are connected within the PCA cable hood for the specific cable.

7-19

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

New editions are complete revisions of the manual. Update packages contain replacement pages or write-in instructions to be merged into the manual by the customer. Manuals will be reprinted as necessary to incorporate all prior updates. A reprinted manual is identical in content (but not in appearance) to the previous edition with all updates incorporated. No information is incorporated into a reprinting unless it appears as a prior update. The edition does not change.

First Edition ..... Jan 1980

### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATER-IAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

# LIST OF EFFECTIVE PAGES

The List of Effective Pages gives the most recent update number on which the technical material on any given page was altered. If a page is simply re-arranged due to a technical change on a previous page, it is not listed as a updated page. Within the manual, changes are marked with a vertical bar in the margin. When a update is incorporated in a reprinted manual the update number and vertical bar in the margin is removed but the update number will remain on this page.

First Edition.....Jan 1980

Pages

Update No.

Pages

Update No.

.

Q

\* .

# SAFETY CONSIDERATIONS

**GENERAL** - This product and relation documentation must be reviewed for familiarization with safety markings and instructions before operation.

SAFETY SYMBOLS

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect the product against damage.

Indicates hazardous voltages.

Indicates earth (ground) terminal (sometimes used in manual to indicate circuit common connected to grounded chassis).

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

CAUTION

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

# CAUTION

#### STATIC SENSITIVE DEVICES

Some of the semiconductor devices used in this equipment are susceptible to damage by static discharge. Depending on the magnitude of the charge, device substrates can be punctured or destroyed by contact or mere proximity to a static charge. These charges are generated in numerous ways such as simple contact, separation of materials, and normal motions of persons working with static sensitive devices. When handling or servicing equipment containing static sensitive devices, adequate precautions must be taken to prevent device damage or destruction. Only those who are thoroughly familiar with industry accepted techniques for handling static sensitive devices should attempt to service the cards with these devices. In all instances, measures must be taken to prevent static charge buildup on work surfaces and persons handling the devices. Cautions are included through this manual where handling and maintenance involve static sensitive devices.

**SAFETY EARTH GROUND** - This is a safety class I product and is provided with a protective earthing terminal. An uninterruptible safety earth ground must be provided from the main power source to the product input wiring terminals, power cord, or supplied power cord set. Whenever it is likely that the protection has been impaired, the product must be made inoperative and be secured against any unintended operation.

**BEFORE APPLYING POWER** - Verify that the product is configured to match the available main power source per the input power configuration instructions provided in this manual.

If this product is to be energized via an auto-transformer (for voltage reduction) make sure the common terminal is connected to the earth terminal of the main power source.

SERVICING

## WARNING

Any servicing, adjustment, maintenance, or repair of this product must be performed only by qualified personnel.

Adjustments described in this manual may be performed with power supplied to the product while protective covers are removed. Energy available at many points may, if contacted, result in personal injury.

Capacitors inside this product may still be charged even when disconnected from its power source.

To avoid a fire hazard, only fuses with the required current rating and of the specified type (normal blow, time delay, etc.) are to be used for replacement.

Eye protection must be worn when removing or inserting integrated circuits held in place with retaining clips.

# CONTENTS

| Section I<br>INTRODUCTION | Page |

|---------------------------|------|

| Introduction              | 1-1  |

| Description               | 1-1  |

| General                   | 1-1  |

| Physical Description      | 1-1  |

| Identification            | 1-1  |

| Product                   | 1-1  |

| Circuit Card              | 1-1  |

| Options                   | 1-1  |

| Reference Manual          | 1-1  |

| Specifications            | 1-4  |

| Section II Page                     |

|-------------------------------------|

| INSTALLATION                        |

| Introduction                        |

| Unpacking and Inspection 2-1        |

| Preparation for Installation2-1     |

| Computation of Current Requirements |

| Interface Requirements              |

| Backplane to HP 12005A Asynchronous |

| Serial Interface                    |

| HP 12005A Asynchronous Serial       |

| Interface to Terminal 2-1           |

| RS-449 Interface                    |

| Teleprinter Interface2-4            |

| Connector J1 Pin Connections        |

| Hardwired Options                   |

| Switch Selectable Options           |

| Virtual Control Panel (VCP)         |

| Interface Selection                 |

| Select Code Selection               |

| Baud Rate Selection2-6              |

| Stop Bit Selection                  |

| Parity Sense Selection              |

| Installation                        |

| Checkout                            |

| Reshipment                          |

| Section III Pag<br>PROGRAMMING       |

|--------------------------------------|

| Introduction                         |

| Use of the Global Register 3-:       |

| I/O Instruction Set                  |

| Instruction Usage Summary            |

| Output Control Word                  |

| Input Status Word                    |

| Direct Memory Access (DMA) Operation |

| DMA Control Words 3-                 |

| DMA Control Register 3-'             |

| DMA Address Register                 |

| DMA Transfer Operation                   | 3-8  |

|------------------------------------------|------|

| DMA Input Transfer                       | 3-8  |

| DMA Output Transfer                      | 3-8  |

| DMA Transfer Termination                 |      |

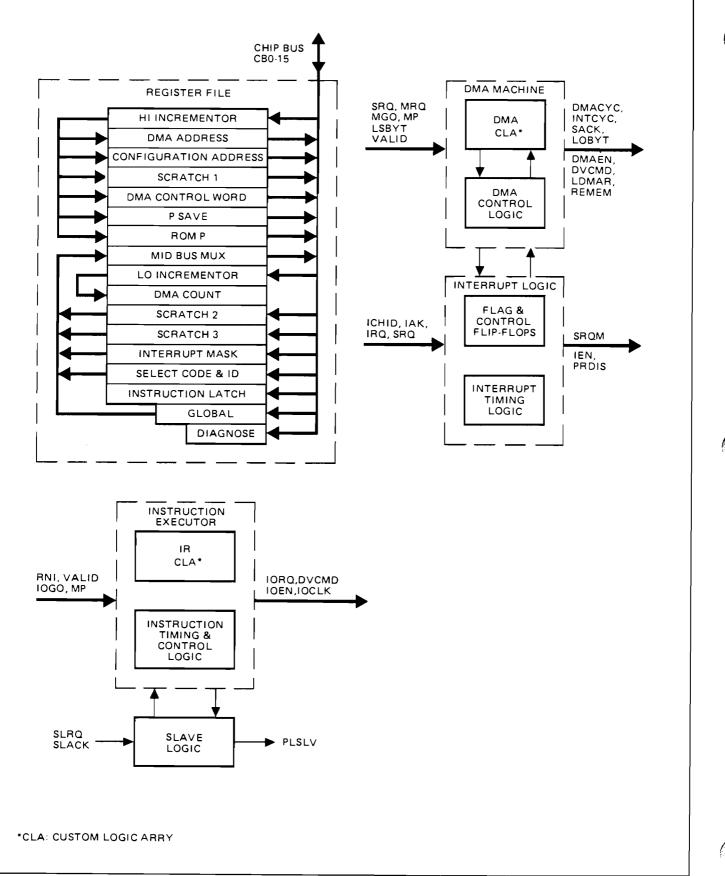

| DMA Self-Configuration Feature           |      |

| DMA Self-Configuration Initialization    |      |

| DMA Self-Configuration Operation         |      |

| DMA Self-Configuration Termination       | 3-9  |

| Format Summary                           |      |

| Control Word Output (Register Number 31) |      |

| Status Word Input (Register Number 32)   |      |

| DMA Register Number 20 (In or Out)       |      |

| DMA Register Number 21 (In or Out)       |      |

| DMA Register Number 22 (In or Out)       |      |

| DMA Register Number 23 (In or Out)       |      |

| DMA Byte Mode Data (In or Out)           |      |

| (Register Number 30)                     | 3-11 |

| DMA Word Mode Data or Non-DMA Data       |      |

| (In or Out)                              | 3-11 |

| Sample Pogrammed I/O Routine             |      |

| HP 12005A Asynchronous Serial            |      |

| Interface Initialization                 | 3-11 |

| Virtual Control Panel                    |      |

| Special Character Recognition Feature    |      |

| Summary of I/O Instruction Usage         | 3-13 |

| OTA/ÕTB                                  |      |

| LIA/LIB                                  |      |

| STC                                      |      |

| CLC                                      |      |

| STF                                      |      |

| CLF                                      |      |

|                                          |      |

.

| Section IV Page<br>THEORY OF OPERATION       |

|----------------------------------------------|

| Introduction                                 |

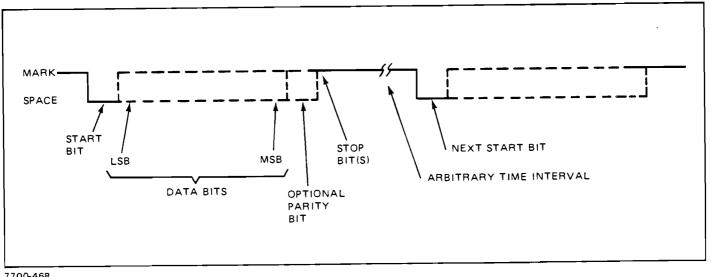

| Asynchronous Serial Communication Format 4-2 |

| Basic Operation of the Asynchronous          |

| Serial Interface                             |

| Transmit Mode 4-3                            |

| Receive Mode                                 |

| Full-Duplex Operation 4-4                    |

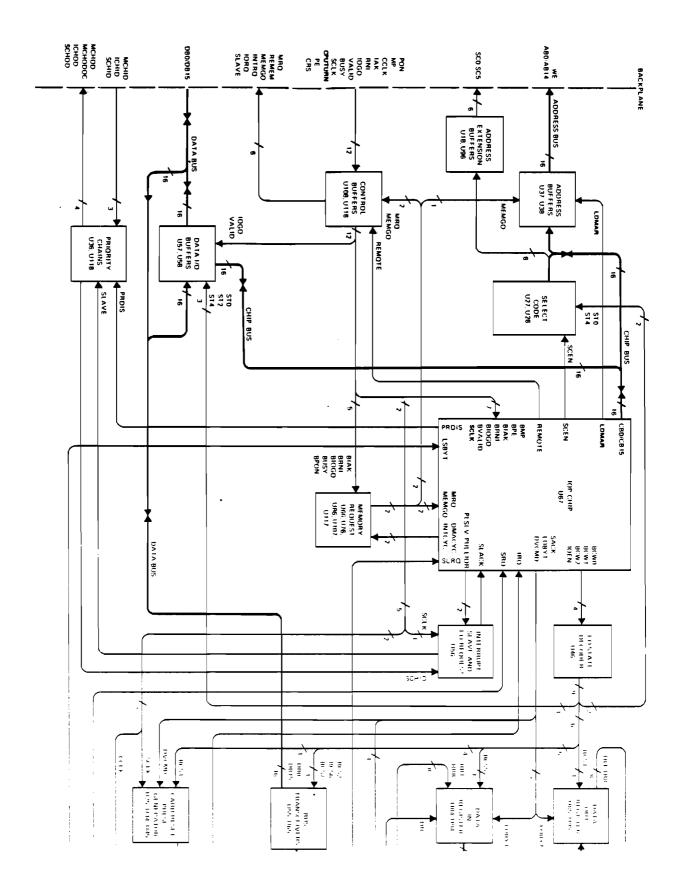

| Functional Theory of Operation 4-4           |

| Principal Data Paths 4-4                     |

| Transmitted Data Path 4-4                    |

| Received Data Path 4-4                       |

| Service Request Logic 4-6                    |

| Interrupt Request Logic 4-6                  |

| Special Character Recognition 4-6            |

| Break Character Detect                       |

| Modem Line Status Change Detect              |

| Baud Rate Generation                         |

| Card Reset Pulse Generator                   |

| Diagnostic Multiplexer 4-7                   |

| Interface-to-Terminal Signal Definitions 4-8 |

# **CONTENTS** (Continued)

| Section V                           | Page |

|-------------------------------------|------|

| MAINTENANCE                         |      |

| Introduction                        | 5-1  |

| Preventive Maintenance              | 5-1  |

| Removal and Installation Procedures |      |

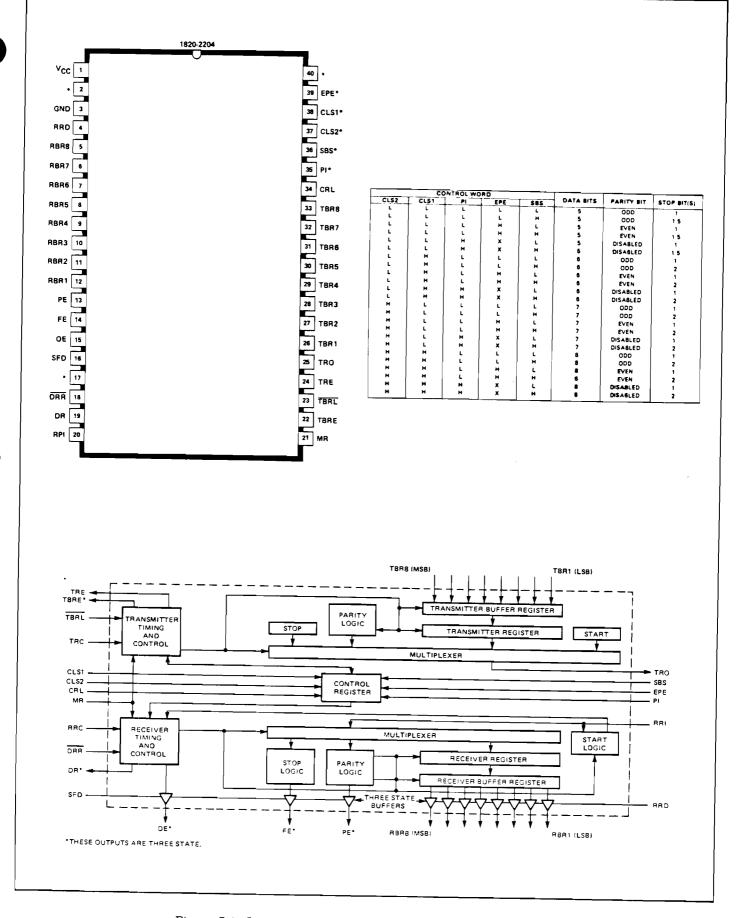

| for the IOP Chip                    | 5-1  |

| Removing the IOP Chip               | 5-1  |

| Installing the IOP Chip             | 5-1  |

| Troubleshooting                     | 5-2  |

| Iloubiconooning                     |      |

| Section VI                                                                     | Page |

|--------------------------------------------------------------------------------|------|

| REPLACEABLE PARTS<br>Introduction<br>Replaceable Parts<br>Ordering Information | 6-1  |

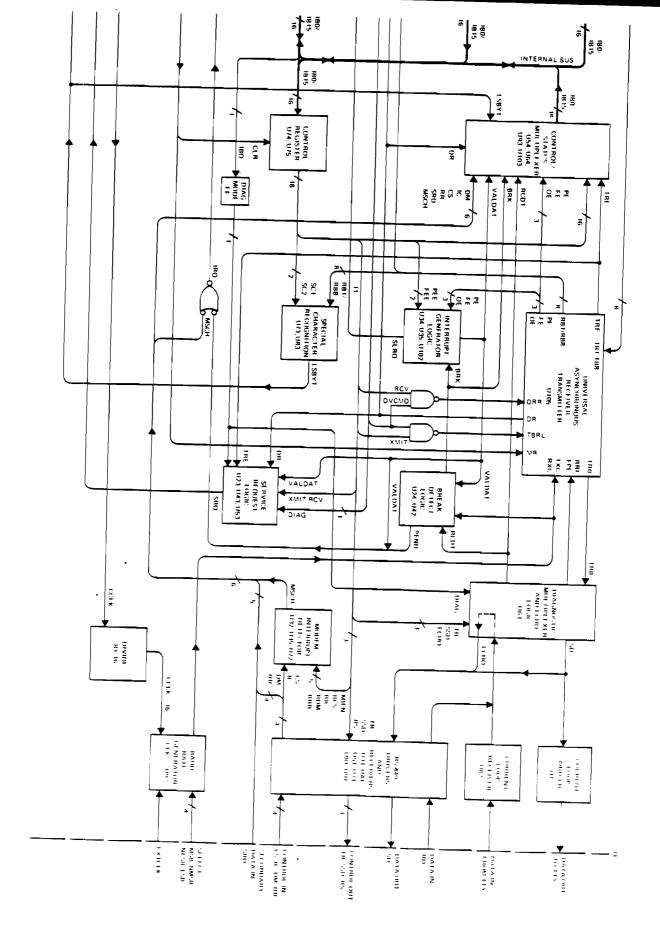

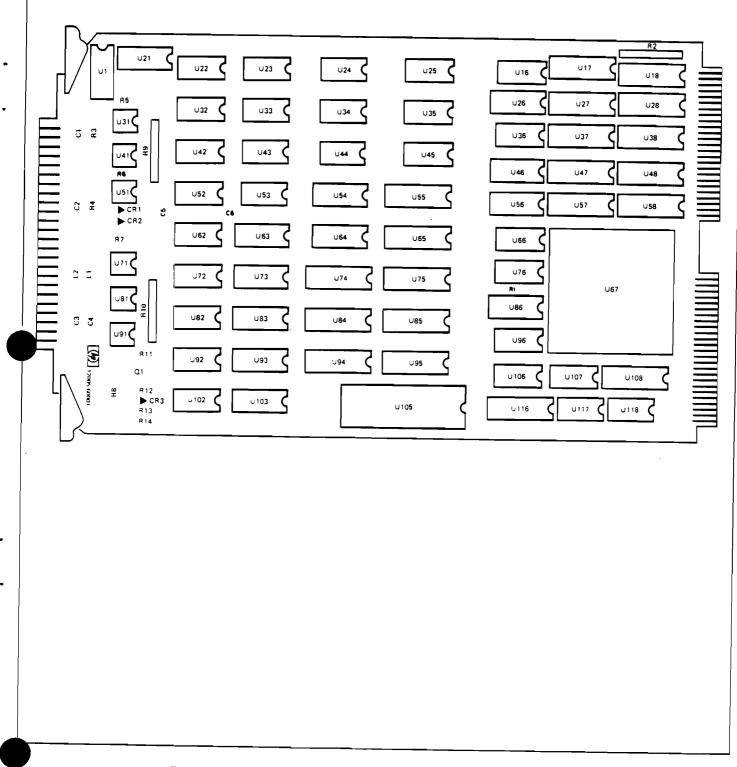

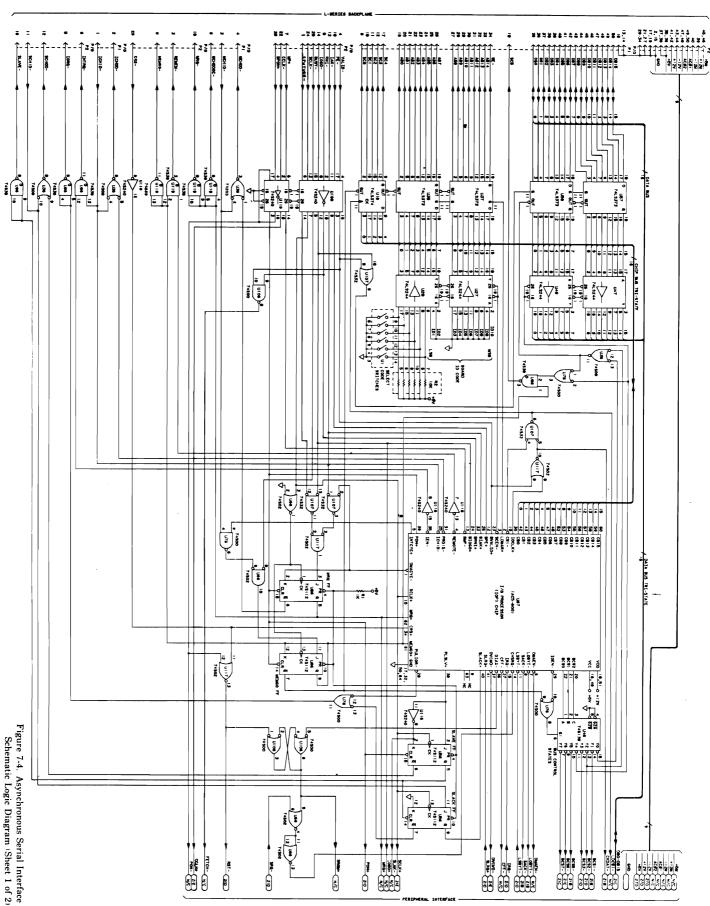

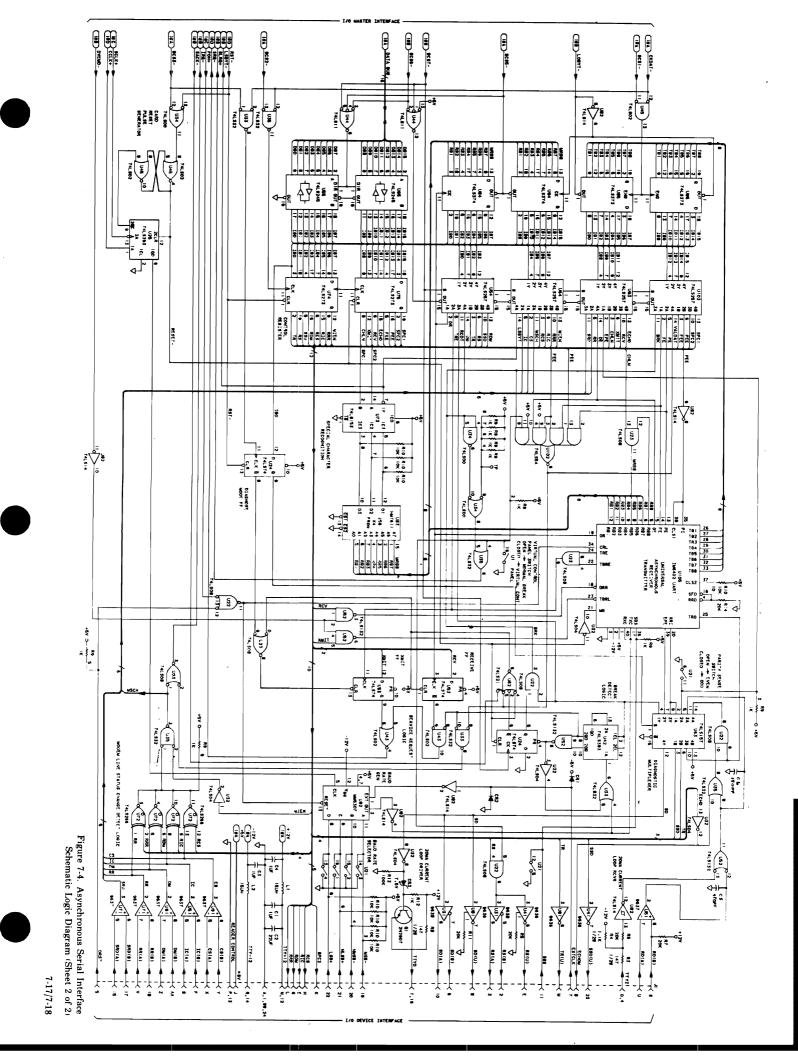

| Section VII                                                                    | Page |

| SERVICING DIAGRAMS<br>Introduction                                             | 7-1  |

| Index                                                                          | I-1  |

# **ILLUSTRATIONS**

| Title Page                                    |  |

|-----------------------------------------------|--|

| HP 12005A Asynchronous Serial Interface       |  |

| Typical L-Series Card Cage Layout             |  |

| Asynchronous Serial Interface Simplified      |  |

| Block Diagram                                 |  |

| Asynchronous Serial Interface in Typical      |  |

| System Environment                            |  |

| RS-449 Interface                              |  |

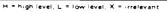

| I/O Chip Block Diagram                        |  |

| DMA Self-Configuration Feature                |  |

| Asynchronous Serial Interface in Typical      |  |

| L-Series System                               |  |

| Asynchronous Serial Communications Format 4-2 |  |

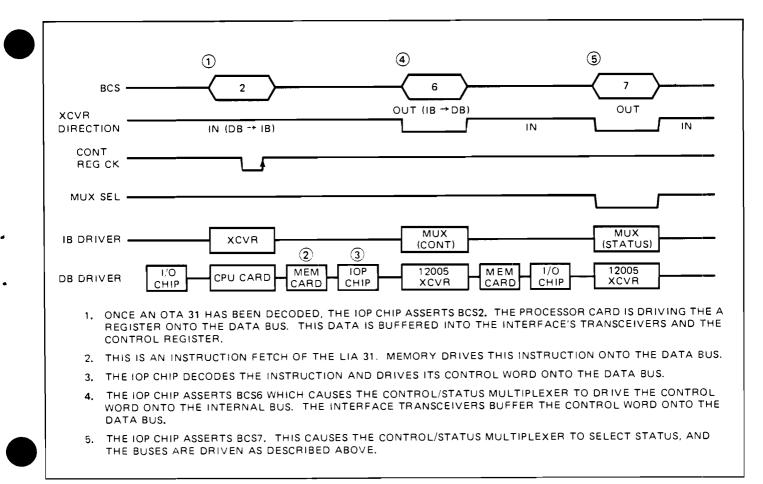

| Instructions OTA 31, LIA 31, LIA 32               |

|---------------------------------------------------|

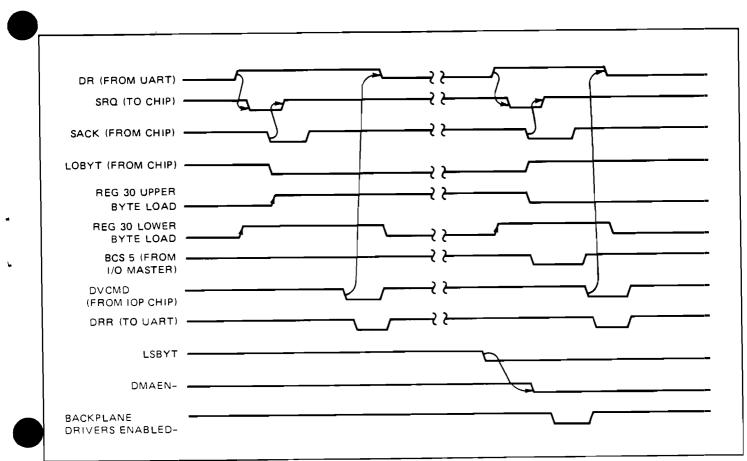

| Timing Diagram 4-3                                |

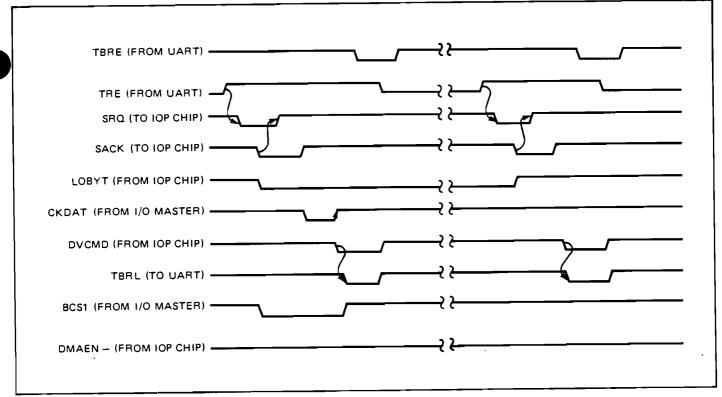

| Transmitted Data Timing Diagram                   |

| Received Data Timing Diagram 4-5                  |

| IOP Chip Socket with Chip and Retaining           |

| Clips in Place                                    |

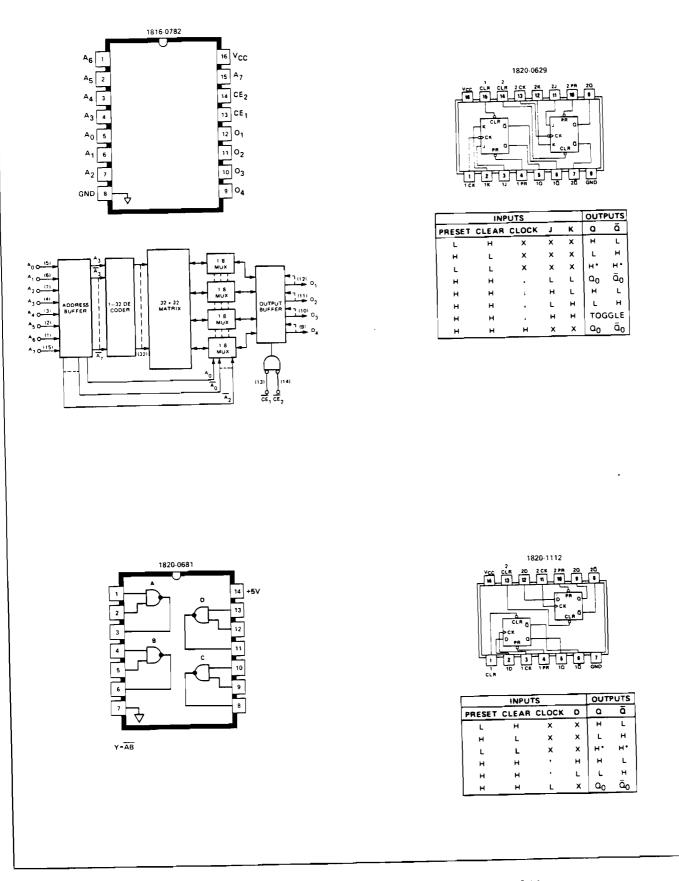

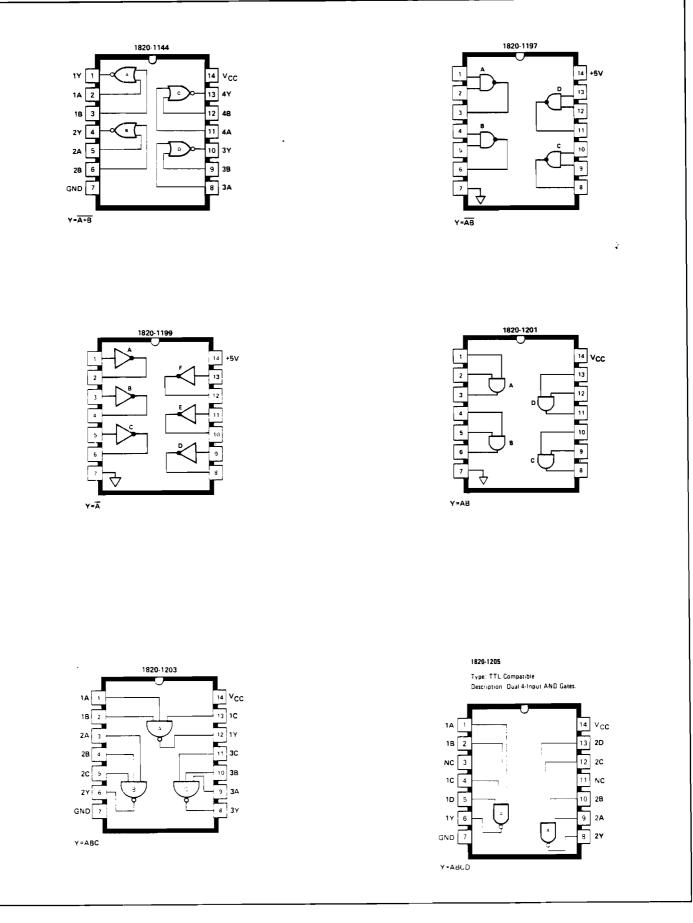

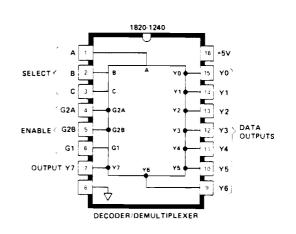

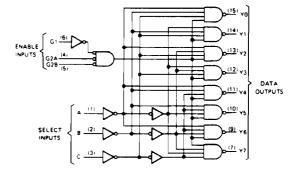

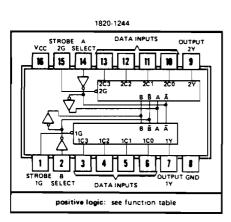

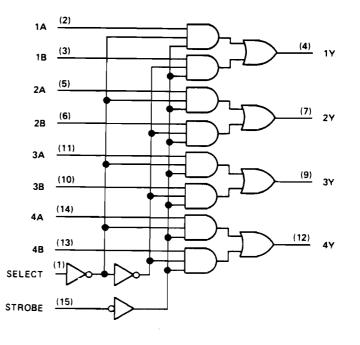

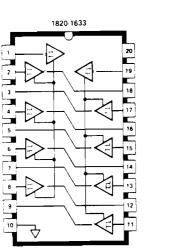

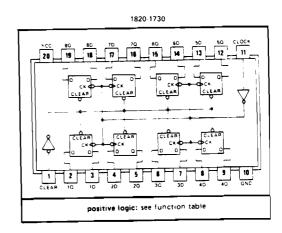

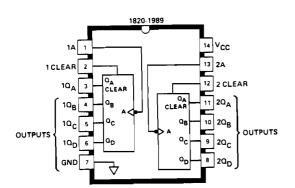

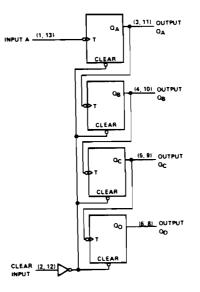

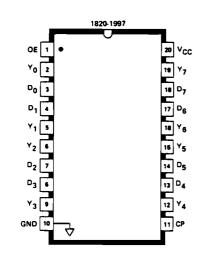

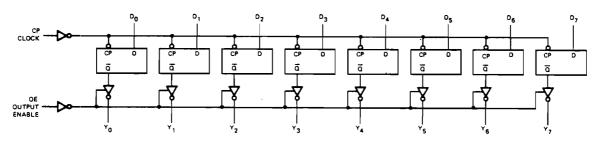

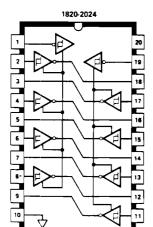

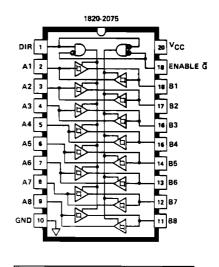

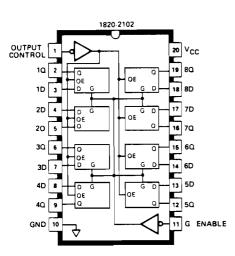

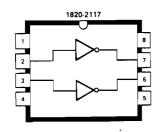

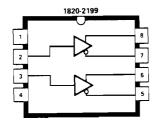

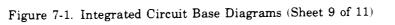

| Integrated Circuit Base Diagrams                  |

| Asynchronous Serial Interface Detailed Functional |

| Block Diagram                                     |

| Asynchronous Serial Interface Parts               |

| Location Diagram                                  |

| Asynchronous Serial Interface Schematic           |

| Logic Diagram                                     |

| LOPIC Diagram                                     |

Title

# **TABLES**

Page

| œ۰. | .1 . |

|-----|------|

| 11  | tie  |

| Title                                                                                                                                                                                                                                                       | Page                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Specifications<br>Backplane Connections, Connector P1<br>Backplane Connections, Connector P2<br>Electronics Industries Association Standards<br>RS-449 RS-232 Equivalency<br>Interface-to-Terminal (Connector J1)<br>Pin Connections<br>Baud Rate Selection | 2-2<br>2-2<br>2-3<br>2-3 |

|                                                                                                                                                                                                                                                             |                          |

| Tit                          | tle                                                                                                                                                                                                                 | Page                          |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| IO<br>Ini<br>Sp<br>Int<br>Co | P Chip Instructions by Select Code<br>itialization Functions<br>ecial Character Sets<br>terface-to-Terminal Signal Definitions<br>mmonly-Used Prefixes for Component Part<br>ference Designations and Abbreviations | 3-12<br>3-12<br>4-8<br>ts 6-1 |

| Re                           | placeable Parts<br>anufacturer's Code List                                                                                                                                                                          | 6-3                           |

# vii

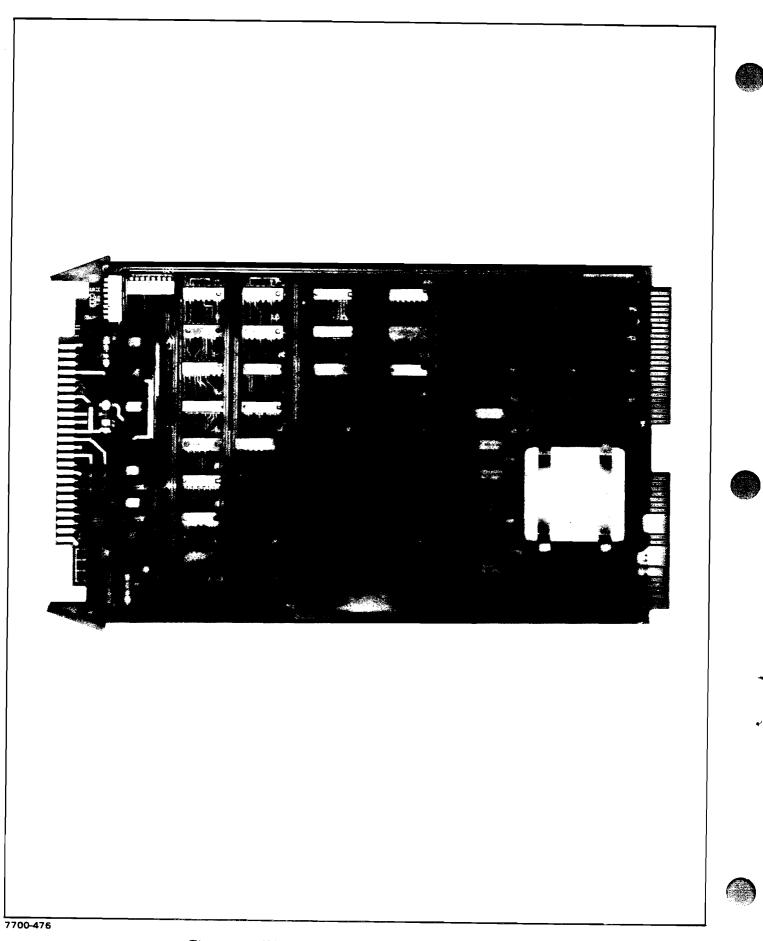

Figure 1-1. HP 12005A Asynchronous Serial Interface

**INTRODUCTION**

# **1-1. INTRODUCTION**

This manual provides general information, installation, programming instructions, theory of operation, maintenance instructions, replaceable parts information, and servicing diagrams for the Hewlett-Packard HP 12005A Asynchronous Serial Interface.

# 1-2. DESCRIPTION

# 1-3. GENERAL

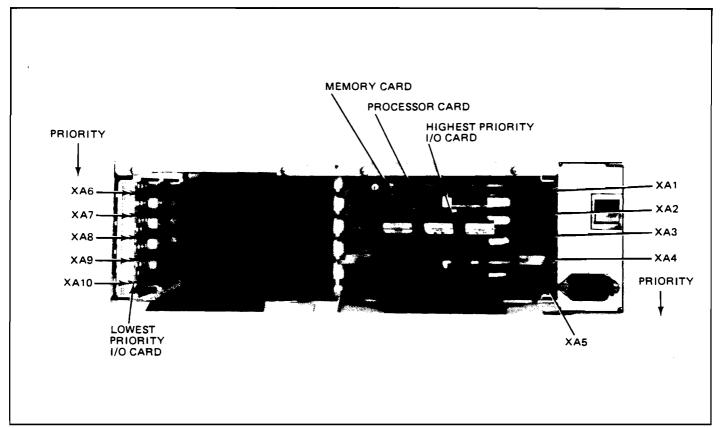

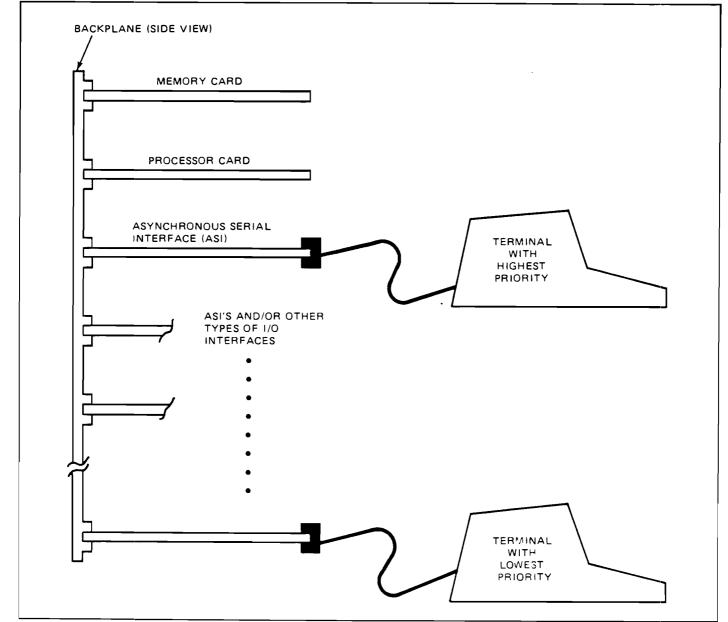

The HP 12005A Asynchronous Serial Interface provides an asynchronous serial communications link between the HP 1000 L-Series Computer and an RS-449 or RS-232 compatible terminal. The asynchronous serial interface, hereafter called the interface, plugs into a single slot in the L-Series backplane (see figure 1-2) and is assigned a single select code.

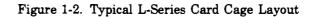

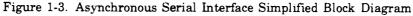

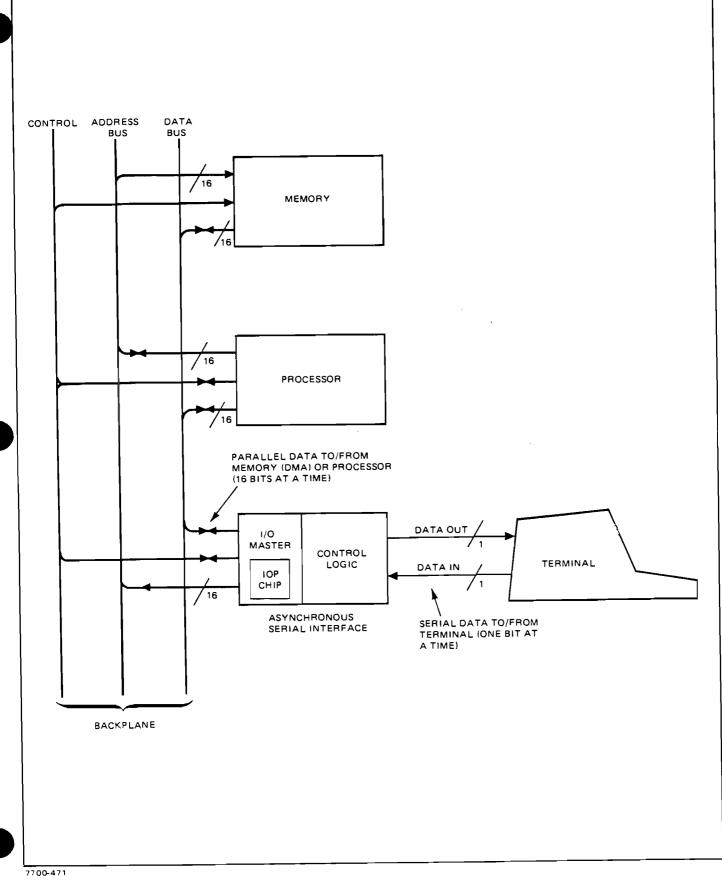

The interface has the capability of handling its own memory accesses (Direct Memory Access (DMA)), of decoding its own instructions from the central processor unit (CPU), and of forcing the CPU into slave mode processing. These features are performed by an input/output (I/O) master containing an I/O processor (IOP) integrated circuit (chip) and associated logic. This I/O master, (including the IOP chip) is located on the interface and performs all functions (including instruction recognition and DMA control) necessary for interfacing with the L-Series backplane. Figure 1-3 is a simplified block diagram of the asynchronous serial interface and figure 1-4 shows the interface in a typical L-Series system environment.

## 1-4. PHYSICAL DESCRIPTION

The HP 12005A Asynchronous Serial Interface is a single circuit card as shown in figure 1-1. Two 50-finger edge connectors connect the interface to the backplane, and one 48-finger edge connector connects the interface, via a cable, to its peripheral device (terminal). The cable is not furnished with the interface. See paragraph 1-8 for a list of available cable options.

## NOTE

In this manual, the word "terminal" refers to a cathode ray tube or other type of terminal, or a teleprinter.

### 1-5. IDENTIFICATION

**1-6. PRODUCT.** Five digits and a letter (12005A in this case) are used to identify Hewlett-Packard products used with HP computers. The five digits identify the product; the letter indicates the revision level of the product.

1-7. CIRCUIT CARD. The interface circuit card is further identified by a part number marked on the card. In addition, a letter and a date code consisting of four digits (e.g., A-1926) are placed below the part number. The letter identifies the version of the etched circuit on the card. The date code (the four digits following the letter) identifies the electrical characteristics of the card with components mounted. Thus, the complete part number on the interface card could be as follows:

12005-60001 A-1926

If the date code stamped on the interface does not agree with the date code on the title page of this manual, there are differences between your interface and the interface described herein. These differences are described in manual supplements available at the nearest Hewlett-Packard Sales and Service Office (a list of Hewlett-Packard Sales and Service Offices is contained at the back of this manual).

1-8. OPTIONS. Three cable options are available for the HP 12005A Asynchronous Serial Interface, as follows:

- Option 001: Cable 12005-60002, used for HP 2621 terminals.

- Option 002: Cable 12005-60003, used for RS-232 terminals connected directly to the interface.

- Option 003: Cable 12005-60004, used for RS-232 terminals connected to the interface through a modem.

**1-9. REFERENCE MANUAL.** The manual supplied with the interface is identified by its name and part number. The part number, 12005-90001, is printed on the title page. The publication date also is printed on the title page. If the manual is revised, the publication date is changed.

7700-480

٠

i.

. •

# 1-10. SPECIFICATIONS

Table 1-1 lists the specifications of the HP 12005A Asynchronous Serial Interface. In the table and throughout this manual the word "character" signifies a 7-bit ASCII (American Standard Code for Information Interchange) character with start and stop bits and an optional parity bit; or an 8-bit binary character with start and stop bits. Thus, a character as handled by the interface can consist of from 9 to 11 bits. In the case of data sent to a terminal, each character results in the display of a letter of the alphabet, a digit, or a symbol; or the character causes actuation of such mechanical functions as carriage return or bell stroke. When a character is sent to the cartridge tape unit of a terminal, the eight data bits are written on the tape.

When data is received from a terminal keyboard, a character is supplied to the interface each time a key is pressed. If a character is furnished by a cartridge tape unit of a terminal, eight data bits are supplied to the interface.

| OUTPUT CHARACTERS           | In an output operation, 7-bit (ASCII) or 8-bit (binary) characters are transferred in parallel from the central processor to the interface. There, one start bit and one or two stop bits, and an optional parity bit, are added, and the resulting bits are transferred in serial to a terminal.                           |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUT CHARACTERS            | In an input operation, 9-bit to 11-bit characters are transferred serially from the terminal to the interface. There, a start bit, optional parity bit, and one or two stop bits are discarded. The resulting 8-bit character is transferred in parallel to the central processor A or B register, or directly into memory. |

| DATA TRANSFER RATE:         |                                                                                                                                                                                                                                                                                                                             |

| Using Internal Clock Pulse: | Data transfer rate is 50, 75, 110, 134.5, 150, 300, 600, 900, 1200, 1800, 2400, 3600, 4800, 7200, or 9600 baud, depending on the settings of switches U21 S1 through U21 S4.                                                                                                                                                |

| Using External Clock Pulse: | Depends on the terminal. Maximum is 56,000 baud.                                                                                                                                                                                                                                                                            |

| PHYSICAL CHARACTERISTICS    |                                                                                                                                                                                                                                                                                                                             |

| Size:                       | 17.15 by 28.91 centimeters<br>(6.75 by 11.38 inches)                                                                                                                                                                                                                                                                        |

| Backplane Interconnects:    | Two 50-finger edge connectors which plug into two sockets (P1 and P2) mounted on the backplane.                                                                                                                                                                                                                             |

| Device Interconnects:       | One 48-finger edge connector on which a cable hood (J1) may be connected.                                                                                                                                                                                                                                                   |

| POWER REQUIREMENTS:         |                                                                                                                                                                                                                                                                                                                             |

| Voltage Current             | Power Dissipation                                                                                                                                                                                                                                                                                                           |

8.3W

1.8W

1.4W

11.5W

Table 1-1. Specifications

+5

+12

-12

0 to 55 °C

1.6A

143mA

107.5mA

Total Power Dissipation

**OPERATING TEMPERATURE RANGE**

SECTION

# INSTALLATION

## 2-1. INTRODUCTION

This section provides information on unpacking, inspecting, installing, and checking the operation of the HP 12005A Asynchronous Serial Interface.

# CAUTION

STATIC SENSITIVE DEVICE. Use anti-static procedures when handling the interface.

# 2-2. UNPACKING AND INSPECTION

If ordered with a computer, the interface is installed at the factory. When this is the case, it is necessary only to check the operation of the terminal and the interface after the computer and the terminal are installed. Checkout instructions are furnished in paragraph 2-19. If the interface is ordered separately, inspect the carton containing the interface before opening it. If there is evidence of damage, if water stains are visible, or if the box rattles, request that the carrier's agent be present when the box is opened.

Inspect the interface for such damage as cracks, dents, broken components, detached parts, corrosion, water damage, etc. If any part is damaged, retain the carton, packing material, and shipping papers, and immediately notify the carrier and the nearest Hewlett-Packard Sales and Service Office. The Sales and Service Office will arrange for repair or replacement of damaged parts without waiting for settlement of claims against the carrier. (HP Sales and Service Offices are listed at the back of this manual.)

After inspecting all components, check the part numbers listed in paragraph 1-5 against the part number on the interface. If an incorrect component has been furnished, notify the nearest Hewlett-Packard Sales and Service Office.

## 2-3. PREPARATION FOR INSTALLATION

### 2-4. COMPUTATION OF CURRENT REQUIREMENTS

The interface obtains its operating voltages from the computer power supply through the backplane. Before installing the interface, it is necessary to determine whether the added current will overload the power supply. (If the interface was installed at the factory, the required calculations have been made, and it has been determined that an overload will not occur.) The current requirements of the interface are listed in Section I, table 1-1.

# 2-5. INTERFACE REQUIREMENTS

#### 2-6. BACKPLANE TO HP 12005A ASYN-CHRONOUS SERIAL INTERFACE

All interface between the HP 12005A Asynchronous Serial Interface, central processor, and main memory occur on the backplane. Connections from the backplane to the 12005A are listed in table 2-1 (connector P1) and table 2-2 (connector P2).

#### 2-7. HP 12005A ASYNCHRONOUS SERIAL INTERFACE TO TERMINAL

Several options are offered for the serial communication between the 12005A and the terminal or modem to which it is connected. The 20 mA current loop driver and receiver provide a minimal teleprinter interface. The RS-449 drivers and receivers provide an interface to most Electronics Industries Association (EIA) standard devices. The 12005A may be connected directly to a terminal, or it can be connected through a Bell 103, 202, or similar modem.

#### 2-8. RS-449 INTERFACE

The EIA has defined a number of standards for interfaces between data communications and data terminals equipment. Currently, RS-232 is the most widely used of these standards. Standards RS-422 and RS-423 have been developed to offer enhanced operation of serial data communications. These new standards allow faster baud rates over longer cables. The basic difference between RS-422 and RS-423 is that RS-422 drivers and receivers are balanced, or differential, so that they offer the highest noise immunity, the highest data signalling rates, and the highest permissible cable lengths. RS-423 drivers and receivers, on the other hand, are single-ended, so that they offer better downward compatibility to RS-232 equipment.

RS-449 is a new standard which is basically a mix of RS-422 and RS-423 specifications. For interchange circuits where higher data signalling rates are used, such as the timing and data circuits and control circuits, RS-449

| P1-                                                                                                                                                                                                                                       | SIGNAL<br>NAME                                                                                                                                              | SIGNAL DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15                                                                                                                                                             | ICHID-<br>ICHOD-<br>MCHID-<br>MCHOD-<br>MLOST-<br>MCHODOC-<br>PFW-<br>SPARE 1<br>SC0<br>SC1<br>SC2<br>SC3<br>GND<br>GND<br>SPARE 2                          | Interrupt Chain In Disable<br>Interrupt Chain Out Disable<br>Memory Chain In Disable<br>Memory Chain Out Disable<br>Memory Lost<br>Memory Chain Out Disable Open Collector<br>Power Fail Warning<br>Address Extension Bus Bit 0<br>Address Extension Bus Bit 1<br>Address Extension Bus Bit 2<br>Address Extension Bus Bit 3                                                                                                                                                                                                                                   |

| 16         17         18         19         20         21         22         23         24         25         26         27         28         29         30         31         32         33         34         35         36         37 | GND<br>SC4<br>SC5<br>AB0<br>AB1<br>AB2<br>AB3<br>AB4<br>AB5<br>AB6<br>AB7<br>AB8<br>AB9<br>AB10<br>AB11<br>AB12<br>AB13<br>AB14<br>WE-<br>DB0<br>DB1<br>DB2 | Address Extension Bus Bit 4<br>Self Configure<br>Address Bus Bit 0<br>Address Bus Bit 1<br>Address Bus Bit 1<br>Address Bus Bit 2<br>Address Bus Bit 2<br>Address Bus Bit 4<br>Address Bus Bit 5<br>Address Bus Bit 5<br>Address Bus Bit 6<br>Address Bus Bit 7<br>Address Bus Bit 7<br>Address Bus Bit 8<br>Address Bus Bit 9<br>Address Bus Bit 10<br>Address Bus Bit 10<br>Address Bus Bit 11<br>Address Bus Bit 12<br>Address Bus Bit 12<br>Address Bus Bit 13<br>Address Bus Bit 14<br>Write Enable<br>Data Bus Bit 0<br>Data Bus Bit 1<br>Data Bus Bit 2 |

| 37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50                                                                                                                                                          | DB2<br>DB3<br>DB4<br>DB5<br>DB6<br>DB7<br>DB8<br>DB9<br>DB10<br>DB11<br>DB12<br>DB13<br>DB14<br>DB15                                                        | Data Bus Bit 2<br>Data Bus Bit 3<br>Data Bus Bit 4<br>Data Bus Bit 5<br>Data Bus Bit 6<br>Data Bus Bit 7<br>Data Bus Bit 8<br>Data Bus Bit 9<br>Data Bus Bit 10<br>Data Bus Bit 11<br>Data Bus Bit 12<br>Data Bus Bit 13<br>Data Bus Bit 14<br>Data Bus Bit 15                                                                                                                                                                                                                                                                                                 |

.

.

| P2-      | SIGNAL<br>NAME      | SIGNAL DEFINITION                                 |     |

|----------|---------------------|---------------------------------------------------|-----|

| 1<br>2   | CPUTURN-<br>GND     | Processor Turn                                    |     |

| 3        | REMEM-              | Remote Memory                                     |     |

| 4        | VALID-              | Data Valid                                        |     |

| 5        | IORQ-               | I/O Handshake Request                             |     |

| 6        | INTRQ-              | Interrupt Request                                 |     |

| 7        | MP                  | Memory Protect                                    |     |

| 8        | RNI-                | Read Next Instruction                             |     |

| 9        | MEMGO-              | Memory Cycle Initiation                           |     |

| 10       | PE-<br>SCHID-       | Parity Error<br>Slave Chain In Disable            |     |

| 11<br>12 | SCHOD-              | Slave Chain in Disable<br>Slave Chain Out Disable | ļ , |

| 13       | IAK-                | Interrupt Acknowledge                             |     |

| 14       | IOGO-               | I/O Handshake Request Acknowledge                 |     |

| 15       | GND                 |                                                   |     |

| 16<br>17 | SLAVE-<br>GND       | Slave Request                                     |     |

| 18       | MRQ-                | Memory Request                                    |     |

| 19<br>20 | GND<br>FCLK-        | Fast Clock                                        |     |

| 21       | GND                 |                                                   |     |

| 22       | CCLK-<br>PINT-      | Communications Clock                              |     |

| 23<br>24 | SCLK-               | Priority Interrupt<br>System Clock                |     |

| 25       | CRS-                | Control Reset                                     |     |

| 26       | PON                 | Power On                                          |     |

| 27       | GND                 |                                                   |     |

| 28       | BUSY-               | Memory Busy                                       |     |

| 29       | GND                 |                                                   |     |

| 30       | GND                 |                                                   |     |

| 31       | GND                 |                                                   |     |

| 32       | GND                 |                                                   |     |

| 33<br>34 | GND<br>GND          |                                                   |     |

| 34       | +5V                 |                                                   |     |

| 36       | +5V                 |                                                   |     |

| 37       | +5V                 |                                                   |     |

| 38       | +5V                 |                                                   |     |

| 39       | +12 <b>M</b>        |                                                   |     |

| 40       | -12M                |                                                   |     |

| 41       | +12V                |                                                   |     |

| 42       | +12V                |                                                   |     |

| 43<br>44 | -12V                |                                                   |     |

| 44       | −12V<br>+5 <b>M</b> |                                                   |     |

| 46       | +5M                 |                                                   |     |

| 47       | ACØ2                |                                                   |     |

| 48       | ACØ2                |                                                   |     |

| 49       | ACØ1                |                                                   |     |

| 50       | AC#1                |                                                   |     |

|          |                     |                                                   |     |

|          |                     |                                                   |     |

|          |                     |                                                   |     |

|          |                     |                                                   |     |

|          |                     |                                                   |     |

|          |                     |                                                   |     |

|          |                     |                                                   |     |

|          |                     |                                                   |     |

|          |                     |                                                   |     |

|          |                     |                                                   |     |

|          | 1                   |                                                   | 1   |

recommends that the balanced drivers be used. For the remaining circuits, unbalanced equipment may be used. Table 2-3 lists EIA standards for RS-232, RS-422, RS-423, and RS-449.

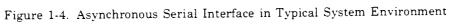

An RS-449 interface is implemented on the 12005A using the scheme shown in table 2-4. Only differential receivers are used. Both differential and single-ended drivers are used, however, and some are driven in parallel. When connecting to single-ended drivers, one of the receiver inputs is grounded. This implementation of RS-449 offers complete compatibility with RS-232 and offers many of the enhancements of RS-422 and RS-423 interfaces.

#### NOTE

Although the lines shown in table 2-4 are named according to the RS-449 standards, this does not restrict their usage to this specification. All lines are software controllable and may be assigned arbitrary meanings according to the needs of a specific application.

The four output lines and six input lines shown in table 2-4 are a subset of RS-449 and are sufficient for most all asynchronous modem and terminal applications. Those

| Table 2-3. | Electronics | Industries | Association | Standards |

|------------|-------------|------------|-------------|-----------|

|------------|-------------|------------|-------------|-----------|

| TYPE DRIVER/         | RS-232C                | R\$-422                                                                          | R\$-423                                                                         | RS-449                                |  |

|----------------------|------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------|--|

| RECEIVER             | SINGLE-ENDED           | DIFFERENTIAL                                                                     | SINGLE-ENDED                                                                    | вотн                                  |  |

| Maximum Cable Length | 15.24 meters (50 feet) | 12.19 meters (40 feet)<br>@ 10M baud.<br>1219 meters (4000 feet)<br>@ 100K baud. | 12.19 meters (40 feet)<br>@ 100K baud.<br>1219 meters (4000 feet)<br>@ 1K baud. | 60.96 meters (200 feet)<br>@ 2M baud. |  |

| Maximum Data Rate    | 20K baud               | 10M baud @<br>12.19 meters (40 feet)                                             | 100K baud @<br>12.19 meters (40 feet)                                           | 2M baud                               |  |

| Table 2 | 2-4. | RS-449/RS-232 | Equivalence | ;y |

|---------|------|---------------|-------------|----|

|---------|------|---------------|-------------|----|

| DIRECTION<br>WITH RESPECT<br>TO HP 12005A | NAME                                  | RS-449                                                                                             | NAME                             | RS-232C                                                                                                                         |

|-------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                           | SG<br>SC<br>RC                        | Signal Ground<br>Send Common<br>Receive Common                                                     | AA<br>AB                         | Protective Ground<br>Signal Ground                                                                                              |

| OUT<br>IN<br>IN<br>OUT<br>IN<br>IN        | RS*<br>CS*<br>DM*<br>TR<br>IC*<br>RR* | Request to Send<br>Clear to Send<br>Data Mode<br>Terminal Ready<br>Incoming Call<br>Receiver Ready | CA<br>CB<br>CC<br>CD<br>CE<br>CF | Request to Send<br>Clear to Send<br>Data Set Ready<br>Data Terminal Ready<br>Ring Indicator<br>Received Line Signal<br>Detector |

| OUT<br>IN                                 | SD*<br>RD*                            | Send Data<br>Receive Data                                                                          | BA<br>BB                         | Transmitted Data<br>Received Data                                                                                               |

| OUT                                       | SSD                                   | Secondary Send Data                                                                                | SBA                              | Secondary<br>Transmitted Data                                                                                                   |

| IN                                        | SRD*                                  | Secondary Receive Data                                                                             | SBB                              | Secondary<br>Received Data                                                                                                      |

\* Indicates differential driver or receiver used on this signal.

. .

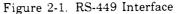

lines containing an asterisk in table 2-4 indicate a circuit which optionally uses RS-422 or balanced electrical characteristics. See figure 2-1 for an illustration of how this option is implemented. When the interface is cabled directly to a terminal, most of the control lines listed in table 2-4 will not be used. When the interface is connected to a modem, however, the output control lines will be software programmed and the input lines can be continuously monitored for status change.

## 2-9. TELEPRINTER INTERFACE

The HP 12005A Asynchronous Serial Interface has a 20 mA current loop interface which is designed to run at 110 baud.

A 20 mA current loop driver is used when interfacing to a teleprinter, and left open otherwise. A 20 mA current loop receiver is used to receive data from a teleprinter, and when left open is pulled down to a logic zero.

## 2-10. CONNECTOR J1 PIN CONNECTIONS

See table 2-5 for pin connections to connector J1. Connector J1 is used to connect a cable from the interface to a terminal or modem.

The seven signals which are brought out to the connector for diagnostic purposes only are marked as such. These signals are used with the diagnostic test hood (see the HP 12005A Asynchronous Serial Interface Diagnostic Operating Manual, part no. 24397-90005) to set baud rates and for testing the 12005A.

# 2-11. HARDWIRED OPTIONS

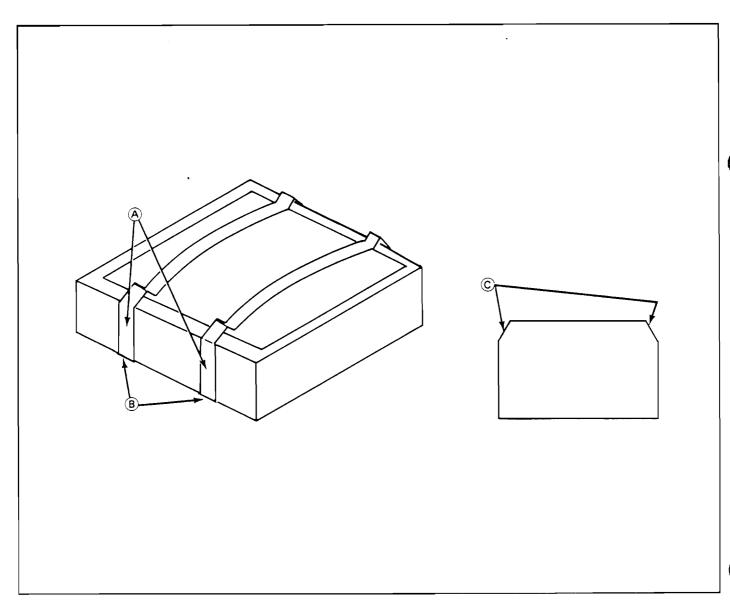

The only hardwired option on the 12005A is the wiring of the RS-449 receivers for balanced or unbalanced signals. All HP 12005A cable options are wired for unbalanced signals; therefore, one input to the differential receiver is grounded in the cable hood. In order to interface to a balanced driver (RS-422 specification), refer to the connections shown in table 2-4. The cable hood may be disassembled as shown in figure 2-2. Check the wiring of all the receivers and remove or add jumpers to ground as necessary.

# 2-12. SWITCH SELECTABLE OPTIONS

The switch selectable options are the select code (6 bits), the baud rate (4 bits), parity sense (1 bit), number of stop bits (1 bit), and Virtual Control Panel (VCP) interface enable (1 bit). The switches are mounted in two dual inline packages (U1 and U21) located close to the cable connector on the interface (see figure 1-1 for the locations of the switches). Each set of switches, U1 and U21, are numbered from S1 to S8. Each switch is closed when in the down position, and is open in the up position.

| Table 2-5. | Interface-to-Terminal (Connector e | J1) |

|------------|------------------------------------|-----|

|            | Pin Connections                    |     |

| J1-         | SIGNAL<br>NAME       | SIGNAL DEFINITION                                             |

|-------------|----------------------|---------------------------------------------------------------|

| A<br>1<br>B | GND<br>GND<br>IC (A) | Incoming Call (A)                                             |

| 2           | RS (B)               | Request to Send (B)                                           |

| С<br>З      | RIC<br>BS (A)        | Used by diagnostics only                                      |

| D           | RS (A)               | Request to Send (A)<br>Teleprinter Input                      |

| 4           | TTYI                 | Teleprinter Input                                             |

| E           | RS (U)               | Request to Send (U)                                           |

| 5           | DRST                 | Reset line used by diagnostics only                           |

| F<br>6      | IC (B)               | Incoming Call (B)                                             |

| н           | RDM<br>RCS           | Used by diagnostics only<br>Used by diagnostics only          |

| 7           | EXTCLK               | Clock from External Device (if any) (16X)                     |

| Ĵ           | +5V                  | +5 to terminal                                                |

| 8           | ECHOM                | Used by diagnostics only                                      |

| К<br>9      | SC2                  | Used by Diagnostics only                                      |

| y<br>L      | SD (B)<br>RRR        | Send Data (B)<br>Used by diagnostics only                     |

| 10          | SD (A)               | Send Data (A)                                                 |

| М           | TR                   | Terminal Ready                                                |

| 11          | SBS                  | Stop Bit Select                                               |

| N           | TTY+12               | +12 to teleprinter                                            |

| 12<br>P     | TTY+12<br>RDR CNTL   | +12 to teleprinter                                            |

| 13          | RDRCNTL              | Reader Control (Gnd)<br>Reader Control (Gnd)                  |

| R           | TTY-12               | -12 to teleprinter                                            |

| 14          | TTY-12               | -12 to teleprinter                                            |

| S           | RD (B)               | Receive Data (B)                                              |

| 15          | SRD (A)              | Secondary Receive Data (A)                                    |

| Т<br>16     | ΤΤΥΟ<br>ΤΤΥΟ         | Output to teleprinter<br>Output to teleprinter                |

| U           | RD (A)               | Receive Data (A)                                              |

| 17          | SRD (B)              | Secondary Receive Data (B)                                    |

| V           | RR (A)               | Receiver Ready (A)                                            |

| 18          | RR (B)               | Receiver Ready (B)                                            |

| W<br>19     | SD (U)<br>MSB-       | Send Data (U)<br>Most significant bit of baud rate select     |

| X           | CS (A)               | Most significant bit of baud rate select<br>Clear to Send (A) |

| 20          | NMSB-                | Next to most significant bit of baud rate select              |

| Y           | CS (B)               | Clear to Send (B)                                             |

| 21          | NLSB+                | Next to least significant bit of baud rate select             |

| z           | DM (A)               | Data Mode (A)                                                 |

| 22          | LSB+                 | Least significant bit of baud rate select                     |

| AA<br>23    | DM (B)               | Data Mode (B)                                                 |

| BB          | SSD<br>GND           | Secondary Send Data                                           |

| 24          | GND                  |                                                               |

|             |                      |                                                               |

#### 2-13. VIRTUAL CONTROL PANEL (VCP) INTERFACE SELECTION

Switch U1 S1 is used to select the 12005A to operate as an interface to a terminal which is functioning as a Virtual Control Panel (VCP). Note that the select code of the

2-5

12005A must be set to 20 (octal) when it is to function as the Virtual Control Panel interface.

- U1 S1 closed (down): The 12005A has been selected to operate as interface to the Virtual Control Panel. A BREAK character will cause the 12005A to enter this mode.

- U1 S1 open (up): The 12005A will not operate as a VCP interface. A BREAK character will cause a flag (Flag 30) to set.

#### NOTE

Switch U1 S2 is not used.

#### 2-14. SELECT CODE SELECTION

Switches U1 S3 through U1 S8 determine the select code for the interface. Note that the select code of the 12005A must be set to 20 (octal) when it is to function as the Virtual Control Panel interface. Switch S3 selects the most significant bit and S8 selects the least significant bit of the six-bit select code.

Open (up) switch: Logic one.

Closed (down) switch: Logic zero.

### 2-15. BAUD RATE SELECTION

The baud rate for the 12005A can be set from 50 to 9600 baud using switches U21 S1 through U21 S4. An open (up) switch produces a logic 1, a closed (down) switch produces a logic zero. Table 2-6 shows the switch settings for the various baud rates.

#### 2-16. STOP BIT SELECTION

Switch U21 S5 selects either one or two stop bits.

U21 S5 open: Two stop bits.

U21 S5 closed: One stop bit.

#### 2-17. PARITY SENSE SELECTION

Switch U21 S6 selects even or odd parity.

U21 S6 open: Even parity.

U21 S6 closed: Odd parity.

NOTE

Switches U21 S7 and S8 are not used.

| Table 2 | 2-6. | Baud | Rate | Selection |

|---------|------|------|------|-----------|

|---------|------|------|------|-----------|

| S1 | S2 | S3 | S4 | BAUD RATE            |  |  |  |

|----|----|----|----|----------------------|--|--|--|

| 0  | 0  | 0  | 0  | External Clock (x16) |  |  |  |

| 0  | 0  | 0  | 1  | 50                   |  |  |  |

| 1  | 0  | 0  | 0  | 75                   |  |  |  |

| 1  | 0  | 0  | 1  | 110                  |  |  |  |

| 0  | 1  | 0  | 0  | 134.5                |  |  |  |

| 0  | 1  | 0  | 1  | 150                  |  |  |  |

| 1  | 1  | 0  | 0  | 300                  |  |  |  |

| 1  | 1  | 0  | 1  | 600                  |  |  |  |

| 0  | 0  | 1  | 0  | 900                  |  |  |  |

| 0  | 0  | 1  | 1  | 1200                 |  |  |  |

| 1  | 0  | 1  | 0  | 1800                 |  |  |  |

| 1  | 0  | 1  | 1  | 2400                 |  |  |  |

| 0  | 1  | 1  | 0  | 3600                 |  |  |  |

| 0  | 1  | 1  | 1  | 4800                 |  |  |  |

| 1  | 1  | 1  | 0  | 7200                 |  |  |  |

| 1  | 1  | 1  | 1  | 9600                 |  |  |  |

A closed (down) switch produces a logic 0.

# 2-18. INSTALLATION

After insuring that the computer power supply can handle the added load, perform the following:

- a. Select the baud rate by setting switches U21 S1 through U21 S4 as shown in table 2-6.

- b. Set switch U1 S1 open or closed depending on whether the 12005A has been selected to operate as interface to a Virtual Control Panel. (See paragraph 2-13.)

- c. Set switch U21 S6 open or closed to determine even or odd parity (open equals even parity, closed equals odd parity. See paragraph 2-17.).

- d. Set the select code for the interface with switches U1 S3 through U1 S8 (see paragraph 2-14).

- e. Install the computer system and the I/O device to be connected to the interface (if these have not already been installed).

- f. Turn off power at the computer and the I/O device. Install the interface in the desired I/O slot in the computer card cage. Note that the interrupting and DMA priority of an I/O interface card depends on its location in the card cage. The card slots are numbered from XA1 (highest priority), in sequence down to the

lowest priority slot, XA10 or XA16, depending on the size of the backplane.

Components on the card must be on the same side of the card as for other cards in the I/O slots. When installing the card, use care not to damage components or traces on the card or on adjacent cards. Press the card firmly into place.

g. Connect the appropriate cable from the terminal (or a modem if one is to be used) to the 12005A interface.

# 2-19. CHECKOUT

To verify operation of the interface, perform the diagnostic test for the interface. Operating procedures for the diagnostic tests are described in the HP 12005A Asynchronous Serial Interface Diagnostic Operating Manual, part no. 24397-90005.

### 2-20. RESHIPMENT

If the interface is to be shipped to Hewlett-Packard for repair, attach a tag identifying the owner and indicating the service to be performed. Include the part number of the interface.

Pack the interface in the original factory packing material. If the original material is not available, good commercial packing material should be used. Reliable commercial packing and shipping companies have the facilities and materials to adequately repack the item.

7700-462

Figure 2-2. Cable Hood Jumper Instructions

(estera)

•

.

.

.

SECTION

PROGRAMMING

111

## 3-1. INTRODUCTION

This section provides assembly-language programming procedures for the HP 12005A Asynchronous Serial Interface and its associated terminal. For information on assembly-language programming, refer to the HP 1000 L-Series Reference Manual, part no. 02103-90007.

Although it has many capabilities such as byte packing, handling its own Direct Memory Access (DMA), decoding its own instructions from the central processor unit (CPU), and handling variable-length records, the 12005A offers the advantage of simplicity, from a software standpoint, in that it can be driven using only one control word.

# 3-2. USE OF THE GLOBAL REGISTER

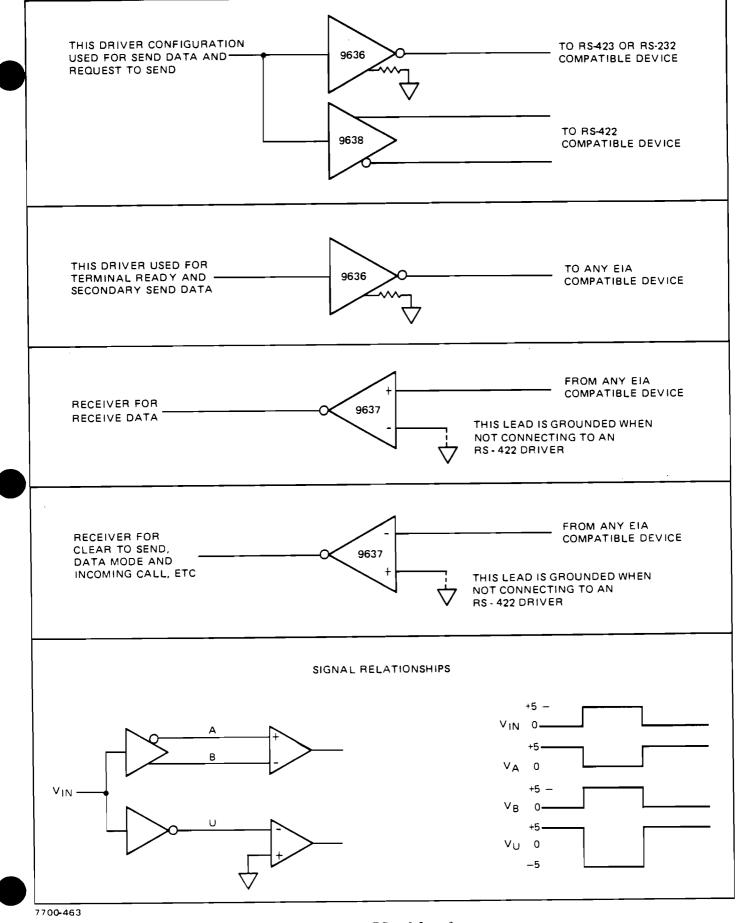

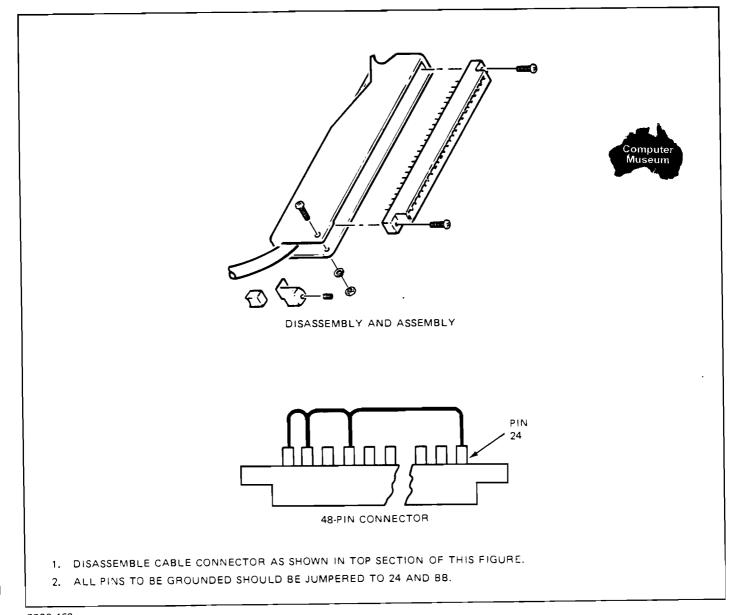

Every I/O interface card (serial interface, parallel interface, etc.) in the HP 1000 L-Series Computer System contains a global register. The global register is located in the IOP chip and is a six-bit register which contains a select code. See figure 3-1 for a block diagram of the IOP chip.

All global registers on all interface cards are controlled by the CPU, thus all global registers contain the same select code. (It is useful, therefore, to think of all the global registers as being one "global" register.) The global register may be loaded with an OTA 2 or OTB 2 instruction, enabled with a CLF 2 instruction and disabled with an STF 2 instruction. When the global register is enabled, any instruction which is executed by the CPU automatically applies to the card whose select code is in the global register. For example, if the global register is enabled and contains the 12005A's select code, the current I/O instruction is decoded and executed by the interface. Using the global register to store select code frees the six least significant bits of LO instructions (these bits do not need to store the select code of the I/O device which is to receive the I(O instruction). Thus, these six bits can be used to address a register on I O interface cards. On the asynchronous serial interface, there are three such registers: one for data, one for control, and one for status, in addition to registers which are internal to the IOP chip.

Data may be transferred to and from the asynchronous serial interface with or without the global register being enabled. In order to access the interface's control and status registers, however, the global register must be used.

# 3-3. I/O INSTRUCTION SET

The I/O master executes twelve I/O instructions as follows:

| CLC | Clear Control      |

|-----|--------------------|

| CLF | Clear Flag         |

| LIA | Load Into A        |

| LIB | Load Into B        |

| MIA | Merge Into A       |

| MIB | Merge Into B       |

| OTA | Output A           |

| OTB | Output B           |

| SFC | Skip if Flag Clear |

| SFS | Skip if Flag Set   |

| STF | Set Flag           |

| STC | Set Control        |

The six-bit global register allows a maximum of 64 (decimal) select codes. The I/O master, however, executes only a portion of this maximum. Select codes 00 through 17 (octal) are reserved for the central processor, leaving 20 through 77 (octal) available for the I/O system.

## 3-4. INSTRUCTION USAGE SUMMARY

Table 3-1 lists all the instructions recognized by the IOP chip by their select code. There are three conditions relevant to the instruction execution. These conditions are as follows:

- a. Is the global register (GR) enabled?

- b. Do the contents of the GR equal the IOP chip's select code, (GR = SC)?

- c. Do the lower six bits of the instruction register equal the IOP chip's select code, (IR = SC)?

The summary indicates which conditions must be met for instruction execution by listing Y for yes. N for no. and X for don't care in each column.

κ.

7700-464

Figure 3-1. I'O Chip Block Diagram

| INSTRUCTION  | FUNCTION                                              | GR ON | GR <i>=</i> SC | IR =SC | NOTE |

|--------------|-------------------------------------------------------|-------|----------------|--------|------|

| LI + 0       | Read interrupt mask                                   | x     | Y              | x      |      |

| MI+ 0        | Merge interrupt mask                                  | X     | Ý              | x      |      |

| <b>DT+ 0</b> | Write interrupt mask                                  | x     | ×              | x x    |      |

| CLF 2        | Enable GR                                             | Â     | x              | Â      |      |

| STF 2        | Disable GR                                            | Â     | x              | Â      |      |

| LI + 2 [,C]  | Read GR                                               | Â     | Ŷ              | x x    | 1    |

| MI + 2 [,C]  | Merge GR                                              | Â     | Ý              |        | 1, 9 |

| DT+ 2 [,C]   | Write GR                                              | Â     | X              | X      | 1, 9 |

|              |                                                       |       |                | X      |      |

| •            | Enable Slave logic                                    | X     | X              | X      | 1, 2 |