# HP 1000 A400 Computer

**Reference Manual**

#### FEDERAL COMMUNICATIONS COMMISSION RADIO FREQUENCY INTERFERENCE INFORMATION

This equipment complies with the requirements in Part 15 of FCC Rules for a Class A computing device. Operation of this equipment in a residential area may cause unacceptable interference to radio and TV reception requiring the operator to take whatever steps are necessary to correct the interference.

WARNING: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

> Data Systems Division 1266 Kifer Road Sunnyvale, CA 94086-5304

Manual Part No. 02424-90001 E1287 Printed in U.S.A. December, 1987

# HP Computer Museum www.hpmuseum.net

For research and education purposes only.

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THE MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Hewlett-Packard Company.

Copyright © 1986, 1987 by HEWLETT-PACKARD COMPANY

# **Printing History**

The Printing History below identifies the edition of this manual and any updates that are included. Periodically, update packages are distributed which contain replacement pages to be merged into the manual, including an updated copy of this printing history page. Also, the update may contain write-in instructions.

Each reprinting of this manual will incorporate all past updates; however, no new information will be added. Thus, the reprinted copy will be identical in content to prior printings of the same edition with its user-inserted update information. New editions of this manual will contain new information, as well as all updates.

To determine what manual edition and update is compatible with your current software revision code, refer to the Manual Numbering File or the Computer User's Documentation Index. (The Manual Numbering File is included with your software. It consists of an "M" followed by a five digit product number.)

| First Edition  | Dec 1986   | 5 |

|----------------|------------|---|

| Update 1       | . Mar 1987 | 7 |

| Second Edition | . Dec 1987 | 7 |

• • • · , • ٠ .

# Table of Contents

Computer Museum

#### Chapter 1 Introduction

| General1-1Features1-1Single-Board Computer Description1-1Architecture1-4Floating Point Processing1-4Virtual Control Panel1-5Bootstrap Loaders1-5Self-Test Routines1-5Time Base Generator1-7Power Supply1-7Input/Output (I/O)1-7On-Board I/O (OBIO)1-7Support of A-Series I/O Cards1-8 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-Board Computer Description1-1Architecture1-4Floating Point Processing1-4Virtual Control Panel1-5Bootstrap Loaders1-5Self-Test Routines1-5Time Base Generator1-7Power Supply1-7Input/Output (I/O)1-7On-Board I/O (OBIO)1-7                                                      |

| Architecture1-4Floating Point Processing1-4Virtual Control Panel1-5Bootstrap Loaders1-5Self-Test Routines1-5Time Base Generator1-7Power Supply1-7Input/Output (I/O)1-7On-Board I/O (OBIO)1-7                                                                                          |

| Floating Point Processing1-4Virtual Control Panel1-5Bootstrap Loaders1-5Self-Test Routines1-5Time Base Generator1-7Power Supply1-7Input/Output (I/O)1-7On-Board I/O (OBIO)1-7                                                                                                         |

| Floating Point Processing1-4Virtual Control Panel1-5Bootstrap Loaders1-5Self-Test Routines1-5Time Base Generator1-7Power Supply1-7Input/Output (I/O)1-7On-Board I/O (OBIO)1-7                                                                                                         |

| Virtual Control Panel       1-5         Bootstrap Loaders       1-5         Self-Test Routines       1-5         Time Base Generator       1-7         Power Supply       1-7         Input/Output (I/O)       1-7         On-Board I/O (OBIO)       1-7                              |

| Bootstrap Loaders       1-5         Self-Test Routines       1-5         Time Base Generator       1-7         Power Supply       1-7         Input/Output (I/O)       1-7         On-Board I/O (OBIO)       1-7                                                                      |

| Self-Test Routines       1-5         Time Base Generator       1-7         Power Supply       1-7         Input/Output (I/O)       1-7         On-Board I/O (OBIO)       1-7                                                                                                          |

| Time Base Generator         1-7           Power Supply         1-7           Input/Output (I/O)         1-7           On-Board I/O (OBIO)         1-7                                                                                                                                 |

| Power Supply         1-7           Input/Output (I/O)         1-7           On-Board I/O (OBIO)         1-7                                                                                                                                                                           |

| Input/Output (I/O)                                                                                                                                                                                                                                                                    |

| On-Board I/O (OBIO) 1-7                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                       |

| Support of A-series I/O Calus                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                       |

| Memory                                                                                                                                                                                                                                                                                |

| Memory Controller 1-9                                                                                                                                                                                                                                                                 |

| Memory Access                                                                                                                                                                                                                                                                         |

| Memory Expansion                                                                                                                                                                                                                                                                      |

| Software                                                                                                                                                                                                                                                                              |

| HP Interface Bus (HP-IB)                                                                                                                                                                                                                                                              |

| Computer Network                                                                                                                                                                                                                                                                      |

| Expansion and Enhancement 1-12                                                                                                                                                                                                                                                        |

| Specifications                                                                                                                                                                                                                                                                        |

### Chapter 2 Operating Features

| Hardware Registers           | . 1 |

|------------------------------|-----|

| A-Register                   |     |

| B-Register                   |     |

|                              |     |

| P-Register                   |     |

| Extend (E) Register 2-       |     |

| Overflow (O) Register 2-     |     |

| Central Interrupt Register   | .2  |

| Violation Register           | -2  |

| Parity Error Register        | •2  |

| Interrupt System Register 2- | .2  |

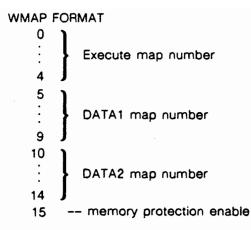

| WMAP-Register                | ·2  |

| Virtual Registers            |     |

| M-Register                   |     |

| T-Register                   |     |

| Self-Test                    | .3  |

| VCP Pre-Test                 | -4  |

| User Interface and Control   |     |

| Bootstrap Loaders            | .9  |

| Loader Selection for Auto-Boot              |

|---------------------------------------------|

| VCP Re-Entry for Extended Boot Loading 2-10 |

| Device Parameters and Media Formats 2-11    |

| Virtual Control Panel (VCP) 2-11            |

| VCP Program Operation                       |

| Extended Memory Test (%M) 2-16              |

| Address Test                                |

| Pattern Test for Stuck Bits 2-17            |

| Parity Error Set Routine (%S) 2-18          |

| Loader Commands 2-19                        |

| VCP User Considerations 2-22                |

### Chapter 3 Programming Information

| D                                                   |

|-----------------------------------------------------|

| Data Formats                                        |

| Addressing                                          |

| Paging 3-2                                          |

| Direct and Indirect Addressing 3-5                  |

| Memory Mapping                                      |

| Virtual Memory Area 3-5                             |

| Code and Data Separation 3-5                        |

| Base-Relative Addressing 3-6                        |

| Reserved Memory Locations                           |

| Nonexistent Memory                                  |

| Base Set Instruction Formats                        |

| Memory Reference Instructions                       |

| Register Reference Instructions                     |

| Input/Output Instructions                           |

| Extended Arithmetic Memory Reference Instructions   |

| Extended Arithmetic Register Reference Instructions |

| Extended Instructions                               |

| Floating Point Instructions                         |

| Double Integer Instructions                         |

|                                                     |

| Language Instruction Set                            |

| Virtual Memory Instructions                         |

| Operating System Instructions                       |

| CDS Instructions                                    |

| Base Set Instruction Coding                         |

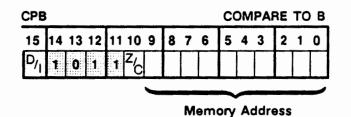

| Memory Reference Instructions 3-11                  |

| Register Reference Instructions 3-16                |

| Input/Output Instructions 3-28                      |

| Extended Arithmetic Memory Reference Instructions   |

| Extended Arithmetic Register Reference Instructions |

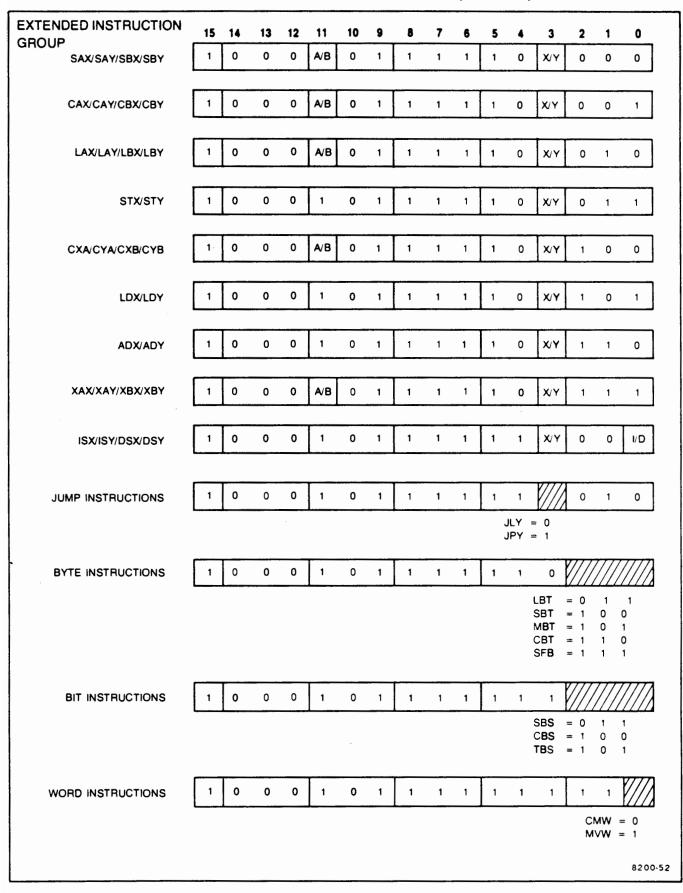

| Extended Instruction Group 3-38                     |

| Floating Point Instructions                         |

| Language Instruction Set 3-58                       |

| Double Integer Instructions                         |

| Virtual Memory Instructions                         |

| Operating System Instruction Set                    |

| Execution Times                                     |

| $C_{A}$                                             |

| Double-Precision          | Float | ing | Poir | nt  | Ins | stru | cti | ion | S   |     |     |     | <br>• • | <br>   |    | <br>   |   |    |   |    | <br>. 3 | -75 |

|---------------------------|-------|-----|------|-----|-----|------|-----|-----|-----|-----|-----|-----|---------|--------|----|--------|---|----|---|----|---------|-----|

| Assembly Language         |       |     |      |     |     |      |     |     |     |     |     |     |         |        |    |        |   |    |   |    |         |     |

| <b>RTE</b> Implementation | • • • |     |      | • • |     | •••  | ••• | ••  | ••• | ••• | ••• | ••• | <br>••• | <br>•• | •• | <br>•• | • | •• | • | •• | <br>. 3 | -80 |

### Chapter 4 Dynamic Mapping System

| femory Addressing                            |  |

|----------------------------------------------|--|

| eneral Descriptions                          |  |

| Page Mapping Register Instructions 4-2       |  |

| Vorking Map Instructions                     |  |

| Cross-Map Instructions                       |  |

| Detailed Descriptions                        |  |

| MS Instruction Execution Times 4-25          |  |

| ssembly Language and RTE Implementation 4-25 |  |

### Chapter 5 Code and Data Separation

| Code and Data Addressing 5                  |     |

|---------------------------------------------|-----|

| General Descriptions                        | 5-3 |

| Procedure Call Instructions                 | 5-3 |

| Procedure Exit Instructions                 | 5-4 |

| C, Q, Z, and IQ Instructions                | 5-4 |

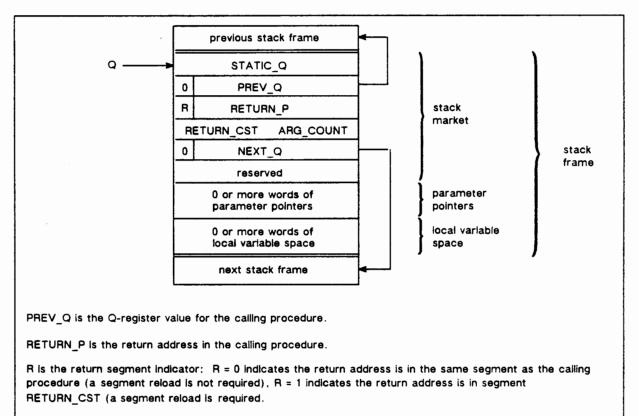

| Stack Frame Description                     | 5-5 |

| Detailed Descriptions                       |     |

| Assembly Language and RTE Implementation 5- | 19  |

| Execution Times                             |     |

### Chapter 6 Interrupt System

| Power-Fail Interrupt                    |   |

|-----------------------------------------|---|

| Parity Error Interrupt                  | , |

| Memory Protect Interrupt                | , |

| Unimplemented Instruction Interrupt 6-5 |   |

| Time Base Generator Interrupt           | ļ |

| Virtual Memory Area Interrupt 6-6       | , |

| CDS Segment Interrupt                   |   |

| Input/Output Interrupt                  |   |

| Interrupt Priority                      | , |

| Central Interrupt Register              |   |

| Processor Status Register               | • |

| Interrupt Type Control                  | , |

| Instruction Summary                     | , |

### Chapter 7 On-Board I/O (OBIO)

| General Description   |          |     | <br>    |   |     |     |     |  | <br>    |   | <br> |   | • • |  |   | <br> |  | <br> |      | <br> | . ′ | 7-1 |

|-----------------------|----------|-----|---------|---|-----|-----|-----|--|---------|---|------|---|-----|--|---|------|--|------|------|------|-----|-----|

| Processor Description | <b>1</b> | • • | <br>    |   |     |     |     |  | <br>    |   | <br> |   |     |  |   | <br> |  | <br> | <br> | <br> | . ′ | 7-2 |

| MCU Pin-Out           |          | • • | <br>••• | • | ••• | • • | • • |  | <br>••• | • | <br> | • | ••• |  | • | <br> |  | <br> |      | <br> | . ′ | 7-2 |

| OBIO Features                                      | · · • |

|----------------------------------------------------|-------|

| I/O Master                                         |       |

| Programming VCP                                    |       |

| Break Detection                                    | . 7-3 |

| MCU Default Configuration for VCP                  | . 7-3 |

| VCP Write                                          |       |

| VCP Read                                           | . 7-4 |

| Driver Registers                                   |       |

| OBIO Data Transfer                                 | . 7-4 |

| CPU to External Device Transfers                   | 7-5   |

| MCU/Driver Communication                           | 7-6   |

| DMA Device Write                                   |       |

| DMA Device Read                                    |       |

| MCU Control Words                                  |       |

| Identity 0: EXEC Read Request                      |       |

| Identity 10: EXEC Write Request                    | . /-/ |

|                                                    |       |

| Identity 11: MCU Control Requests                  |       |

| Identity 11-0000: Port3 Diagnostics                |       |

| Identity 11-0001: Load Executable Code             | /-11  |

| Identity 11-0010: Return MCU Dynamic State         |       |

| Identity 11-0011: Undefined                        |       |

| Identity 11-0100: De-Assert SLRQ- Line             |       |

| Identity 11-0101: Reset                            |       |

| Identity 11-0110: Enter VCP Mode                   |       |

| Identity 11-0111: Set Protocol                     | 7-12  |

| Identity 11-1000: Define User Terminator           | 7-13  |

| Identity 11-1001: Dump FIFO                        | 7-13  |

| Identity 11-1010: Set Baud Rate                    | 7-13  |

| Identity 11-1011: Modem Control                    | 7-14  |

| Identity 11-1100: FIFO Buffering (Input Buffering) | 7-14  |

| Identity 11-1101: Disable Break                    |       |

| Identity 11-1110: Set MCU State                    |       |

| Identity 11-1111: Undefined                        |       |

| Table Of Control Word Responses                    | 7-15  |

| MCU Status Words                                   |       |

| TYPE 000: Read Data Buffer Ready                   | 7-17  |

| TYPE 001: Write Data Buffer Empty                  | 7-17  |

| TYPE 010: Destinationless. Char/Speed Sensing      | 7-17  |

| TYPE 011: Reset Result                             | 7-17  |

| TYPE 100: Modem Information                        | 7-18  |

| TYPE 101: Backspace Information                    |       |

| TYPE 110: FIFO Buffering Data Available            | 7-10  |

| TYPE 111: Error                                    |       |

| MUX Driver Description                             |       |

| A 400 MUX Driver Desisters                         | 7-20  |

| A400 MUX Driver Registers                          |       |

| Data Register 30                                   | 7-20  |

| Control Register 31                                | 7-20  |

| Transfer Type Selection                            |       |

| Register 31 Decoder                                | 7-22  |

| Status Register 32                                 |       |

| Modem Control                                      | 7-22  |

.

.

| Modem States                            |

|-----------------------------------------|

| Modem CPU Interrupts                    |

| RTS [Pin #4]/DTR [Pin #5] 7-23          |

| Clear To Send (CTŠ) Line [Pin #5] 7-23  |

| Data Set Ready (DSR) Line [Pin #6] 7-23 |

| Ring Indicator (RI) Line [Pin #22]      |

| Carrier Detect (CD) Line [Pin #8] 7-24  |

| Firmware Architecture                   |

| CPU Interrupt Request Line              |

| Initialization                          |

| Self-Test                               |

| Port Definitions                        |

| P10 – P17: Modem Control                |

| P20 – P24: SCI                          |

| P30 – P37: MCU Data Port                |

| P40 – P47: MCU Misc Port                |

| Definition Of On-Board RAM 7-26         |

### Chapter 8 Input/Output (I/O) System

| Input/Output Addressing                 |   |

|-----------------------------------------|---|

| Input/Output Priority                   |   |

| Interface Elements                      | 7 |

| Global Register                         | 7 |

| Control Bits                            | 7 |

| Flag Bits                               | 8 |

| Data Buffer Register                    | 8 |

| Control Register                        |   |

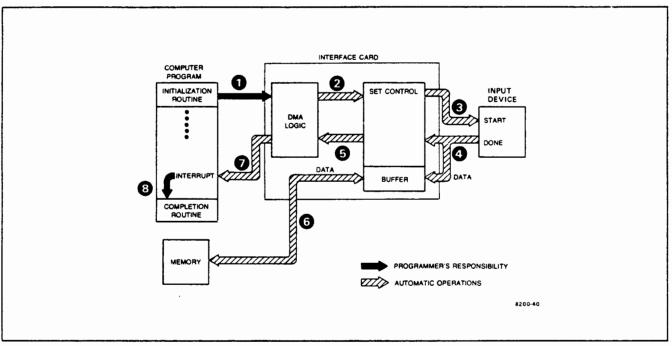

| Direct Memory Access                    |   |

| Control Word 1                          |   |

| Control Word 2                          |   |

| Control Word 3                          |   |

| DMA Transfer Initialization             | 1 |

| Self-Configured DMA                     |   |

| DMA Data Transfer                       |   |

| Non-DMA Data Transfer                   |   |

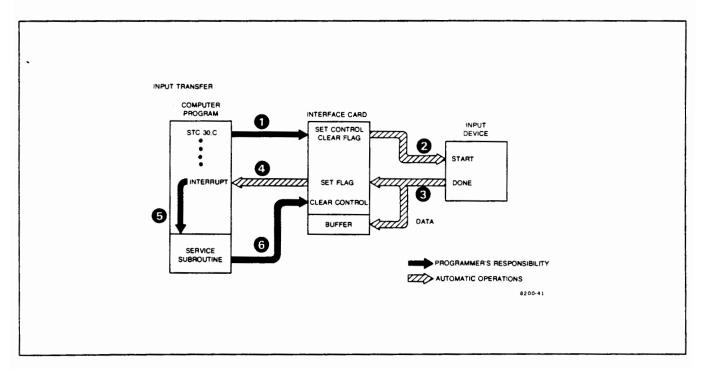

| Input Data Transfer (Interrupt Method)  |   |

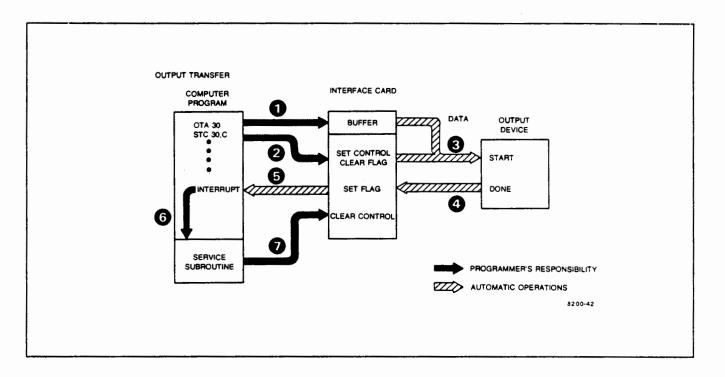

| Output Data Transfer (Interrupt Method) | 5 |

| Non-Interrupt Data Transfer             | 6 |

| Diagnose Modes                          |   |

| Diagnose Mode 1                         |   |

| Diagnose Mode 2                         |   |

| Diagnose Mode 3                         |   |

| Diagnose mode 5                         | , |

#### Appendix A Reference Tables and Conversions

# List of Illustrations

| Figure   | 1-1. | HP 1000 A400 Computers 1-3                                   |

|----------|------|--------------------------------------------------------------|

| Figure   | 1-2. | A400 Computer Simplified Block Diagram                       |

| Figure   | 2-1. | Loading Device Parameters and Media Formats 2-13             |

| Figure   | 2-1. | Loading Device Parameters and Media Formats (Continued) 2-14 |

| Figure   | 2-2. | Loader Command Format 2-20                                   |

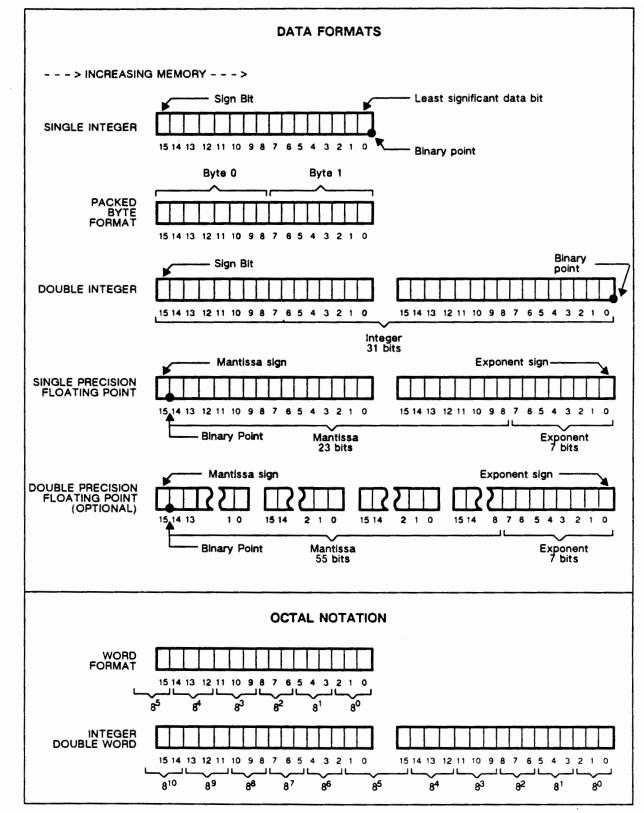

| Figure   | 3-1. | Data Formats and Octal Notation 3-3                          |

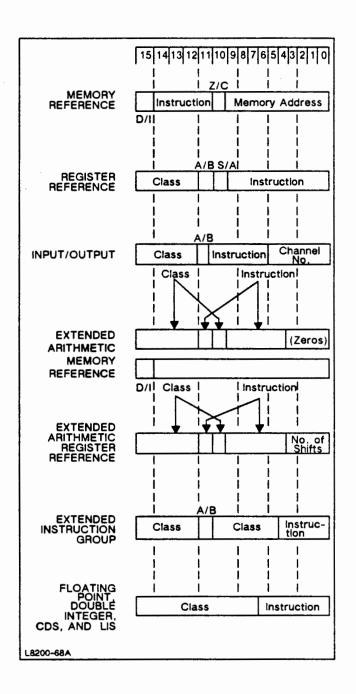

| Figure   | 3-2. | Base Set Instruction Formats                                 |

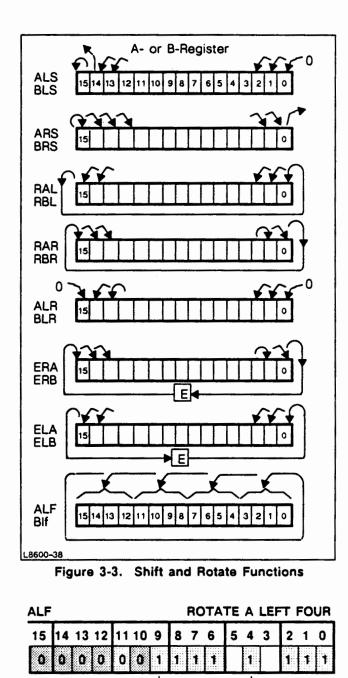

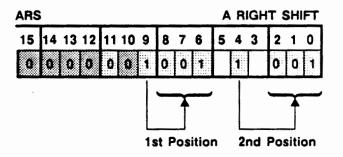

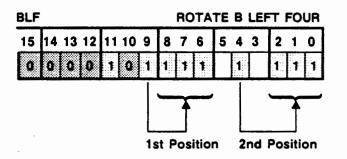

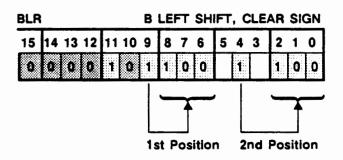

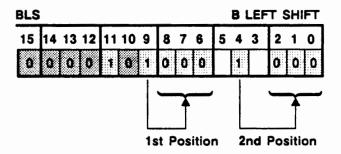

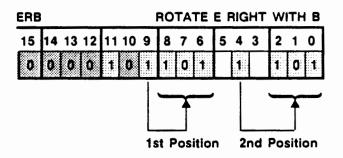

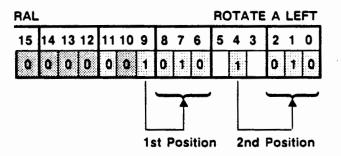

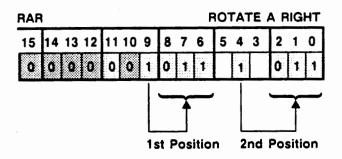

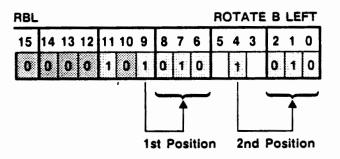

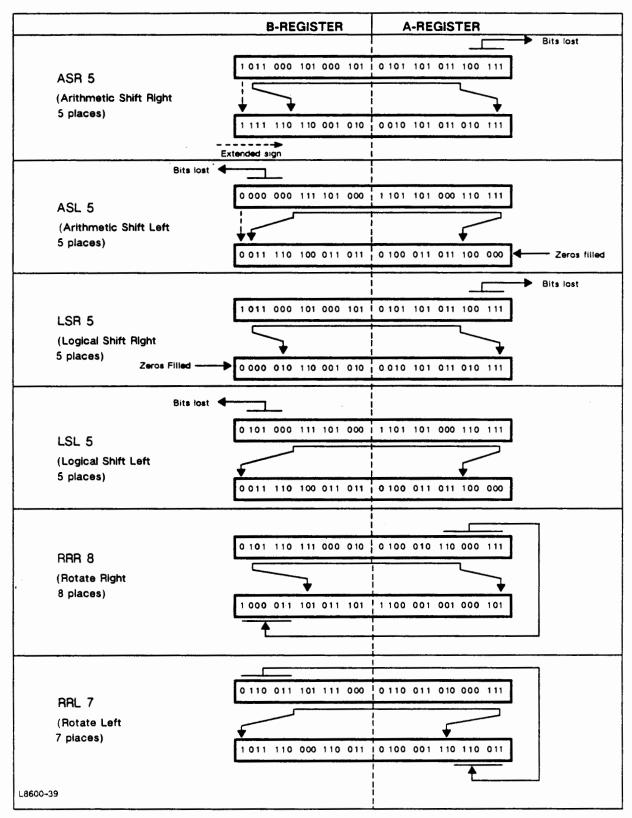

| Figure   | 3-3. | Shift and Rotate Functions                                   |

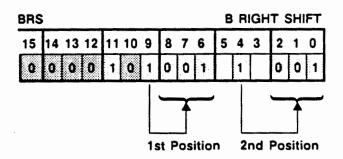

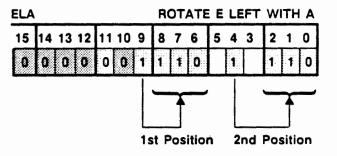

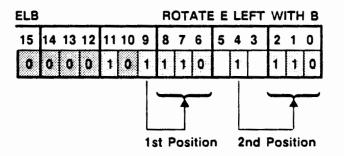

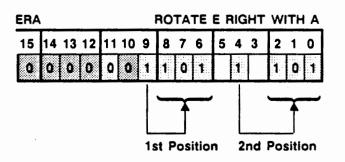

| Figure   | 3-4. | Examples of Double-Word Shifts and Rotates 3-36              |

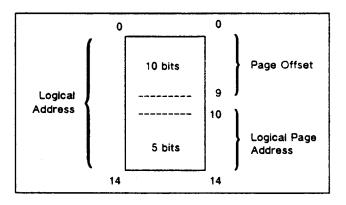

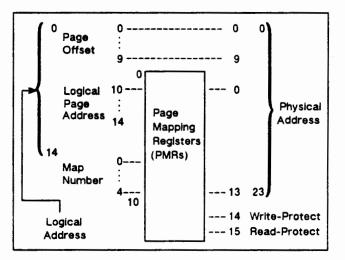

| Figure - | 4-1. | Basic Logical Memory Addressing Scheme 4-1                   |

| Figure   | 4-2. | Expanded Memory Addressing Scheme 4-2                        |

| Figure   | 5-1. | Stack Frame General Layout                                   |

| Figure   | 8-1. | Input/Output System                                          |

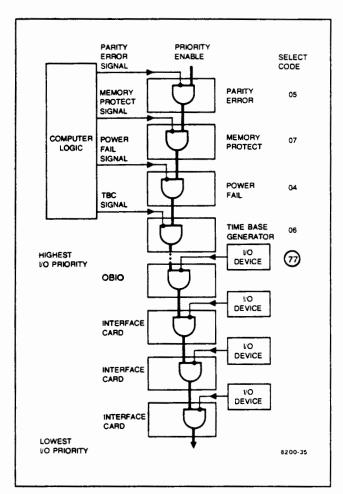

| Figure   | 8-3. | Priority Linkage (Simplified)                                |

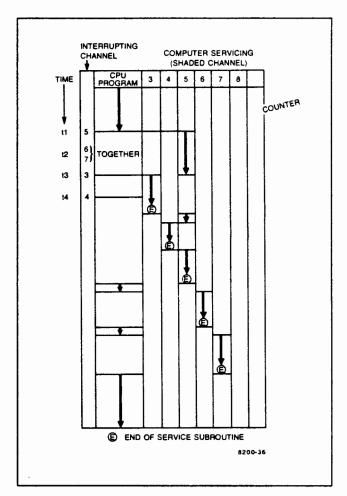

| Figure   | 8-4. | Interrupt Sequence                                           |

# Tables

| Table 1-1. | Options and Accessories                                  | 1-13  |

|------------|----------------------------------------------------------|-------|

| Table 1-2. | Specifications                                           |       |

| Table 1-2. | Specifications (Continued)                               | 1-15  |

| Table 1-2. | Specifications (Continued)                               | 1-16  |

| Table 1-2. | Specifications (Continued)                               | 1-17  |

| Table 1-2. | Specifications (Continued)                               | 1-18  |

| Table 1-2. | Specifications (Continued)                               | 1-19  |

| Table 1-2. | Specifications (Continued)                               | 1-20  |

| Table 1-2. | Specifications (Continued)                               | 1-21  |

| Table 1-2. | Specifications (Continued)                               | 1-22  |

| Table 1-2. | Specifications (Continued)                               |       |

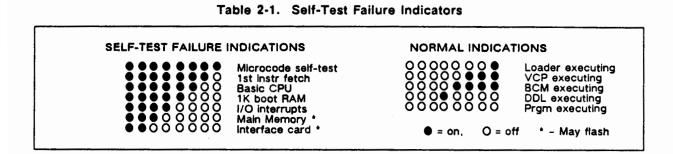

| Table 2-1. | Self-Test Failure Indicators                             | . 2-4 |

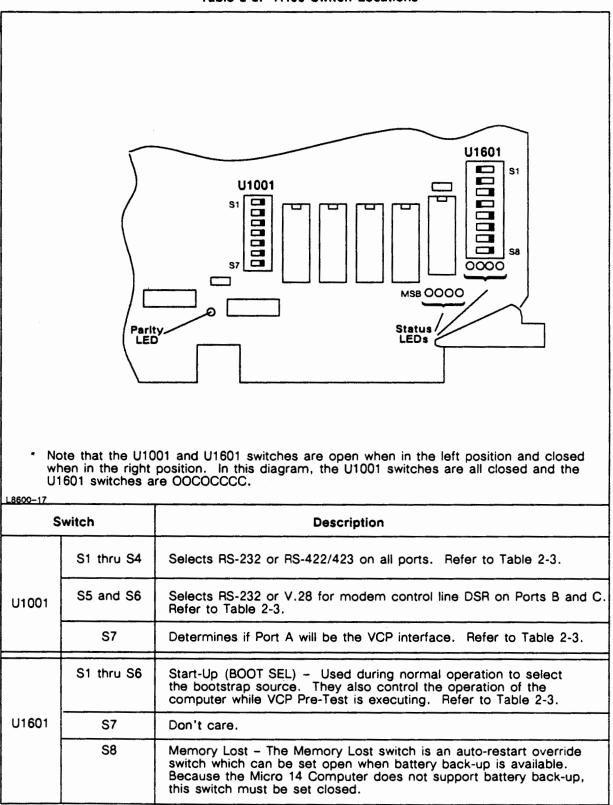

| Table 2-2. | A400 Switch Locations                                    | . 2-7 |

| Table 2-3. | A400 Switch Settings                                     | . 2-8 |

| Table 2-4. | LED Display for I/O Cards                                | . 2-8 |

| Table 2-5. | VCP Characters and Associated Registers                  | 2-15  |

| Table 2-6. | VCP Commands                                             |       |

| Table 2-7. | VCP Loader Command Errors                                | 2-21  |

| Table 3-1. | Memory Paging                                            | . 3-4 |

| Table 3-2. | Reserved Memory Locations                                | . 3-6 |

| Table 3-3. | Shift/Rotate Group Combining Guide                       | 3-17  |

| Table 3-4. | Alter/Skip Group Combining Guide                         | 3-24  |

| Table 3-5. | Typical Base Set Instruction Execution Times             |       |

| Table 3-5. | Typical Base Set Instruction Execution Times (Continued) | 3-82  |

| Table 3-5. | Typical Base Set Instruction Execution Times (Continued) | 3-83  |

| Table 3-5. | Typical Base Set Instruction Execution Times (Continued) | 3-84  |

| Table 3-5. | Typical Base Set Instruction Execution Times (Continued) | 3-85  |

| Table 3-6. | Double Precision Floating Point Execution Times          | 3-85  |

| Table 3-7. | Instructions and Opcodes for RTE-A Implementation        |       |

| Table 4-1. | Dynamic Mapping Instructions Execution Times             |       |

| Table 5-1. | CDS Instruction Execution Times 5-2            | 20 |

|------------|------------------------------------------------|----|

| Table 6-1. | A400 Interrupt Assignments                     | -2 |

| Table 6-2. | Sample Power-Fail Subroutine                   | .3 |

| Table 6-3. | Instructions for Select Codes 00 through 07 6- | .9 |

| Table 8-1. | Non-Interrupt Transfer Rates                   | 7  |

| Table 8-2. | Diagnose Mode 1 8-1                            | 8  |

| Table 8-3. | Diagnose Mode 2 8-1                            | 9  |

#### ALPHABETICAL INDEX OF STANDARD INSTRUCTIONS

| ADA  | Add to A                 | 3-12  |

|------|--------------------------|-------|

| ADB  | Add to B                 | 3-12  |

| ADQA | Add Q to A               | 5-19  |

| ADQB | Add Q to B               |       |

| ADX  | Add Memory to X          |       |

| ADY  | Add Memory to Y          |       |

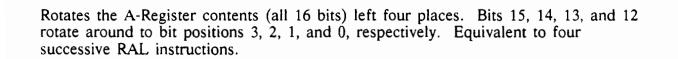

| ALF  | Rotate A Left Four       | 3-18  |

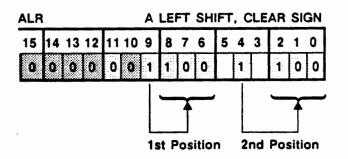

| ALR  | A Left Shift, Clear Sign |       |

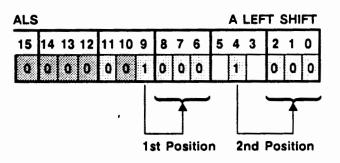

| ALS  | A left Shift             |       |

|      |                          |       |

| AND  | "And" to A               |       |

| ARS  | A Right Shift            |       |

| ASL  | Arithmetic Shift Left    |       |

| ASR  | Arithmetic Shift Right   |       |

| BLF  | Rotate B Left Four       |       |

| BLR  | B Left Shift, Clear Sign | 3-20  |

| BLS  | B Left Shift             | 3-20  |

| BRS  | B Right Shift            | 3-21  |

| CACQ | Copy A to C and Q        |       |

| CAX  | Copy A to X              |       |

| CAY  | Copy A to Y              |       |

| CAZ  | Copy A to Z              |       |

| CBCO | Copy B to C and Q        |       |

| CBS  | Clear Bits               |       |

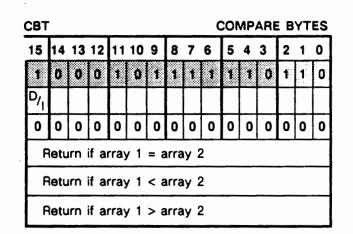

| CBT  | Compare Bytes            |       |

| CBX  | Copy B to X              |       |

| CBX  |                          |       |

|      | Copy B to Y              | 5 17  |

| CBZ  | Copy B to Z              |       |

| CCA  | Clear and Complement A   | 3-24  |

| CCB  | Clear and Complement B   | 3-25  |

| CCE  | Clear and Complement E   | 3-25  |

| CCQA | Copy C to Q and A        | 5-16  |

| CCQB | Copy C to Q and B        |       |

| CIQA | Copy Interrupted Q to A  |       |

| CIQB | Copy Interrupted Q to B  |       |

| CLA  | Clear A                  | 3-25  |

| CLB  | Clear B                  | 3-25  |

| CLC  | Clear Control            | 3-29  |

| CLE  | Clear E                  | ,3-25 |

| CLF  | Clear Flag               |       |

| CLO  | Clear Overflow           |       |

| CMA  | Complement A             |       |

| CMB  | Complement B             |       |

| CME  | Complement E             | 3-26  |

| CMW  | Compare Words            |       |

| CPA  | Compare to A             |       |

| CPA  |                          |       |

|      | Compare to B             |       |

| CXA  | Copy X to A              |       |

| CXB  | Copy X to B              |       |

| CYA  | Copy Y to A              | 3-40  |

| CYB   | Copy Y to B                      | 3-40 |

|-------|----------------------------------|------|

| CZA   | Copy Z to A                      |      |

| CZB   | Copy Z to B                      | 5-18 |

| DIV   | Divide                           | 3-33 |

| DLD   | Double Load                      | 3-34 |

| DST   | Double Store                     | 3-34 |

| DSX   | Decrement X and Skip if Zero     | 3-40 |

| DSY   | Decrement Y and Skip if Zero     | 3-40 |

| ELA   | Rotate E Left with A             |      |

| ELB   | Rotate E Left with B             |      |

| ERA   | Rotate E Right with A            |      |

| ERB   | Rotate E Right with B            |      |

| EXIT  | Procedure Exit                   |      |

| EXIT1 | Procedure Exit with One Skip     |      |

| EXIT2 | Procedure Exit with Two Skips    |      |

| FAD   | Floating Point Add               | 3-55 |

| FDV   | Floating Point Divide            |      |

| FIX   | Floating Point to Single Integer |      |

| FLT   | Single Integer to Floating Point | 3-57 |

| FMP   | Floating Point Multiply          |      |

| FSB   | Floating Point Subtract          |      |

| HLT   | Halt                             |      |

| INA   | Increment A                      |      |

| INB   | Increment B                      |      |

| IOR   | "Inclusive OR" to A              |      |

| ISX   | Increment X and Skip if Zero     |      |

| ISY   | Increment Y and Skip if Zero     | 3-41 |

| ISZ   | Increment and Skip if Zero       |      |

| JLA   | Jump and Load A                  |      |

| JLB   | Jump and Load B                  |      |

| JLY   | Jump and Load Y                  |      |

| JMP   | Jump                             | 3-14 |

| JPY   | Jump Indexed by Y                | 3-48 |

| JSB   | Jump to Subroutine               |      |

| LAX   | Load A Indexed by X              |      |

| LAY   | Load A Indexed by Y              |      |

| LBT   | Load Byte                        |      |

| LBX   | Load B Indexed by X              | 3-42 |

| LBY   | Load B Indexed by Y              | 3-43 |

| LDA   | Load A                           |      |

| LDB   | Load B                           |      |

| LDMP  | Load A Map                       |      |

| LDX   | Load X from Memory               |      |

| LDY   | Load Y from Memory               |      |

| LIA   | Load Input to A                  |      |

| LIB   | Load Input to B                  |      |

| LPMR  | Load Page Mapping Register       |      |

| LSL   | Logical Shift Left (32)          | 3-37 |

| LSR   | Logical Shift Right (32)         |      |

| LWD1  | Load DATA1 Map                   |      |

| LWD2  | Load DATA2 Map                   | 4-10 |

| MB00 Cross I | Move Bytes, Execute to Execute    |

|--------------|-----------------------------------|

| MB01 Cross I | Move Bytes, Execute to DATA1 4-21 |

| MB02 Cross I | Move Bytes, Execute to DATA2      |

| MB10 Cross I | Move Bytes, DATA1 to Execute      |

|              |                                   |

| MB11 Cross I | Move Bytes, DATA1 to DATA1 4-22   |

|              | Move Bytes, DATA1 to DATA2 4-23   |

|              | Move Bytes, DATA2 to Execute      |

| MB21 Cross l | Move Bytes, DATA2 to DATA1 4-24   |

| MB22 Cross I | Move Bytes, DATA2 to DATA2 4-24   |

|              | Bytes                             |

|              | Into A                            |

|              | Into B                            |

|              | y                                 |

|              |                                   |

|              | Words                             |

|              | Move Words, Execute to Execute    |

| MW01 Cross I | Move Words, Execute to DATA1 4-16 |

| MW02 Cross I | Move Words, Execute to DATA2 4-17 |

| MW10 Cross I | Move Words, DATA1 to Execute      |

| MW11 Cross I | Move Words, DATA1 to DATA1 4-18   |

| MW12 Cross   | Move Words, DATA1 to DATA2        |

| MW20 Cross   | Move Words, DATA2 to Execute      |

| MW20 Closs I | Move Words, DATA2 to DATA1        |

|              | Move Words, DATA2 to DATA1        |

|              | Move Words, DATA2 to DATA2 4-20   |

|              | eration                           |

| OTA Output   | A 3-31                            |

| OTB Output   | B                                 |

|              | 1 Procedure Call                  |

|              | al Procedure Call                 |

|              | le External Procedure Call        |

|              | ure Call .ENTR Compatible         |

|              |                                   |

|              | ure Call .ENTN Compatible         |

|              | A Left                            |

|              | A Right                           |

|              | B Left                            |

| RBR Rotate   | B Right                           |

| RRL Rotate   | Left (32) 3-37                    |

|              | Right (32)                        |

|              | e Skip Sense                      |

|              | A Indexed by X                    |

|              | A Indexed by Y                    |

|              |                                   |

|              | s                                 |

|              | Byte                              |

|              | 3 Indexed by X                    |

| SBY Store B  | 3 Indexed by Y 3-45               |

| SDSP Store I | Display                           |

|              | E is Zero                         |

|              | or Byte                           |

|              | Flag Clear                        |

|              | Flag Set                          |

|              |                                   |

|              | nterrupted Map                    |

| SLA Skip if  | LSB of A is Zero                  |

|              |                                   |

| SLB          | Skip if LSB of B is Zero 3                                       | -24,3-27                     |

|--------------|------------------------------------------------------------------|------------------------------|

| SOC          | Skip if Overflow Clear                                           |                              |

| SOS          | Skip if Overflow Set                                             | 3-32                         |

| SPMR         | Store Page Mapping Register                                      | 4-6                          |

| SSA          | Skip if Sign of A is Zero                                        | 3-27                         |

| SSB          | Skip if Sign of B is Zero                                        |                              |

| STA          | Store A                                                          |                              |

| STB          | Store B                                                          |                              |

| STC          | Set Control                                                      | 3-32                         |

| STF          | Set Flag                                                         | 3-32                         |

| STMP         | Store A Map                                                      |                              |

| STO          | Set Overflow                                                     | 3-33                         |

| STX          | Store X to Memory                                                |                              |

| STY          | Store Y to Memory                                                |                              |

| SWMP         | Save Working Map                                                 |                              |

| SZA          | Skip if A is Zero                                                |                              |

| SZB          | Slip if B is Zero                                                |                              |

| TBS          | Test Bits                                                        |                              |

| XAX          | Exchange A and X                                                 |                              |

| XAY          | Exchange A and Y                                                 | 3-46                         |

| XBX          | Exchange B and X                                                 |                              |

| XBX          | Exchange B and Y                                                 |                              |

| XCA1         | Cross Compare A through DATA1 Map                                |                              |

| XCA2         | Cross Compare A through DATA2 Map                                |                              |

| XCB1         | Cross Compare B through DATA1 Map                                |                              |

| XCB1         | Cross Compare B through DATA2 Map                                |                              |

| XJCQ         | Cross Map Jump (and Load C and Q)                                | ۲-۲-۲<br>م.۸                 |

| XJCQ         | Cross Map Jump (and Load C and Q)                                | <del>4</del> -0              |

| XLA1         | Cross Load A through DATA1 Map                                   | ، <del>.</del><br>۸-10       |

| XLA1<br>XLA2 | Cross Load A through DATA1 Map                                   |                              |

| XLA2<br>XLB1 |                                                                  |                              |

| XLB1<br>XLB2 | Cross Load B through DATA1 Map<br>Cross Load B through DATA2 Map | ۰۰۰ <del>۱</del> -۱۱<br>۸-11 |

| XOR          | "Exclusive OR" to A                                              |                              |

| XSA1         | Cross Store A through DATA1 Map                                  |                              |

| XSA1         | Cross Store A through DATA2 Map                                  |                              |

| XSB1         | Cross Store B through DATA1 Map                                  |                              |

| XSB2         | <b>U</b> 1                                                       |                              |

| .CFER        | Cross Store B through DATA2 Map                                  |                              |

| .CPER        | Transfer Complex or Double Floating Point                        | 2 6                          |

|              | Single Integer Arithmetic Compare                                | 2 74                         |

|              | Processor Identification                                         |                              |

| .DAD         | Double Integer Add                                               | 3-03                         |

| .BLE         | Single Floating Point to Double                                  | 2 (2                         |

| DCO          | Floating Point                                                   | 3-02                         |

| .DCO         | Double Integer Compare                                           | 3-0/                         |

| .DDE         | Double Integer Increment                                         |                              |

| .DDI         | Double Integer Divide                                            | 3-69                         |

| .DDIR        | Double Integer Divide Reverse                                    |                              |

| .DDS         | Double Integer Decrement and Skip if Zero                        | 3-67                         |

| .DFER        | Transfer Three Consecutive Words                                 |                              |

| .DIN         | Double Integer Increment                                         | 3-68                         |

| .DIS         | Double Integer Increment and Skip if Zero                        | 3-68                         |

| .DMP  | Double Integer Multiply                 | 3-69 |

|-------|-----------------------------------------|------|

| .DNG  | Double Integer Negate                   | 3-67 |

| .DSB  | Double Integer Subtract                 |      |

| .DSBR | Double Integer Subtract Reverse         | 3-66 |

| .ENTC | Transfer Parameter Addresses            | 3-64 |

| .ENTN | Transfer Parameter Addresses            | 3-64 |

| .ENTP | Transfer Parameter Addresses            | 3-60 |

| .ENTR | Transfer Parameter Addresses            | 3-60 |

| .FIXD | Floating Point to Double Integer        | 3-57 |

| .FLTD | Double Integer to Floating Point        |      |

| .FLUN | Unpack Floating Point Quantity          |      |

| .FWID | Firmware Identification                 | 3-75 |

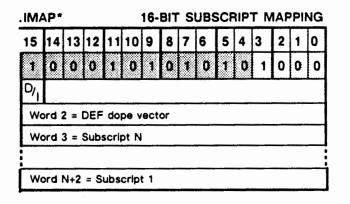

| .IMAP | 16-Bit Subscript Mapping                | 3-71 |

| .IRES | 16-Bit Subscript Resolution             |      |

| .JMAP | 32-Bit Subscript Mapping                | 3-72 |

| .JRES | 32-Bit Subscript Resolution             |      |

| .LBP  | Mapping with Registers                  | 3-74 |

| .LBPR | Mapping with DEF                        | 3-74 |

| .LPX  | Indexed Mapping with Registers          | 3-73 |

| .LPXR | Indexed Mapping with DEF                | 3-73 |

| .NGL  | Double Floating Point to Single         |      |

|       | Floating Point                          | 3-63 |

| .PACK | Normalize Floating Point Quantity       | 3-63 |

|       | Map Specified Page                      | 3-70 |

| .PWR2 | X Times 2 to the Power N                | 3-63 |

| .SETP | Set A Table                             |      |

| .SIP  | Skip if Interrupt Pending               |      |

| .TADD | Double Floating Point Add               |      |

| .TDIV | Double Floating Point Divide            |      |

| .TFTD | Double Integer to Double Floating Point |      |

| .TFTS | Single Integer to Double Floating Point | 3-77 |

|       | Double Floating Point to Double Integer |      |

| .TFXS |                                         |      |

|       | Double Floating Point Multiply          | 3-78 |

| .TSUB | Double Floating Point Subtract          |      |

| .WFI  | Wait for Interrupt                      |      |

|       | Transfer Three Consecutive Words        |      |

|       | Transfer Eight Words                    | 3-58 |

| FCM   | Complement and Normalize Single         |      |

|       |                                         | -    |

|       | Floating Point                          | 3-61 |

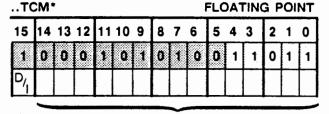

| TCM   |                                         |      |

# Introduction

### General

The HP 1000 A400 Computers and Computer System (hereafter referred to as A400 computers) are low-cost members of the high-performance HP 1000 A-Series processor family. Memory and I/O are combined on the processor board, thereby eliminating two or more PC boards and some redundant logic. The A400 is available at these three levels of integration:

- HP 12100A Single board computer

- HP 2134A Computer in a 20-slot box

- HP 2424A Micro 14 Computer in low-cost 6-slot box

- HP 2434A Micro 24 Computer in 14-slot Micro/1000 box (with or without integral disc)

- HP 2484A/B Micro 24 System Processor Unit with RTE-A Operating System in Micro/1000 box, with or without integral disc.

# Features

- Full A-Series compatibility

- 512k bytes of on-board parity memory

- 32k bytes of Boot PROM

- 10ms time base generator

- Full support of code and data separation (CDS)

- Battery backup and power fail recovery capabilities

- Support for up to four A-Series memory array cards

- 4-channel asynchronous MUX with two ports supporting modem control

- 300, 1200, 9600, 19.2k, and 76.8k baud transfers

# **Single-Board Computer Description**

Product number 12100A is the A400 single-board computer that consists of a CPU, memory controller, 512k bytes of parity memory, and asynchronous serial I/O multiplexer. The A400 board will plug into any A600+/A700 backplane with up to four parity memory arrays and as many standard A-Series I/O cards as the backplane will hold.

The 12100A can be used as the foundation for building a customized computer system. A user-supplied computer cabinet provides the necessary backplane, power supply and cooling fans. The On-Board I/O (OBIO) cable is available for four 25-pin RS-232 serial I/O connections.

Since the A400 board computer is software compatible with current A-Series CPUs, the RTE-A Operating System and all existing A-Series software packages are available for building a computer system.

Table 1-1 gives a brief list of options and accessories available. The following publications provide additional information on selecting components and configuring a computer system.

- A400 Engineering and Reference Documentation, 02424-90003.

- HP 1000 Computer System Software Technical Data, Volume I, part no. 5953-8710 or replacement.

- HP 1000 Computer System Software Technical Data, Volume II, 5953-8721, part no. 5953-8721 or replacement.

- HP 1000 A-Series Computer Handbook, part no. 5954-8576 or replacement.

- HP 1000 System Designer's Guide, part no. 92077-90001.

Figure 1-1. HP 1000 A400 Computers

# Architecture

The A400 computer architecture is based on a distributed intelligence concept that separates the processing of input/output (I/O) instructions from that of other instructions. Most central processor unit (CPU) circuitry resides on a single CMOS chip, packaged in a ceramic 168-pin grid array (PGA).

The A400 CPU executes the HP 1000 instruction set, including:

- Index instructions.

- Instructions for logical operations.

- Bit and byte manipulation.

- Base instructions that include

- Single and double-precision floating point operations.

- Double-integer and virtual memory addressing instructions.

- Language instructions for increased program execution speed for higher level languages such as FORTRAN and Pascal.

The CPU also performs several system-level functions including memory protect, power fail/auto restart, time base generation, and parity error handling.

The entire micromachine plus much of the macromachine support circuitry (such as clock generation, memory control, interrupt control, and macro registers) is included in the CPU chip. The chip is implemented in 1.3 micron double-level CMOS standard cells and contains approximately 20,000 gate equivalents (1 gate equivalent = 2 input NAND gates), plus three custom register files (sixteen 16-bit registers). The mapping system, on-board memory array, control store, and backplane interface are implemented external to the processor chip on the PC board.

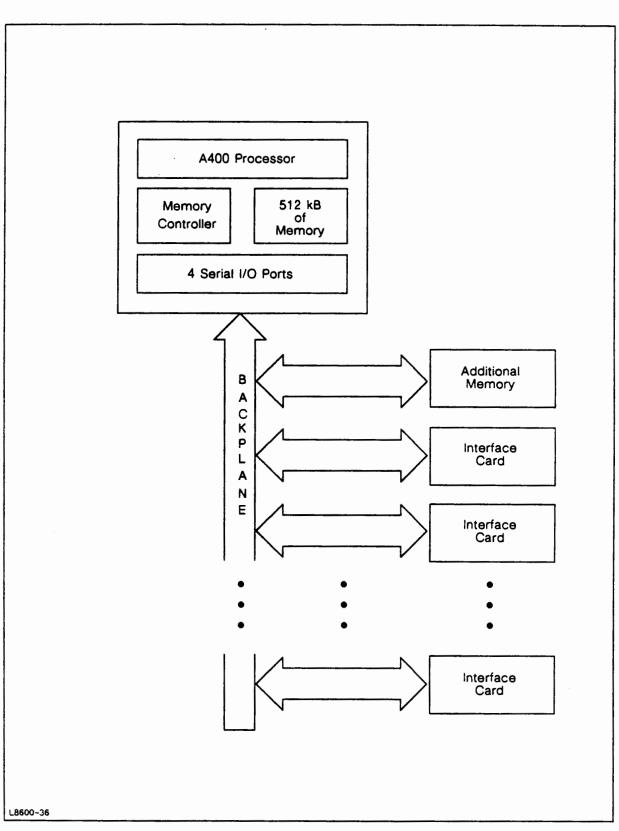

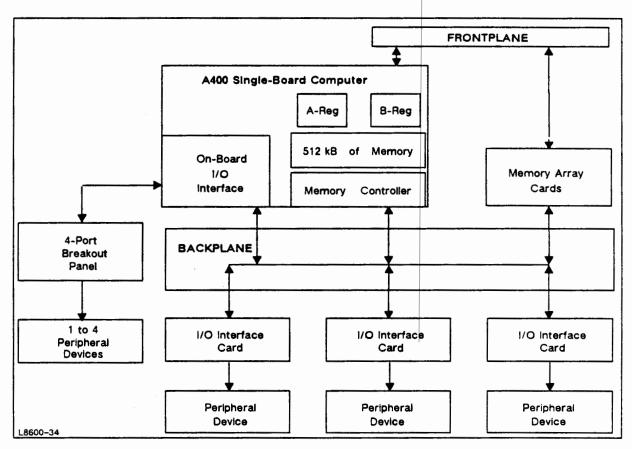

All I/O instructions are executed by custom CMOS input/output processor (IOP) integrated circuit chips that reside on the on-board I/O or on the individual I/O interface cards. A common backplane links the A400 with additional memory array and I/O cards. The instructions are fetched from memory and decoded by the CPU. When an instruction is decoded as being of the I/O type, it is broadcast on the backplane for execution by the appropriate I/O card. Because the OBIO and each I/O card is capable of operating independently of the CPU, the A400 can perform direct memory access (DMA) I/O transfers very efficiently. An I/O card interacts with the CPU only on DMA initiation and completion; beyond that, the entire high-speed transfer is handled by the I/O card, leaving the CPU free to work on other tasks. This achieves high efficiency in CPU and I/O throughput. Figure 1-2 is a simplified block diagram of the A400 computer.

### **Floating Point Processing**

Floating point processing is implemented in firmware, providing high-speed dedicated logic that performs exceptionally fast single precision (32-bit) and double precision (64-bit) floating point arithmetic operations.

## Virtual Control Panel

The Virtual Control Panel (VCP) program is an interactive program that enables an external device (such as a terminal) to control the CPU in a manner similar to a conventional computer control panel. It allows you to access the various registers (such as A, B, and P), examine or change memory, and control execution of a program. The VCP program is stored in the boot memory PROM of the A400. When not being used as the VCP, the VCP-enabled terminal can be used in the same way as any other terminal connected to the system, except that the BREAK key has a unique function in VCP mode. When the A400 computer is operating as a node in a computer network via NS/1000 or DS/1000-IV, the VCP device can be an adjacent computer in the network.

## **Bootstrap Loaders**

There are several bootstrap loaders stored in the VCP PROM on the A400 board. The loaders provide program loading from several sources including disc drives, PROM storage modules, NS/1000 or DS/1000-IV network link, magnetic tapes, HP mini-cartridge tapes, and cartridge tapes of the disc drives. The first three loaders can be selected for auto-boot by switches on the A400 board; any of the loaders can be selected by operator commands via the VCP.

## **Self-Test Routines**

Self-test routines are standard in the A400 computer and are stored in PROM on the A400 board. These routines are executed whenever computer power is turned on, or by operator command via the VCP, providing a check of specific areas of CPU logic.

Figure 1-2. A400 Computer Simplified Block Diagram

## **Time Base Generator**

The A400 board includes a time base generator (TBG) which can be used to update the real-time clock, establish timing points for task switching, and generate microcode timeout interrupts. The time base generator (TBG) can generate an interrupt every 10 milliseconds. The TBG is disabled at power up, and must be explicitly enabled using standard I/O instructions. Once enabled, the first TBG pulse will be generated 10 milliseconds later.

# **Power Supply**

A400 computer packages have power supplies designed to continue normal operation in environments where AC line power may fluctuate widely. Input line voltages and frequencies may vary widely without affecting the operation of the computer.

Battery backup is supported by the A400 processor in 2134A, 2434A, and 2484A/B packages. An optional battery backup card and/or battery pack can be installed to sustain memory for 15 to 90 minutes (depending on memory size) in the event of a complete power failure, thus providing an automatic restart capability.

If power fail protection is needed in an HP 2424A package, an uninterruptable power supply (UPS) should be considered.

Another power supply enhancement to Micro/1000 configurations (and standard in the 2134A) is 25-kHz voltage that can be rectified at the load and used to power accessory plug-in cards used for measurement and control applications.

## Input/Output (I/O)

Data transfer between the computer and I/O devices can take place under DMA control or program control. The DMA capability provides a direct link between memory and I/O devices. The total bandwidth available through multiple DMA channels is 4.4 million bytes (2.2 million words) per second.

#### On-Board I/O (OBIO)

The A400 computer contains on-board I/O (OBIO) circuitry consisting of an I/O processor chip, I/O master circuitry, and four serial I/O ports. The following functionality is provided by the OBIO circuitry:

Transmission Mode Bit-serial, Asynchronous Capacity

Four full duplex communications channels Two-channel modem support

**Programmable Features**

Echo on or off Switch-programmable VCP port Record termination processing (any character) Baud rate selection (300, 1200, 9600, 19.2K, and 76.8K) Backspace processing ENQ/ACK handshake XON/XOFF handshake

Interface Levels

RS-232 and V.28 (standard) RS-422/423 (user-supplied cable for each channel) Any mix of interface levels

Maximum Cable Length (depending on baud rate)

RS-232, 15 meters (19.2k baud) RS-423, 50 meters (19.2k baud) RS-422, 1200 meters (19.2k baud)

Error Detection

Framing errors and overrun errors Parity errors may be checked using software library routines.

Modem Control

Interacts with six modem control lines: Clear to Send, Request to Send, Data Set Ready, Carrier Detect, Data Terminal Ready, Ring Indicator.

Two of the four ports drive the six modem control lines required for normal modem control. A "Break" on Port A will give you access to VCP, when enabled. The port processor also handles backspace processing to minimize the interrupts that the CPU must process. The I/O master and the single DMA channel that it provides are shared by the four port processors. The select code for OBIO is select code 77, and cannot be changed.

#### Support of A-Series I/O Cards

The A400 supports as many A-Series I/O cards as the card cage capacity allows. The I/O cards contain a custom I/O processor chip on each card, enabling each card to process its own I/O instructions and handle direct memory access (DMA) data transfers. The I/O system has a multilevel vectored priority interrupt structure with 60 distinct interrupt levels, each of which has a unique priority assignment. Any I/O device can be selectively enabled or disabled, or all I/O devices can be enabled or disabled under program control.

An important feature of the interface cards is a common-content Global Register which can be loaded with the select code of a specific I/O card. When the Global Register is enabled, all I/O instructions are executed only by the I/O card whose select code is in the Global Register. This not only facilitates setting up DMA transfers but also makes reconfiguration of an I/O driver a simple matter of changing the Global Register to the appropriate select code. Also, because the Global Register can direct I/O instructions to a specific I/O card, the I/O-instruction address bits can be used to access registers on an I/O card. This feature is utilized in the design of the I/O cards to increase their capabilities.

About one-third of the area on the interface cards is occupied by the I/O Master, which consists of an I/O processor chip and its associated logic. The I/O Master is also available in breadboard form for users who wish to design their own I/O cards. The I/O Master is described in detail in the HP 1000 A/L-Series Computer I/O Interfacing Guide, part no. 02103-90005.

## Memory

The A400 computer contains a memory controller and 512k bytes of user RAM (with parity) resident on board. Also included are 2k bytes of boot RAM and 32k bytes of boot PROM on board.

#### Memory Controller

The memory controller interfaces to the processor, on-board memory, optional memory array cards, and I/O. The processor controls memory array card operations by connections across the backplane and a memory array front plane. Interaction with I/O occurs across the backplane.

The memory controller is responsible for the following functions:

- Generating handshake signals for backplane (BUSY, VALID).

- Latching data and addresses during memory cycles.

- Generating interrupt signals (MPV, PE).

- Arbitrating memory and refresh cycles.

- Generating read strobes for array cards.

- Protecting memory during illegal accesses.

- Accessing loader and front panel firmware.

- Inhibiting array cards during protected access.

- Maintaining memory data during power failures.

- Verifying that physical address indeed accesses an existing array card and if not drive all "1's" onto backplane.

- Determine whether the requested memory cycle should occur in two or three clock signal cycles.

#### Memory Access

The A400 memory system is "dynamically mapped" which provides the ability to access more than 32k words of 16-bit data. Map RAMs generate the physical address of data to be accessed during a memory cycle. Mapping widens the 15-bit address bus on the backplane (which can access up to 32k words of memory) to a 24-bit address bus (combined backplane and frontplane) which can access up to 16M words of memory. The memory array cards are word addressable.

Memory access can be initiated by either the processor or by an I/O device using DMA. Processor accesses can be read and/or write protected by two bits that are stored in the map RAMs. Thus, processor access to protected memory will cause an interrupt to occur (if memory protect is enabled) and the access will be aborted. An I/O device using DMA can access protected memory, however. This is true for either a read or write access.

The detection of a parity error on a read causes the assertion of a parity error signal on the backplane. This condition signal is handled by the processor or by the I/O card depending on which initiates the access.

#### Memory Expansion

The A400 processor allows main memory expansion beyond the on-board 512k bytes. A maximum of four megabytes of main memory can be supported by adding the following memory array cards:

- 12103C 512k byte parity array card

- 12103D 1M byte parity array card

- 12103K 2M byte parity array card

- 12103L 4M byte parity array card

- 12103M 8M byte parity array card

Error correcting code (ECC) memory and the 12103B 256k byte memory array card are not supported.

When a 12103C or 12103D array card is added to the system, its size must conform to the address space boundaries. A compatible size is indicated when an integer results from dividing the size of existing memory by the size of the array card to be added. The 12103K/L/M cards are self-configuring and the integer rule does not apply. They can be added on any half-megabyte boundary.

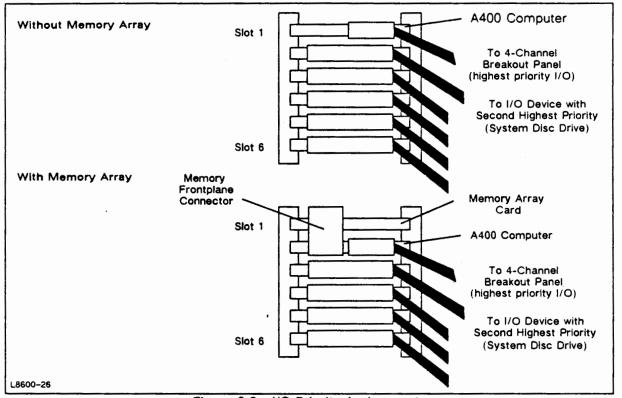

When installing array cards there is no need to physically identify the array cards (such as jumper or switch setting to set recognition of physical address space). The memory controller automatically designates the on-board memory as the first memory address space. The array cards configure themselves in ascending order going away from the on-board memory. The beginning of the memory is, therefore, the on-board memory and the end of memory is on the array farthest from the on-board memory.

It is possible to use partially loaded array cards as long as the total memory on the array is either 512k or 1M bytes. The partially loaded arrays can be incorporated into the module self-configuring scheme. There can be a total of up to four array cards in the system. For the proper order of installation, refer to the appropriate installation and service manual.

### Software

Software support for the A400 computers begins with RTE-A, a member of HP's family of Real-Time Executive (RTE) operating systems. RTE-A is a real-time multi-programming, multi-user operating system designed to take full advantage of the A400 I/O structure to enhance overall CPU and I/O throughput. RTE-A offers a wide range of configurations, from a small, memory-based, execute-only system to a full disc-based system with on-line program development. Utilizing the A400 mapped memory system, RTE-A supports user partitions of up to 64k bytes and memory sizes up to 32 megabytes.

Memory can be divided into fixed and dynamically allocated partitions at system generation time. Critical programs can be made resident in fixed partitions to ensure fastest possible response to requests for their execution. Other programs can be assigned partitions from the dynamic memory pool according to need, using the smallest available block of memory.

RTE-A also supports Virtual Memory Addressing (VMA) for access to data arrays much larger than main memory (up to 12.6 megabytes). The disc functions as an extension of main memory so far as data is concerned, in a manner that is transparent to the user and does not require any special programming. In addition, RTE-A supports a special case of VMA, called Extended Memory Area (EMA). With EMA, up to two megabytes of a program's data can be in main memory at once, which affords faster processing of data arrays small enough to use the EMA capability. The programmer chooses the data array handling mode at program load time.

Disc-based RTE-A systems support program development in FORTRAN 77, Pascal/1000, BASIC/1000, and Macro/1000 Assembly Language. Program development for the A400 can also be performed on an HP 1000 System under RTE-6/VM or RTE-IVB.

The diagnostic packages listed in Table 1-1 may be used for testing and fault location.

## HP Interface Bus (HP-IB)

Among the I/O interface cards available for the A400 computer is the HP 12009A HP-IB Interface Card which can interface the A400 computer to a variety of HP peripherals and other equipment compatible with the Hewlett-Packard Interface Bus (HP-IB). (HP-IB is the Hewlett-Packard implementation of IEEE standard 488-1978, "Digital Interface for Programmable Instrumentation".) A single HP 12009A can control up to 14 HP-IB instruments and several can be used to achieve concurrent operation of multiple HP-IB instrumentation clusters under the RTE-A multiprogramming operating system.

## **Computer Network**

You can configure the A400 computer into an HP NS/1000 or DS/1000-IV Distributed System by using either an HP 12007B or an HP 12044A HDLC Interface. Both of these interfaces support the high-level data link communications (HDLC) protocol, functioning as a preprocessor to handle low and medium levels of protocol processing. The A400 computers can be easily mixed with other members of the HP 1000 family in a single computer network. The HP 12042B Programmable Serial Interface (PSI) card allows sophisticated OEMs to design customized protocols for networks. Hewlett-Packard offers a customer training course on how to program the PSI card.

### **Expansion and Enhancement**

Table 1-1 lists accessory products available to expand or enhance the A400 computers.

### **Specifications**

The HP 1000 A-Series Computer Handbook, part no. 5954-8576 or replacement, provides complete specifications for the A400 computers and systems.

Table 1-2 provides an abridged set of A400 specifications. Except where indicated, the specifications are applicable to the HP 2134A/2424A/2434A Computer and the HP 2484A/B Computer System. Both the computer and the computer system have been product accepted by the Underwriters' Laboratories (UL) and the Canadian Standards Association (CSA). The A400 computer and system also meet the RFI standards of the Federal Communications Commission (FCC) and Verband Deutches Electrotechnikes (VDE).

| DESCRIPTION                                                                                   | HP PRODUCT NO.   |

|-----------------------------------------------------------------------------------------------|------------------|

| 230 Vac Operation                                                                             | Opt 015          |

| 512K Byte Memory Array Card                                                                   | 12103C           |

| 1M Byte Memory Array Card                                                                     | 12103D           |

| 2M Byte Memory Array Card                                                                     | 12103K           |

| 4M Byte Memory Array Card                                                                     | 12103L           |

| 8M byte Memory Array Card                                                                     | 12103M           |

| Memory Connector for one memory array card                                                    | 12038A           |

| Memory Connector for two memory array cards                                                   | 12038B<br>12038C |

| Memory Connector for three memory array cards<br>Memory Connector for four memory array cards | 12038D           |

| Asynchronous Serial Interface                                                                 | 12005B           |

| Parallel Interface                                                                            | 12005B           |

|                                                                                               | 12008A           |

| HDLC Interface (modem operation)                                                              |                  |

| PROM Storage Module                                                                           | 12008A           |

| HP-IB Interface                                                                               | 12009A           |

| Intelligent Breadboard                                                                        | 12010A           |

| Extender Board                                                                                | 12011A           |

| Priority Jumper Card                                                                          | 12012A           |

| Input/Output Extender                                                                         | 12025A/B-002     |

| 8-Channel Asynchronous Multiplexer                                                            | 12040D           |

| Multi-use 8-channel Multiplexer                                                               | 12041A/B         |

| Programmable Serial Interface                                                                 | 12042A           |

| Multi-use Programmable Serial Interface                                                       | 12043A           |

| HDLC Interface (hard-wired operation)                                                         | 12044A           |

| High-Level Analog Input Card*                                                                 | 12060A           |

| Expansion Multiplexer Card*                                                                   | 12061A           |

| Analog Output Card*                                                                           | 12062A           |

| 16-In/16-Out Isolated Digital I/O Card*                                                       | 12063A           |

| Color Video Interface                                                                         | 12065A           |

| DS/1000-IV Data Link Slave Interface                                                          | 12072A           |

| DS/1000-IV Modem Interface to HP 3000                                                         | 12073A           |

| LAP-B Network Interface                                                                       | 12075A           |

| DS/1000-IV Direct Connect Interface to HP 3000                                                | 12082A           |

| LAN Interface                                                                                 | 12076A           |

| Data Link Master Interface                                                                    | 12092A           |

| HP-IB Extender Card                                                                           | 37203L           |

| Integral Modem Interface                                                                      | 37222A           |

| Battery Backup Card                                                                           | 12154A           |

| Battery Backup for 2134A                                                                      | 12157B           |

| 25 kHz Sine Wave Card                                                                         | 12159A           |

| Diagnostic Package for A400 processor and interfaces**                                        | 24612A           |

|                                                                                               | 24398B           |

| Diagnostic Package for A400-compatible hard disc drives and                                   |                  |

| magnetic tape units**                                                                         |                  |

| HP-1B Extender card                                                                           | 37203L           |

| Integral Modem Interface                                                                      | 37222A           |

#### Table 1-1. Options and Accessories

•

SPECIFICATIONS COMMON TO THE HP 2134A, 2424A, 2434A, AND 2484A/B CENTRAL PROCESSOR 16 Word Size: Instruction Set: 205 standard instructions. Memory Reference: 14 43 Register Reference: 13 Input/Output: 10 **Extended Arithmetic:** 34 Index: 10 Bit, Byte, Word Manipulation: Floating Point (single precision): 8 Language: 11 40 Dynamic Mapping: Double Integer: 12 Virtual Memory: 9 4 Operating System: Floating Point (double precision): 8 Code and Data Separation: 21 Registers: Accumulators: Two (A and B), 16 bits each. Implicitly addressable, also explicitly addressable as memory locations. Two (X and Y), 16 bits each. Index: One (P), 15 bits. Memory Register: One (Q), 15 bits; one (C), 1 bit. Base: Bounds: One (Z), 16 bits. Supplementary: Two (overflow and extend), 1 bit each. Time Base Generator A time base generator interrupt is provided for Interrupt: maintaining a real time clock. The interrupt request is made when the CPU signals, at 10-millisecond intervals, that its internal clock is ready to roll over. Timing accuracy of the time base generator is ±2.16 seconds per 24-hour day.

| MICROMACHINE                  |                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Space:                | 16,384 words (256 blocks of 64 words each).                                                                                                                                                                                                                                                                                                                                                                               |

| Microinstruction Word Size:   | 32 bits.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Microaddress Space            | 16k microwords.                                                                                                                                                                                                                                                                                                                                                                                                           |

| Word Types:                   | six                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycle Time:                   | 227 nanoseconds                                                                                                                                                                                                                                                                                                                                                                                                           |

| Microorders:                  | 198                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operations:                   | 14                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Special:                      | 56                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ALU and Conditional:          | 48                                                                                                                                                                                                                                                                                                                                                                                                                        |