# **HP 1000 A-Series Computer**

I/O Interfacing Guide

Measurement & Control Systems Divison 11000 Wolfe Road Cupertino, CA 95014

Manual Part No. 02103-90055 E0292 Printed in U.S.A. February 1992 First Edition

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THE MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Hewlett-Packard Company.

RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARs 252.227.7013

Copyright © 1992 by HEWLETT-PACKARD COMPANY

### Safety and Regulatory Information

For your protection, this product has been tested to various national and international regulations and standards. The scope of this regulatory testing includes electrical/mechanical safety, radio frequency interference, ergonomics, acoustics, and hazardous materials. Where required, approvals obtained from third-party test agencies are shown on the product label. In addition, various regulatory bodies require some of the information under the following headings.

#### **USA Radio Frequency Interference**

The United States Federal Communications Commission (in 47CFR Subpart J, of Part 15) has specified that the following notice be brought to the attention of the users of this product:

# Warning

This equipment generates, uses, and can radiate radio frequency energy, and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested for compliance with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

#### Japanese Radio Frequency Interference

The following notice is for users of this product in Japan:

この装置は、第一種情報装置(商工業地域において使用されるべき情報装置) で商工業地域での電波障害防止を目的とした情報処理装置等電波障害自主規制 協議会(VCCI)基準に適合しております。 従って、住宅地域またはその隣接した地域で使用すると、ラジオ、テレビジ ョン受信機等に受信障害を与えることがあります。 取扱説明書に従って止しい取り扱いをして下さい。

#### Japanese Radio Frequency Interference

## HP Computer Museum www.hpmuseum.net

For research and education purposes only.

#### **German Radio Frequency Notice**

This is to certify that this product meets the Radio Frequency Interference Requirements of Directive 1046/84. The German Bundespost has been notified that this equipment has been put into circulation and has been granted the right to check the product type for compliance with these requirements.

#### Funkentstörung Deutschland (German EMI Compliance) Herstellerbescheinigung

Hiermit wird bescheinigt, daß dieses System in Übereinstimmung mit den Bestimmungen von Postverfügung 1046/84 funkentstört ist.

Der Deutschen Bundespost wurde das Inverkehrbringen dieses Systems angezeigt und die Berechtigung zur Überprüfung der Serie auf Einhaltung der Bestimmungen eingeräumt.

United Kingdom Telecom Statement (For the United Kingdom Only)

Interconnection of ports marked "UNITED KINGDOM TELECOM WARNING: Connect only apparatus complying with BS 6301 to these ports" with ports not so marked may produce hazardous conditions on the network and advice should be obtained from a competent engineer before such a connection is made.

Connect only apparatus complying with BS 6301 to the ports marked with the above warning.

# **Safety Considerations**

GENERAL - This product and related documentation must be reviewed for familiarization with safety markings and instructions before operation.

## SAFETY SYMBOLS

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect the product against damage.

Indicates hazardous voltages.

Indicates earth (ground) terminal (sometimes used in manual to indicate circuit common connected to grounded chassis).

Explanation of Caution

Caution

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

Explanation of Warning

# Warning

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

·

.

.

# **Printing History**

The Printing History below identifies the edition of this manual and any updates that are included. Periodically, update packages are distributed which contain replacement pages to be merged into the manual, including an updated copy of this printing history page. Also, the update may contain write-in instructions.

Each reprinting of this manual will incorporate all past updates; however, no new information will be added. Thus, the reprinted copy will be identical in content to prior printings of the same edition with its user-inserted update information. New editions of this manual will contain new information, as well as all updates.

First Edition ...... Feb 1992 .....

- -

# Preface

This manual has been prepared as a guide in selecting the proper interfacing approach and as an aid in selecting or designing the appropriate hardware and software interfaces to the HP 1000 A-Series Computer I/O system. This manual complements the HP 1000 A400, A600/A600+, A700, A900, and A990 Computer Reference Manual. You should become thoroughly familiar with the contents of this manual and the applicable Computer Reference Manual before attempting to use the information presented in any part of this manual.

**CHAPTER 1:** INTRODUCTION — Presents an overview of the A-Series computer architecture, features, concepts, functional specifications, and an introduction to the ease of hardware and software interfacing.

**CHAPTER 2:** PROGRAMMING — Presents specific code segments that perform the functions of the I/O system. Included are any special features or considerations to simplify the task of the designer.

**CHAPTER 3:** HP INTERFACES — Provides a list of available general-purpose A-Series I/O interfacing cards and their manuals, and gives a brief description of the HP 12010A Breadboard interface.

CHAPTER 4: I/O MASTER — Describes the purpose, elements, and control of the I/O system and the I/O Master theory of operation. Also included are specifications and diagrams for the HP 12010A Breadboard; lists of signal names, mnemonics, and definitions; and signal timing diagrams and specifications.

.

·

# **Table of Contents**

## Chapter 1 Introduction

| Computer Overview              | 1-1  |

|--------------------------------|------|

| A400 Computer                  | 1-1  |

| A600 and Å600+ Computer        | 1-2  |

| A700 Computer                  | 1-2  |

| A900 Computer                  | 1-3  |

| A990 Computer                  | 1-3  |

| A-Series Backplane             | 1-4  |

| I/O System                     | 1-4  |

| I/O Addressing                 | 1-5  |

| I/O Priority                   | 1-10 |

| I/O Processing                 | 1-13 |

| Slave Mode Transfers           | 1-14 |

| Interrupt Processing           | 1-14 |

| Interface Elements             | 1-15 |

|                                | 1-15 |

| Global Register                | 1-15 |

| Control Bits                   |      |

|                                | 1-16 |

| Data Buffer Register           | 1-16 |

| Card Control Register          | 1-16 |

| Functional Specifications      | 1-16 |

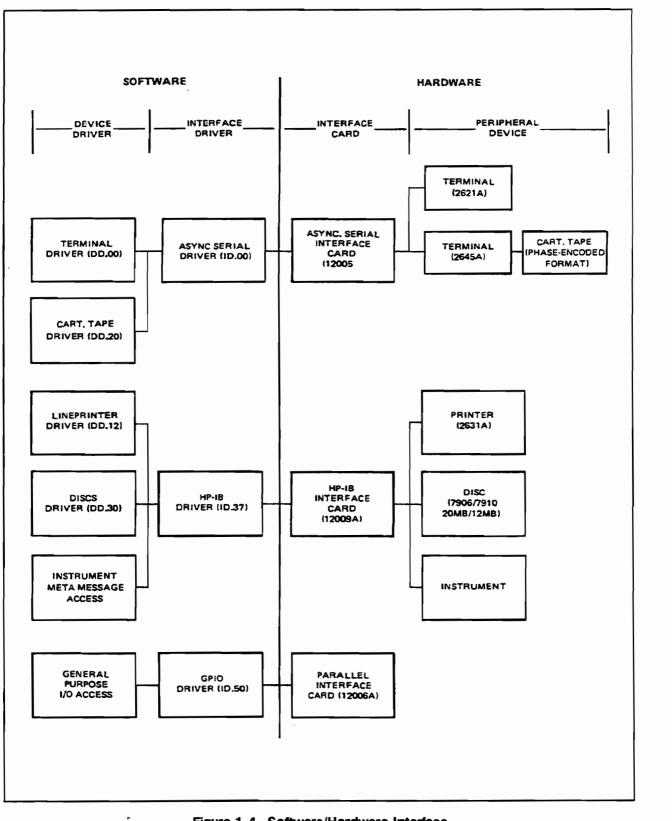

| Introduction to Interfacing    | 1-21 |

| Interface/Device Drivers       | 1-21 |

| I/O Master                     |      |

| User Interface Requirements    | 1-23 |

| Levels of Hardware Interfacing | 1-24 |

| Level 1                        | 1-24 |

| Level 2                        | 1-24 |

| Level 3                        | 1-24 |

| Available Documentation        | 1-25 |

## Chapter 2 Programming

| I/O System Programming                                              | 2-1 |

|---------------------------------------------------------------------|-----|

| System Level I/O (Select Code 0-17)                                 | 2-1 |

| Interrupt System, Control Reset, and Interrupt Mask (Select Code 0) | 2-2 |

| Status Register, Processor LEDs, Switches and Overflow Bit          |     |

| (Select Code 1)                                                     | 2-3 |

| Global and Diagnose Registers, and ROM Enable (Select Code 2)       | 2-3 |

| Virtual Control Panel (Select Code 3)                               | 2-5 |

| Power-Fail/Auto-Restart and CIR (Select Code 4)       | 2-5  |

|-------------------------------------------------------|------|

| Parity Error (Select Code 5)                          | 2-6  |

| Time Base Generator (Select Code 6)                   | 2-7  |

| Memory Protect and Violation Register (Select Code 7) | 2-7  |

| Unimplemented Instruction (Select Code 10)            | 2-8  |

| Reserved (Select Code 11–16)                          | 2-8  |

| Interrupt Priority                                    | 2-8  |

| Instruction Usage Summary                             | 2-9  |

| Interface I/O (Select Codes 20–77)                    | 2-9  |

|                                                       | 2-10 |

|                                                       | 2-13 |

|                                                       | 2-14 |

|                                                       | 2-14 |

|                                                       | 2-14 |

|                                                       | 2-14 |

|                                                       | 2-17 |

|                                                       | 2-17 |

|                                                       | 2-18 |

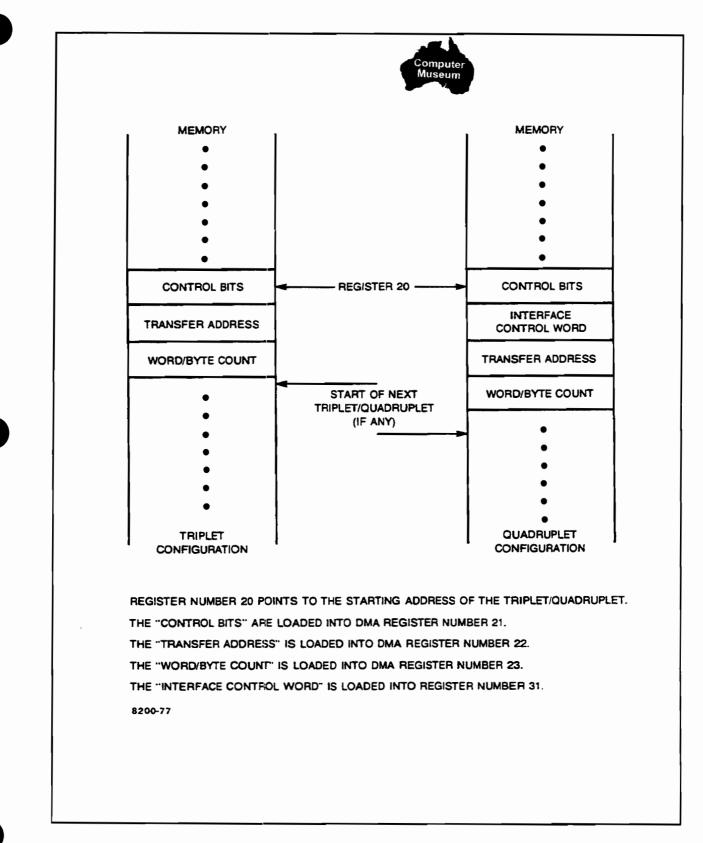

| Self-Configured DMA Operation                         | 2-20 |

| Self-Configured DMA Termination                       | 2-22 |

| Programmed I/O                                        | 2-22 |

|                                                       | 2-22 |

|                                                       | 2-22 |

|                                                       | 2-24 |

| Interrupt Processing                                  | 2-24 |

|                                                       | 2-25 |

| Input Initiation                                      | 2-25 |

|                                                       | 2-26 |

|                                                       | 2-26 |

|                                                       | 2-26 |

| Output Operation                                      | 2-27 |

| Output Termination                                    | 2-27 |

| Non-Interrupt I/O                                     | 2-28 |

| Input Initiation                                      | 2-28 |

| Input Operation                                       | 2-28 |

|                                                       | 2-29 |

| Output Initiation                                     | 2-29 |

|                                                       | 2-30 |

| Output Termination                                    | 2-30 |

.

## Chapter 3 HP Interfaces

| I/O Interface                  | 3-1 |

|--------------------------------|-----|

| Available Interfaces           | 3-2 |

| HP 12010A Breadboard Interface | 3-2 |

| Features                       | 3-2 |

## Chapter 4 I/O Master

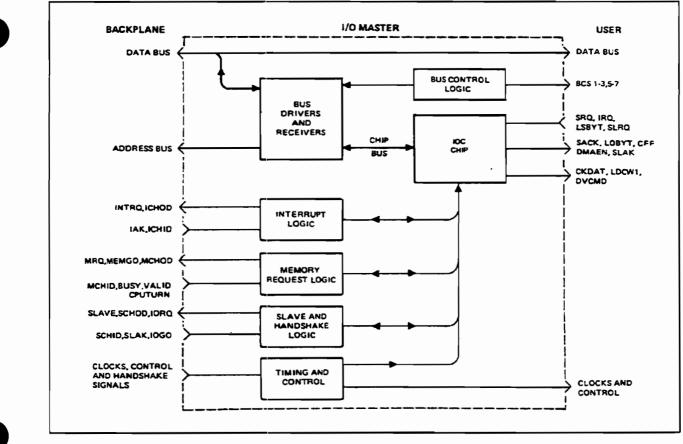

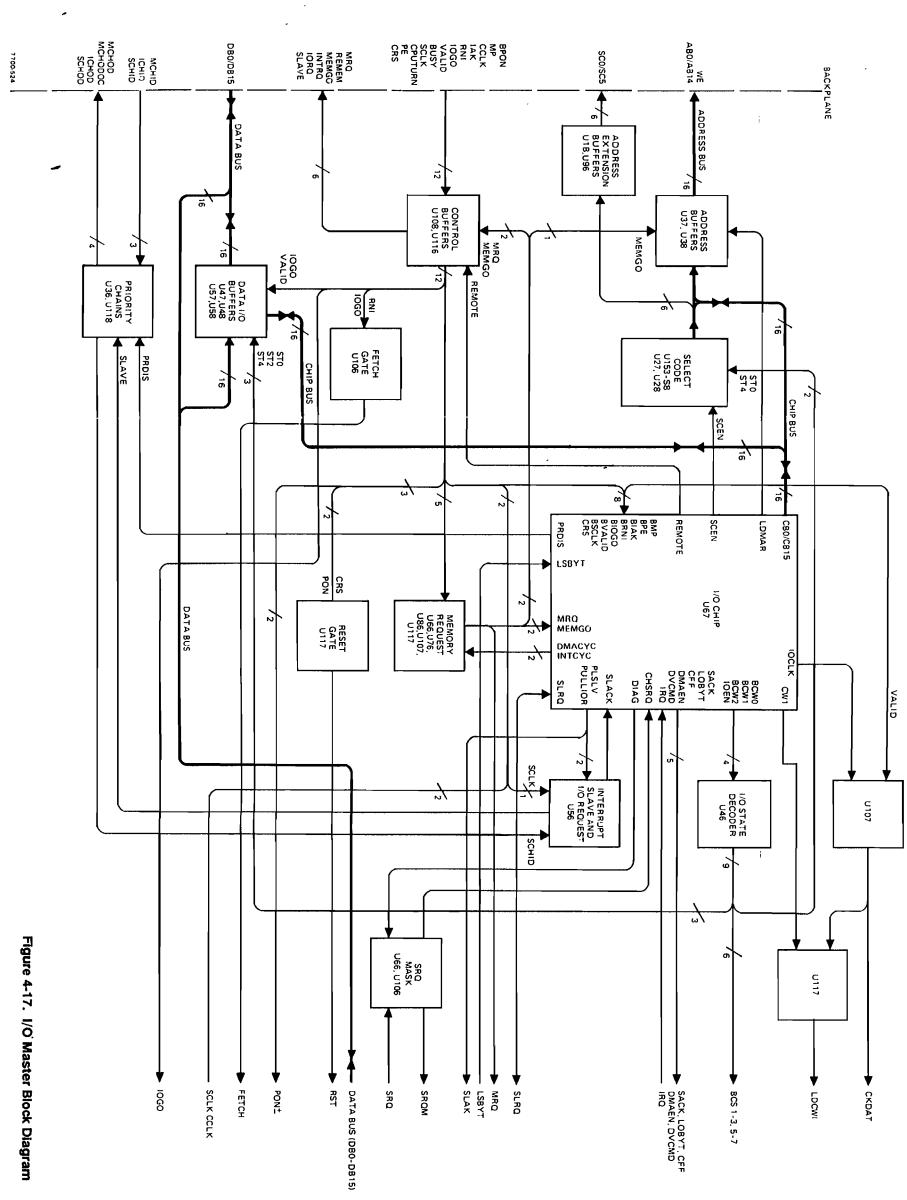

| Functional Description                                      | 4-1  |

|-------------------------------------------------------------|------|

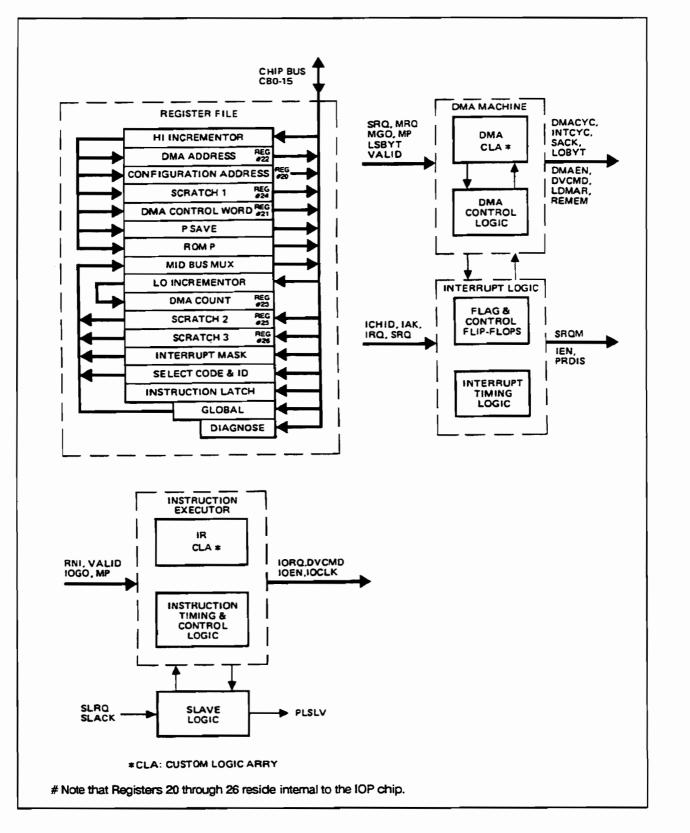

| I/O Processor (IOP) Chip                                    | 4-1  |

| Timing and Control Logic                                    | 4-2  |

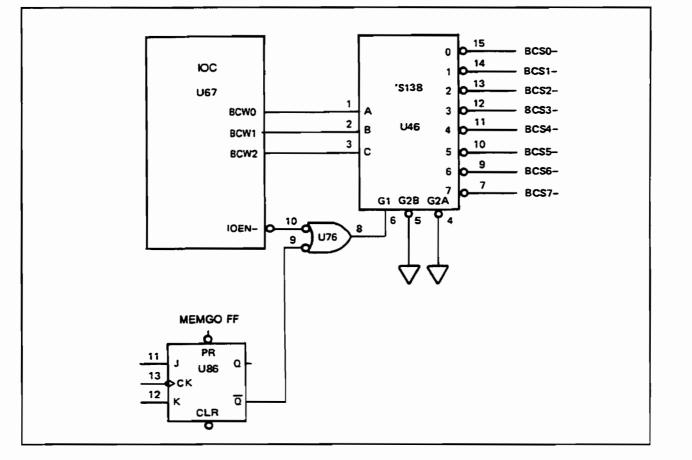

| Bus Control Logic                                           | 4-2  |

| Bus Drivers and Receivers                                   | 4-2  |

| Slave and Handshake Logic                                   | 4-2  |

| Interrupt Logic                                             | 4-3  |

| Memory Request Logic                                        | 4-3  |

| I/O Master Circuit Description                              | 4-6  |

| Signal Names and Mnemonics                                  | 4-6  |

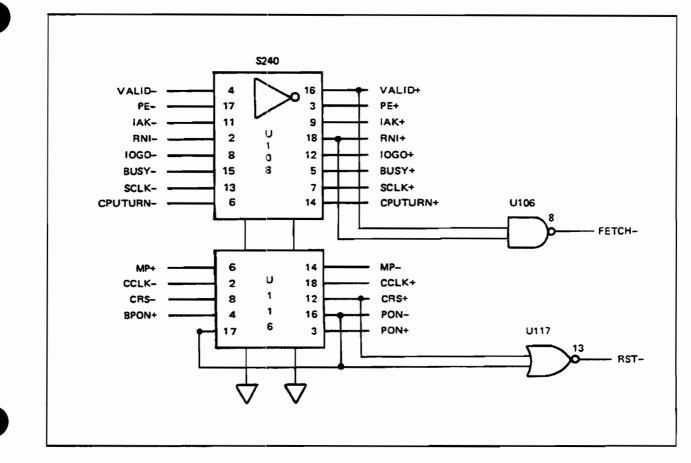

| Timing and Control Signals                                  | 4-0  |

| Timing and Control Signals                                  | 4-0  |

|                                                             |      |

| RST-                                                        | 4-7  |

| Bus Control Logic                                           | 4-7  |

| Bus Drivers and Receivers                                   | 4-7  |

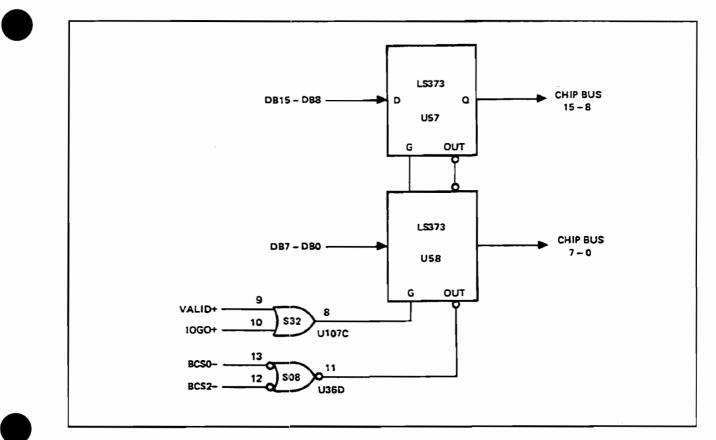

| Data Bus Receiver/Latch                                     | 4-7  |

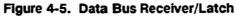

| Data Bus Driver                                             | 4-8  |

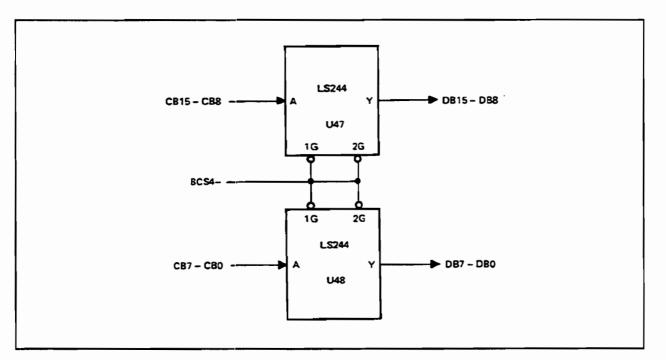

| Select Code and Board ID Driver                             | 4-8  |

| Address Drivers                                             | 4-8  |

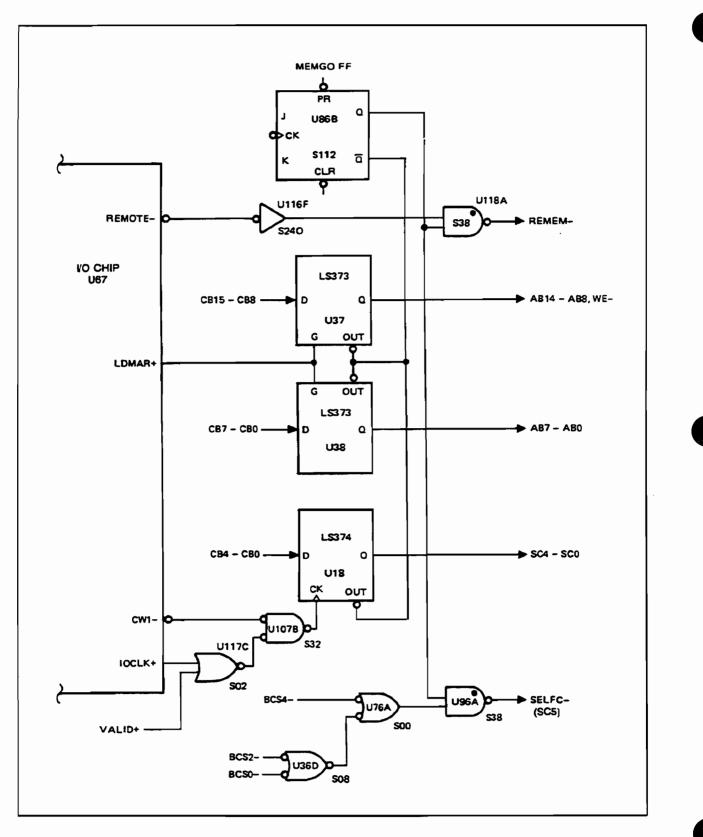

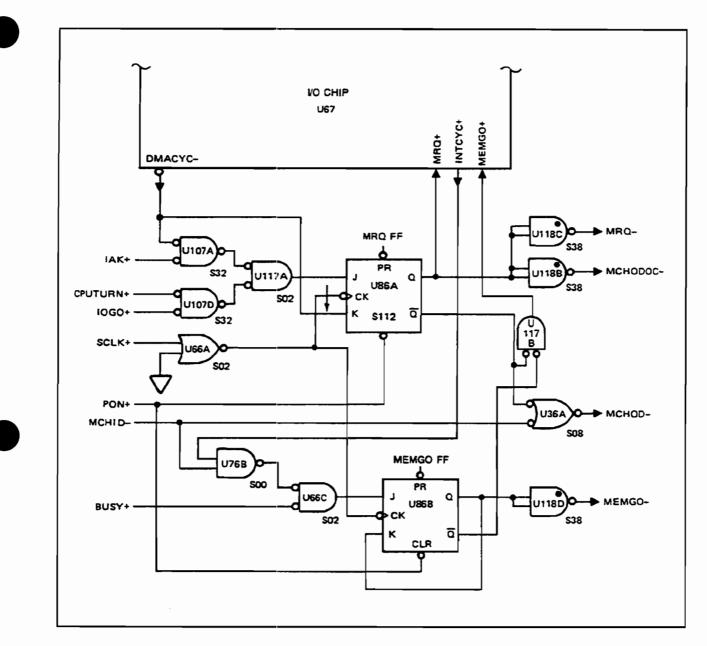

| Memory Request Logic                                        | 4-9  |

| DMA Memory Requests                                         | 4-9  |

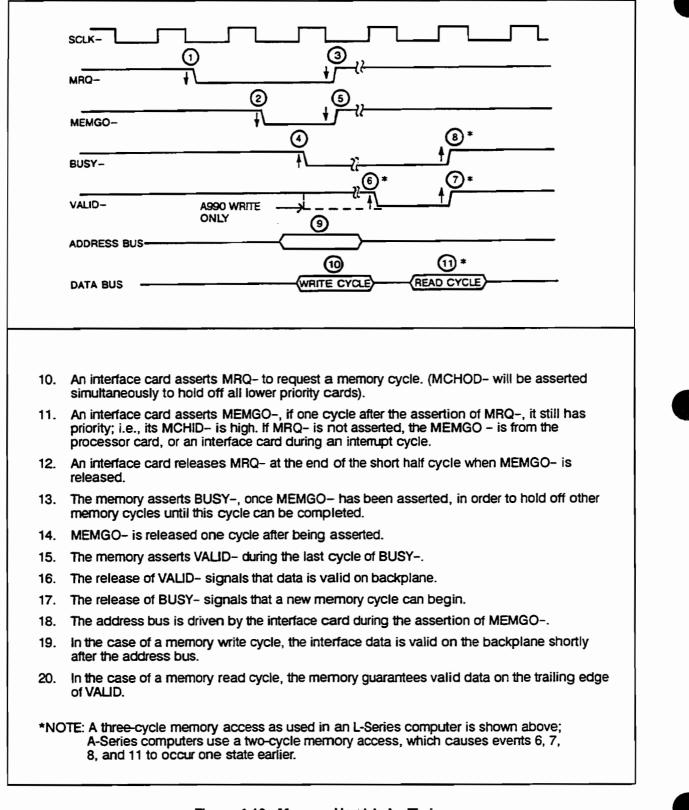

| Memory Cycle Initiation                                     | 4-12 |

| Memory Handshake Timing                                     | 4-12 |

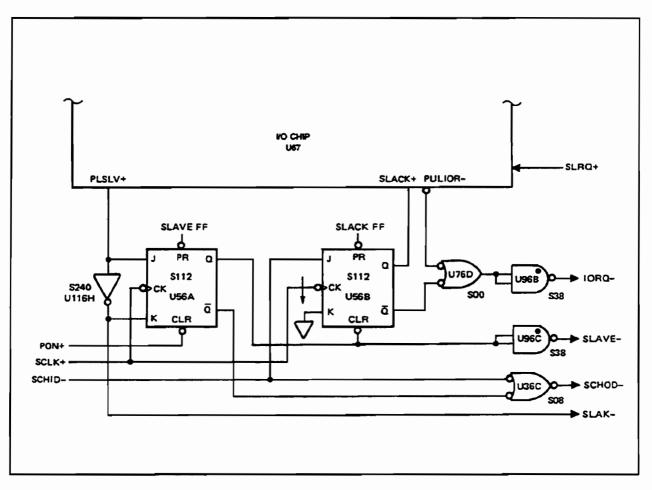

| Slave and Handshake Logic                                   | 4-12 |

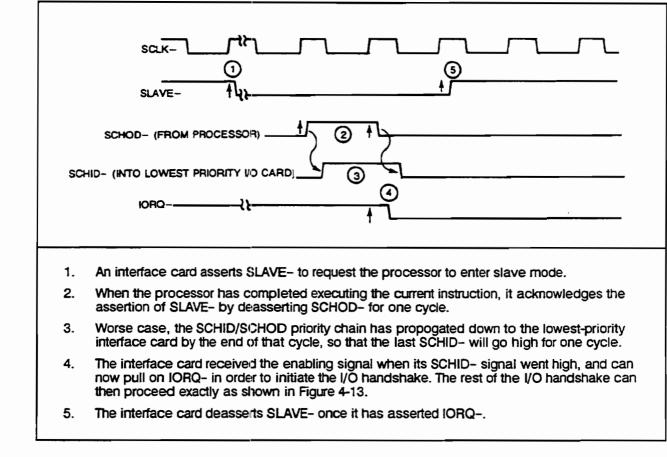

| Slave Sequence                                              | 4-12 |

| Slave Mode Timing                                           | 4-13 |

| I/O Instruction Handshake Logic                             | 4-13 |

| I/O Handshake Timing                                        | 4-13 |

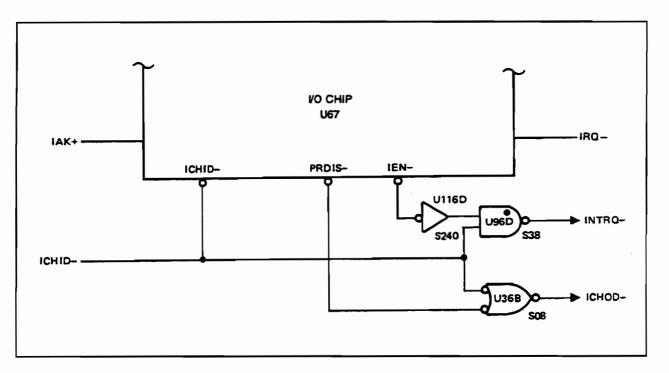

| Interrupt Logic                                             | 4-17 |

| Interrupt Signal Description                                | 4-17 |

| Interrupt Timing                                            | 4-17 |

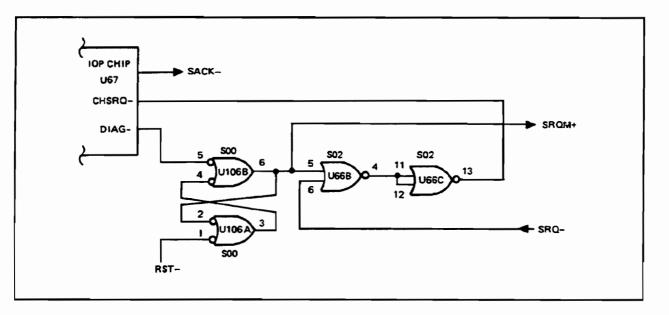

| Service Dequest and Mack Logic                              | 4-17 |

| Service Request and Mask Logic                              |      |

| Reset Signals                                               | 4-21 |

| I/O Master Diagrams                                         | 4-21 |

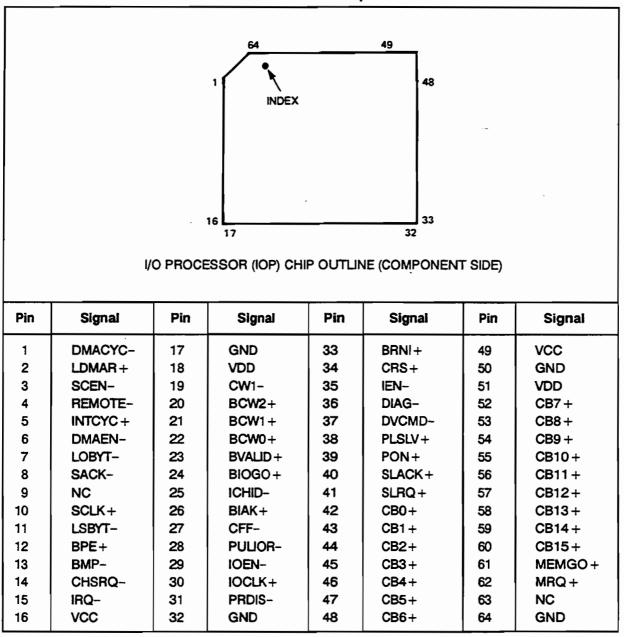

| I/O Processor Chip Signal Definitions                       | 4-21 |

| I/O Master-To-Device Interface                              |      |

| Backplane Clocks                                            | 4-21 |

| Switch Options                                              | 4-24 |

| Input Signals                                               | 4-24 |

| Output Signals                                              | 4-24 |

| Signal Timing Specifications and Waveforms                  | 4-25 |

| Output Timing Specifications                                | 4-25 |

| Timing Diagrams                                             | 4-25 |

| Timing Diagrams<br>Designing an Interface to the I/O Master | 4-25 |

| I/O Interface Design                                        | 4-35 |

| Input Requirements                                          | 4-43 |

| DMA Rate Calculation              | 4-43 |

|-----------------------------------|------|

| I/O Interface Card Specifications | 4-44 |

| Capacitive Loading                | 4-68 |

| Initial Design Considerations     | 4-68 |

| Development Checklist             | 4-69 |

## List of Illustrations

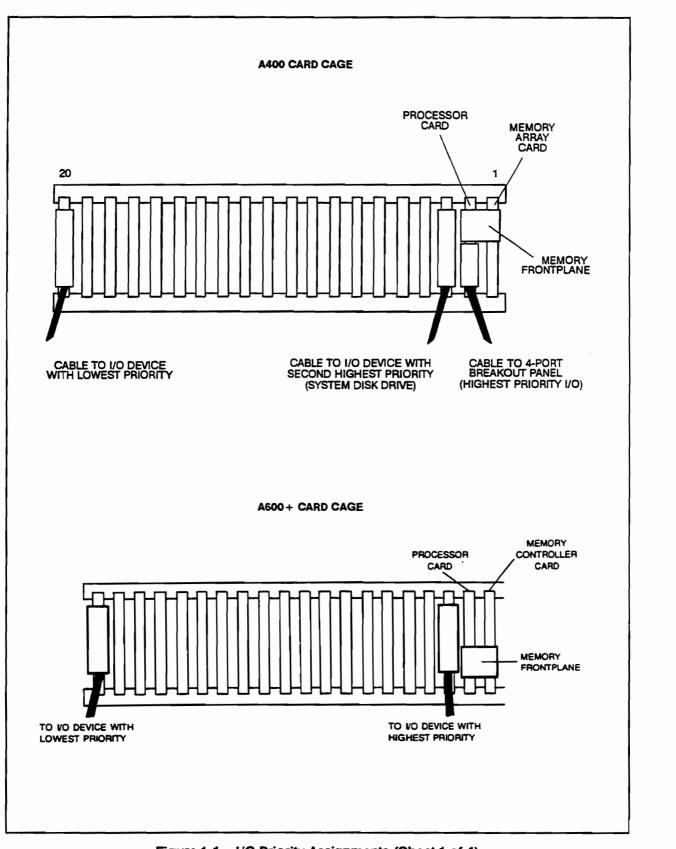

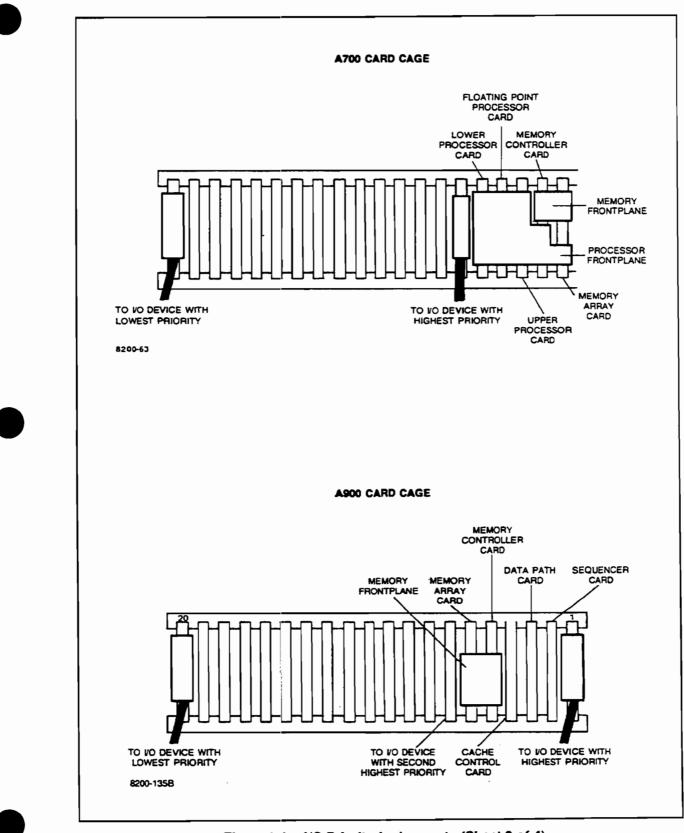

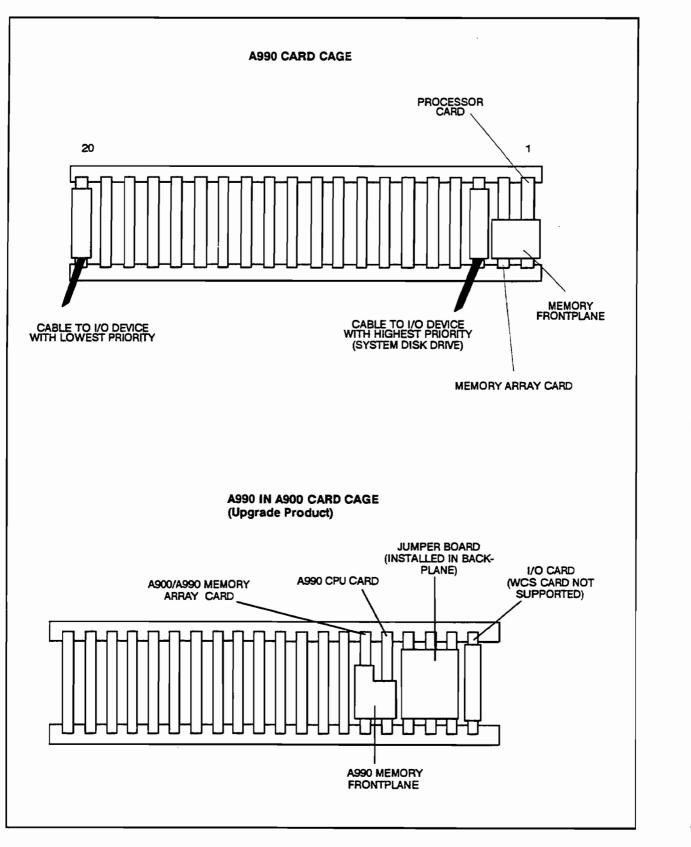

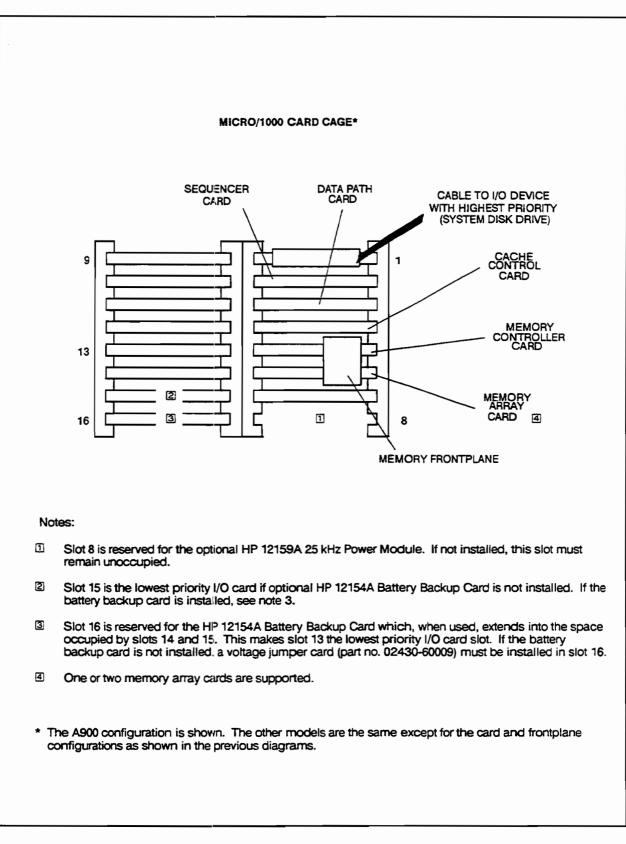

| Figure 1-1. | I/O Priority Assignments (Sheet 1 of 4)          | 1-6  |

|-------------|--------------------------------------------------|------|

| Figure 1-2. | Priority Linkage (simplified)                    | 1-11 |

| Figure 1-3. | Interrupt Sequences                              | 1-12 |

| Figure 1-4. | Software/Hardware Interface                      | 1-22 |

| Figure 1-5. | I/O Interface Layout                             | 1-23 |

| Figure 2-1. | General Bit Definitions for Control Word 1       | 2-19 |

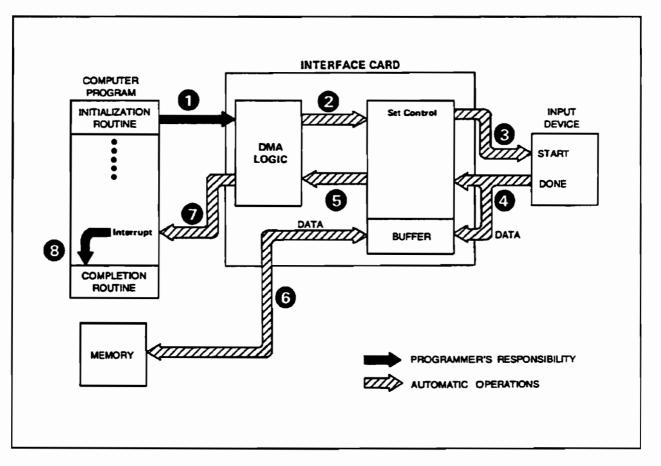

|             | Standard DMA Input Transfer                      |      |

| Figure 2-3. | DMA Self-Configuration Feature                   | 2-21 |

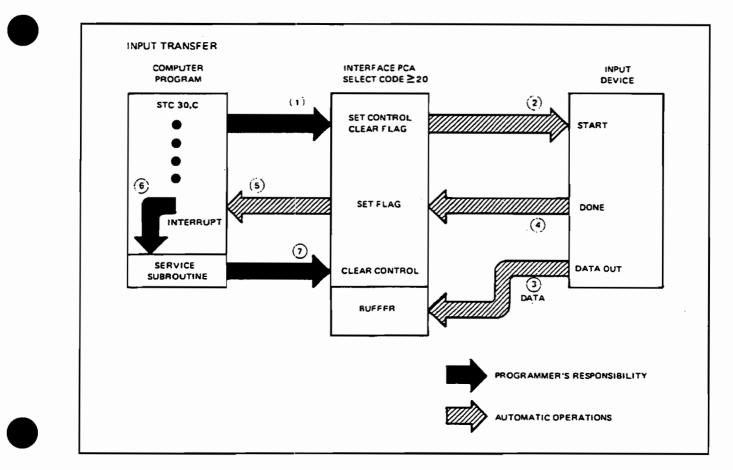

| Figure 2-4. | Input Data Transfer (Interrupt Method)           | 2-23 |

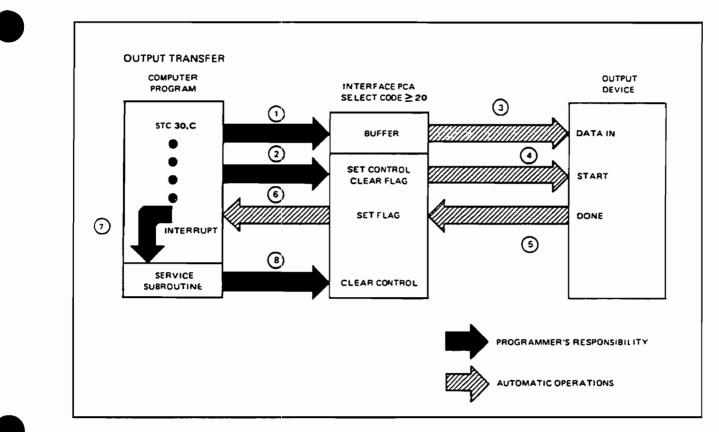

| Figure 2-5. | Output Data Transfer (Interrupt Method)          | 2-27 |

|             | I/O Master Simplified Block Diagram              |      |

| Figure 4-2. | I/O Processor Chip Block Diagram                 | 4-4  |

| Figure 4-3. | Timing and Control Signals                       | 4-9  |

| Figure 4-4. | Bus Control Logic                                | 4-10 |

| Figure 4-5. | Data Bus Receiver/Latch                          | 4-11 |

| Figure 4-6. | Data Bus Driver                                  | 4-11 |

| Figure 4-7. | Select Code and ID Driver                        | 4-13 |

|             | Address Drivers                                  |      |

| Figure 4-9. | Memory Request Logic                             | 4-15 |

|             | . Memory Handshake Timing                        |      |

| Figure 4-11 | . Slave and Handshake Logic                      | 4-18 |

| Figure 4-12 | . Slave Mode Timing                              | 4-19 |

| Figure 4-13 | . I/O Handshake Timing                           | 4-20 |

|             | . Interrupt Logic                                |      |

|             | . Interrupt Timing                               |      |

| Figure 4-16 | . Service Request Mask Logic                     | 4-24 |

| Figure 4-17 | . I/O Master Block Diagram                       | 4-27 |

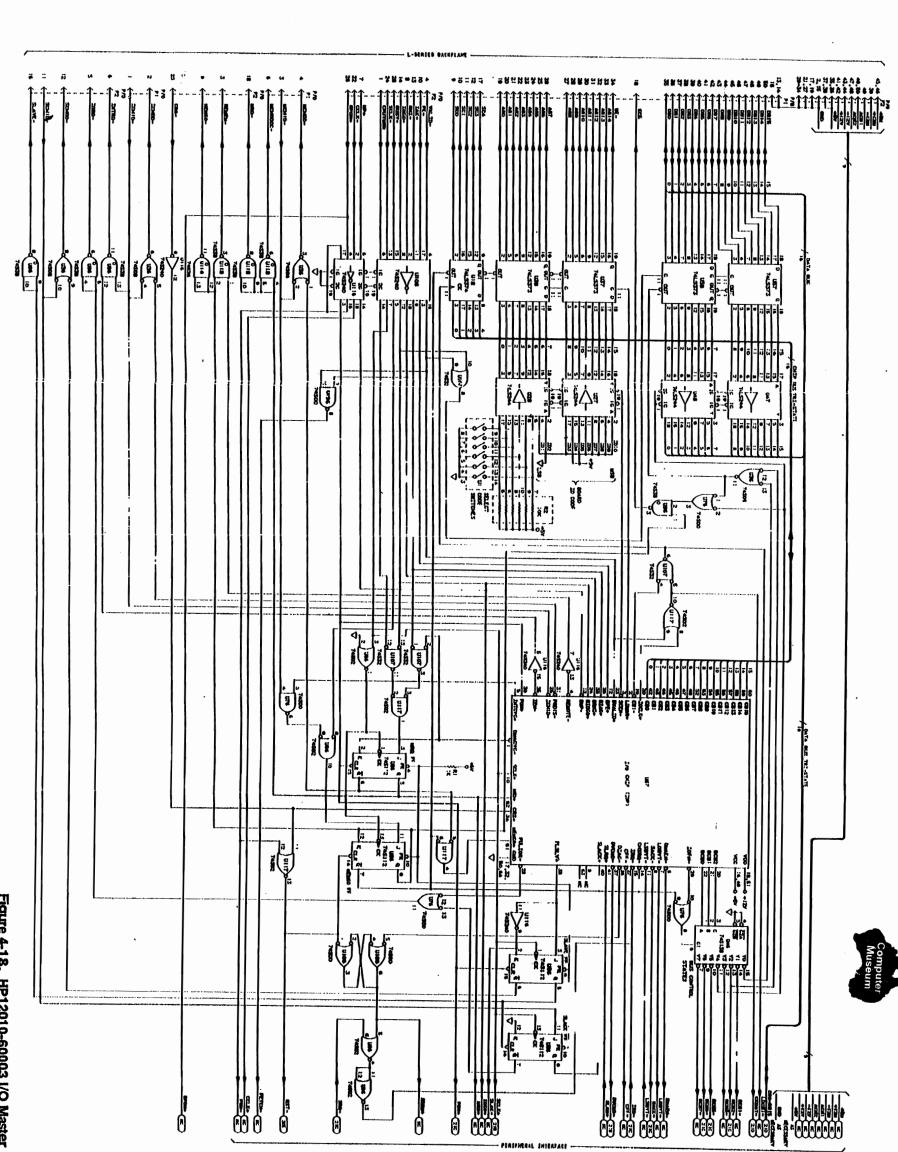

| Figure 4-18 | . HP12010-60003 I/O Master Schematic Diagram     | 4-29 |

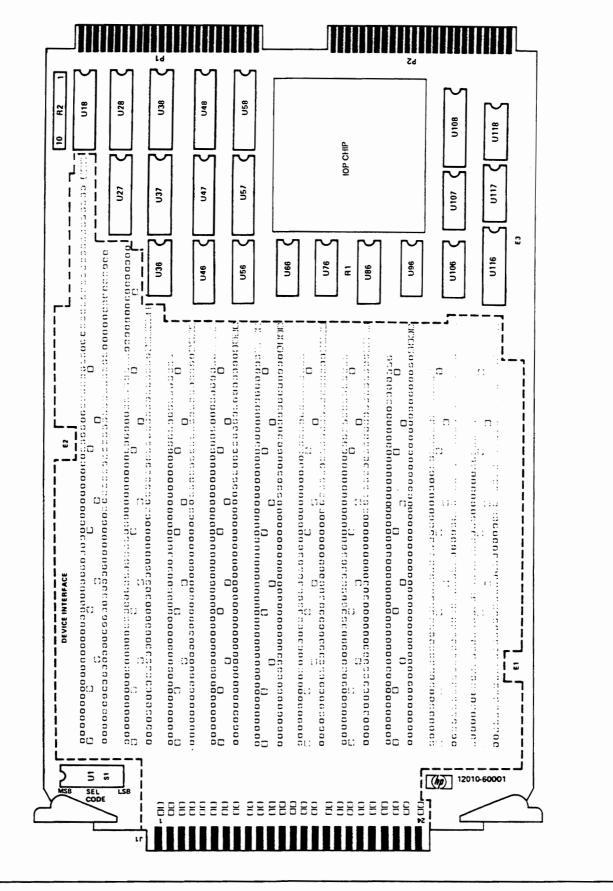

|             | . HP 12010-60003 I/O Breadboard Assembly         |      |

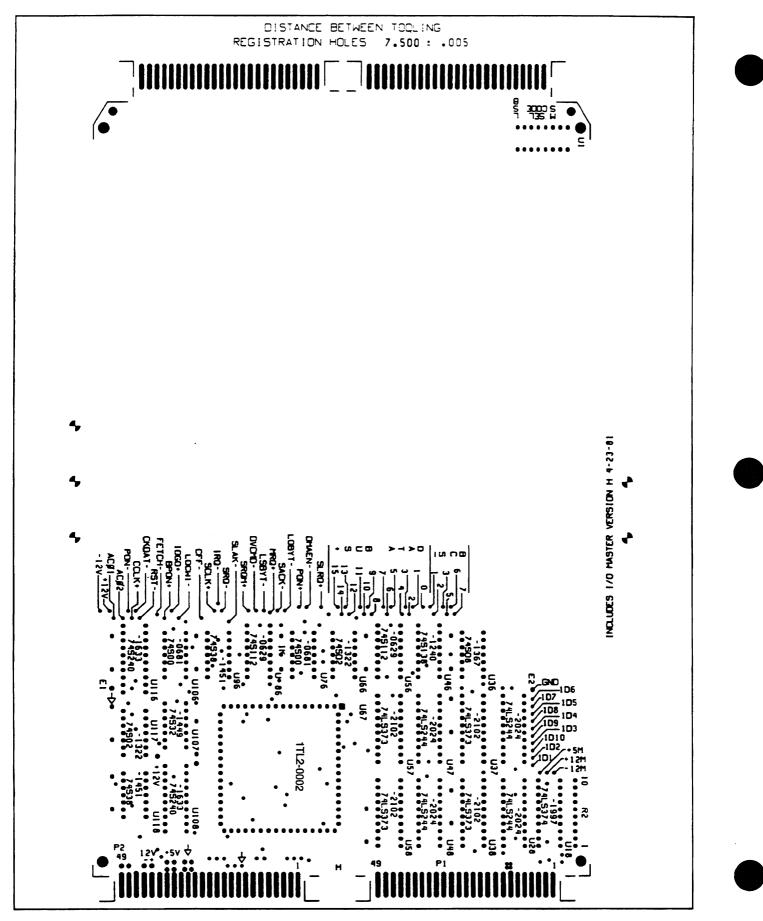

| Figure 4-20 | . HP 12010-60003 I/O Breadboard Probe Points     | 4-32 |

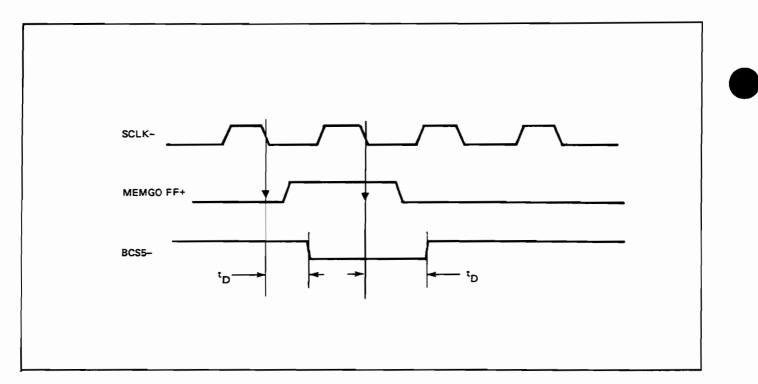

| Figure 4-21 | . BCS Timing – I/O Handshake                     | 4-59 |

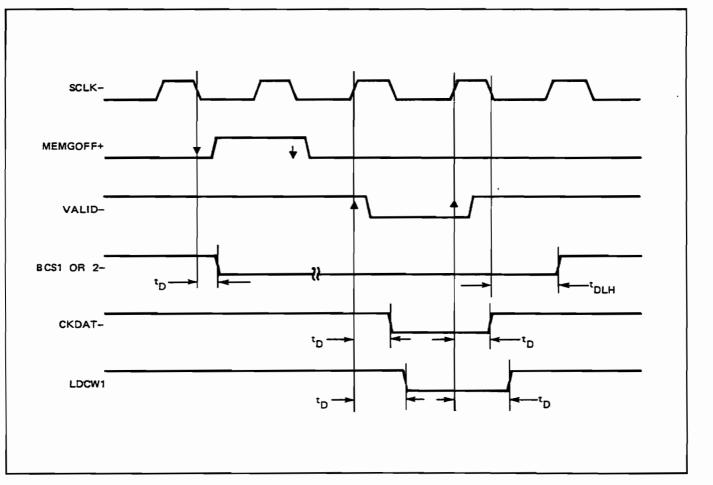

| Figure 4-22 | . BCS Timing - DMA input                         | 4-60 |

| Figure 4-23 | . BCS Timing - DMA Output and Self-Configuration | 4-60 |

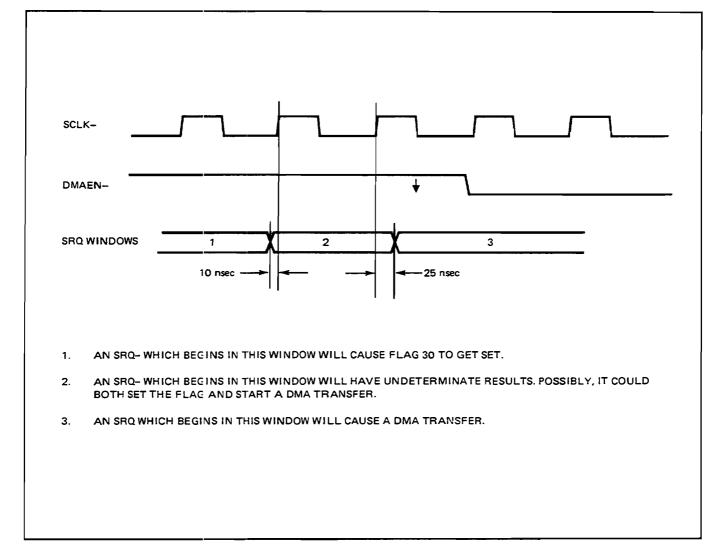

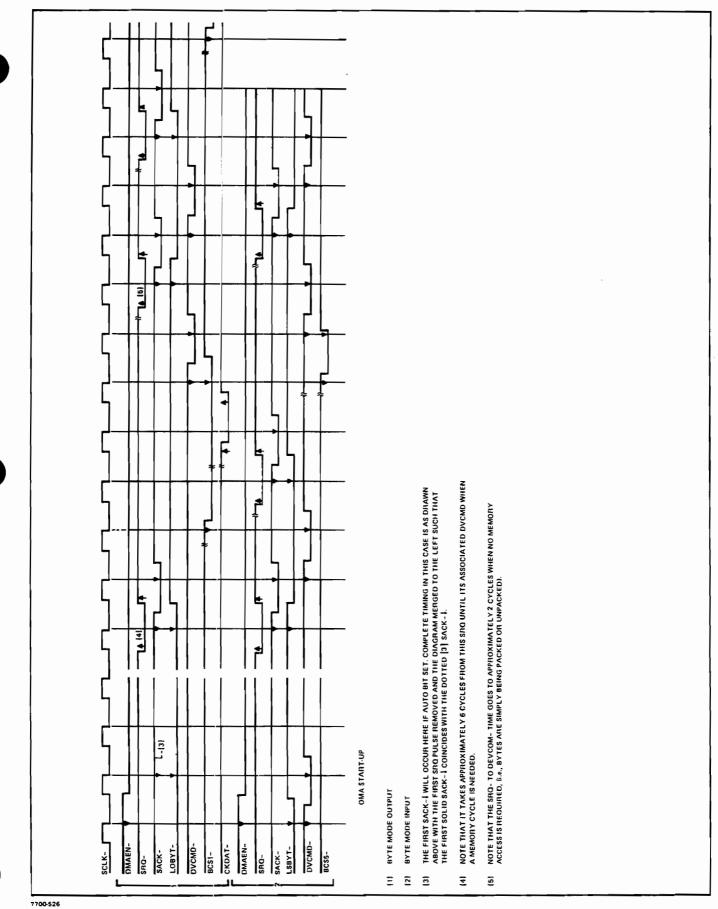

| Figure 4-24 | . SRQing on DMA Start-Up                         | 4-61 |

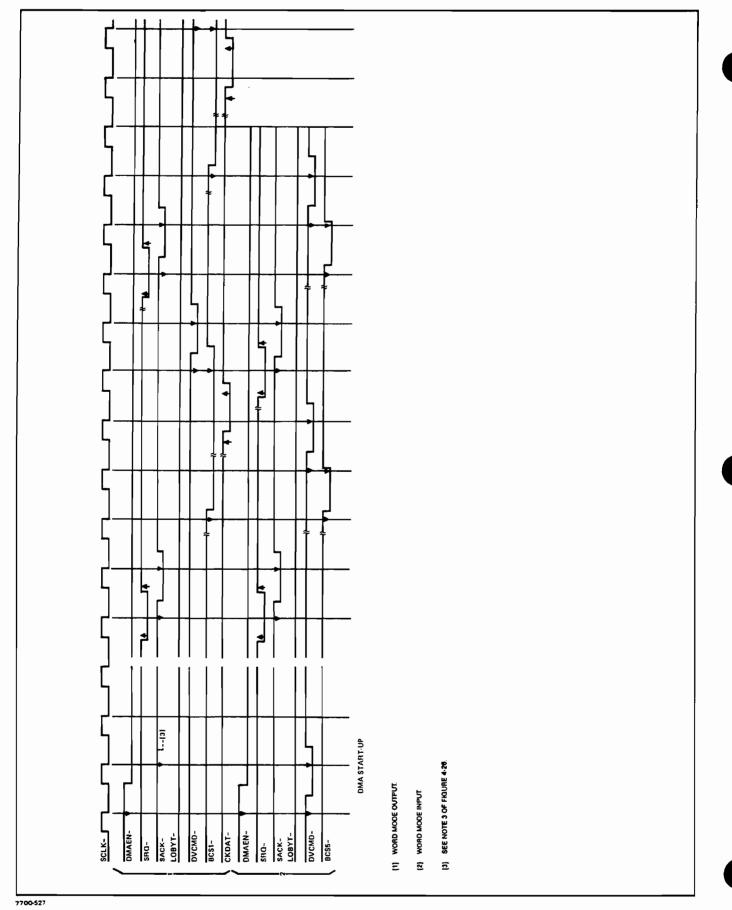

| Figure 4-25 | . Low-Speed DMA Transfers – Word Mode            | 4-62 |

|             | . Low-Speed DMA Transfers – Byte Mode            |      |

| Figure 4-27 | . Full Speed DMA In Progress                     | 4-64 |

| Figure 4-28 | . DMA Termination - Word Mode                    | 4-65 |

| Figure 4-29 | . DMA Termination – Byte Mode (Sheet 1 of 2)     | 4-66 |

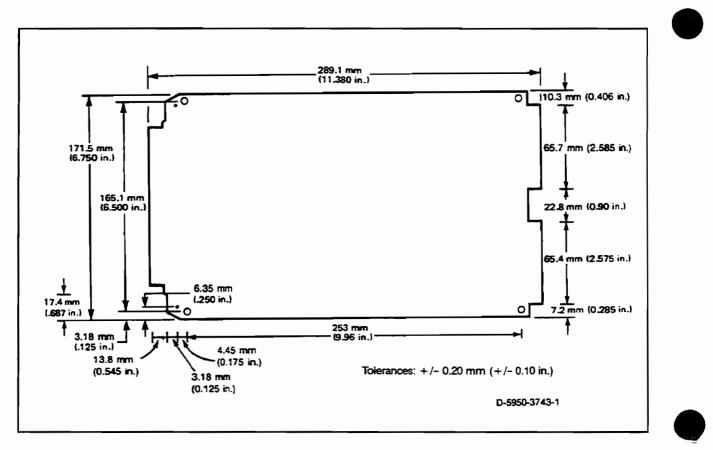

| Figure 4-30 | A-Series I/O Card Dimensions                     | 4-70 |

## Tables

|                    | Functional Specifications for A-Series Computers | 1-17 |

|--------------------|--------------------------------------------------|------|

| Table 1-2.         | I/O Interfacing Related Reference Manuals        | 1-26 |

| Table 2-1.         | IOP Chip Instructions By Select Code             | 2-11 |

| <b>Table 3-1</b> . | Manuals for A-Series I/O Cards                   | 3-3  |

| Table 4-1.         |                                                  | 4-5  |

| Table 4-2.         | Bus Control States                               | 4-10 |

| Table 4-3.         | HP 12010-60003 I/O Master Material List          | 4-33 |

| Table 4-4.         | I/O Processor Chip Pin Definitions               | 4-34 |

| Table 4-5.         | I/O Processor Chip Signal Definitions            | 4-36 |

|                    | Signal Definitions – I/O Master/User Interface   | 4-45 |

|                    | Definitions of Terms Used in Timing Diagrams and |      |

|                    | Timing Specifications                            | 4-52 |

| Table 4-8.         | BCS- Timing Specifications                       | 4-55 |

| Table 4-9.         | CCLK- Timing Specifications                      | 4-55 |

| Table 4-10.        | CFF- Timing Specifications                       | 4-55 |

|                    | CKDAT- Timing Specifications                     | 4-55 |

| Table 4-12.        | DB0-DB15* Timing Specifications                  | 4-56 |

| Table 4-13.        | DMAEN- Timing Specifications                     | 4-56 |

| Table 4-14.        | DVCMD- Timing Specifications                     | 4-56 |

| Table 4-15.        | FETCH- Timing Specifications                     | 4-56 |

| Table 4-16.        | IRQ- Timing Specifications                       | 4-57 |

| Table 4-17.        | LDCW1- Timing Specifications                     | 4-57 |

| Table 4-18.        | LOBYT- Timing Specifications                     | 4-57 |

| Table 4-19.        | LSBYT- Timing Specifications                     | 4-57 |

| Table 4-20.        | MRQ + Timing Specifications                      | 4-57 |

|                    | PON + Timing Specifications                      | 4-57 |

| Table 4-22.        | RST- Timing Specifications                       | 4-58 |

| Table 4-23.        | SACK- Timing Specifications                      | 4-58 |

| Table 4-24.        | SCLK + Timing Specifications                     | 4-58 |

| Table 4-25.        | SLRQ + Timing Specifications                     | 4-58 |

| Table 4-26         | SRQ- Timing Specifications                       | 4-58 |

|                    | SRQM + Timing Specifications                     | 4-59 |

|                    |                                                  |      |

## Introduction

The HP 1000 A-Series Computers are LSI-based computers designed for users who require a low-priced computer that combines powerful computational capability with efficient Input/Output (I/O) processing. This chapter contains a general discussion of the HP 1000 A-Series Computer's operation and architecture, functional specifications, and interfacing requirements.

## **Computer Overview**

The A-Series Computers comprise a central processor, memory, one or more input/output interface cards, and a power supply and backplane. The central processor (CPU) and I/O interfaces share control of the backplane and memory. The CPU and the I/O processor (IOP) chip have a master-slave relationship so that at any given time either the CPU or a single IOP is master of the bus and the other is a slave.

The backplane comprises a data bus, a memory address bus, and a control bus. The data bus holds data as it is being transferred between memory, the central processor and I/O interfaces. The address bus holds the address of the location to be referenced in memory. Either the central processor or the I/O chips may drive the address bus. The data bus is 16 bits wide, whereas the address bus is 20 bits wide; both buses are TTL compatible, and driven by tri-state logic.

## A400 Computer

The A400 Computer is a single-board computer that consists of a CPU, memory controller, 512K bytes of parity memory, and an asynchronous serial I/O multiplexer, all on a single printed-circuit assembly. The A400 board plugs into a 6-slot, 14-slot, or 20-slot A-Series box with up to four parity memory arrays and as many standard A-Series I/O cards as the box will support. Most of the central processor unit (CPU) circuitry resides on a single CMOS chip.

All I/O instructions are executed by a custom input/output processor (IOP) chip that is part of the on-board I/O (OBIO) circuitry on the A400 board. The OBIO cable provides four 25-pin RS-232 serial I/O connections.

## A600 and A600 + Computer

The A600/A600 + Computer design utilizes microprogrammed bit-slice chips in the CPU. The basic A600/A600 + computer (excluding I/O interface cards and expanded memory) consists of two printed circuit cards: a central processor card, and a memory controller card that includes either 512K or 1M bytes of dynamic RAM. The memory may be expanded up to 32M bytes by the addition of one to four memory array cards. (The A600 computer has been discontinued by HP and is discussed in this manual for reference only.)

The control logic is implemented as a microprogram contained in a PROM control store of 1024 56-bit microinstruction words. Decoding of 16-bit assembly language instructions is done by PROMs, which contain the entry point addresses in the control store associated with every defined opcode.

The memory accessing logic in response to control signals from the instruction decode logic arbitrates DMA versus processor contention for memory as well as generating the appropriate backplane signals for instruction fetching. The interrupt processing logic collects interrupt requests from various system and I/O level sources. An interrupt vector generator decides which interrupt is serviceable by passing a microcode entry point to the microprogram sequencer. This causes a microcode branch to the service routine for that interrupt.

The I/O accessing logic primarily participates in the IORQ/IOGO handshake protocol as used in all A-Series computers. It generates all of the necessary signals to send or receive data over the backplane or to freeze the micromachine if conditions do not permit the microcode to proceed further. One category of I/O instructions (STC/ CLC or STF/CLF) affects only the IOP, whereas the second category (SFS/C, LIA/B, MIA/B, or OTA/B) requires interaction with the CPU to modify the program counter or to access or modify the A/B-Register. The CPU during initial fetch of an I/O instruction determines if handshaking is required. An I/O state machine generates the necessary signal timing for communication over the backplane. For slave processing, I/O handshake protocol is used after the initial interrupt has been serviced.

A600 + computers are available with either of two memory systems. The standard memory system is based on a 512K-byte memory controller card, while the alternate memory system uses a 1M-byte memory controller. Main memory in either system may be expanded by the addition of up to four memory array cards, each having 512K, 1M, 2M, 4M, or 8M bytes of dynamic RAM with single-bit parity.

## A700 Computer

The A700 Computer is a fully microprogrammable machine that uses bit-slice chips in the CPU and uses the A-Series distributed intelligence I/O system. The A700 computer consists of two processor cards, a memory controller card, from one to four memory array cards, and a floating point processor card. Data and addresses are exchanged between the computer cards over frontplane buses and the backplane links the computer cards, the I/O system cards, and power supply. The control store resides on the lower processor card (base instruction set), on the floating point processor card (instruction set enhancements), and optional writable control store or PROM control store cards. (The A700 computer has been discontinued by HP and is discussed in this manual for reference only.)

In operation, assembly language instructions are translated through a look-up table into addresses in the 16k 32-bit word control store. The microinstructions from the control store are translated into control signals by microinstruction decode logic. The base instruction set (2k 32-bit words) of the control store resides on the lower processor board and the upper processor card contains the memory and L/O access logic.

The CPU generates low select-code system level interrupts such as memory protect, time base generation, and unimplemented instruction interrupt; logic is provided for detecting other system level functions such as power fail/ auto restart and parity error interrupt.

The A700 memory system consists of a memory controller card and up to four memory array cards.

## A900 Computer

The A900 computer features a high-speed microprogrammed control processor that resides on four cards called the sequencer, data path, cache control, and memory controller. The high speed is achieved through "pipelining" of the next instruction sequence and a cache memory to speed up memory accesses. The A900 uses the same distributed intelligence concept as the other A-Series computers that separates the processing of I/O instructions from that of other instructions.

Data and addresses are exchanged between the memory controller and memory array card or cards over a frontplane. If a control store card is installed, there is a separate frontplane going between the control store and sequencer cards. The backplane links the computer card, the I/O system cards, and power supply. The internal control store resides on the sequencer card and an optional control store card includes 4k words of writable control store and 2k words PROM control store. Arithmetic and floating point functions are contained on the data path card. Each microword is 48 bits wide.

The computer is always under microprogram control and executing microinstructions when power is applied. Assembly language instructions are translated through a look-up table with pointers to microroutines in control store that implement the instructions. There are 6k words of ROM storing the A900 base set.

Most of the input/output logic resides on the cache card and the macrointerrupt logic is on the memory controller card. The CPU generates low select-code interrupts such as memory protect, time base generation, multi-bit error, and unimplemented instruction. Logic is provided for detecting other system functions such as power fail/auto restart and parity error interrupt.

The A900 memory system consists of a memory controller and up to eight memory array cards.

## A990 Computer

The A990 Computer is a single-board processor and is the fastest HP 1000 Computer. Pipeline technology with two-level cache memory, boosted even more by a fast built-in hardware floating point processor having both scientific and vector instruction sets in firmware, provides unmatched computational speed. The A990 design is based on the A900 Computer but uses proprietary

application-specific integrated chips (ASICs) to greatly improve overall performance. With 3/4-Mbyte, 3-Mbyte, and 8-Mbyte Error Correcting Code (ECC) memory cards available, and card cage space for up to four memory cards, the A990 memory can be a total of up to 32 Mbytes.

## **A-Series Backplane**

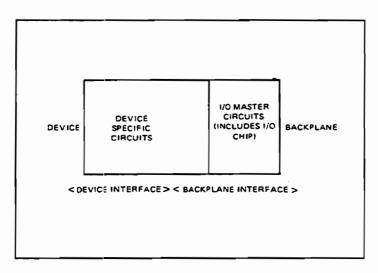

The backplane provides the link between the central processor, memory, interface cards, and power supply. It is a printed circuit card on which the traces distribute the power, ground, and interconnecting signals between all the cards in an A-Series Computer. The backplane is the hardware communications link between all cards in the system. Communication with a device interface is handled by the I/O Master. This I/O Master circuitry located on every A-Series interface card serves to standardize the I/O interface to the backplane. This frees the I/O designer from the details of interfacing to the backplane and allows concentration on the device specific interface design. -

## I/O System

The A-Series I/O system allows data to be transferred between a computer and external devices either through the central processor A- and B-Registers (programmed I/O) or directly to memory (direct memory access). The external device itself may be physically located on the interface, such as the PROM Storage Module. The I/O interface logic has been optimized for direct memory access (DMA) data transfers. Once this DMA logic, which is included on every interface, has been initialized, no further programming is involved and the transfer to or from memory is automatically handled by the interface. This transfer occurs in two distinct steps as follows:

- a. Between the external device and its I/O interface in the computer.

- b. Between the I/O interface and memory via the backplane data bus.

An output transfer uses the same process except, in reverse order.

Data may be transferred under program control without using the DMA capability. This type of transfer allows the computer to manipulate the data during the transfer process. A programmed I/O input transfer is a three step process as follows:

- a. Between the external device and its I/O interface.

- b. Between the I/O interface and the A- or B-Register via the data bus and the central processor.

- c. Between the A- or B-Register and memory via the processor and the data bus.

Note that during a DMA transfer the central processor is bypassed. Since a DMA transfer eliminates programmed steps that load data into the A- and B-Registers and store the data directly into memory, the DMA transfer time is very short. Thus the DMA capability is especially useful with high-speed devices that may transfer data at rates up to 3.9 megabytes per second

(A700), 3.7 megabytes per second (A900), 4.0 megabytes per second (A990), or 4.3 megabytes per second (A400/A600 + ). DMA transfers also eliminate time consuming processor interrupts that are associated with each programmed I/O data transfer. A self-configuration feature of the I/O Master (to be discussed later) further reduces the processor interrupts by allowing the next DMA transfer to fetch its set of control words directly from memory, to reconfigure and enable itself automatically.

## I/O Addressing

As shown in Figure 1-1, an external device is connected by cable directly to an I/O interface located in the computer mainframe. The I/O interface, in turn, plugs into one of the input/output slots in the backplane. Note, however, that the select code (I/O address) of each I/O interface is independent of its priority. The computer communicates with a specific device on the basis of its select code, which is set by switches on the I/O interface.

Figure 1-1 shows an I/O interface inserted in the I/O slot having the highest priority (in the A900 this I/O card may be replaced with the control store card). If it is decided that the associated device should have lower priority, its I/O interface and cable may simply be exchanged with those occupying some other I/O slot. This will change the priority but not the I/O address (select code). Due to priority chaining, there can be no vacant slots from the uppermost memory card slot to the lowest priority slot used. Only select codes 20 through 77 (octal) are available for I/O interfaces; the lower select codes (00 through 17) are reserved.

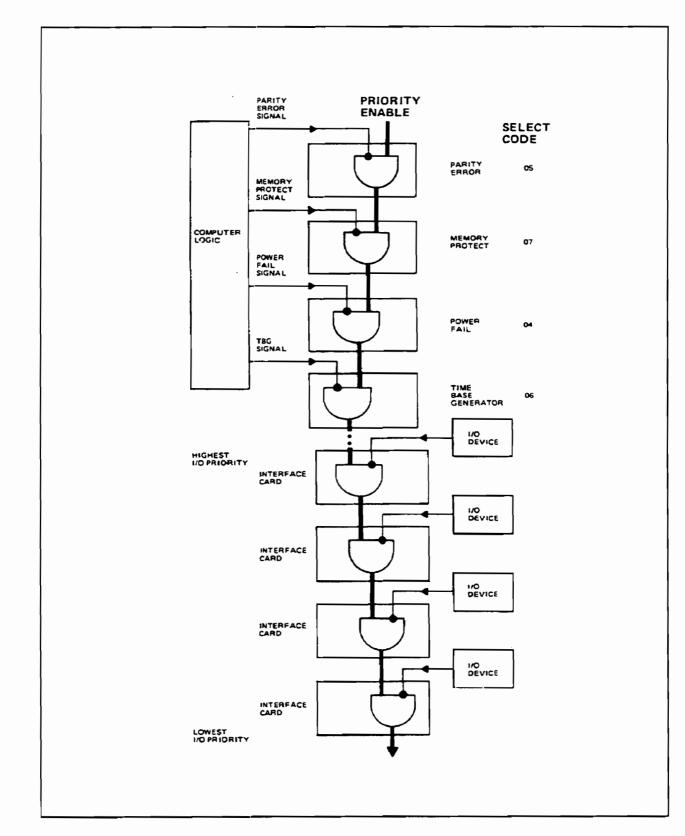

Figure 1-1. I/O Priority Assignments (Sheet 1 of 4)

Figure 1-1. I/O Priority Assignments (Sheet 2 of 4)

#### I/O Priority

The plug-in card slots of the A-Series computers are numbered consecutively from top to bottom (starting in the right side if there are two columns) for those configurations with horizontal slots or from right to left with vertical slots. Generally, memory occupies the highest priority slots, then the central processor and remaining slots are available for I/O interfaces. The slot immediately following the Processor card will have the highest I/O interrupt priority except for the A900 processor where the first I/O slot is immediately above the sequencer card, unless it is occupied by a control store card.

When an input/output device is ready to be serviced, it causes its I/O interface to request an interrupt so that the computer will interrupt the current program and service the device. Since many device interfaces may request service at random times, it is necessary to establish an orderly sequence for granting interrupts. Also, it is desirable that high-speed devices should not have to wait for low-speed device transfers. Both of these requirements are met by a series-linked priority structure, illustrated by Figure 1-2. The bold line, representing a priority enabling signal, is routed in series through each card. The card cannot interrupt unless this enabling signal is present at its input.

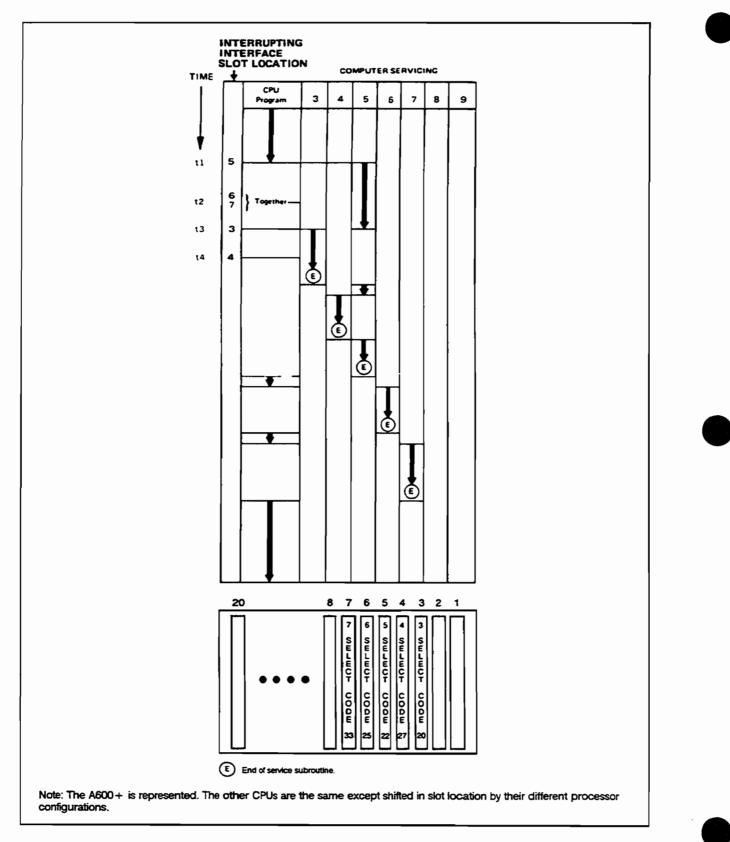

Each device (or other interrupt function) can break the enabling line when it requests an interrupt, by pulling its signal line low. If two devices simultaneously request an interrupt, the device with the highest priority will be the first one that can interrupt because it has broken the enable line for the lower-priority device. The other device cannot begin its service routine until the first device is finished. However, a still higher-priority device (one interfaced through a lower-numbered slot) may interrupt the service routine of the first device. Figure 1-3 illustrates a hypothetical case in which several devices request service by interrupting a CPU program. Both simultaneous and time-separated interrupt requests are considered.

Assume that the computer is executing a program when an interrupt from the I/O interface located in slot 5 occurs (at reference time t1), and that the card in slot 5 is assigned select code 22. With the I/O card supplying the select code to the address bus, a JSB instruction in memory location 22 causes a program jump to the service routine for the interface in slot 5 (select code 22). The JSB instruction automatically saves the return address (in a location which the programmer must reserve in the service routine) for a later return to the CPU program. The program counter is not affected by the interrupt and the subsequent execution of the JSB at location 22, so effectively the JSB is "inserted" into the program at whatever point the interrupt occurs. (The JSB is not physically inserted, so that later passes through the same section of code would not JSB to the interrupt routine unless another interrupt occurred.)

Figure 1-2. Priority Linkage (simplified)

.

Figure 1-3. Interrupt Sequences

The routine for select code 22 is still in progress when several other devices request service (set flag). First, interfaces in slots 6 and 7 (select codes 25 and 33) request simultaneously at time t2; however, as neither one has priority over the interface in slot 5, their flags are ignored and the routine for select code 22 continues executing. But at t3, a higher priority (select code 20) requests service. This request interrupts the select-code 22 routine and causes the select-code 20 routine to begin. The JSB instruction saves the return address for return to the select-code 22 routine.

During the transfer to the slot 3 interface's service routine, the flag on the interface in slot 4 (select code 27) is set (t4). Since it has lower priority than the interface in slot 3, the slot 4 interface must wait until the end of the select-code 20 routine. Because the select-code 20 routine when it ends contains a return address to the select-code 22 routine, program control temporarily returns to the select-code 22 routine, even though the waiting interface in slot 4 has higher priority. The JMP,I instruction used for the return inhibits all interrupts until after the next instruction is executed. At the end of this short interval, the select-code 27 interrupt request is granted.

When the select-code 27 routine is finished, control is returned to the select-code 22 routine, which at last has sufficient priority to complete its routine. Since the select-code 22 routine has been saving a return address to the main program, control returns to this program.

The two waiting interrupt requests from select codes 25 and 33 can now be considered. The interface in slot 6 has the higher priority and goes first. At the end of the select-code 25 routine, control is temporarily returned to the CPU program. Then the select-code 33 interface interrupts and completes its routine. Finally, control is returned to the CPU program, which resumes processing.

#### I/O Processing

In the A-Series, most of the I/O group instructions are not executed by the CPU chip or micromachine. Instead, they are executed by the IOP chip on the interface to which the instruction pertains. Instructions such as LIA, OTB, MIA, or that require the executor to read or modify some register in the CPU are executed using a special I/O access protocol. When an I/O interface determines that it should execute the instruction just fetched, it also decides if the execution will require interaction with the CPU. If the CPU is needed, the interface will request an I/O handshake over the backplane to the central processor. In the meantime, the central processor has determined that it is not responsible for the execution of the instruction, and has prepared itself for a possible I/O handshake request.

The CPU acknowledges the I/O handshake request after any active and pending DMA memory requests are complete. The interface that requested the handshake responds by driving a command word onto the data bus at the completion of the handshake.

For some instructions, such as skip, passing a command to the CPU is all that must be done. For instructions that require transfer of data, such as OTA or LIA, two handshakes are required. In the first handshake, the control word passed to the CPU tells it what to do for the second handshake. The control word will select the A- or B-Register and set the direction of the data transfer. The CPU will either write to or read from the data bus during the second handshake, while the I/O interface performs the opposite operation.

According to their execution requirements, I/O instructions may be broken down into three groups as follows:

a. Data Transfer I/O Instructions-OTA/B, LIA/B, MIA/B

This group requires a double handshake. In the first handshake, a control word is transferred from the I/O interface to the central processor. In the second handshake, the data is transferred either into or out of the A- or B-Register, according to which of the six instructions is being executed. I/O transfers over the backplane to the central processor have lower priority than DMA transfers, and can be preempted.

b. Status Sensing I/O Instructions-SFS, SFC

This group requires, at most, a single handshake during which a control word (signalling the CPU to increment P) is transferred from the I/O interface to the central processor. If no skip is required, no handshake occurs.

c. Status Altering Instructions-STC, CLC, STF, CLF

This group affects only the control or flag flip-flops on the I/O processor, and requires no interaction with the central processor.

#### **Slave Mode Transfers**

An I/O interface may force the central processor to enter the slave or Virtual Control Panel (VCP) mode. When the central processor is operating in slave mode, it is under control of the slave mode requestor, and thus the device connected to the requestor becomes a virtual control panel. As such, this device can initiate I/O transfers as described above in step a.

#### Interrupt Processing

The A-Series interrupt system allows an external, asynchronous event to obtain the attention of the central processor without the processor having to specifically check the status of the I/O interfaces periodically. On acknowledging an interrupt, control may pass directly to a routine that services the interrupt. This is especially useful for time-critical processes that must receive a quick response. The interrupt system allows the operating system to suspend the currently executing program, respond to the time-critical event, then resume processing the suspended program.

An interrupt request occurs when an interface control is set and the flag is set either by the device itself or by the execution of an STF instruction. This causes the interface to assert an interrupt-requesting signal on the backplane. An interrupt acknowledgement, from the central processor, is triggered by an interrupt request from any of the I/O interfaces. When the CPU is ready to fetch the next instruction, and if the interrupt system is enabled and interrupts are not temporarily being held off, then the central processor will assert an interrupt acknowledge signal.

Since interrupt servicing is accomplished with the aid of a memory cycle, the interrupt handshake timing is similar to that of a memory cycle. After the interrupt is acknowledged and memory is ready, the interface drives its select code on the address bus. The CPU then executes the instruction held in the memory location corresponding to the interrupting interface's select code. This instruction will normally be a JSB,I to the interrupt service routine. All such service routines

normally end with an XJMP indirect instruction to the beginning of the service routine, which will return the computer to the program that was executing when the interrupt occurred. For example, if the interrupting interface has select code 25, the CPU executes the instruction in memory location 25, which should hold a JSB,I to the service routine. When the interface requested an interrupt, it also issued a signal to disable all lower-priority interfaces from requesting interrupt service. If a higher-priority interface preempts the request, the lower priority requesting card will be disabled. The lower-priority interface should maintain its request until the disabling signal is terminated and the lower-priority interface can be serviced.

Note

In an A-Series computer, only JMP(,I) or JSB(,I) may be used in an interrupt trap cell.

The interrupt system flag (FLG0) is set and cleared under program control. It permits a programmer to specify which parts of a program may be interrupted for I/O and which may not.

#### Interface Elements

The I/O interface provides the communication link between the computer and one or more external devices. The I/O interface includes several basic elements, some of which either the computer or the device can control in order to effect the necessary communication. These basic elements are the Global Register, control flip-flop, flag flip-flop, data buffer register, card control register, and DMA control registers. DMA control registers are discussed in Chapter 2 under DMA.

#### **Global Register**

The A-Series computer utilizes a design feature called the "Global Register" for addressing interfaces. Every I/O interface card (serial interface, parallel interface, etc.) in the HP 1000 A-Series Computer System contains a Global Register. The Global Register is located in the IOP chip and is a six-bit register which contains a select code. The select code of a particular I/O interface is set by switches on that interface.

All Global Registers on all interface cards are controlled by the CPU, thus all Global Registers contain the same select code. (It is useful, therefore, to think of all the Global Registers as being one "global" register.) When the Global Register is enabled, any I/O instruction fetched by the CPU automatically applies only to the card whose select code matches the value stored into the Global Register. For example, if the Global Register is enabled and contains a value of 22, then the current I/O instruction is decoded and executed only by the interface with a select code of 22.

Using the Global Register to address I/O interfaces allows the six least significant bits of the I/O instruction to be used to address specific registers on the I/O interface cards. (These six bits are not needed for identification of the I/O interface to which the instruction applies since that is already taken care of by the Global Register.) For example, with the Global Register previously set to a value of 22, an OTA instruction with a value of 31 stored in the six least significant bits of the

instruction field would cause the contents of the A-Register to be output to register 31 of the I/O interface card having a select code of 22.

#### **Control Bits**

The control bits on an I/O interface are used to initiate I/O functions. In addition, a control bit must be set to allow the corresponding flag bit to cause an interrupt. There are three control bits associated with each I/O select code: control 20, 21, and 30. When control 30 is set, it generates an action command, allowing one word or character to be transferred to or from the data buffer. When control 20 is set, it turns on DMA self-configuration (refer to Chapter 2 under DMA). The setting of control 21 starts a DMA transfer.

#### **Flag Bits**

The flag bits, when set, are used primarily to interrupt or to signal task completion. Flag 30, the only flag accessible without using the Global Register, signals either one data element has been transferred or that an interrupting condition has been detected. There are five other flags. Flag 21 signals DMA transfer complete; flag 20 signals DMA self-configuring transfer complete; and flag 22 signals that a parity error occurred during a DMA memory access. The device cannot clear the flag bits. If the corresponding control bit is set and the interrupt system is enabled, then setting the flag bit will cause an interrupt to the location corresponding to the I/O interface's select code. Flag 23 is the logical OR of flags 20, 21, and 22. It is used to distinguish between DMA and I/O interrupts. If flag 23 is not set, the interrupt is not DMA related. Flag 24 may be used to determine whether DMA is enabled (set) or disabled (clear).

#### **Data Buffer Register**

The data buffer register (designated Register 30 by HP convention) is used for the intermediate storage of data during an I/O transfer. Typically, the data capacity is 16 bits. The data register is not part of the I/O Master, it must be designed into the user interface logic.

#### **Card Control Register**

The card control register (designated Register 31 by HP convention) enables a general purpose I/O interface to be configured for compatibility with a specific I/O device or to be programmed for particular modes of operation. The control register must be programmatically set up (GR enabled, OTA/B 31) for a particular application. The control register is not part of the I/O Master; it must be designed into the user interface logic.

## **Functional Specifications**

Table 1-1 lists the functional specifications for the A-Series computers.

| ARCHITECTURE             |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                         |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Туре:                    | Distributed intelligence<br>communicating with eac                                                                                                                                                                                                                                                                                                                                                   | Distributed intelligence with separate CPU and I/O Processors<br>communicating with each other and with memory via a single bus.                                                                                                        |  |  |  |

| Implementation:          | Microcoded with bipola                                                                                                                                                                                                                                                                                                                                                                               | r LSI and MSI hardware.                                                                                                                                                                                                                 |  |  |  |

| Data Path Width:         | 16 bits.                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                         |  |  |  |

| Bus Structure:           | Single backplane bus fo                                                                                                                                                                                                                                                                                                                                                                              | or memory, processor, I/O.                                                                                                                                                                                                              |  |  |  |

| Backplane Bus Speed:     | A600/A600 + : Up to 4.3<br>A700: Up to 3.9M bytes<br>A900: Up to 3.7M bytes                                                                                                                                                                                                                                                                                                                          | A400: Up to 4.3M bytes/sec.<br>A600/A600+: Up to 4.3M bytes/sec.<br>A700: Up to 3.9M bytes/sec.<br>A900: Up to 3.7M bytes/sec on inpur; up to 2.5M bytes on output.<br>A990: Up to 4.0M bytes/sec on input; up to 2.7M bytes on output. |  |  |  |

| Interrupt System:        | Vectored priority intern<br>in priority.                                                                                                                                                                                                                                                                                                                                                             | upt structure with the following assignments                                                                                                                                                                                            |  |  |  |

|                          | Select Code/<br>Memory Location                                                                                                                                                                                                                                                                                                                                                                      | Function                                                                                                                                                                                                                                |  |  |  |

|                          | 00005                                                                                                                                                                                                                                                                                                                                                                                                | Memory parity interrupt (A900/A990: mul-<br>tibit error)                                                                                                                                                                                |  |  |  |

|                          | 00010<br>00007<br>00004<br>00006<br>00011-00016<br>00020-00077                                                                                                                                                                                                                                                                                                                                       | Unimplemented instruction interrupt<br>Memory protect interrupt<br>Power fail interrupt<br>Time base generator interrupt<br>Reserved<br>I/O device interrupts                                                                           |  |  |  |

| CENTRAL PROCESSOR        |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                         |  |  |  |

| Accumulators:            | 2 (A and B), 16 bits ea<br>rnemory locations.                                                                                                                                                                                                                                                                                                                                                        | ach. Implicitly addressable, also explicitly as                                                                                                                                                                                         |  |  |  |

| Index Registers:         | 2 (X and Y), 16 bits ea                                                                                                                                                                                                                                                                                                                                                                              | ich.                                                                                                                                                                                                                                    |  |  |  |

| Supplementary Registers: | 2 (overflow and extend                                                                                                                                                                                                                                                                                                                                                                               | d), one bit each.                                                                                                                                                                                                                       |  |  |  |

| Power Fail Provisions:   | When primary line power falls below a predetermined level while the computer is running, a power fail warning signal from the power supply causes an interrupt to memory location 00004. Memory location 00004 is intended to contain a jump-to-subroutine (JSB) instruction to a user-written power fail subroutine. A minimum of 5 milliseconds is available to execute the power fail subroutine. |                                                                                                                                                                                                                                         |  |  |  |

| Memory Protect:          | CPU memory protect logic (when enabled):                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                         |  |  |  |

|                          | <ol> <li>Protects memory of<br/>entry by programm<br/>and B-Registers.</li> </ol>                                                                                                                                                                                                                                                                                                                    | on a page-by-page basis against alteration or<br>ned instructions, except those involving the A-                                                                                                                                        |  |  |  |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                         |  |  |  |

#### Table 1-1. Functional Specifications for A-Series Computers

#### Table 1-1. Functional Specifications for A-Series Computers (Continued)

|                                         | <ol> <li>Prohibits execution of I/O instructions except those referencing<br/>select code 01 (the CPU status register and overflow register). This<br/>limits control of I/O operations to interrupt control only, which can<br/>be used to give exclusive control of the I/O system to an executive<br/>program.</li> </ol>                                                                                             |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | <ol> <li>In response to a memory protect violation, interrupts the computer<br/>and saves the address of the violating instruction in the memory<br/>protect violation register, from which it can be made accessible in<br/>the A- or B-Register by a single assembly language instruction.</li> </ol>                                                                                                                  |

| Time Base Generator Interrupt:          | A time base generator interrupt is provided for maintaining a real-time<br>clock. The interrupt request is made when the CPU signals, at<br>10-millisecond intervals, that its clock is ready to roll over. Timing<br>accuracy of the TBG is plus or minus 2.16 seconds per day. The A990<br>also allows setting the TBG to a user-selected frequency.                                                                   |

| Unimplemented Instruction<br>Interrupt: | An unimplemented instruction interrupt is requested when the CPU chip signals that the last instruction fetched was not recognized by it. This interrupt provides a straightforward entry to software routines for the execution of instruction codes not recognized by the A-Series system hardware.                                                                                                                    |

| MEMORY                                  |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Memory Structure:                       | 64 pages minimum of 2048 bytes per page, with direct access to cur<br>rent page or base page (page 00), and indirect or mapped access to<br>all other pages.                                                                                                                                                                                                                                                             |

| Memory Cycle Time:                      | A400: 454 nanoseconds.<br>A600/A600+: 454 nanoseconds.<br>A700: 500 nanoseconds.<br>A900: 133 nanoseconds (cache memory)<br>A990: 100 nanoseconds (cache memory)                                                                                                                                                                                                                                                         |

| I/O MASTER                              |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Purpose:                                | To maintain the high performance of the A-Series I/O structure, HP<br>uses the I/O Master as the standard interface circuitry to the back<br>plane. It includes the I/O processor (IOP) chip, which executes I/O<br>instructions, and other circuitry to make high-speed transfers possible.<br>Every HP 1000 A-Series I/O interface card including the HP 12010A<br>Breadboard interface, has the I/O Master circuitry. |

| Determination of I/O Address:           | The I/O address select code is set for each interface by select code switches on the interface card and is therefore independent of the card position along the backplane bus. This select code address is loaded into a register in the IOP on power up and is compared with any I/O address instruction which is executed.                                                                                             |

| I/O Addressing:                         | An I/O interface is pre-addressed by having its select code loaded<br>into the Global Register (GR) of the IOP chip, with a single instruction.<br>This leaves the six select code bits of I/O instructions available for<br>addressing registers or other functions on the interface.                                                                                                                                   |

| Table 1-1. | Functional S | pecifications for | <b>A-Series</b> | Computers | (Continued) |

|------------|--------------|-------------------|-----------------|-----------|-------------|

|------------|--------------|-------------------|-----------------|-----------|-------------|

| I/O Instruction Execution Times: |                                                                                                                                                                                                                                                                                                                                                   |                  |                            |                         |                        |                  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------|-------------------------|------------------------|------------------|

|                                  | Execute Time (µse                                                                                                                                                                                                                                                                                                                                 |                  |                            |                         |                        |                  |

|                                  | Instruction                                                                                                                                                                                                                                                                                                                                       | A400             | A600+                      | A700                    | A900                   | A990             |

|                                  | STC,CLC,STF,CLF                                                                                                                                                                                                                                                                                                                                   | 2.66             | 2.95                       | 3.50                    | **                     | ***              |

|                                  | LIAVB                                                                                                                                                                                                                                                                                                                                             | 5.31             | 5.90                       | 6.00                    | 3.07                   | 5.30             |

|                                  | MIA/B                                                                                                                                                                                                                                                                                                                                             | 5.31             | 5.90                       | 6.00                    |                        | 5.30             |

|                                  | OTA/B                                                                                                                                                                                                                                                                                                                                             | 4.50             | 4.99                       | 5.25                    | 3.33                   | 5.30             |

|                                  | SFC,SFS without skip                                                                                                                                                                                                                                                                                                                              |                  | 2.95                       | 3.50                    | 1.33                   | 3.80             |

|                                  | SFC,SFS with skip                                                                                                                                                                                                                                                                                                                                 | 3.67             | 4.09                       | 5.25                    | 2.40                   | 3.80             |

|                                  | * These figures assume<br>increase execution tim<br>** STC, CLC = 2.667; (<br>*** STC, CLC = 3.6; C                                                                                                                                                                                                                                               | nes.<br>CLF, STF | = 1.2                      | on; DMA                 | intervent              | tion may         |

| I/O Device Interrupt Priority:   | Depends on I/O interfac<br>face closest to the centr<br>the other interfaces in ca<br>having successively low                                                                                                                                                                                                                                     | al proce         | ssor card<br>farther fro   | has the h               | nighest pr             | riority, with    |

| I/O Interrupt Procedure:         | One or more I/O interfaces requests an interrupt. When the central processor acknowledges the interrupt request, it executes the instruction in a memory location that corresponds to the select code of the highest-priority interrupting interface. The select code is placed on the address bus by the interface.                              |                  |                            |                         |                        |                  |

| Interrupt Masking:               | The I/O Master logic includes an interrupt mask register which pro-<br>vides for selective inhibition of interrupts from specific interfaces under<br>program control. This register can be programmed to temporarily cut<br>off undesirable interrupts from any combination of interfaces when<br>they could interfere with crucial transfers.   |                  |                            |                         |                        |                  |

| Interrupt Latency:               | A400: 4.2 to 36 microseconds; 4.6 microseconds typical. (Interrupts cannot be serviced until a DMA cycle or an instruction in progress has completed execution.) The worst-case latency of 36 microseconds is based upon time to complete the longest uninterruptible standard instruction.                                                       |                  |                            |                         |                        |                  |

|                                  | A600/A600+: 4.7 to 40 microseconds; 5.1 microseconds typical.<br>(Interrupts cannot be serviced until a DMA cycle or an instruction in<br>progress has completed execution.) The worst-case latency of 40<br>microseconds is based upon time to complete loading or storing of<br>a map (LMAP, SMAP), the longest standard instruction.           |                  |                            |                         |                        |                  |

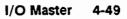

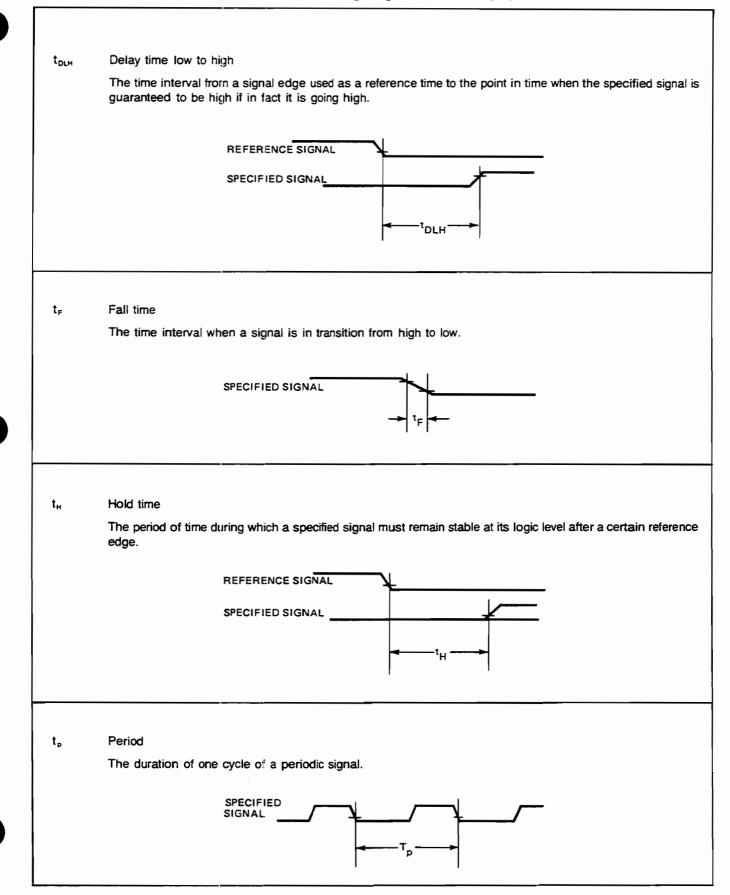

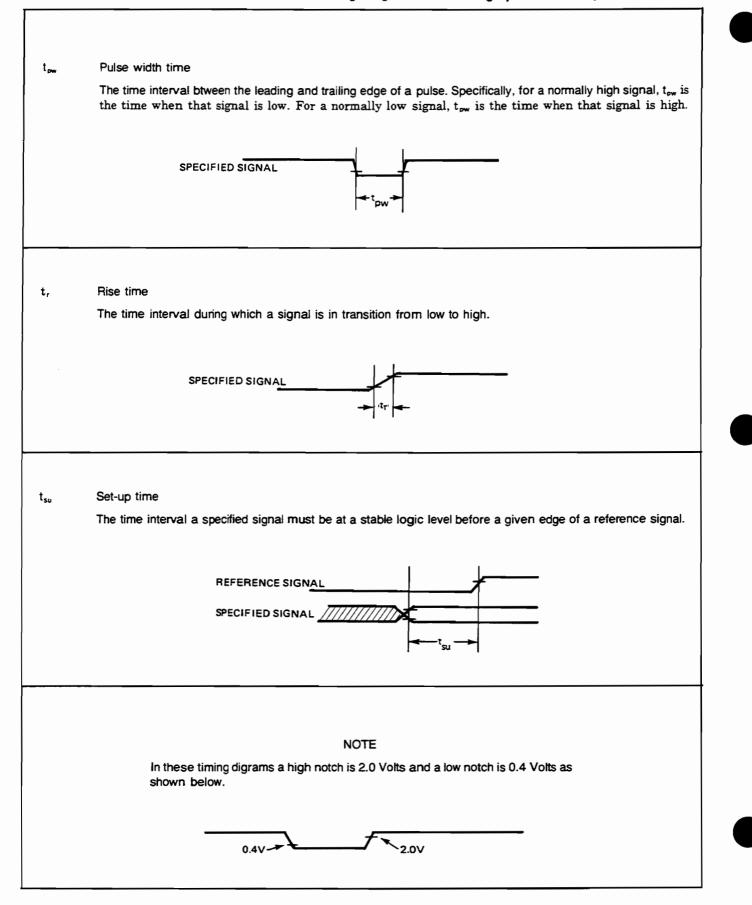

|                                  | A700: 8.00 to 29.75 microseconds; 10.00 microseconds typical. (In-<br>terrupts cannot be serviced until a DMA cycle or an instruction in<br>progress has completed execution.) The worst-case latency of 29.75<br>microseconds is based upon time to complete a floating point divide<br>(FDV), the longest uninterruptible standard instruction. |                  |                            |                         |                        |                  |